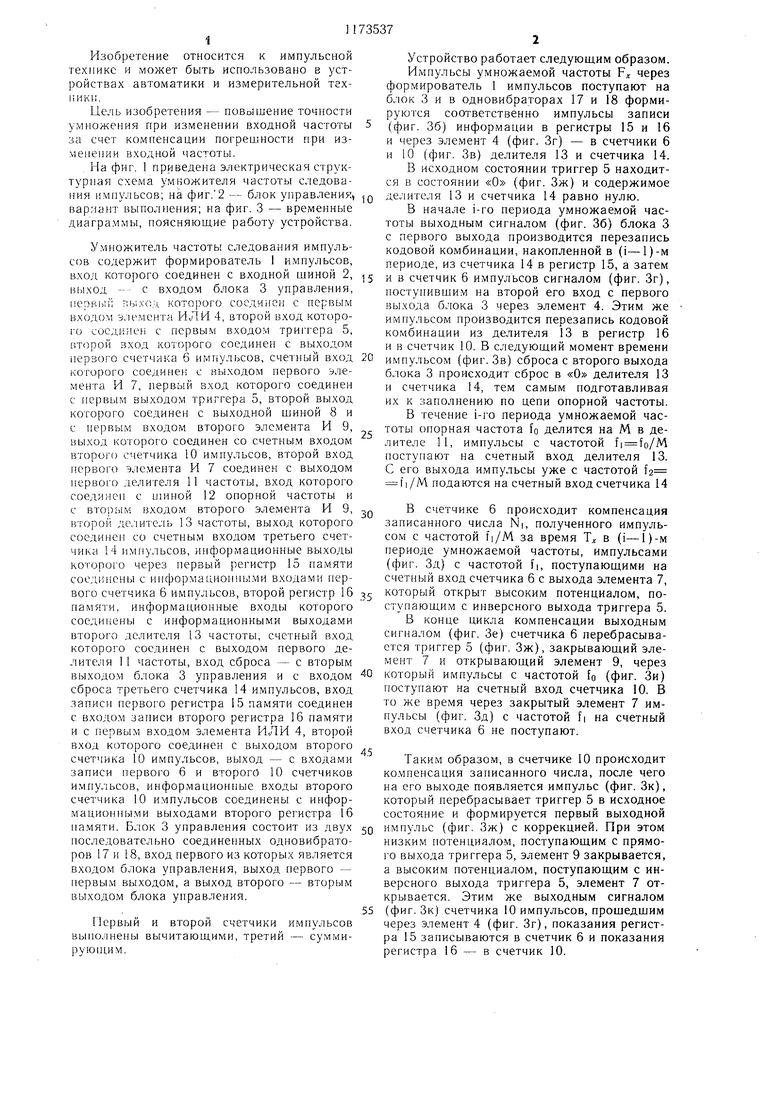

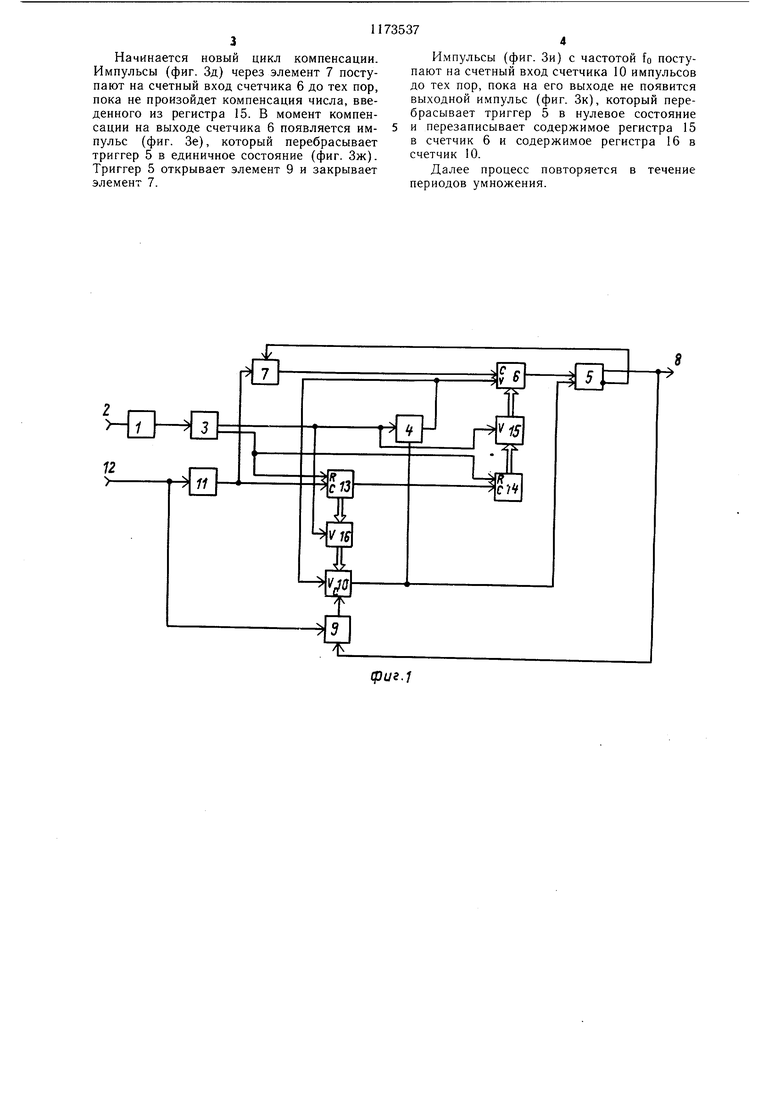

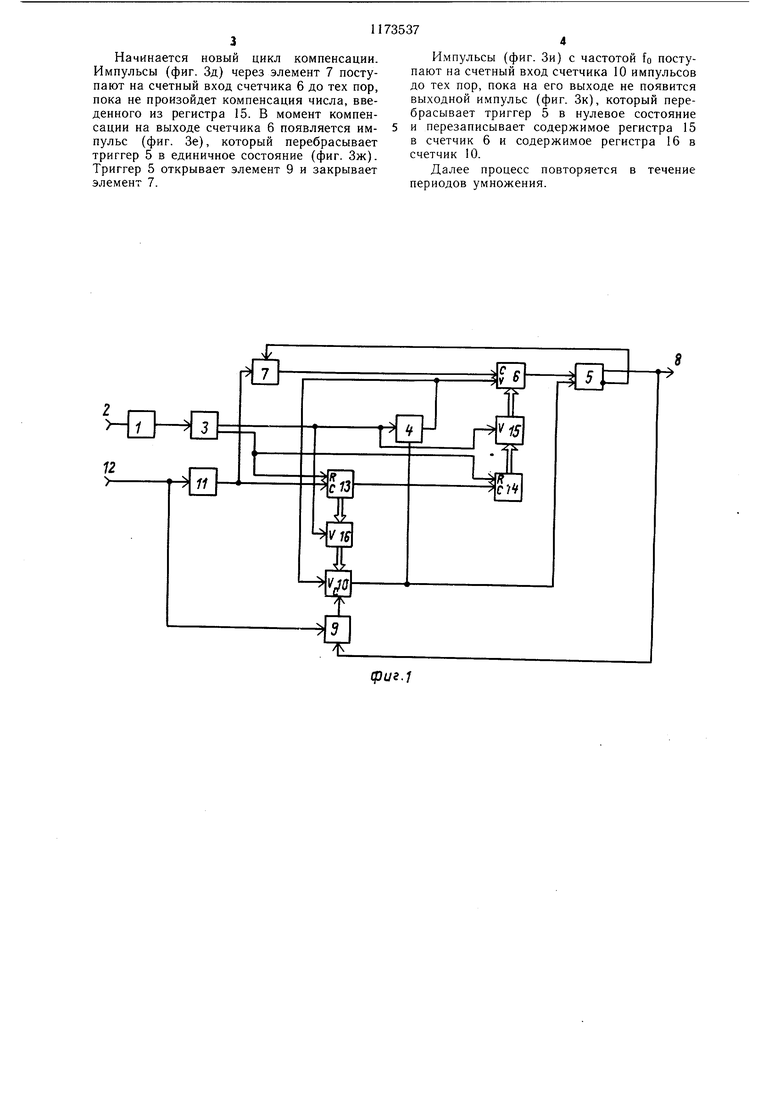

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и измерительной техЦель изобретения - пово шение точности умножения при изменении входной частоты за счет компенсации погрешности при изменении входной частоты. На фиг. 1 приведена электрическая структурная схема умножителя частоты следования импульсов; на фиг.2 - блок управления вариант выполнения; на фиг. 3 - вре.менные диагра.ммы, поясняющие работу устройства. Умножитель частоты следования импульсов содержит формирователь 1 импульсов. вход которого соединен с входной шиной 2, выход - с входом блока 3 управления пеовый р.ыход которого соединен с первым входом элемента ИЛИ 4, второй вход которого сосдииер с первым входом триггера 5, второй вход которого соединен с выходом первого счетчика 6 импульсов, счетный вход которого соединен с выходом первого элемента И 7, первый вход которого соединен с первым выходом триггера 5, второй выход которого соединен с выходной шиной 8 и с первым входом второго элемента И 9, выход которого соединен со счетным входом второго счетчика 10 импульсов, второй вход первого эле.мента И 7 соединен с выходом первого делителя 11 частоты, вход которого соедянен с 12 опорной частоты и с BTOjibiM входом второго элемента И 9, второй делитель 13 частоты, выход которого соединен со счетным входом третьего счетчика 14 импульсов, информационные выходы которого через первый регистр 15 памяти соединены с информационными входами первого счетчика 6 импульсов, второй регистр 16 памяти, информационные входы которого соединены с информационными выходами второго делителя 13 частоты, счетный вход которого соединен с выходом первого делителя 1 1 частоты, вход сброса - с вторым выходом блока 3 управления и с входом сброса третьего счетчика 14 импульсов, вход записи первогО регистра 15 памяти соединен с входом записи второго регистра 16 памяти и с первым входом элемента ИЛИ 4, второй вход которого соединен с выходом второго счетчика 10 импульсов, выход - с входами записи первого 6 и второго К) счетчиков импульсов, информационные входы второго счетчика 10 импульсов соединены с информационными выходами второго регистра 16 па.мяти. Блок 3 управления состоит из двух последовательно соединенных одновибраторов 17 и 18, вход нервого из которых является входом блока управления, выход первого - первым выходом, а выход второго - вторым выходом блока управления. Первый и второй счетчики импульсов выполнены вычитающими, третий - сумми)уЮ1ДИМ. Устройство работает следующим образом. Импульсы умножаемой частоты F через формирователь 1 импульсов поступают на блок 3 и в одновибраторах 17 и 18 формируются соответственно импульсы записи (фиг. 36) информации в регистры 15 и 16 и через элемент 4 (фиг. Зг) - в счетчики 6 и 10 (фиг. Зв) делителя 13 и счетчика 14. В исходном состоянии триггер 5 находится в состоянии «О (фиг. Зж) и содержимое делителя 13 и счетчика 14 равно нулю. В начале i-ro периода умножаемой частоты выходным сигналом (фиг. 36) блока 3 с первого выхода производится перезапись кодовой комбинации, накопленной в (i-1)-м периоде, из счетчика 14 в регистр 15, а затем ив счетчик 6 импульсов сигналом (фиг. Зг), поступившим на второй его вход с первого выхода блока 3 через элемент 4. Этим же импульсом производится перезапись кодовой комбинации из делителя 13 в регистр 16 и в счетчик 10. В следующий момент времени импульсо.м (фиг. Зв) сброса е второго выхода блока 3 происходит сброс в «О делителя 13 и счетчика 14, тем самым подготавливая их к заполнению по цепи опорной частоты. В течение i-ro периода умножаемой частоты опорная частота fo делится на М в делителе 11, импульсы с частотой f| fo/M поступают на счетный вход делителя 13. С его выхода импульсы уже с частотой f2 fi/M подаются на счетный вход счетчика 14 В счетчике 6 происходит компенсация записанного числа NI, полученного импульсом с частотой f:/M за время Т в (i-1)-м периоде умножаемой частоты, импульсами (фиг. Зд) с частотой fi, поступающими на счетный вход счетчика 6 с выхода элемента 7, который открыт вь соким потенциалом, поступающим с инверсного выхода триггера 5. В конце цикла компенсации выходным сигналом (фиг. Зе) счетчика 6 перебрасывается триггер 5 (фиг. Зж), закрывающий элемент 7 и открывающий элемент 9, через который импульсы с частотой fo (фиг. Зи) поступают на счетный вход счетчика 10. В то же время через закрытый элемент 7 импульсы (фиг. З.д) с частотой fi на счетный вход счетчика 6 не поступают. Таким образом, в счетчике 10 происходит ко.мпенсация записанного числа, после чего на его выходе появляется импульс (фиг. Зк), который перебрасывает триггер 5 в исходное состояние и формируется первый выходной импульс (фиг. Зж) с коррекцией. При этом низким потенциалом, поступающим с прямого выхода триггера 5, элемент 9 закрывается, а высоким потенциалом, поступающим с инверсного выхода триггера 5, элемент 7 открывается. Этим же выходным сигналом (фиг. Зк) счетчика 10 импульсов, прощедщим через элемент 4 (фиг. Зг), показания регистра 15 записываются в счетчик 6 и показания регистра 16 - в счетчик 10. 3 Начинается новый цикл компенсации. Импульсы (фиг. Зд) через элемент 7 поступают на счетный вход счетчика 6 до тех пор, пока не произойдет компенсация числа, введенного из регистра 15. В момент компенсации на выходе счетчика 6 появляется импульс (фиг. Зе), который перебрасывает триггер 5 в единичное состояние (фиг. Зж). Триггер 5 открывает элемент 9 и закрывает элемент 7. Импульсы (фиг. Зи) с частотой Ь поступают на счетный вход счетчика 10 импульсов до тех пор, пока на его выходе не появится выходной импульс (фиг. Зк), который перебрасывает триггер 5 в нулевое состояние и перезаписывает содержимое регистра 15 в счетчик 6 и содержимое регистра 16 в счетчик 10. Далее процесс повторяется в течение периодов умножения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления в избыточном последовательном коде | 1986 |

|

SU1365078A1 |

| Преобразователь последовательного кода в параллельный | 1987 |

|

SU1418911A1 |

| Умножитель частоты | 1983 |

|

SU1135004A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Умножитель частоты | 1979 |

|

SU907781A1 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1709515A1 |

| Умножитель частоты | 1987 |

|

SU1448394A2 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1001098A1 |

| Способ компенсации погрешностей акустических локационных уровнемеров и устройство для его осуществления | 1985 |

|

SU1529047A1 |

УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ, содержащий формирователь импульсов, вход которого соединен с входной шиной, выход - с входом блока управления, первый выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с первым входом триггера, второй вход которого соединен с выходом первого счетчика импульсов, счетный вход которого соединен с выходом первого элемента И, первый вход которого соединен с первым выходом триггера, второй выход которого соединен с выходной шиной и с первым входом второго элемента И, выход которого соединен со счетным входом второго счетчика импульсов, второй вход первого элемента И соединен с выходом первого делителя частоты, вход которого соединен с шиной опорной частоты и с вторым входом второго элемента И, второй делитель частоты, выход которого соединен со счетным входом третьего счетчика импульсов, информационные выходы которого через первый регистр памяти соединены с информационными входами первого счетчика импульсов, отличающийся тем, что, с целью повышения точности умножения при изменении входной частоты, в него введен второй регистр памяти, информационные входы которого соединены с информационными выходами второго делителя частоты, счетный вход которого соединен с выходом первого $S делителя частоты, вход сброса - с вторым выходом блока управления и с входом сброса (Л третьего счетчика импульсов, вход записи первого регистра памяти соединен с входом записи второго регистра памяти и с первым входом элемента ИЛИ, второй вход которого соединен с выходом второго счетчика импульсов, выход - с входами записи первого и второго счетчиков импульсов, а информационные входы второго счетчика импульсов соединены с информационными выходами второго регистра памяти. 00 гСЛ СО

qpui.l

5 fifi

lirillllllllllllllllllllllll Illlllllllllllllllllllllllllllll mill

M

и

(риг.З

h

IIIIHII

| Умножитель частоты повторения импульсов | 1981 |

|

SU1056372A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР № 760420 кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-08-15—Публикация

1984-02-07—Подача