сд

;о

О5 Jib

4

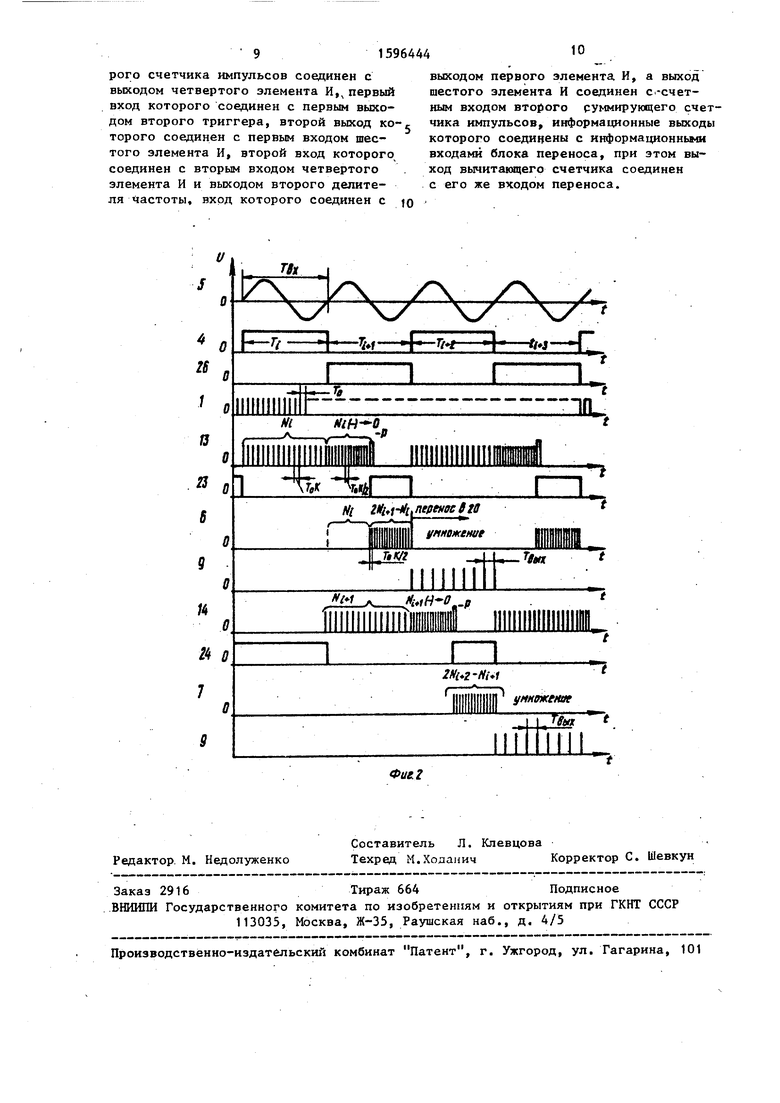

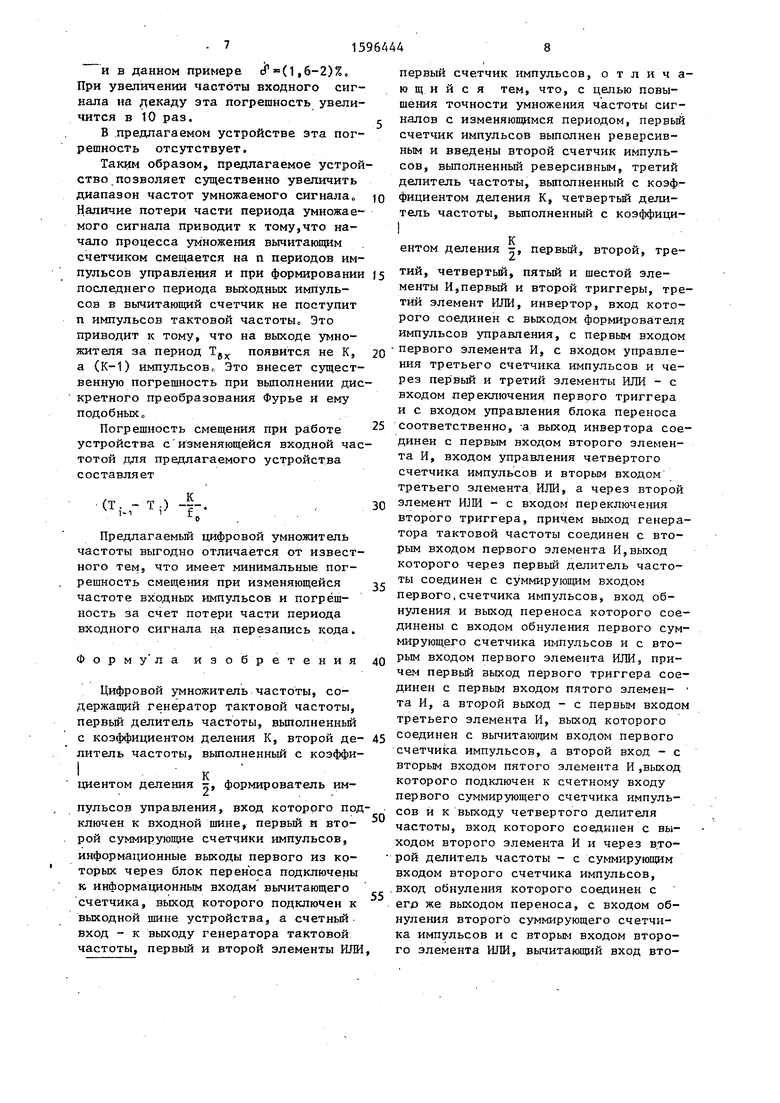

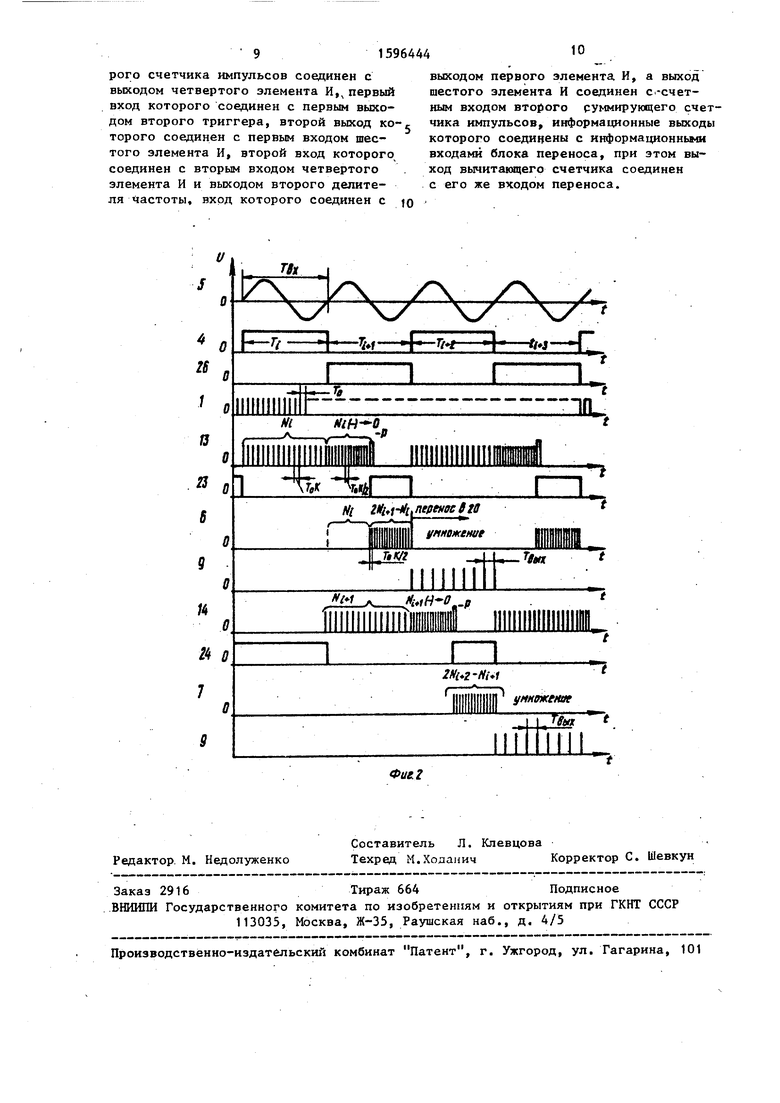

4; Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники, а также в синтезаторах частот. Цель изобретения - повышение точности умножения частоты сигналов с изменяющимся периодом. За счет уменьшения погрешности смещения и потери части периода входного сигнала на перезапись кода. На Фиг. 1 приведена электрическая функциональная схема устройства; на фиг„ 2 - временные диаграммы, поясняющие работу устройства. Цифровой умножитель частоты содержит генератор 1 тактовой частоты, первый делитель 2 частоты, выполненный с коэффициентом деления К, второй делитель 3 частоты, выполненньй с коэффициентом деления , формирователь 4 импульсов управления, вход которого подключен к входной шине 5, первый и .второй суммирующие счетчики 6 и 7 им}пульсов, информационные входы первого суммирующего счетчика 6 через блок 8 переноса подключены к информационным входам вычитающего счетчика 9, выход которого подключен к выходной шине 10 устройства, а счетный вход подключен к выходу генератора 1 тактовой частоты, первьй и второй элементы ИЛИ 11 и 12, первый и второй счетчики 13 и 14 импульсов, выполненные реверсивными, третий делитель 15 частоты, выполненный с коэффициентом деления К, четвер тьй делитель 16 частоты, выполненньй с коэффициентом деления г, первый, второй, третий, четвертьй, пятьй и шестой элементы И 17 - 22, первый и второй триггеры 23 и 24, третий элемент ИЛИ 25, инвертор 26, вход которо го соединен с выходомформирователя 4 импульсов управления, с первым входом первого элемента И 17, с входом управления третьего счетчика 13 импульсов и через первьй и третий элементы ИЛИ 11 и 25 - с входом переключения первого триггера 23 с входом уп равления блока 8 переноса соответственно, а выход инвертора 26 соединен с первым входом второго элемента И 18 входом управления четвертого счетчика 14 импульсов и вторым входом третьего элемента ИЛИ 25, а через второй элемент ИЛИ 12 - с входом переключения второго триггера 24, причем выход ге-. нератора 1 такто)вой частоты соединен с вторьм входом первого элемента И 17, выход которого через первый делитель 2 частоты соединен с суммирующим входом первого счетчика 13 импульсов, вход обнуления и выход переноса которого соединен с входом обнуления первого суммирующего счетчика 6 импульсов и с вторым входом первого элемента ИЛИ 11, причем первый выход первого триггера 23 соединен с первым входом пятого элемента И 21, а второй выход с первым входом третьего элемента И 19, выход которого соединен с вычитающим входом первого счетчика 13 импульсов, а второй вход соединен с выходом четвертого делителя 16 импульсов и с вторым входом пятого элемента И 21, выход которого соединен с счетным входом первого суммирующего счетчика 6 импульсов, вход четвертого делителя 16 импульсов соединен с выходом второго элемента И 18 и через второй делитель 15 частоты - с суммиру-ющим входом второго счетчика 14 импульсов, вход обнуления которого соединен с его же выходом переноса,- с входом обнуления второго суммирующего счетчика и с вторым входом второго элемента ИЛИ 12, вычитающий вход второго реверсивного счетчика 14 импульсов соединен с выходом четвертого элемента И 20, первый вход которого соединен с первым выходом второго триггера 24, второй выход которого соединен с первым входом шестого элемента И 22, второй вход которого соединен с вторым входом четвертого элемента И 20 и выходом второго делителя 3 час-. тоты, вход которого соединен с выходом первого элемента И 17 а выход шестого элемента И 22 соединен с счетным входом второго суммирующего счетчика 7 импульсов, информационные выходы которого соединены с информационными входами блока переноса 8, при этом выход вычитающего счетчика 9 импульсов соединен с его же входом переноса В электрической функциональной схеме устройства не указаны связи для установки триггеров 23 и 24 счётчиков 6,7,13 и 14, блока переноса 8 и др. в исходное состояние. Для исключения влияния выходов суммирующих счетчиков 6 и 7 друг на друга передача кодов чисел с их выходов осуществляется через схемы , чи ло которых равно числу разрядов (схе мы в структурной схеме также не указаны, но входят в состав суммирующих счетчиков 6 и 7), Устройство работает следующим образом. Формирователь 4 из входного перио дического сигнала формирует прямоугольные импульсы управления длитель ностью, равной периоду входного сигн ла Тьх Зти импульсы поступают на вх ды управления первого и второго реверсивного счетчиков 13 и 14,вход уп равления блока 8, на входы первого 2 и второго 24 триггеров Импульсы с в хода делителя 2 с частотой F, 1, где частота следов кия импульсов генератора 1 тактовой частоты, поступают на суммирующий вход первого реверсивного счетчика 13о Число импульсов, записанное в счетчике за период (Т)., равно к начала еле дующего (i+1) периода на вычитающий вход этого счетчика с выхода делителя 16 через элемент И 19 поступают импульсы, с частотой К числе импульсов, равном Nj, происходит переполнение счетчика 13 и на вы ходе его возникает импульс, с помощь которого происходит обнуление счетчиков 13 и 6, опрокидьшание первого . триггера 23. При этом счетные импульсы с четвертого делителя 16 с частотой F, поступают через пятый г К элемент И 21 на вход суммирующего счетчика 6, в котором к концу (i+1) периода входного сигнала формируется код следующего (i+2) периода, который равен N , 2N ,-, - N j. Одновременно за (i+1) период с выхода третьего делителя 15 поступают импульсы с частотой |на суммирующий вход второго реверсивного счетчика 14, в котором записан код (i+1) периода-. В момент прихода (i+2) периода входного сигнала задним фронтом (i+1) импульса управления осуществляется: передача кода (i+2) периода с выхода счетчика 6 с помощью блока переноса в вычитающий счетчик 9} установка триггера 23 в исходное состояние; начинается формирование кода (i+3) периода в реверсивном 14 и суммирующем 7 счетчикахс Таким образом, процесс умножения частоты вдет непрерывно, В предлагаемом, у стройстве момент передачи кода из суммирующего счетчика в вычиташций совпадает с началом периода умножаемого сигнала. Следовательно, отсутствует потеря части периода входного сигнала на перезапись кода из суммирующего в вычитающий счетчик. Процесс перезаписи существенно упростился Это приведет к более стабильной и надежной работе. Если принять в качестве входного сигнала периодический сигнал треугольной формы, то дпя него амплитуда одиннадцатой гармоники составляет 0,6% от первой и может быть принята за максимальную частоту спектра входного сиг«зла f „ В этом случае частота дискретизации fo Fg,,; 5f;««KC 5-11 FO, 55 Fjy, a коэффициент умножения К 55. Если для цифрового умножения частоты применить интегральные микросхемы серии 155, которые обладают большим быстродействием, а максимальная частоf 1 та входных импульсов 0 т « - 10 МГц, то, следовательно, частота импульсов управления не должна превышать этой величины Примем двоичные суммирующий и вычитающий счетчики восьмиразрядными, имеющими емкость 255 импульсов. Наибольшая частота входного умножаемого сигнала опредеf (вх макс ится из выражения 715 Рц. При этой частоте в известом устройстве импульсы на выходе уможителя имеют смещение относительно оминального их положения на величиу, определяемую из выражения ji :1де п - число импульсов (периодов), атраченных на перезапись кода из сумирующего в вычитающий счетчик; 1. 6х меле и в данном примере а(1,6-2)% При увеличении частоты входного сигнала на декаду эта погрешность увеличится в 10 раз. В .предлагаемом устройстве эта погрешность отсутствует. Таким образом, предлагаемое устрой ство позволяет существенно увеличить диапазон частот умножаемого сигнала„ Наличие потери части периода умножаемого сигнала приводит к тому,что начало процесса умножения вычитающим счетчиком смещается на п периодов импульсов управления и при формировании последнего периода выходных импульсов в вычитающий счетчик не поступит п импульсов тактовой частоты Это приводит к тому, что на выходе умножителя за период Tg появится не К, а (К-1) импульсово Это внесет существенную погрещнОсть при выполнении дис кретного преобразования Фурье и ему подобных Погрешность смещения при работе устройства сизменяющейся входной час тотой для предлагаемого устройства составляет (Tf-r ТР -fПредлагаемьй цифровой умножитель частоты выгодно отличается от известного тем, что имеет минимальные погрешность смещения при изменяющейся частоте входных импульсов и погрешность за счет потери части периода входного сигнала на перезапись кода. Формула изобретения Цифровой умножитель частоты, содержащий генератор тактовой частоты, первьй делитель частоты, выполненньй с коэффициентом деления К, второй де литель частоты, выполненный с коэффи циентом деления , формирователь импульсов управления, вход которого по ключен к входной шине, первый и второй суммируюш 1е счетчики импульсов, информационные выходы первого из которых через блок переноса подключены к информационным входам вычитающего счетчика, выход которого подключен к выходной шине устройства, а счетньй вход - к выходу генератора тактовой частоты, первый и второй элементы ИЛ первый счетчик импульсов, отличающийся тем, что, с целью повышения точности умножения частоты сигналов с изменяющимся периодом, первьй счетчик импульсов выполнен реверсивным и введены второй счетчик импульсов, вьшолненньй реверсивным, третий делитель частоты, выполненный с коэффициентом деления К, четвертьй делитель частоты, выполненный с коэффициIентом деления , первый, второй, третий, четвертьй, пятьй и шестой элементы И,первый и второй триггеры, третий элемент ИЛИ, инвертор, вход которого соединен с выходом формирователя импульсов управления, с первым входом первого элемента И, с входом управления третьего счетчика импульсов и через первый и третий элементы ИЛИ - с входом переключения первого триггера и с входом управления блока переноса соответственно, а выход инвертора соединен с первым входом второго элемента И, входом управления четвертого счетчика импульсов и вторьм входом третьего элемента ИЛИ, а через второй элемент HJM - с входом переключения второго триггера, причем выход генератора тактовой частоты соединен с вторым входом первого элемента И,выход которого через первый делитель частоты соединен с суммирующим входом первого,счетчика импульсов, вход обнуления и выход переноса которого соединены с входом обнуления первого суммирующего счетчика импульсов и с вторым входом первого элемента ИЛИ, причем первьй выход первого триггера соединен с первым входом пятого элемента И, а второй выход - с первым входом третьего элемента И, выход которого соединен с вычитающим входом первого счетчика импульсов, а второй вход - с вторым входом пятого элемента И ,выход которого подключен к счетному входу первого суммирующего счетчика импульсов и к выходу четвертого делителя частоты, вход которого соединен с выходом второго элемента И и через второй делитель частоты - с суммирующим входом второго счетчика импульсов, вход обнуления которого соединен с его же выходом переноса, с входом обнуления второго суммирующего счетчика импульсов и с вторым входом второго элемента ИЛИ, вычитающий вход второго счетчика импульсов соединен с выходом четвертого элемента И,, первый вход которого соединен с первым выходом второго триггера, второй выход которого соединен с первым входом шестого элемента И, второй вход которого соединен с вторым входом четвертого элемента И и выходом второго делителя частоты, вход которого соединен с ю

выходом первого элемента. И, а выход шестого элемента И соединен с.-счетным входом второго руммирующего счетчика импульсов, информационные выходы которого соединены с информационными входами блока переноса, при этом выход вычитакяцего счетчика соединен с его же входом переноса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь частоты в код | 1987 |

|

SU1418906A2 |

| Устройство для стабилизации частоты вращения электродвигателя | 1989 |

|

SU1667214A1 |

| Функциональный преобразователь полинома третьей степени | 1988 |

|

SU1562907A1 |

| Формирователь импульсов с регулируемой частотой следования | 1990 |

|

SU1780186A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Преобразователь частота-код | 1987 |

|

SU1515368A1 |

| Устройство синхронизации | 1990 |

|

SU1781835A1 |

| Цифровой регистратор | 1984 |

|

SU1164549A1 |

| Устройство для кодирования сигналов частотных датчиков | 1985 |

|

SU1336246A1 |

| Цифровой частотомер | 1975 |

|

SU783701A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники. Цель изобретения - повышение точности умножения частоты сигналов с изменяющимся периодом-достигается за счет уменьшения погрешности смещения и потери части периода входного сигнала на перезапись кода. Это обеспечивается путем введения в устройство счетчика 14 импульсов, делителей 15, 16 частоты, элементов И 17-22, триггеров 23, 24, элемента ИЛИ 25, инвертора 26. Кроме того устройство содержит генератор 1 тактовой частоты, делители 2,3 частоты, формирователь 4 импульсов управления, счетчики 6,7,9,13 импульсов, блок 8 переноса, элементы ИЛИ 11, 12,входную и выходную шины 5 и 10 соответственно. 2 ил.

и

К. . .

j -г/+-TM fM

IS

fflffiH- O

л. - -Д

JeK Ч I

f/l jftf-AJiW //

н в

2 о 7

л

,-г--v v

1

уннткеное

IIIIIIH

| Цифровой умножитель частоты | 1978 |

|

SU790181A1 |

Авторы

Даты

1990-09-30—Публикация

1987-11-27—Подача