мяти, регистры 9 - 11, блоки сравнения (БС) 12 - 15, блоки совпадения 16 и 17, блок выбора передаваемых символов, шифратор 19, блок 20 управления памятью, блок 21 памяти, блок 22 памяти младших разрядов,блоки 23 и 24 разрешения записи и блок 25 пилот-сигнала. Информация, передаваемая в канал связи, является результатом двумерной обработки исходного ТВС, Элементы j-й строки передаются через отсчет (четные отсчеты) информацией об истинных значениях четырех старших разрядов исходного кода. Элементы (j + 1)-й строки пе

1

Изобретение относится к технике телевидения и может быть использовано в цифровых системах передачи изображений.

Цель изобретения - уменьшение ис- кажений цифрового телевизионного сигнала.

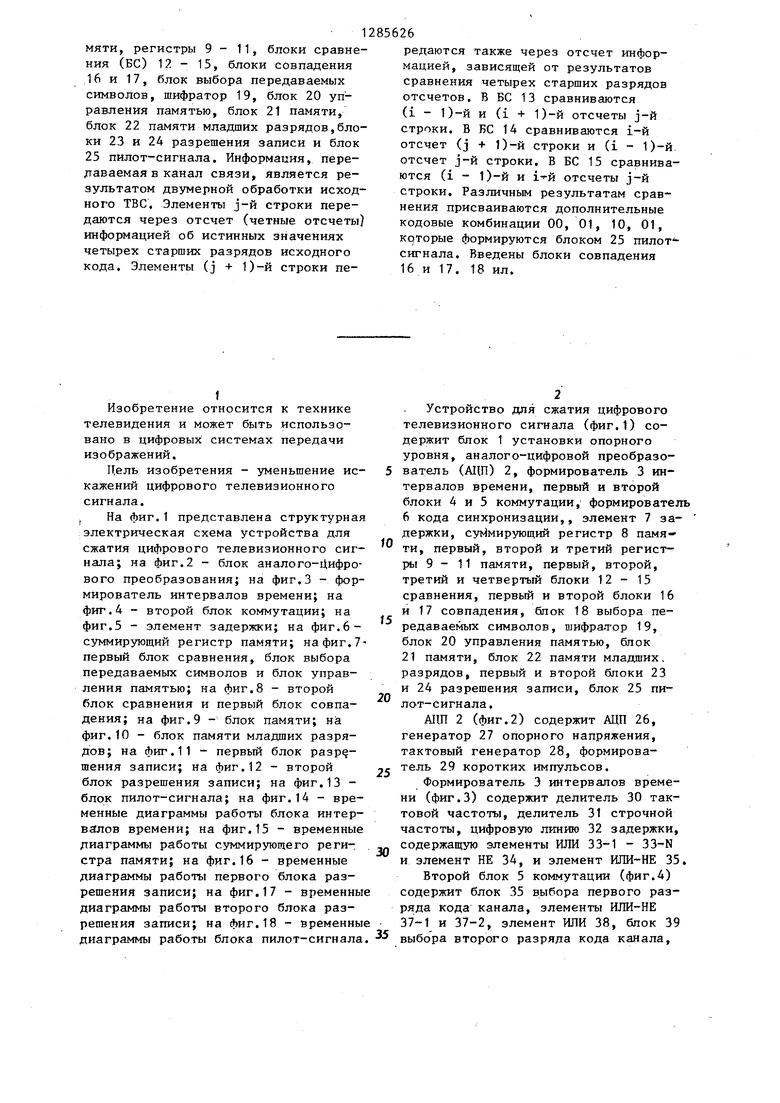

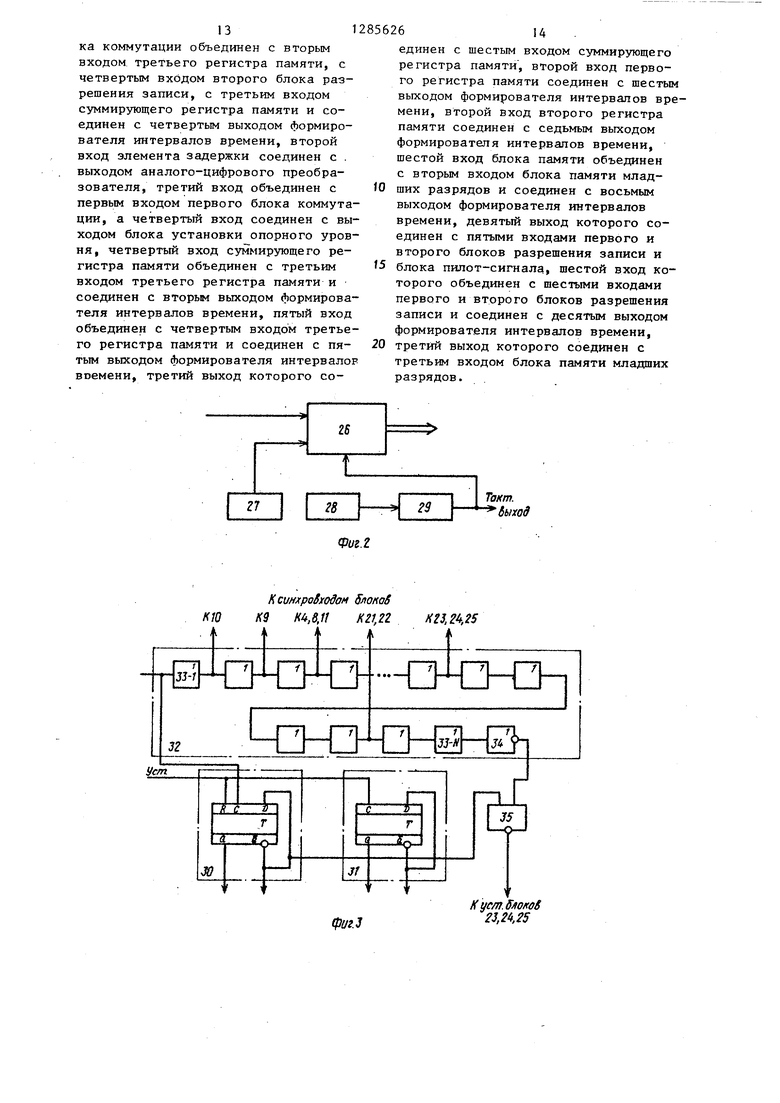

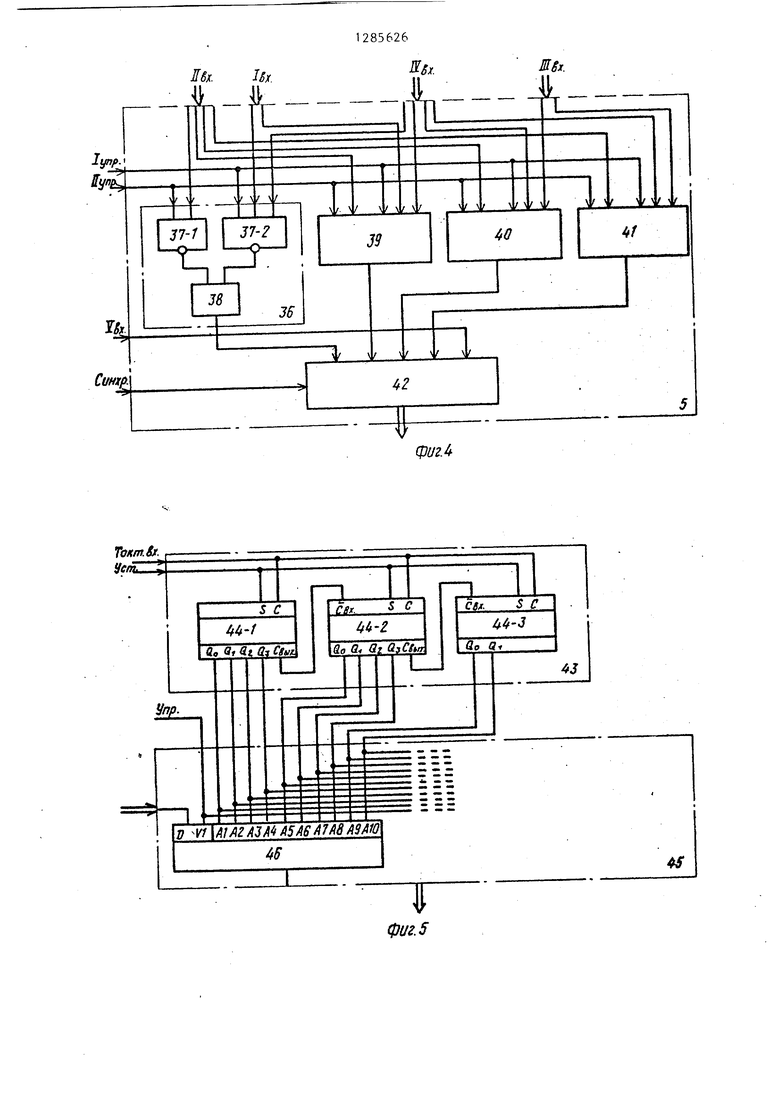

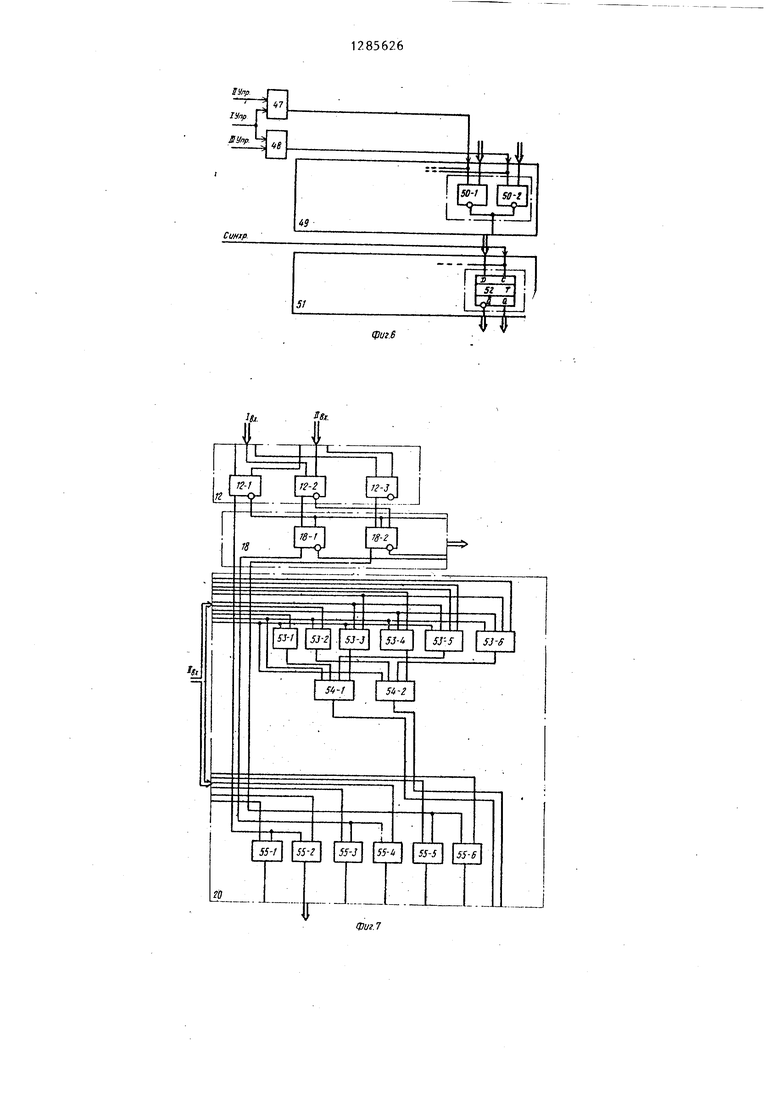

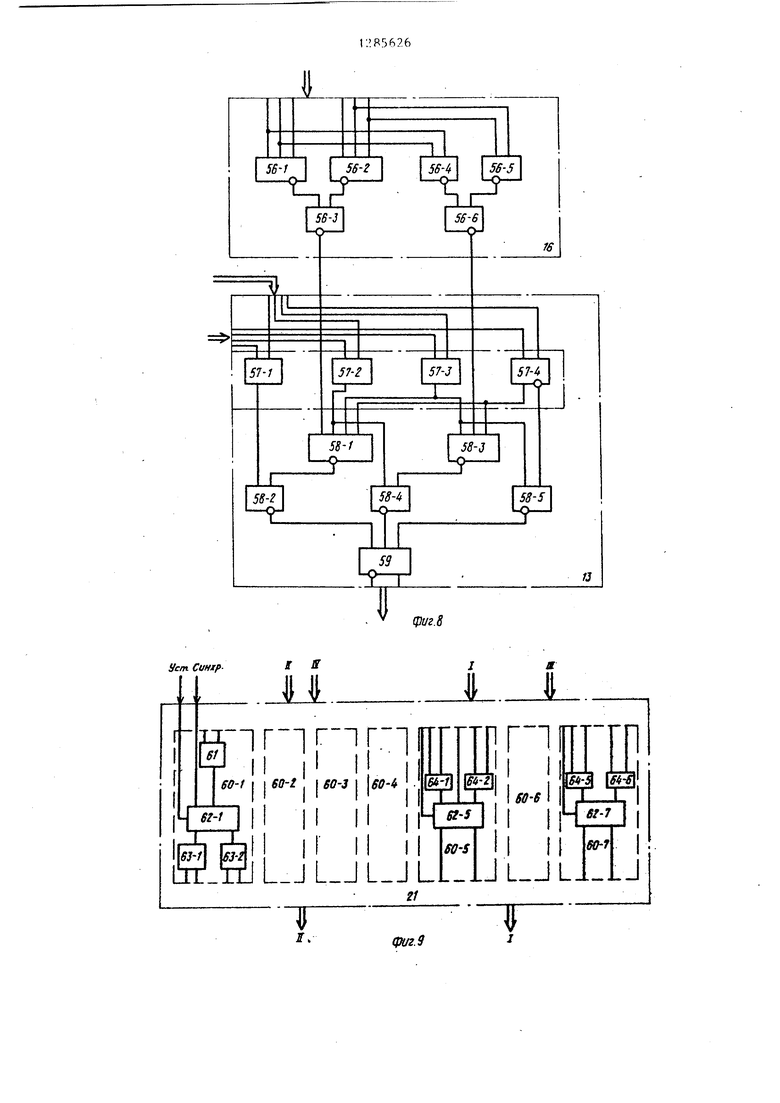

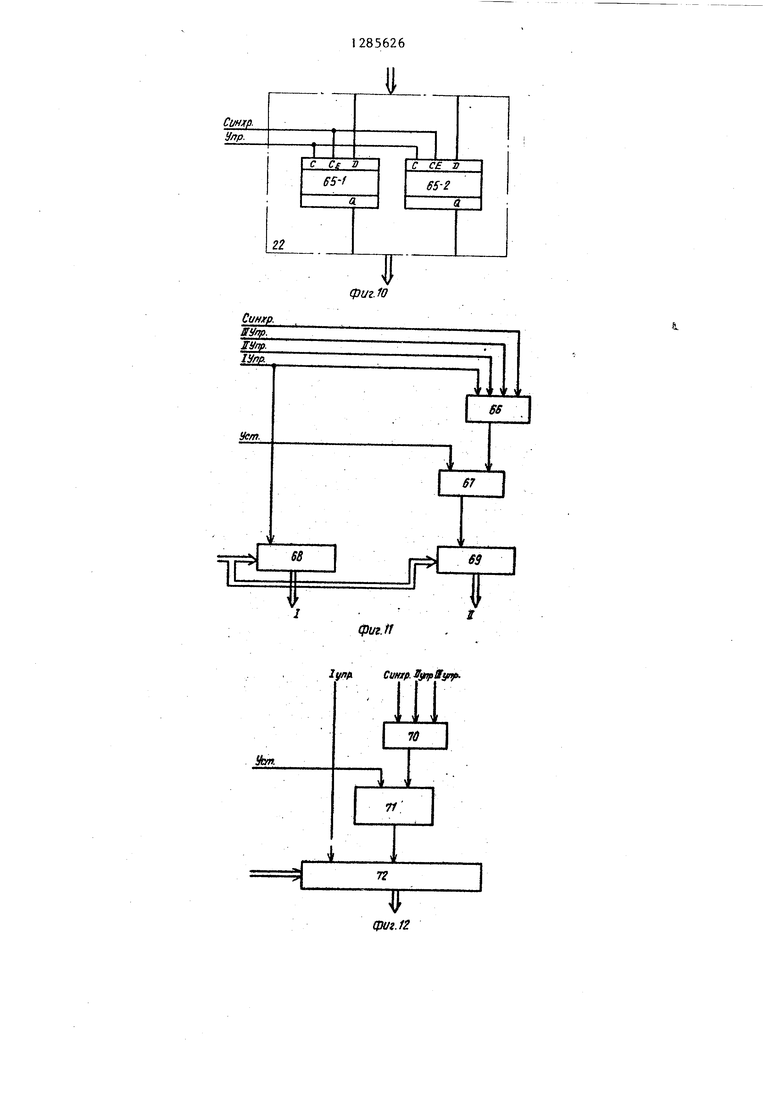

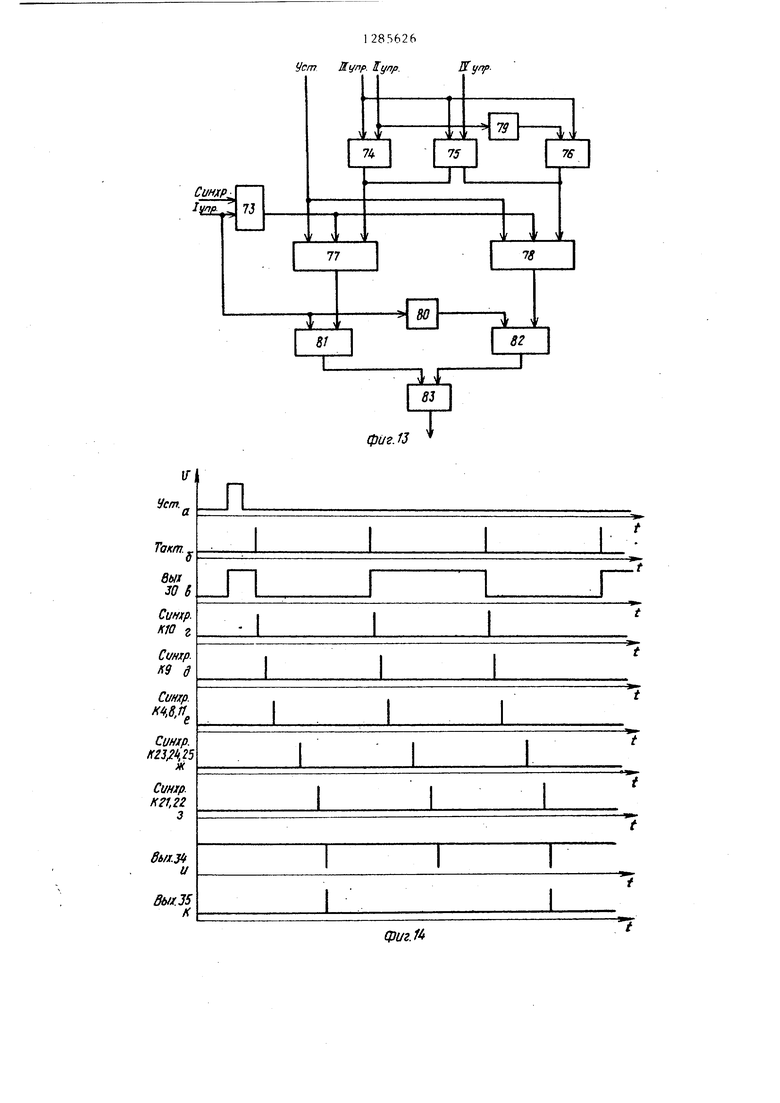

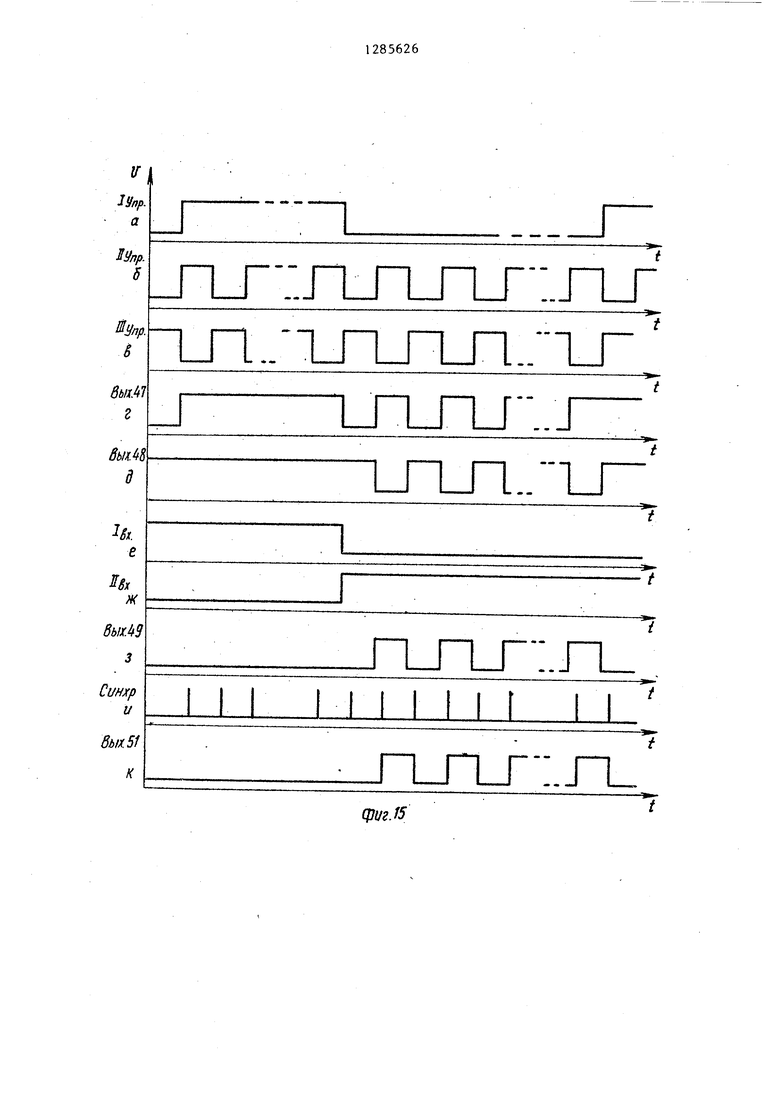

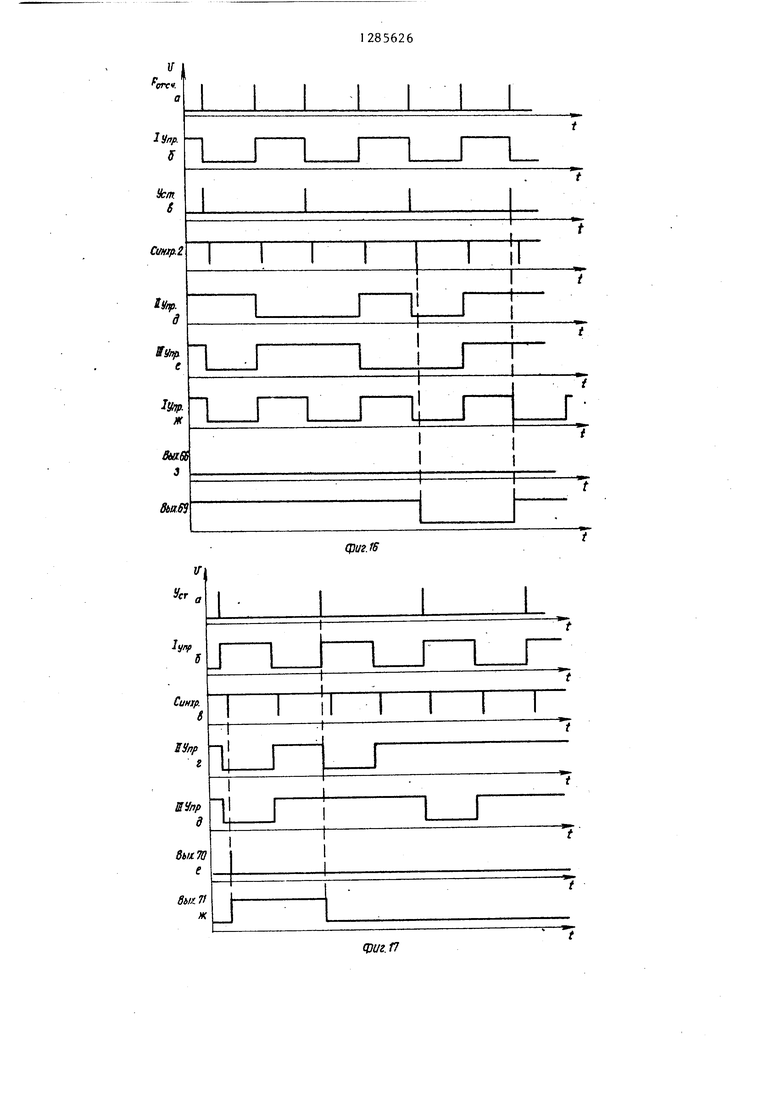

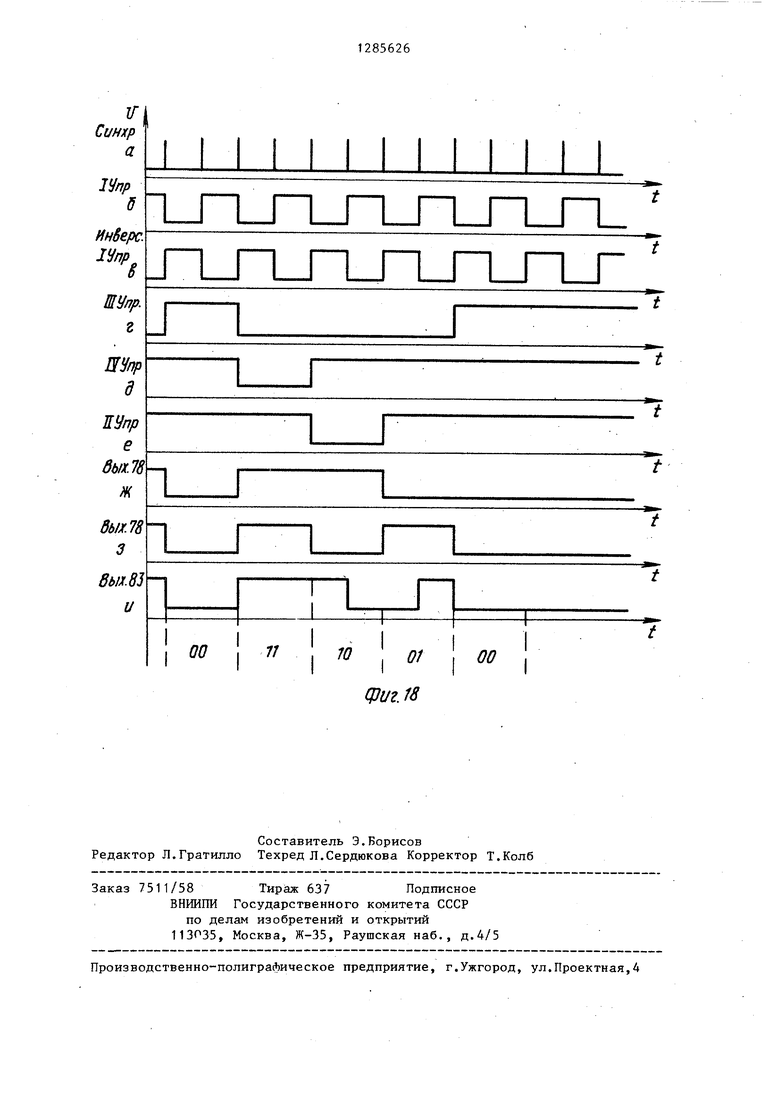

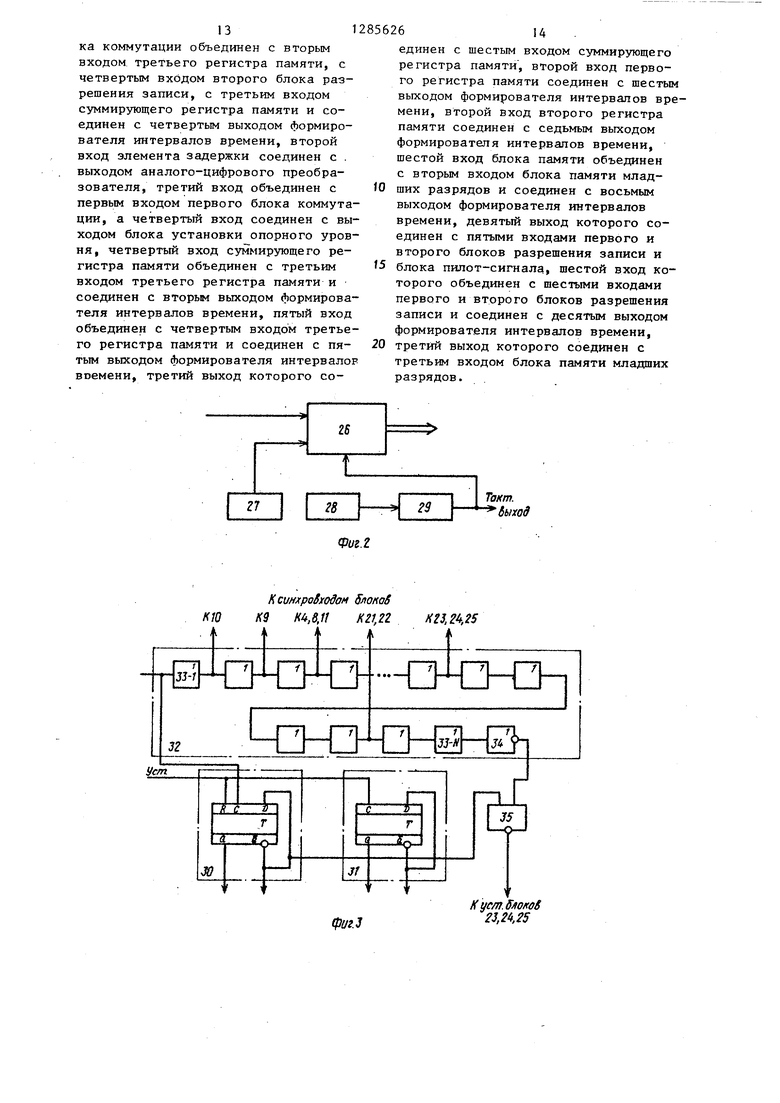

. На фиг.1 представлена структурная электрическая схема устройства для сжатия цифрового телевизионного сиг- нала; на фиг.2 - блок аналого-Дифро- вого преобразования; на фиг.З - формирователь интервалов времени; на фиг.4 - второй блок коммутации; на фиг.5 - элемент задержки; на фиг.6- суммирутощий регистр памяти; на фиг.7 первый блок сравнения, блок выбора передаваемых символов и блок управления памятью; на фиг.8 - второй блок сравнения и первый блок совпадения; на фиг.9 - блок памяти; на фиг.10 - блок памяти младших разрядов; на фиг.11 - первый блок разрушения записи; на фиг.12 - второй блок разрешения записи; на фиг.13 - блок пилот-сигнала; на фиг.14 - временные диаграммы работы блока интервалов времени; на фиг.15 - временные диаграммы работы суммирующего реги- стра памяти; на фиг.16 - временные диаграммы работы первого блока разрешения записи; на фиг.17 - временны диаграммы работы второго блока разрешения записи; на фиг.18 - временны диаграммы работы блока пилот-сигнала

85626

редаются также через отсчет информацией, зависящей от результатов сравнения четырех старших разрядов отсчетов. В БС 13 сравниваются (L - 1)-й и (i + 1)-й отсчеты j-й строки. В БС 14 сравниваются i-й отсчет (J + 1)-й строки и (i - 1)-й отсчет j-й строки. В БС 15 сравниваются (i - 1)-й и ii-й отсчеты j-й строки. Различным результатам сравнения присваиваются дополнительные кодовые комбинации 00, 01, 10, 01, которые формируются блоком 25 пилот сигнала. Введены блоки совпадения 16 и 17. 18 ил.

5

5

.

0

Устройство для сжатия цифрового телевизионного сигнала (фиг.1) содержит блок 1 установки опорного уровня, аналого-цифровой преобразователь (АЦП) 2, формирователь 3 интервалов времени, первый и второй блоки 4 и 5 коммутации, формирователь 6 кода синхронизации,, элемент 7 задержки, суммирующий регистр 8 памяти, первый, второй и третий регистры 9 - 11 памяти, первый, второй, третий и четвертый блоки 12 - 15 сравнения, первый и второй блоки 16 и 17 совпадения, блок 18 выбора передаваемых символов, шифра-тор 19, блок 20 управления памятью, блок 21 памяти, блок 22 памяти младших, разрядов, первый и второй блоки 23 и 24 разрешения записи, блок 25 пилот-сигнала.

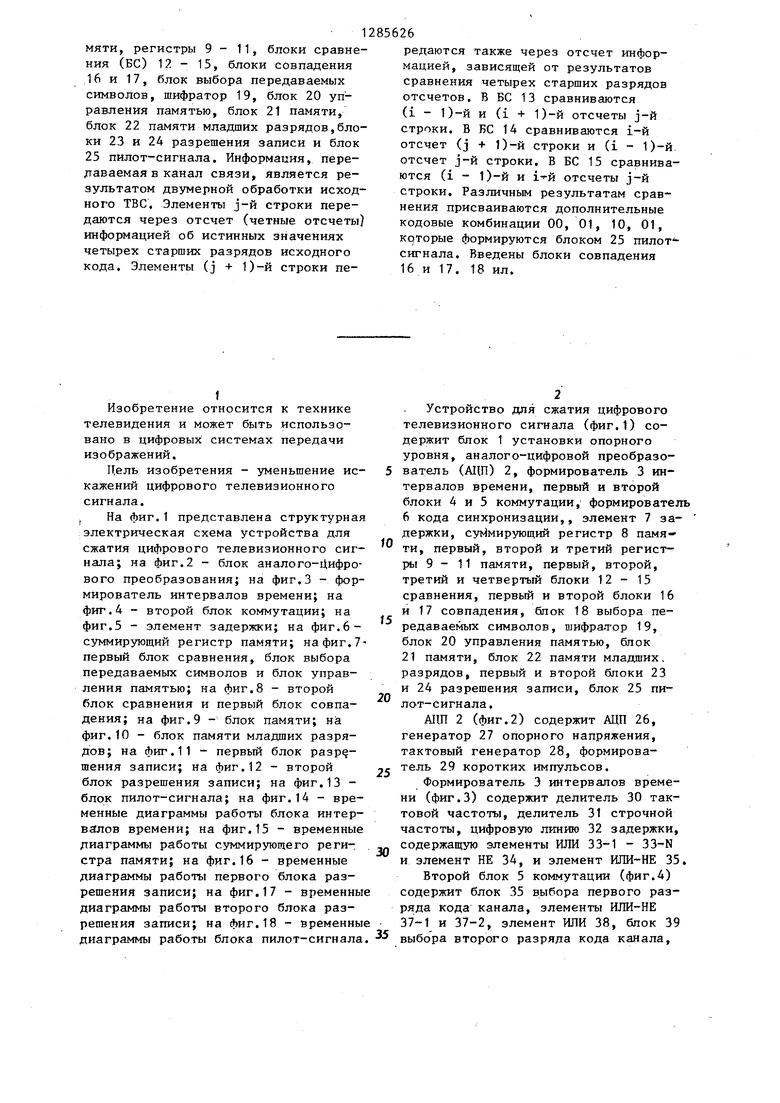

Aim 2 (фиг.2) содержит АЦП 26, генератор 27 опорного напряжения, тактовый генератор 28, формирователь 29 коротких импульсов.

Формирователь 3 интервалов времени (фиг.З) содержит делитель 30 тактовой частоты, делитель 31 строчной частоты, цифровую линию 32 задержки, содержащую элементы ИЛИ 33-1 - 33-N и элемент НЕ 34, и элемент ИЛИ-НЕ 35.

Второй блок 5 коммутации (фиг.4) содержит блок 35 выбора первого разряда кода канала, элементы ИЛИ-НЕ 37-1 и 37-2, элемент ИЛИ 38, блок 39 выбора второго разряда кода канала.

блок АО выбора третьего разряда кода канала, блок 41 выбора четвертого разряда кода канала, блок 42 памяти кода канала.

Элемент 7 задержки (фиг.5) содержит блок 43 формирования адреса, четырехразрядные счетчики 44-1 и 44-3, элемент 45 памяти, элемент 46 памяти одного разряда.

Суммирующий регистр 8 памяти (фиг,6) содержит элементы ИЛИ 47 и 48, блок 49 разрешения записи, элементы ИЛИ-НЕ 50-1 и 50-2, элемент 51 памяти, элемент 52 памяти одного разряда.

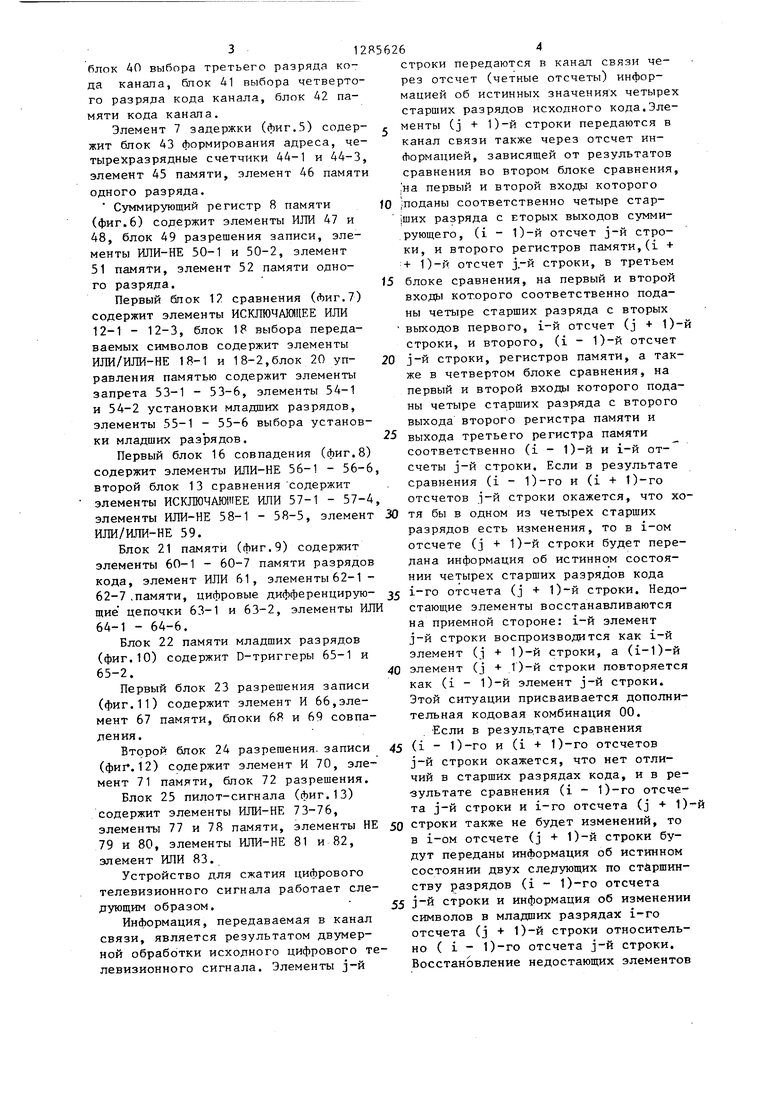

Первый блок 12 сравнения (Лиг.7) содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 12-1 - 12-3, блок 18 выбора передаваемых символов содержит элементы ИЛИ/ИЛИ-НЕ 18-1 и 18-2,блок 20 управления памятью содержит элементы запрета 53-1 - 53-6, элементы 54-1 и 54-2 установки младших разрядов, элементы 55-1 - 55-6 выбора установки младших разрядов.

Первый блок 16 совпадения (фиг,8) содержит элементы ИЛИ-НЕ 56-1 - 56-6, второй блок 13 сравнения содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 57-1 - 57-4, элементы ИЛИ-НЕ 58-1 - 58-5, элемент ИЛИ/ИЛИ-НЕ 59,

Блок 21 памяти (фиг.9) содержит элементы 60-1 - 60-7 памяти разрядов кода, элемент ИЛИ 61, элементы 62-1 строки передаются в канал связи через отсчет (четные отсчеты) информацией об истинных значениях четырех старших разрядов исходного кода,Элег менты (J + 1)-й строки передаются в канал связи также через отсчет ин- йюрмапией, зависящей от результатов сравнения во втором блоке сравнения, ; на первый и второй входы которого

fO /поданы соответственно четыре стар- 1ших разряда с вторых выходов суммирующего, (L - 1)-й отсчет j-й строки, и второго регистров памяти,(i + + 1)-й отсчет j.-й строки, в третьем

15 блоке сравнения, на первый и второй входы которого соответственно поданы четыре старщих разряда с вторых выходов первого, i-й отсчет (j + 1)-й строки, и второго, (i - 1)-й отсчет

20 j-й строки, регистров памяти, а также в четвертом блоке сравнения, на первый и второй входы которого поданы четыре старших разряда с второго выхода второго регистра памяти и

25 выхода третьего регистра памяти

соответственно (i - 1)-й и i-й от- счеты j-й строки. Если в результате сравнения (i - 1)-го и (i + 1)-го отсчетов j-й строки окажется, что хо30 тя бы в одном из четырех старших разрядов есть изменения, то в i-ом отсчете (j + 1)-й строки будет передана информация об истинном состоянии четырех старших разрядов кода

62-7 .памяти, цифровые дифференцирую- 35 го отсчета (j + 1)-й строки, Недо- щие цепочки 63-1 и 63-2, элементы ИЛИ стающие элементы восстанавливаются 64-1 - 64-6,на приемной стороне: i-й элемент

Блок 22 памяти младших разрядов j-й строки воспроизводится как i-й

элемент (j + 1)-й строки, а (i-1)-й 40 элемент (j + 1)-й строки повторяется как (i - 1)-й элемент j-й строки. Этой ситуации присваивается дополнительная кодовая комбинация 00, Если в результанте сравнения 45 (i 1)-го и (i + 1)-го отсчетов j-й строки окажется, что нет отличий в старших разрядах кода, и в ре- зультате сравнения (i - 1)-го отсчета j-й строки и i-ro отсчета (j « 1)-й элементы 77 и 78 памяти, элементы НЕ 50 строки также не будет изменений, то 79 и 80, элементы ИЛИ-НЕ 81 и 82, в i-ом отсчете (j + 1)-й строки будут переданы информация об истинном состоянии двух следующих по старшинству разрядов (i - 1)-го отсчета 55 строки и информация об изменении символов в младших разрядах i-ro отсчета (j + 1)-й строки относительно ( i - 1)-го отсчета j-й строки.

(фиг,10) содержит D-триггеры 65-1 и 65-2,

Первый блок 23 разрешения записи (фиг,11) содержит элемент И 66,элемент 67 памяти, блоки 68 и 69 совпадения.

Второй блок 24 разрегаения. записи (фиг, 12) содержит элемент И 70, элемент 71 памяти, блок 72 разрешения.

Блок 25 пилот-сигнала (фиг.13) содержит элементы ИЛИ-НЕ 73-76,

элемент ИЛИ 83,

Устройство для сжатия цифрового телевизионного сигнала работает следующим образом.

Информация, передаваемая в канал связи, является результатом двумерной обработки исходного цифрового телевизионного сигнала. Элементы j-й

строки передаются в канал связи через отсчет (четные отсчеты) информацией об истинных значениях четырех старших разрядов исходного кода,Элементы (J + 1)-й строки передаются в канал связи также через отсчет ин- йюрмапией, зависящей от результатов сравнения во втором блоке сравнения, ; на первый и второй входы которого

/поданы соответственно четыре стар- 1ших разряда с вторых выходов суммирующего, (L - 1)-й отсчет j-й строки, и второго регистров памяти,(i + + 1)-й отсчет j.-й строки, в третьем

блоке сравнения, на первый и второй входы которого соответственно поданы четыре старщих разряда с вторых выходов первого, i-й отсчет (j + 1)-й строки, и второго, (i - 1)-й отсчет

j-й строки, регистров памяти, а также в четвертом блоке сравнения, на первый и второй входы которого поданы четыре старших разряда с второго выхода второго регистра памяти и

выхода третьего регистра памяти

соответственно (i - 1)-й и i-й от- счеты j-й строки. Если в результате сравнения (i - 1)-го и (i + 1)-го отсчетов j-й строки окажется, что хотя бы в одном из четырех старших разрядов есть изменения, то в i-ом отсчете (j + 1)-й строки будет передана информация об истинном состоянии четырех старших разрядов кода

Восстановление недостающих элементов

происходит как и в предыдущем случае Этой ситуации присваивается дополнительная кодовая комбинация 11. Если в результате сравнения (i - 1)-го и (i + 1)-го отсчетов j-й строки нет изменений в старших разрядах, а в результате сравнения старших разрядов (i - 1)-го отсчета j-fi строки и i-ro отсчета (j + 1)-й строки изменения обнаружены, то производится сравнение старших разрядов (i - 1)- го и i-ro отсчетов j-й строки. Если при этом будут обнаружены изменения, что говорит о появлении в изображении поэлементной вертикальной штриховой структуры, то в i-oM отсчете (J + 1)-й строки будет передана информация об истинном состоянии четырех старших разрядов i-ro отсчета (j + 1)-й строки и восстановление недостающих элементов будет происходить как и в предыдущем случае. Этой ситуации присваивается дополнительная кодовая комбинация 10, В противнем случае, т.е. когда в старших раз-25 рабатьшает короткие импульсы (фиг, 14 б)

рядах (i - 1)-го и i-ro отсчетов j-й строки нет отличий, что говорит о появлении в сигнале горизонтального перепада яркости, характер передачи сохранится, но восстановление недостающих элементов иное: (i - 1)-и отсчет (j + 1)-й строки воспроизводится как i-й отсчет этой же строки, а i-й отсчет j-й строки повторяется как (i - 1)й отсчет этой же строки. Этой ситуации присваивается дополнительная кодовая комбинация 01. Причем для устранения влияния .шумов датчика сигнала на алгоритм восстановления недостающих элементов при сравнении (i-1)- го и (i +1)-го отсчетов j-й строки, а также (i - 1)--го и i-ro отсчетов этой же строки вводится некоторая запрещенная группа изменений между символами соответствующих отсчетов, при попадании в которую считается, что между отсчетами изменений не происходит,

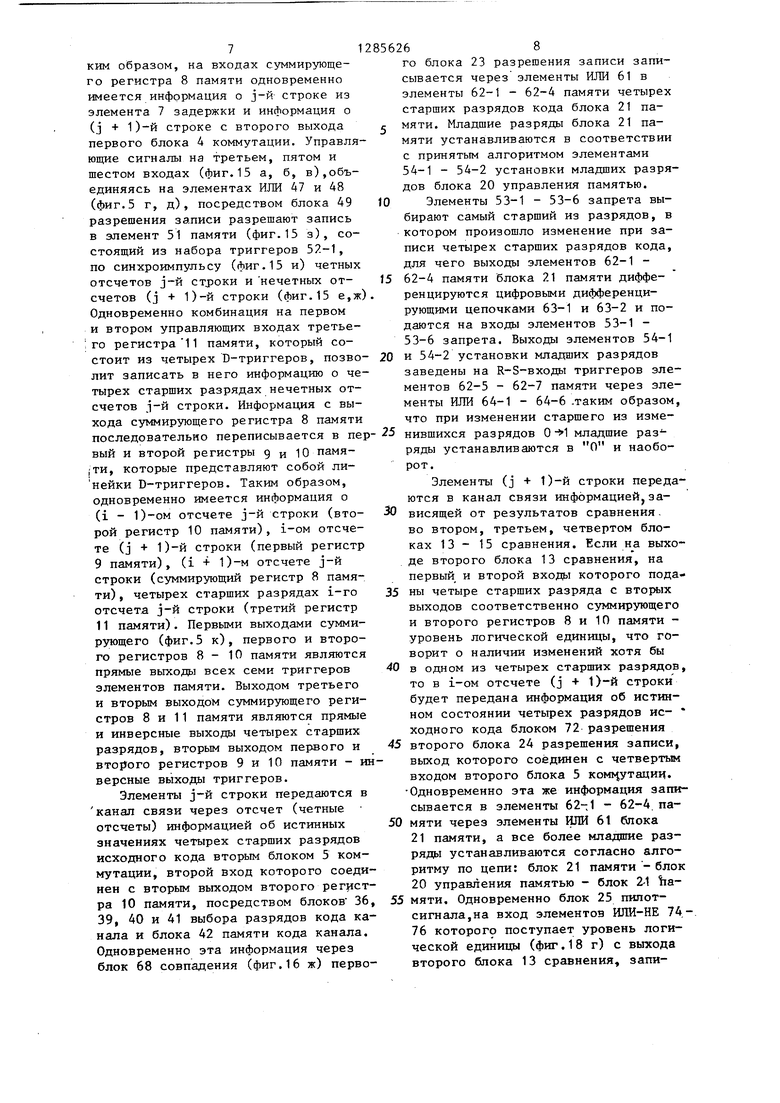

В результате, когда входной аналоговый сигнал поступает на входы блока 1 установки опорного уровня и АЦП 2 (фиг.1), селектор блока 1. установки опорного уровня, выделяет из аналогового сигнала синхросмесь, а соединенный последовательно с селектором мультивибратор вырабатывает по переднему фронту синхроимпульсов положительные импульсы (фиг,14 а)

из сигнала тактовой частоты, который поступает на первый выход и служит для запуска блока 43 формирования адреса элемента 7 задержки для полу30 чения полутактовой частоты (фиг,14 в) делителем 30 тактовой частоты формирователя 3 интервалов времени,Последний осуществляет синхронизацию работы всего устройства импульсами

35 с дервого, второго, третьего, четвертого и пятого выходов (фиг,14 г, д, е, ж, з) формирователя 3 интервалов времени . Шестой выход цифровой линии 22 задержки (фиг.14 и, к) слу40 жит для установки в исходное состояние элемента 67 памяти первого блока 23 разрешения записи,(фиг,16 в,и), элемента памяти 71,второго блока 24 разрешения записи (фиг,17 а, ж) и

45 элементов 77 и 78 памяти блока 25 пилот-сигнала. Первым выходом формирователя 3 интервалов времени является инверсный -выход полутактовой частоты, вторым - выход полутакто50 вой частоты, третьим - выход полустрочной частоты, четвертым - инверс- ньвй выход полустрочной частоты. Элемент 7 задержки записывает информацию о состояниях разрядов С выхода

55 первого блока 4 коммутации во время отрицательной полуволны на управляющем входе элемента 7 задержки и разрешает считывать информацию во время положительной полуволны. Таслужащие для установки делителя 30 тактовой частоты (фиг.14 в) формирователя 3 интервалов времени, блока 43 формирования адреса, элемента 7

задержки и элементов 60-1 - 60-7 памяти разрядов кода блока 7.1 памяти в исходное состояние и получения полустрочной частоты делителем 31 строчной частоты формирователя 3 интервашов времени, а также поступают на вход формирователя 6 кода синхронизации, который за время этого импульса вырабатывает специальные кодовые посылки, обозначающие начало

строки, В канал связи эти посылки передаются вторым блоком 5 коммутации через шифратор 19. Аналого- цифровой преобразователь 26 АЛП 2 преобразует входной аналоговый сигнал Б цифровую форму. Семиразрядный параллельный код поступает на выход АЦП 2 с тактовой частотой, задаваемой тактовым генератором 28, Форми- рователь 29 коротких импульсов выиз сигнала тактовой частоты, который поступает на первый выход и служит для запуска блока 43 формирования адреса элемента 7 задержки для полу30 чения полутактовой частоты (фиг,14 в) делителем 30 тактовой частоты формирователя 3 интервалов времени,Последний осуществляет синхронизацию работы всего устройства импульсами

35 с дервого, второго, третьего, четвертого и пятого выходов (фиг,14 г, д, е, ж, з) формирователя 3 интервалов времени . Шестой выход цифровой линии 22 задержки (фиг.14 и, к) слу40 жит для установки в исходное состояние элемента 67 памяти первого блока 23 разрешения записи,(фиг,16 в,и) элемента памяти 71,второго блока 24 разрешения записи (фиг,17 а, ж) и

45 элементов 77 и 78 памяти блока 25 пилот-сигнала. Первым выходом формирователя 3 интервалов времени является инверсный -выход полутактовой частоты, вторым - выход полутакто50 вой частоты, третьим - выход полустрочной частоты, четвертым - инверс- ньвй выход полустрочной частоты. Элемент 7 задержки записывает информацию о состояниях разрядов С выхода

55 первого блока 4 коммутации во время отрицательной полуволны на управляющем входе элемента 7 задержки и разрешает считывать информацию во время положительной полуволны. ТаКИМ образом, на входах суммирующего регистра 8 памяти одновременно имеется информация о j-й строке из элемента 7 задержки и информация о (J + 1)-й строке с второго выхода первого блока 4 коммутации. Управляющие сигналы на третьем, пятом и шестом входах (фиг.15 а, б, в),объединяясь на элементах ИЛИ 47 и 48 (фиг.5 г, д), посредством блока 49 разрешения записи разрешают запись в элемент 51 памяти (фиг.15 з), состоящий из набора триггеров 57.-1, по синхроимпульсу (фиг.15 и) четных отсчетов j-й строки и нечетных отсчетов (J + 1)-й строки (фиг.15 е,ж Одновременно комбинация на первом и втором управляющих входах третье- iго регистра 11 памяти, который состоит из четырех D-триггеров, позволит записать в него информацию о четырех старших разрядах нечетных отсчетов т-и строки. Информация с выхода суммирующего регистра 8 памяти

20 и 54-2 установки младших разрядов заведены на R-S-входы триггеров эле ментов 62-5 - 62-7 памяти через элементы ИЖ 64-1 - 64-6 .таким образом что при изменении старшего из изме- л-25

последовательно переписывается в пер- нившихся разрядов О младшие и наобовый и второй регистры g и 10 памя- 1 Ти, которые представляют собой ли- нейки D-триггеров. Таким образом, одновременно имеется информация о (i - 1)-ом отсчете j-й строки (второй регистр 10 памяти), i-ом отсчете (J + 1)-й строки (первый регистр 9 памяти), (i + 1)-м отсчете j-й строки (суммирующий регистр 8 памяти) , четырех старших разрядах i-ro отсчета j-й строки (третий регистр 11 памяти). Первьши выходами суммирующего (фиг.5 к), первого и второго регистров 8-10 памяти являются прямые выходы всех семи триггеров элементов памяти. Выходом третьего и вторым выходом суммирующего регистров 8 и 11 памяти являются прямые и инверсные выходы четырех старших разрядов, вторым выходом первого и второго регистров 9 и 10 памяти - инверсные выходы триггеров.

Элементы j-й строки передаются в канал связи через отсчет (четные отсчеты) информацией об истинных значениях четырех старших разрядов исходного кода вторым блоком 5 коммутации, второй вход которого соединен с вторым выходом второго регист30

ряды устанавливаются в рот.

Элементы (j + 1)-й строки переда ются в канал связи информацией зависящей от результатов сравнения. во втором, третьем, четвертом блоках 13 - 15 сравнения. Если на выхо де второго блока 13 сравнения, на первый и второй входы которого пода ны четыре старших разряда с выходов соответственно суммирующего и второго регистров 8 и 10 памяти - уровень логической единицы, что говорит о наличии изменений хотя бы в одном из четырех старших разрядов то в i-oM отсчете (j + 1)-й строки будет передана информация об истинном состоянии четырех разрядов не- ходного кода блоком 72 разрешения

45 второго блока 24 разрешения записи, выход которого соединен с четвертым входом второго блока 5 ком1 утации. Одновременно эта же информация запи сывается в элементы 62-1 - 62-А. па50 мяти через элементы ИЛИ 61 блока 21 памяти, а все более младшие разряды устанавливаются согласно алгоритму по цепи: блок 21 памяти - блок 20 управления памятью - блок 2-1 Ъа35

40

ра 10 памяти, посредством блоков 36, 55 мяти. Одновременно блок 25 пипотсигнала,на вход элементов ИЛИ-НЕ 7 76 которого поступает уровень логи ческой единицы (фиг.18 г) с выхода второго блока 13 сравнения, запи39, 40 и 41 выбора разрядов кода канала и блока 42 памяти кода канала. Одновременно эта информация через блок 68 совпадения (фиг.16 ж) перво856268

го блока 23 разрешения записи записывается через элементы ИЛИ 61 в элементы 62-1 - 62-4 памяти четырех старших разрядов кода блока 21 па- г мяти. Младшие разряды блока 21 памяти устанавливаются в соответствии с принятым алгоритмом элементами 54-1 - 54-2 установки младших разрядов блока 20 управления памятью.

10 Элементы 53-1 - 53-6 запрета выбирают самый старший из разрядов, в котором произошло изменение при записи четырех старших разрядов кода, для чего выходы элементов 62-1 15 62-4 памяти блока 21 памяти дифференцируются цифровыми дифференцирующими цепочками 63-1 и 63-2 и подаются на входы элементов 53-1 - 53-6 запрета. Выходы элементов 54-1

20 и 54-2 установки младших разрядов заведены на R-S-входы триггеров элементов 62-5 - 62-7 памяти через элементы ИЖ 64-1 - 64-6 .таким образом, что при изменении старшего из изме- 25

нившихся разрядов О младшие и наобо

ряды устанавливаются в рот.

Элементы (j + 1)-й строки передаются в канал связи информацией зависящей от результатов сравнения. во втором, третьем, четвертом блоках 13 - 15 сравнения. Если на выходе второго блока 13 сравнения, на первый и второй входы которого поданы четыре старших разряда с выходов соответственно суммирующего и второго регистров 8 и 10 памяти - уровень логической единицы, что говорит о наличии изменений хотя бы в одном из четырех старших разрядов, то в i-oM отсчете (j + 1)-й строки будет передана информация об истинном состоянии четырех разрядов не- ходного кода блоком 72 разрешения

второго блока 24 разрешения записи, выход которого соединен с четвертым входом второго блока 5 ком1 утации. Одновременно эта же информация записывается в элементы 62-1 - 62-А. памяти через элементы ИЛИ 61 блока 21 памяти, а все более младшие разряды устанавливаются согласно алгоритму по цепи: блок 21 памяти - блок 20 управления памятью - блок 2-1 Ъа

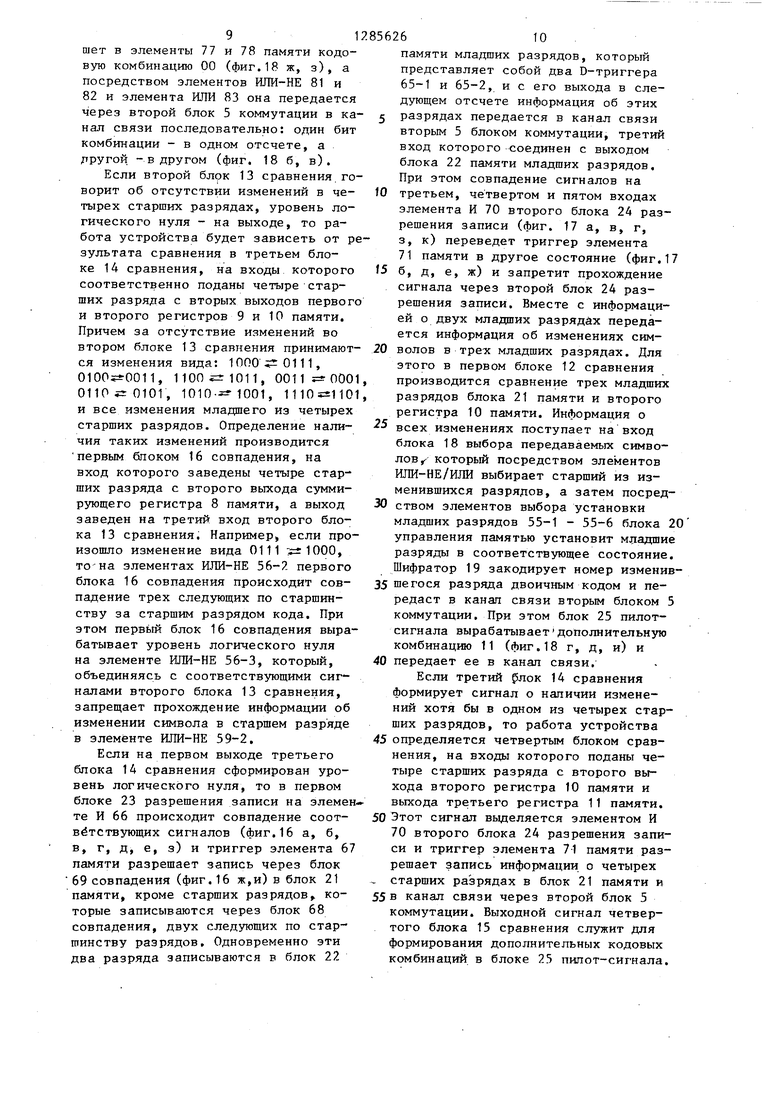

мяти. Одновременно блок 25 пипотсигнала,на вход элементов ИЛИ-НЕ 74,76 которого поступает уровень логической единицы (фиг.18 г) с выхода второго блока 13 сравнения, запишет в элементы 77 и 78 памяти кодовую комбинацию 00 (фиг.18 ж, з), а посредством элементов ШШ-НЕ 81 и 82 и элемента ИЛИ 83 она передается через второй блок 5 коммутации в канал связи последовательно: один бит комбинации - в одном отсчете, а другой - в другом (фиг. 18 б, в).

Если второй блок 13 сравнения говорит об отсутствии изменений в четырех старших разрядах, уровень логического нуля - на выходе, то работа устройства будет зависеть от результата сравнения в третьем блоке 14 сравнения, на входы которого соответственно поданы четыре старших разряда с вторых выходов первого и второго регистров 9 и 10 памяти. Причем за отсутствие изменений во втором блоке 13 сравнения принимаются изменения вида: , , , , , 1010- 1001, , и все изменения младшего из четырех старших разрядов. Определение наличия таких изменений производится первым блоком 16 совпадения, на вход которого заведены четыре старших разряда с второго выхода суммирующего регистра В памяти, а выход заведен на третий вход второго блока 13 сравнения. Например, если произошло изменение вида 0111 т ггЮОО, ТО на элементах ИЛИ-НЕ 56-7. первого блока 16 совпадения происходит совпадение трех следующих по старшинству за старшим разрядом кода. При этом первый блок 16 совпадения вырабатывает уровень логического нуля на элементе ИЛИ-НЕ 56-3, который, объединяясь с соответствующими сигналами второго блока 13 сравнения, запрещает прохождение информации об изменении символа в старшем разряде в элементе ИЛИ-НЕ 59-2.

Если на первом выходе третьего блока 14 сравнения сформирован уровень логического нуля, то в первом блоке 23 разрешения записи на элементе И 66 происходит совпадение соотетствующих сигналов (фиг.16 а, б, , г, д, е, з) и триггер элемента 67 памяти разрешает запись через блок 69 совпадения (фиг.16 ж,и) в блок 21 амяти, кроме старших разрядов которые записываются через блок 68 совпадения, двух следующих по старинству разрядов. Одновременно эти ва разряда записываются в блок 22

памяти младших разрядов, который представляет собой два D-триггера 65-1 и 65-2, и с его выхода в следующем отсчете информация об этих

разрядах передается в канал связи вторым 5 блоком коммутации, третий вход которого соединен с выходом блока 22 памяти младших разрядов. При этом совпадение сигналов на

третьем, четвертом и пятом входах элемента И 70 второго блока 24 разрешения записи (фиг. 17 а, в, г, 3, к) переведет триггер элемента 71 памяти в другое состояние (фиг.17

б, д, е, ж) и запретит прохождение сигнала через второй блок 24 разрешения записи. Вместе с информацией о двух младших разрядах передается информация об изменениях символов в трех младших разрядах. Для этого в первом блоке 12 сравнения производится сравнение трех младших разрядов блока 21 памяти и второго регистра 10 памяти. Информация о

всех изменениях поступает на вход блока 1В выбора передаваемых символов, который посредством элементов ИЛИ-НЕ/ИЛИ выбирает старший из изменившихся разрядов, а затем посредством элементов выбора установки

младших разрядов 55-1 - 55-6 блока 20 управления памятью установит младшие разряды в соответствующее состояние. Шифратор 19 закодирует номер изменившегося разряда двоичным кодом и передаст в канал связи вторым блоком 5 коммутации. При этом блок 25 пилот- сигнала вырабатываетдополнительную комбинацию 11 (фиг.18 г, д, и) и

передает ее в канал связи.

Если третий 5лок 14 сравнения формирует сигнал о наличии изменений хотя бы в одном из четырех старших разрядов, то работа устройства

определяется четвертым блоком сравнения, на входы которого поданы четыре старших разряда с второго выхода второго регистра 10 памяти и выхода третьего регистра 11 памяти.

Этот сигнал выделяется элементом И 70 второго блока 24 разрешения записи и триггер элемента 71 памяти разрешает запись информации о четырех

старших разрядах в блок 21 памяти и

в канал связи через второй блок 5 коммутации. Выходной сигнал четвертого блока 15 сравнения служит для формирования дополнительных кодовых комбинаций в блоке 25 пилот-сигнала.

111

Если четвертый блок 15 сравнения формирует сигнал о наличии изменений символов, причем так же, как и во втором блоке 13 сравнения, часть изменений запрещается вторьм блоком 17 совпадения, то вырабатывается дополнительная кодовая комбинация 10 (фиг.18 а, г, д, е, ж),

В противном случае вырабатывается дополнительная кодовая комбинация 01 Вся информация, поступающая на входы второго блока 5 коммутации, записывается в блок 42 памяти кода канала и с его выхода считывается на выход устройства.

Формула изобретения

Устройство для сжатия цифрового телевизионного сигнала, содержащее последовательно соединенные аналого- цифровой преобразователь, формирова - тель интервалов времени, первый блок коммутации, элемент задержки, суммирующий регистр памяти, первьй регистр памяти, второй регистр памяти, первый блок сравнения, блок выбора передаваемых символов, шифратор и второй блок коммутации, последовательно соединенные блок управления памятью, вход которого соединен с вторым выходом блока выбора передаваемых символов и блок памяти, выход которого соединен с вторым входом первого блока сравнения, последова- тельно соединенные второй блок сравнения, первый вход которого соединен с вторым выходом суммирующего регистра памяти, а второй вход соединен с вторьм выходом второго регистра па мяти, первый блок разрешения записи и блок памяти младших разрядов, выход которого соединен с вторым входо второго блока коммутации, последовательно соединенные блок установки опорного уровня, вход которого объединен с входом аналого-цифрового преобразователя, и формирователь кода синхронизации, выход которого соединен с вторым входом шифратора, последовательно соединенные третий блок сравнения, первый вход которого соединен с вторым выходом второго регистра памяти, а второй вход соединен с вторым выходом первого регистра памяти, и второй блок разрешения записи, выход которого соединен с вторым входом блока памяти и с третьим входом второго блока комму

26

12

5

5

0 5 О 5 0 5

0

тации, последовательно соединенные третий регистр памяти, первый вход которого соединен с вторым выходом первого блока коммутации, и четвертый блок сравнения, второй вход которого объединен с четвертым входом второго блока коммутации, с вторыми входами второго блока сравнения, первого и второго блоков разрешения записи и соединен с вторым выходом второго регистра памяти и блок пилот-сигнала, первый и второй входы которого соединены с первым выходом третьего и с выходом четвертого блоков сравнения соответственно- - а выход соединен с пятым входом второго блока коммутации, шестой вход которого соединен с вторым выходом формирователя интервалов времени, при этом выход блока установки опорного уровня соединен с вторым входом формирователя интервалов времени, второй выход аналого-цифрового преобразователя соединен с вторым входом первого блока коммутации, третий выход которого соединен с

.вторым входом суммирующего регистра памяти, выход второго блока сравнения подключен к третьим входам второго блока разрешения записи и блока пилот-сигнала, второй выход третьего блока сравнения соединен с третьим входом первого блока разрешения записи, а третий, четвертый и пятый входы блока памяти соединены с выходом блока установки опорного уровня, с вторым и первым выходами первого блока разрешения записи соответственно, а второй выход блока памяти соединен с вторым входом блока управления памятью, о т л и .чающееся тем, что, с целью уменьшения искажения цифрового телевизионного сигнала, введены первый блок совпадения, вход которого .соединен с вторым выходом суммирующего регистра памяти, а выход соеди нен с третьим входом второго блока сравнения, и второй блок совпадения, вход которого соединен с выходом третьего регистра памяти, а выход соединен с третьим входом четвертого блока сравнения, при этом седьмой вход второго блока коммутации объединен с четвертыми входами первого блока разрешения записи и блока пилот-сигнала и соединен с третьим выходом формирователя интервалов времени, восьмой вход второго бло13

ка коммутации объединен с вторым входом третьего регистра памяти, с четвертым входом второго блока разрешения записи, с третьим входом суммирующего регистра памяти и соединен с четвертым выходом формирователя интервалов времени, второй вход элемента задержки соединен с . выходом аналого-цифрового преобразователя, третий вход объединен с первым входом первого блока коммутации, а четвертый вход соединен с выходом блока установки опорного уровня, четвертый вход суммирующего регистра памяти объединен с третьим входом третьего регистра памяти и соединен с вторым выходом формирователя интервалов времени, пятый вход объединен с четвертым входом третьего регистра памяти и соединен с пятым выходом формирователя интервалор воемени, третий выход которого соКсинхроКходом 5мко6

кю КЗ к,б,11 щгг нгз.2.25

562614

единен с шестым входом суммирующего регистра памяти , второй вход первого регистра памяти соединен с шестым выходом формирователя интервалов времени, второй вход второго регистра

памяти соединен с седьмым выходом формирователя интервалов времени, шестой вход блока памяти объединен с вторым входом блока памяти младших разрядов и соединен с восьмым выходом формирователя интервалов времени, девятый выход которого соединен с пятыми входами первого и второго блоков разрешения записи и

блока пилот-сигнала, шестой вход которого объединен с шестыми входами первого и второго блоков разрешения записи и соединен с десятым выходом формирователя интервалов времени,

третий выход которого соединен с третьим входом блока памяти младших разрядов.

Токт.&1. УетГ

S С

CSi. S с

ltU 1

До QiHtU Csui.

gg ОУ Qt QjCfM

Упр.

g У1 А1АгАЗА А5АВА7А8АЗАЮ 45

сел. s с

44-f

4-J

go gi

Т

0й г .5

фиг.В

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для кодирования телевизионных сигналов | 1986 |

|

SU1356259A1 |

| Устройство для сжатия цифровых телевизионных сигналов | 1982 |

|

SU1059702A1 |

| Устройство для сжатия цифровых телевизионных сигналов | 1984 |

|

SU1243159A2 |

| Устройство для сжатия цифровых телевизионных сигналов | 1984 |

|

SU1238268A2 |

| Устройство для сжатия цифровых телевизионных сигналов | 1980 |

|

SU944145A1 |

| Устройство стабилизации уровня видеосигнала | 1987 |

|

SU1406822A1 |

| Устройство для ввода аналоговой информации | 1986 |

|

SU1377848A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1991 |

|

SU1807516A1 |

| Устройство для гистограммной обработки изображений объектов | 1989 |

|

SU1667106A1 |

| Устройство для разделения коррелограмм | 1987 |

|

SU1432558A1 |

Изобретение обеспечивает уменьшение искажений телевизионного сигнала (ТВС). Устройство содержит блок 1 установки опорного уровня, АЦП 2, формирователь 3 интервалов времени, блоки 4 и 5 коммутации, формирователь 6 кода синхронизации, элемент 7 задержки, суммирующий регистр 8 . СП ГчЭ оо 01 О5 го О5

.

г-г 72-3 i-T-o-i -r: C J J

I 78-r I7g-2 I

HJ 5J-j| I fj- I I -j

I I I T

Л-/W-/

5J-/ Я- 55-J

0

j-(f

r .1 J 1

f3

57-г

yiJ Iji

УстСинжр-f У

11

57-4 -P-O-J

H

(pw.5

1IL

fIT

nrnnn

ffff-f I I 5ff-/ . I so-3 I k/;-« .

Sf-t

Ш-.

ffO-S

II II

nil 4,|i i

w «

Sf-S

fff-e

ffO-S

II II

ff.

f/

фиг. 9

Ci/HJTp.

10

lynft. Citmft. SyipSynfдд

V V 1

г

S9

Citmft. SyipSynf

дд

CiJ

пг

фиг.12

Уст Synp. Купр.

Sy/Tf ir

1Упр.

/%

5

rvj

%7/.

вшА7

г

быкМ д

J/r. е

ffgx ж

вш49

3

Синхр и

Вык51 к

..J

.п I I I I I I I I I II

..J

фуг./5

| Устройство для сжатия цифровых телевизионных сигналов | 1982 |

|

SU1059702A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-01-23—Публикация

1985-05-21—Подача