рующий регистр 7 памяти (РП), РП 8 - ill, блоки IS-16 сравнения, блок 17 выбора передаваемых символов, блок 18 управления памятью, блоки 19 и 26 памяти (БП), шифратор 20, блоки 21,

22и 25 разрешения записи (БРЗ), БП

23младших разрядов и блок 24 пилот- сигнала. Цель достигается введением РП 11, БРЗ 25 и БП 26, с помощью которых пе зедаваемая на выход устройст

Изобретение относится к технике телевидения и может быть использовано для кодирования телевизионных сигналов.

Цель изобретения - увеличение объ- ема кодируемой информации.

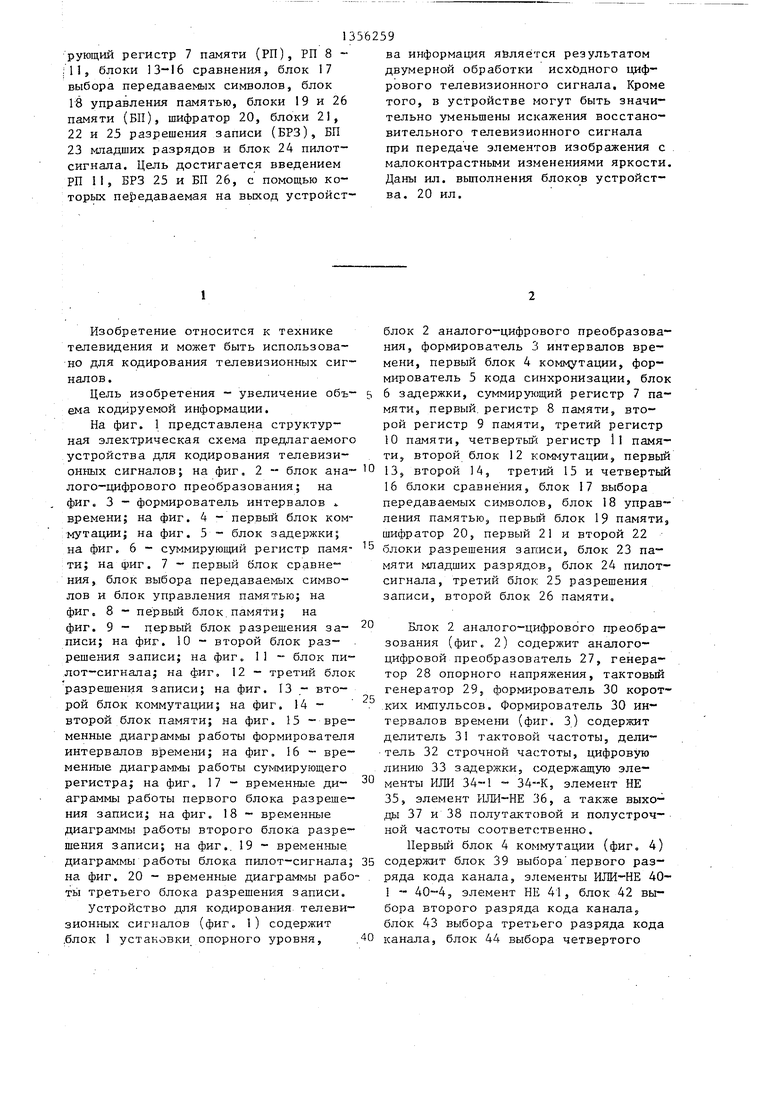

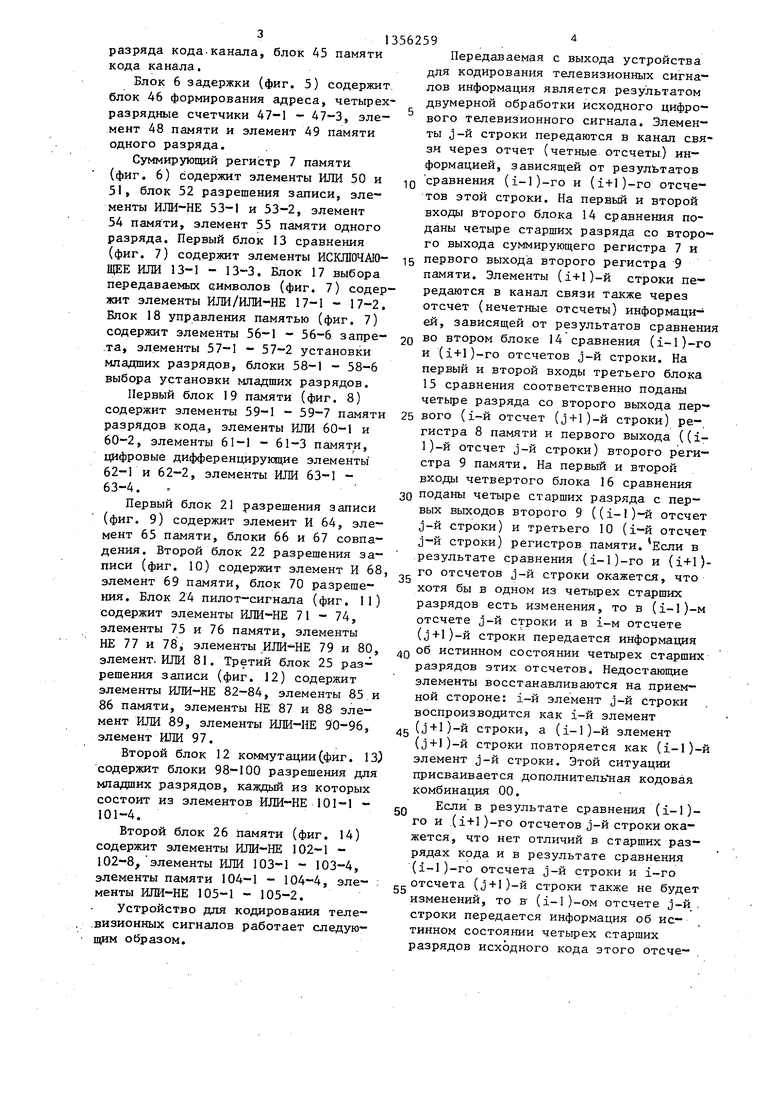

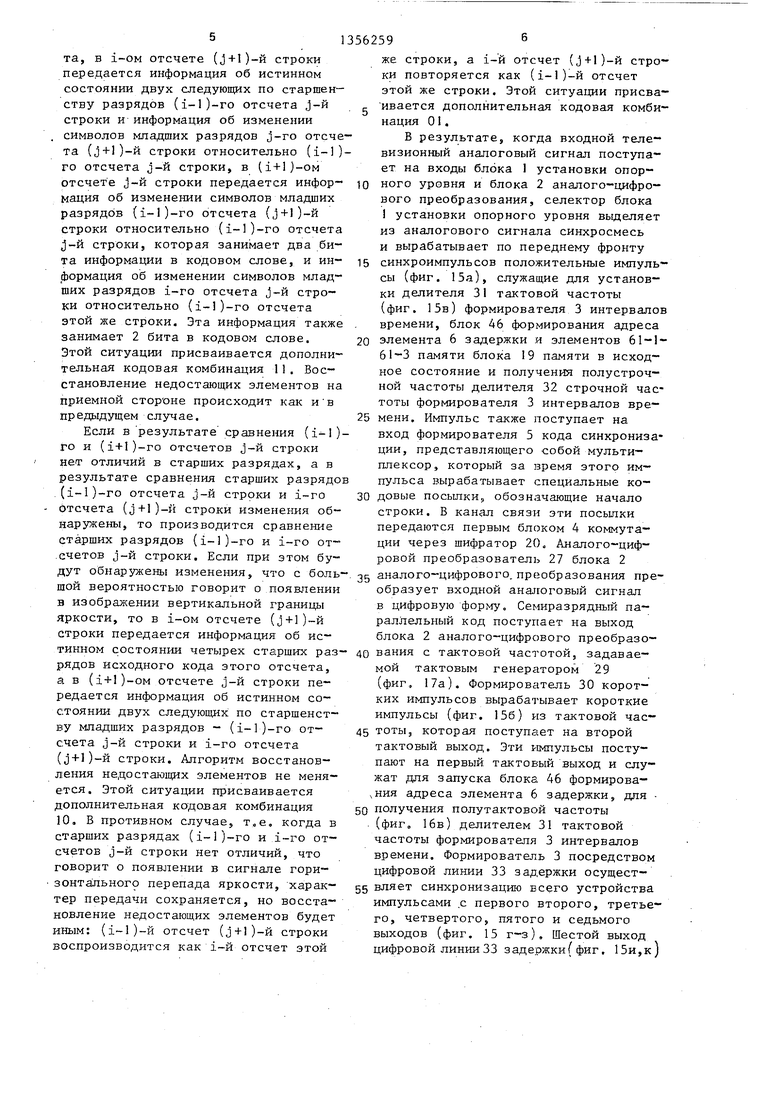

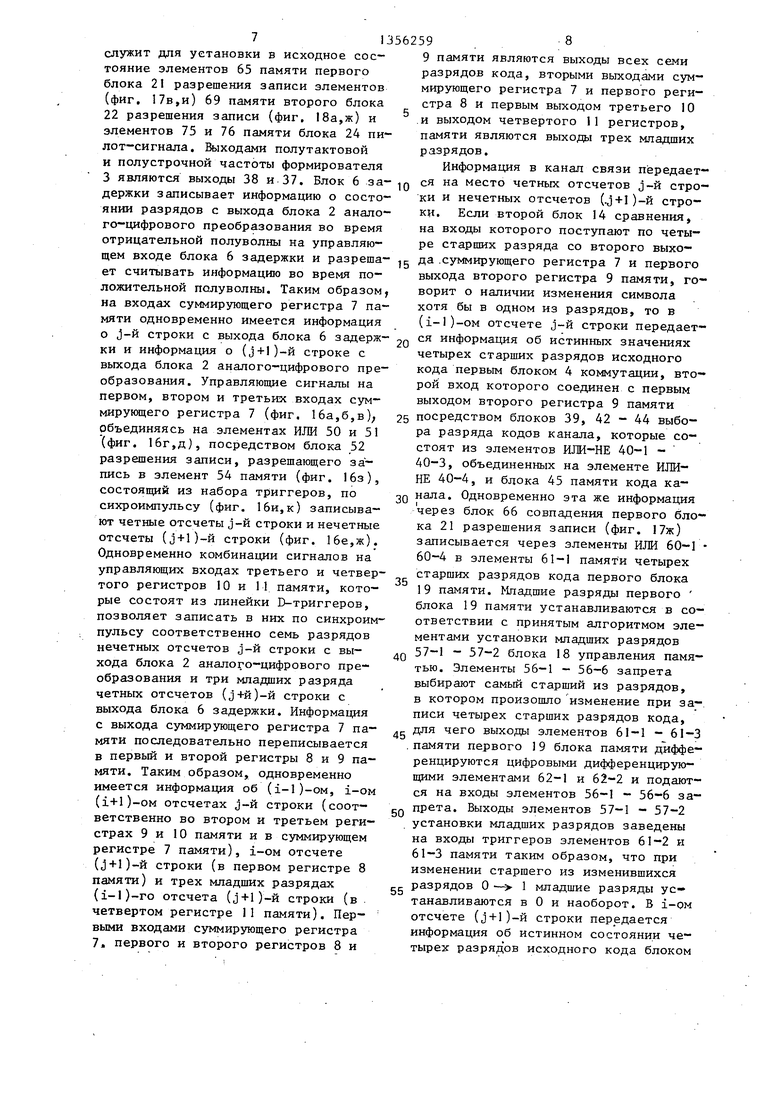

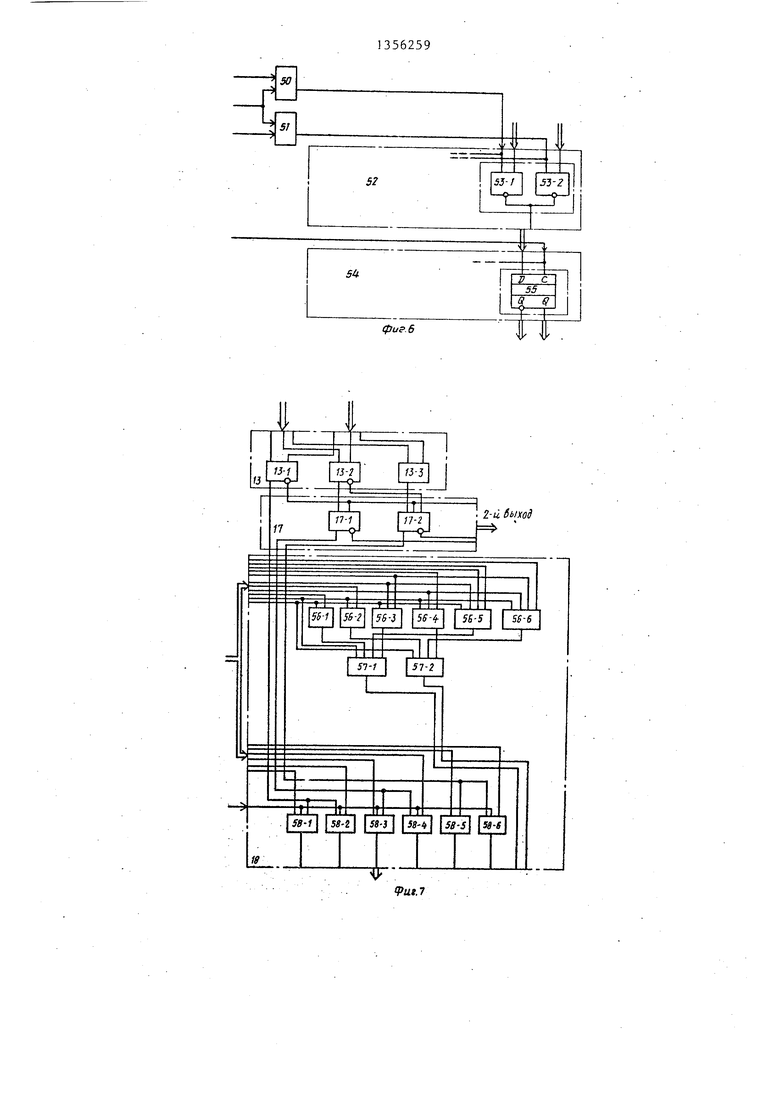

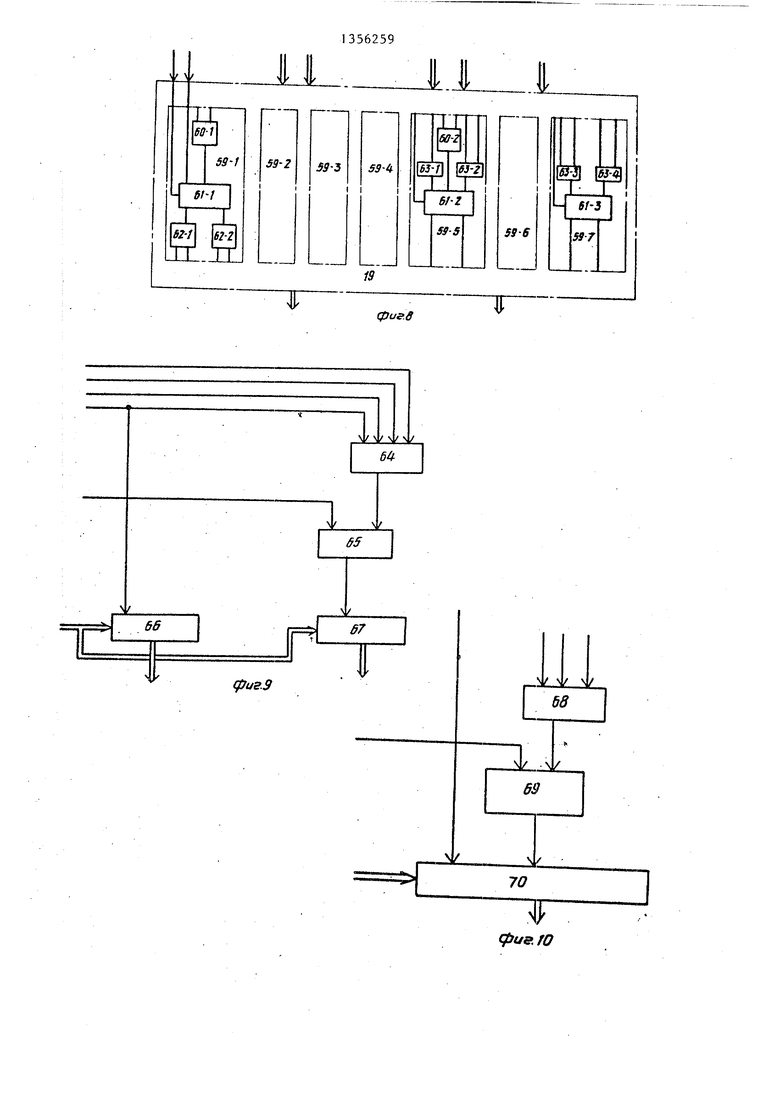

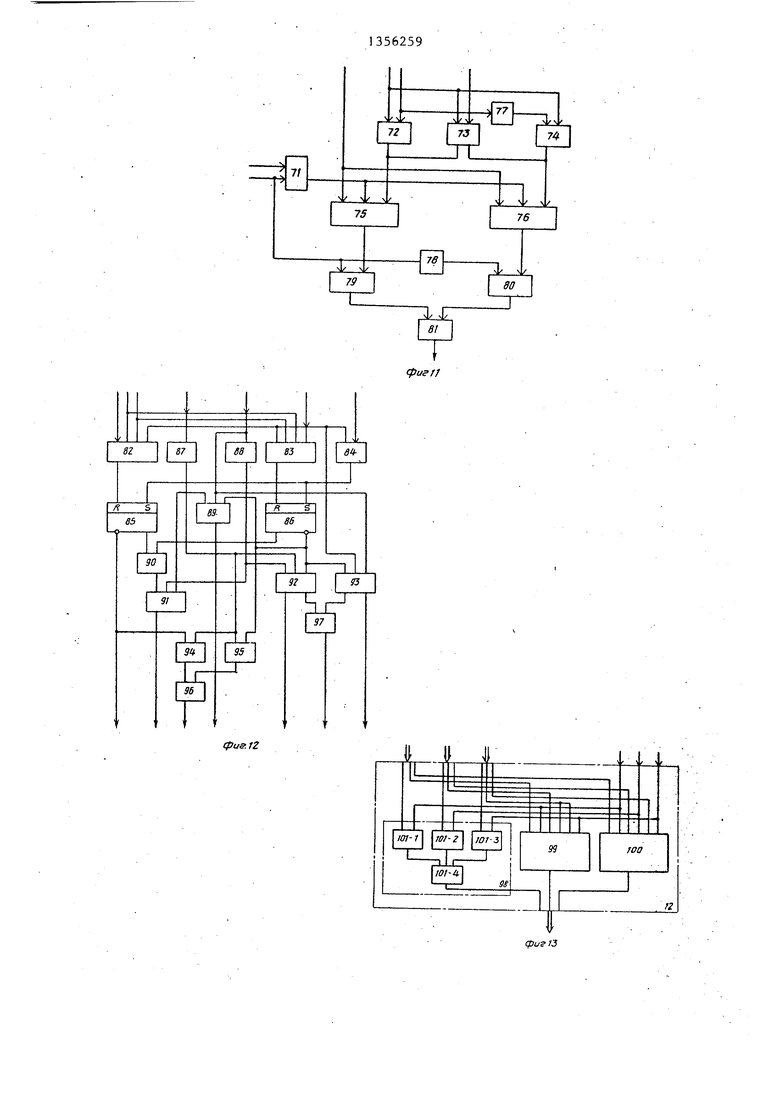

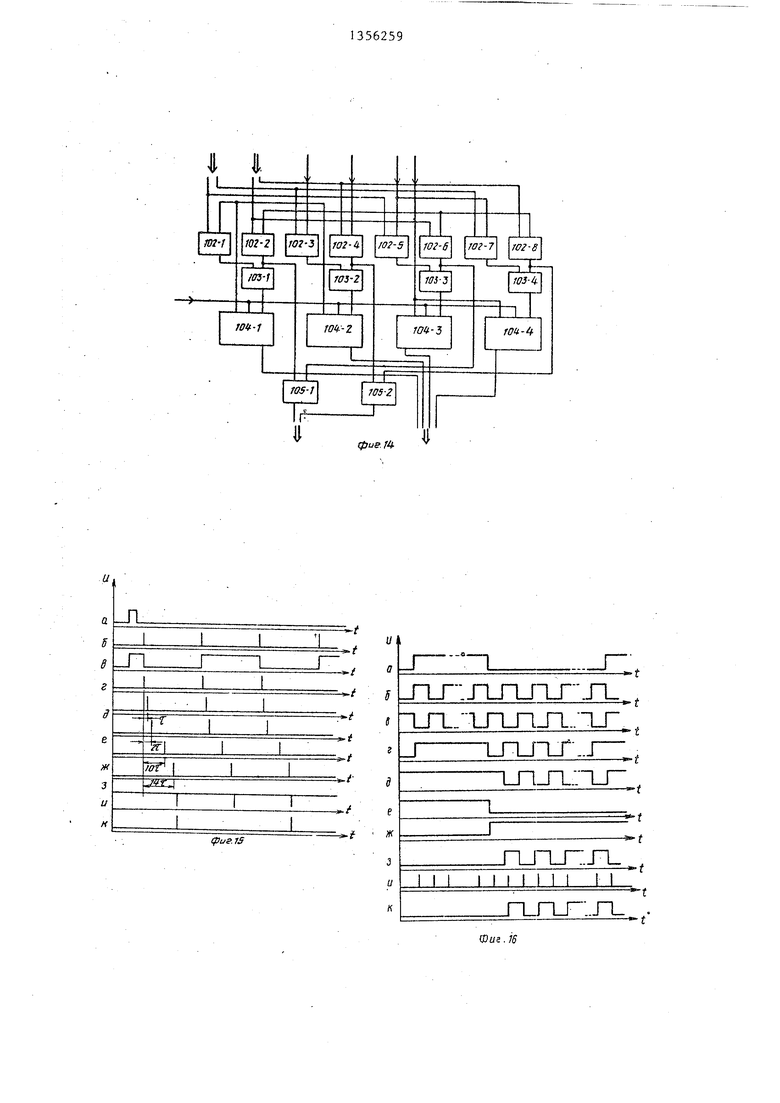

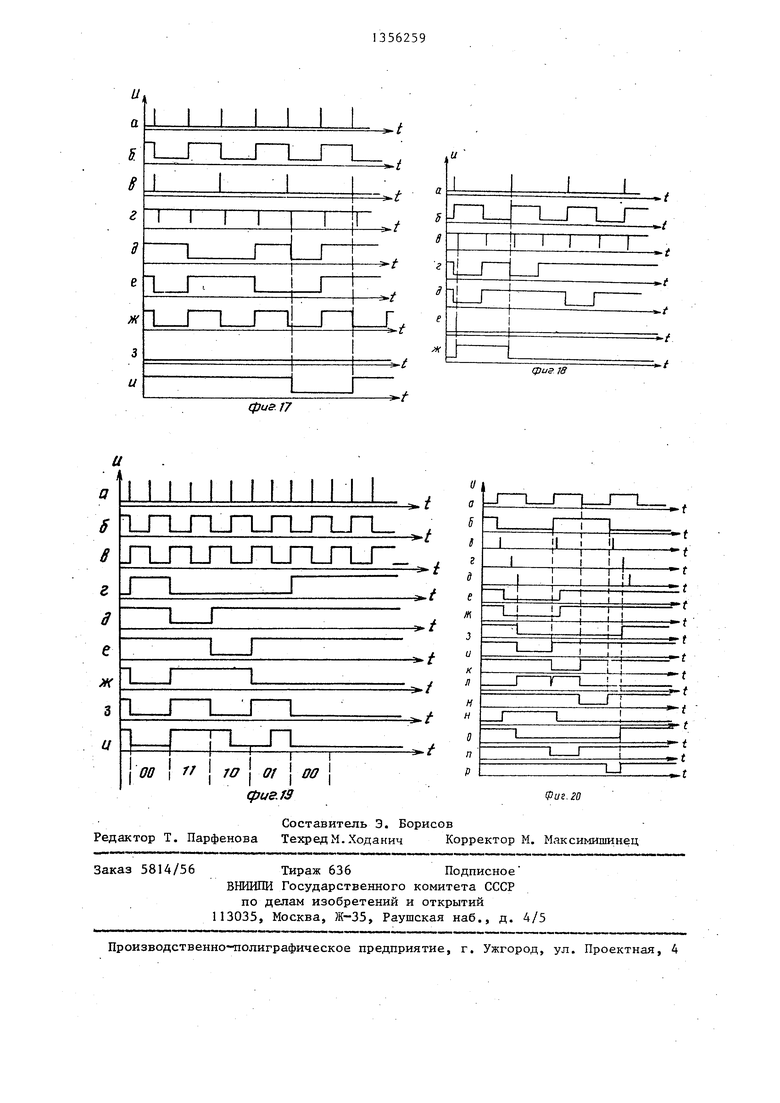

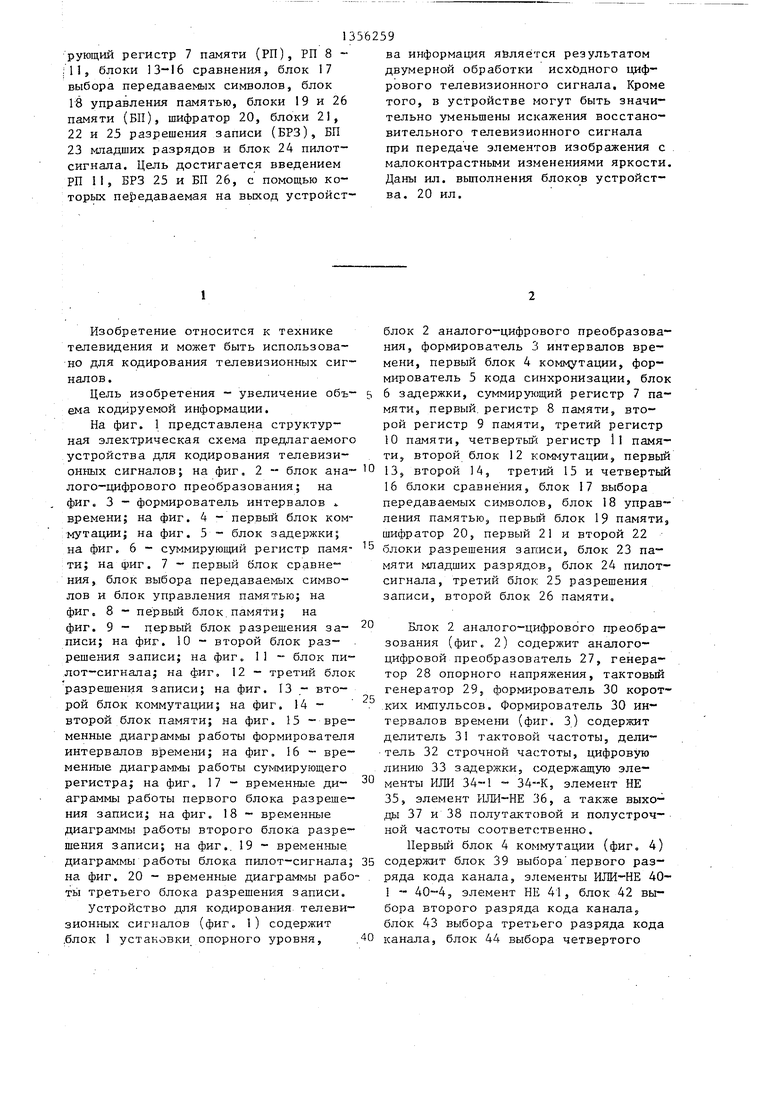

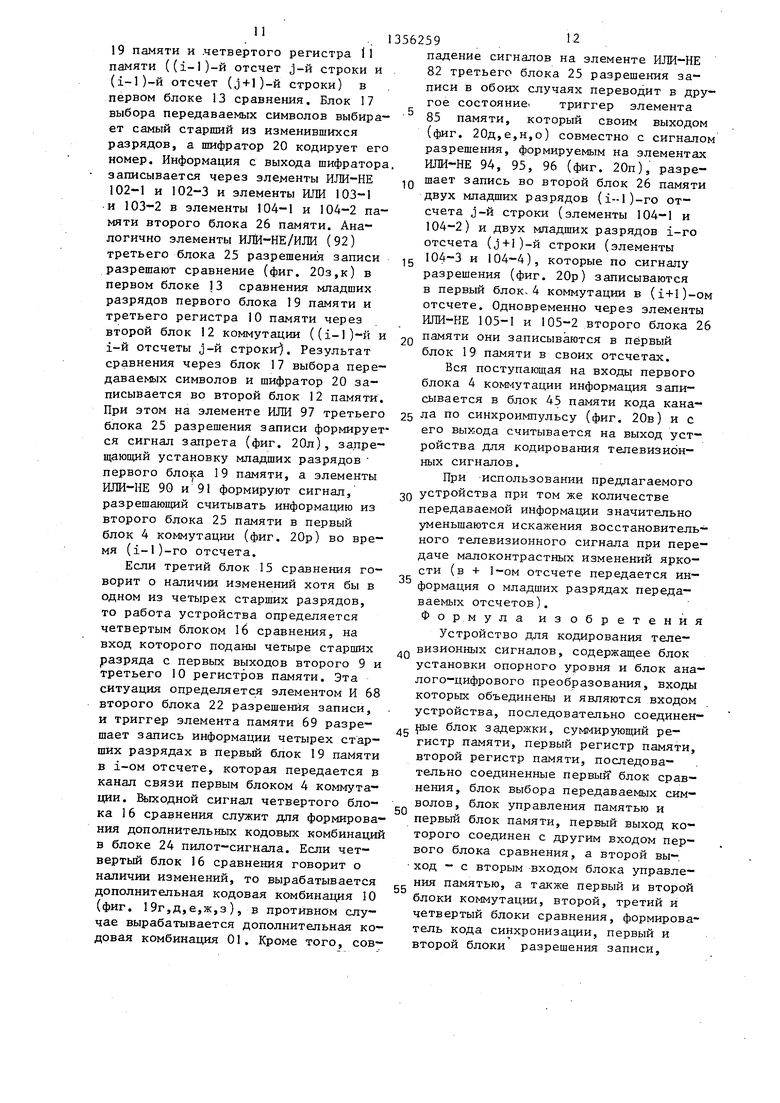

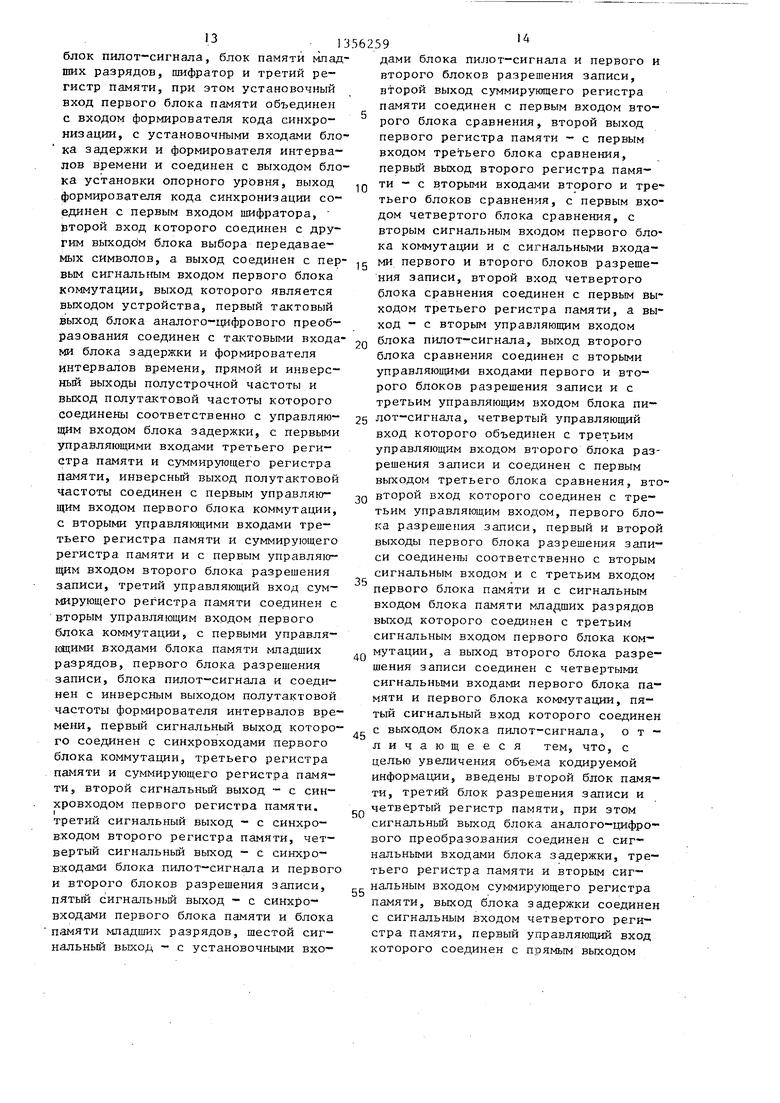

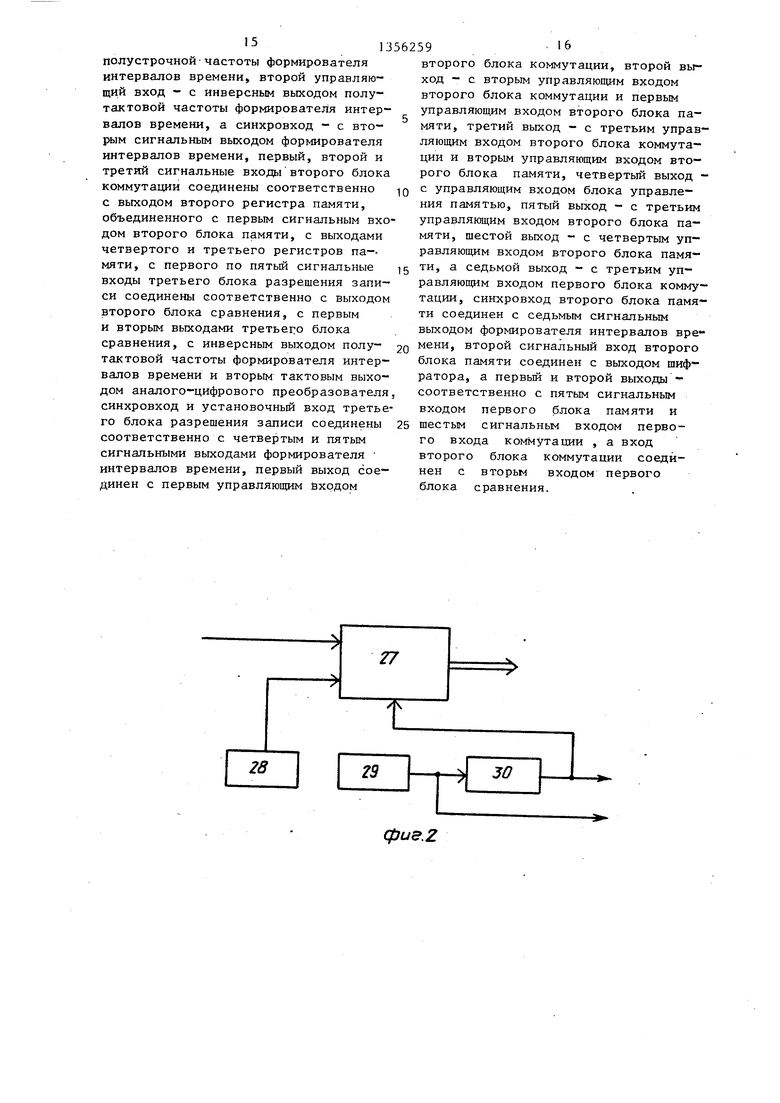

На фиг. 1 представлена структурная электрическая схема предлагаемого устройства для кодирования телевизионных сигналов; на фиг. 2 - блок ана лого-цифрового преобразования; на фиг. 3 - формирователь интервалов времени; на фиг. 4 - первый блок коммутации; на фиг. 5 - блок задержки; на фиг, 6 - суммирующий регистр памя- ти; на фиг. 7 - первый блок сравнения, блок выбора передаваемых символов и блок управления памятью; на фиг 8 - первый блок,памяти; на фиг. 9 - первый блок разрешения за- писи; на фиг. 10 - второй блок раз- решения записи; на фиг. I1 - блок пилот-сигнала; на фиг, 12 - третий блок разрешения записи; на фиг. 13 - второй блок коммутации; на фиг. 14 - второй блок памяти; на фиг. 15 - временные диаграммы работы формирователя интервалов времени; на фиг, 16 - временные диаграммы работы суммирующего регистра; на фиг. 17 - временные ди- аграммы работы первого блока разрешения записи; на фиг. 18 - временные диаграммы работы второго блока разрешения записи; на фиг.. 19 - временные диаграммы работы блока пилот-сигнала; на фиг. 20 - временные диаграммы рабо ты третьего блока разрешения записи.

Устройство для кодирования телевизионных сигналов (фиг о 1) содержит .блок 1 установки опорного уровня,

56259

на информация является результатом двумерной обработки исходного цифрового телевизионного сигнала. Кроме того, в устройстве могут быть значительно уменьшены искажения восстановительного т(1левизионного сигнала при передаче элементов изображения с малоконтрастными изменениями яркости. Даны ил. выполнения блоков устройства. 20 ил.

5 0 5 .

5

блок 2 аналого-цифрового преобразования, формирователь 3 интервалов времени, первый блок 4 коммутации, формирователь 5 кода синхронизации, блок 6 задержки, суммирующий регистр 7 памяти, первый, регистр 8 памяти, второй регистр 9 памяти, третий регистр 10 памяти, четвертый регистр 11 памяти, второй блок 12 коммутации, первый 13, второй 14, третий 15 и четвертый 16 блоки сравнения, блок 17 выбора передаваемых символов, блок 18 управления памятью, первьй блок 19 памяти, шифратор 20, первый 21 и второй 22 блоки разрешения записи, блок 23 памяти младших разрядов, блок 24 пилот- сигнала, третий блок 25 разрешения записи, второй блок 26 памяти.

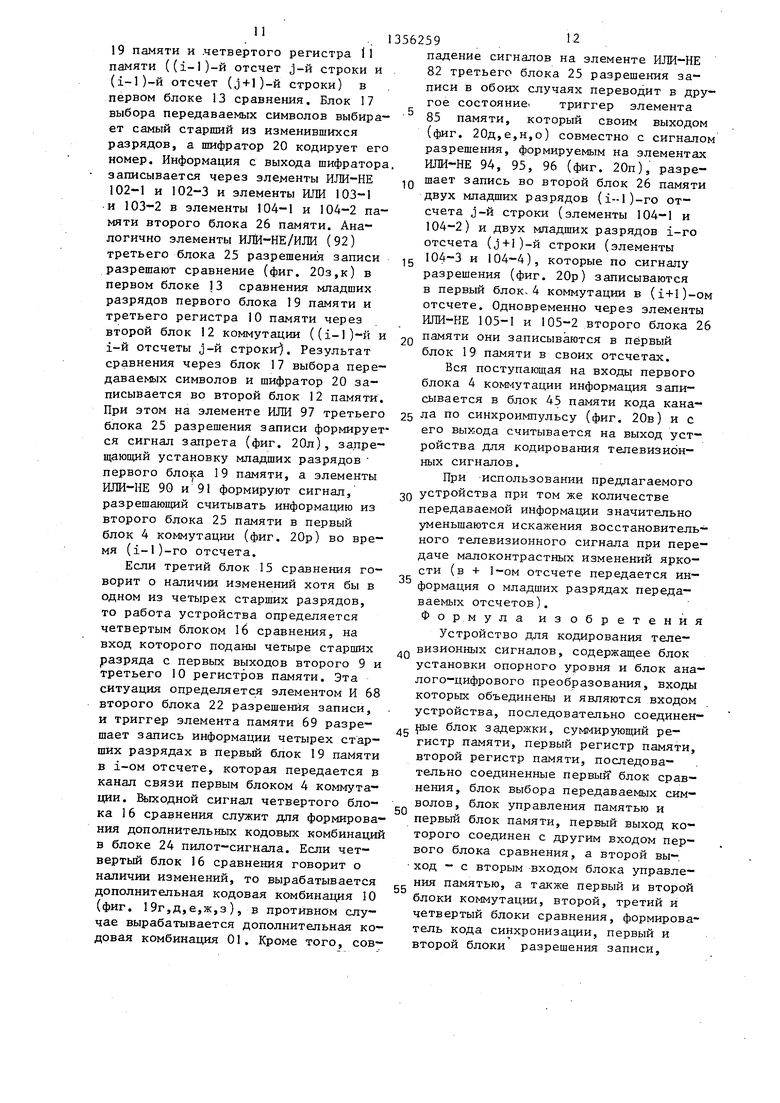

Блок 2 ангшого-цифрового преобразования (фиг. 2) содержит аналого- цифровой преобразователь 27, генератор 28 опорного напряжения, тактовый генератор 29, формирователь 30 корот- .ких импульсов. Формирователь 30 интервалов времени (фиг. 3) содержит делитель 31 тактовой частоты, дели- тель 32 строчной частоты, цифровую линию 33 задерж:ки, содержащую элементы ИЛИ 34-1 - 34--К, элемент НЕ 35, элемент ИЛИ-НЕ 36, а также выходы 37 и 38 полутактовой и полустроч- ной частоты соответственно.

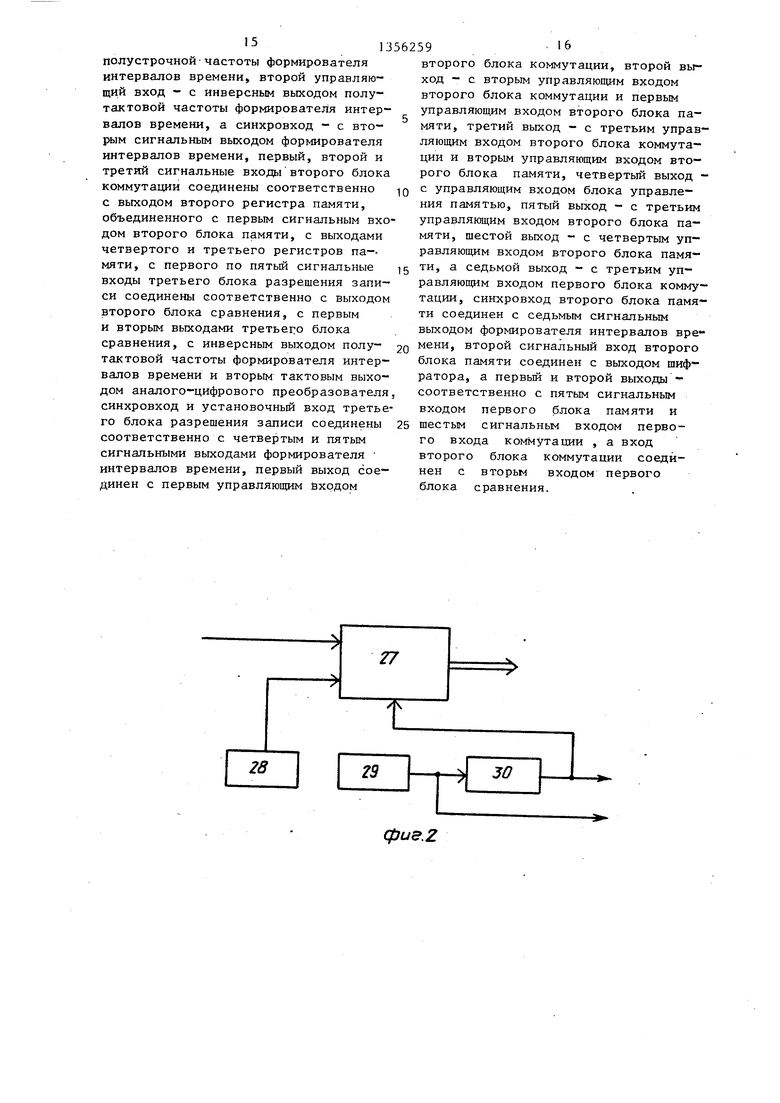

Первый блок 4 коммутации (фиг. 4) содержит блок 39 выбора первого разряда кода канала, элементы ИЛИ-НЕ 40- 1 - 40-4, элемент НЕ 41, блок 42 выбора второго разряда кода канала, блок 43 выбора третьего разряда кода канала, блок 44 выбора четвертого

разряда кода-канала, блок 45 памяти кода канала.

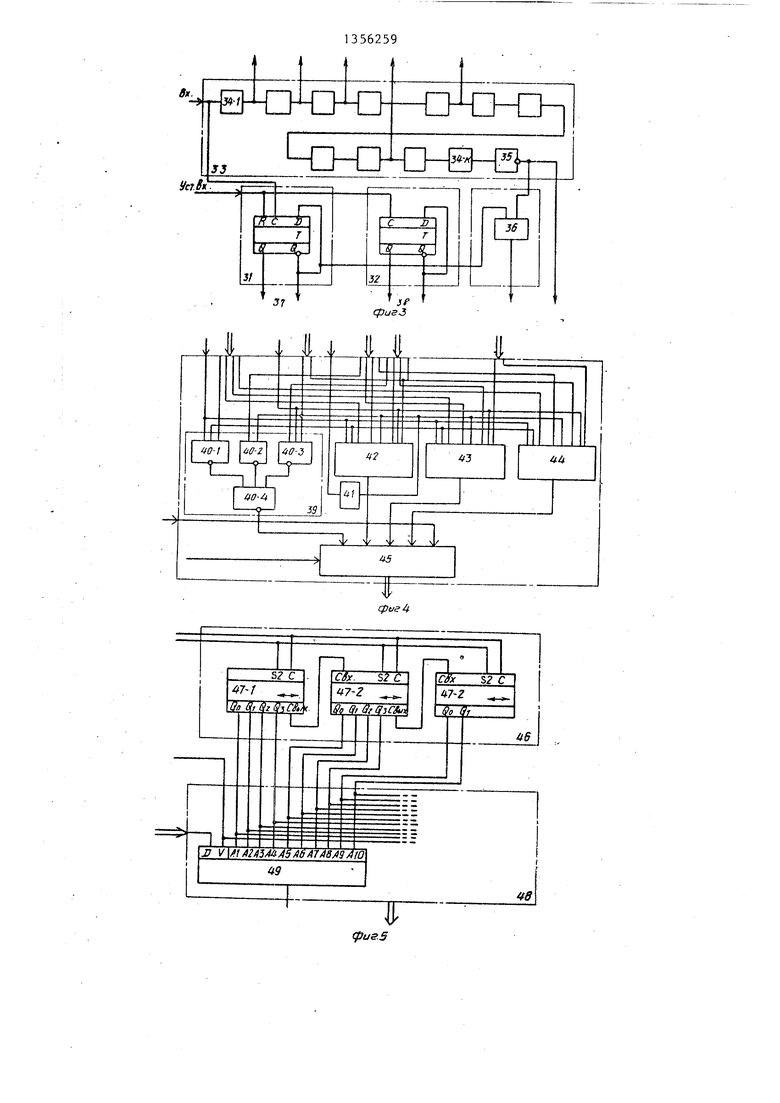

Блок 6 задержки (фиг. 3) содержит. блок 46 формирования адреса, четырехразрядные счетчики 47-1 - 47-3, элемент 48 памяти и элемент 49 памяти одного разряда.

Суммирующий регистр 7 памяти {фиг. 6) содержит элементы ИЛИ 50 и 51, блок 52 разрешения записи, элементы ИЛИ-НЕ 53-1 и 53-2, элемент 54 памяти, элемент 55 памяти одного разряда. Первый блок 13 сравнения (фиг. 7) содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 13-1 - 13-3. Блок 17 выбора передаваемых символов (фиг. 7) содержит элементы ИЛИ/ШШ-НЕ 17-1 - 17-2. Впок 18 управления памятью (фиг. 7) содержит элементы 56-1 - 56-6 запре- .та, элементы 57-1 - 57-2 установки младших разрядов, блоки 58-1 - 58-6 выбора установки младших разрядов.

Первый блок 19 памяти (фиг, 8)

10

15

20

Передаваемая с выхода устройства для кодирования телевизионных сигналов информация является результатом двумерной обработки исходного цифрового телевизионного сигнала. Элементы j-й строки передаются в канал связи через отчет (четные отсчеты,) информацией, зависящей от результатов сравнения (i-l)-ro и (i+l)-ro отсчетов этой строки. На первый и второй входы второго блока 14 сравнения поданы четыре старших разряда со второго выхода суммирующего регистра 7 и первого выхода второго регистра 9 памяти. Элементы (1+1)-й строки передаются в канал связи также через отсчет (нечетные отсчеты) информаци- ей, зависящей от результатов сравнени во втором блоке 14 сравнения (i-l)-ro и (i+l)-ro отсчетов j-й строки. На первый и второй входы третьего блока 15 сравнения соответственно поданы четыре разряда со второго выхода персодержит элементы 59-1 - 59-7 памяти 25 вого (i-й отсчет (j+l)-й строки) реразрядов кода, элементы ИЛИ 60-1 и 60-2, элементы 61-1 - 61-3 памяти, цифровые дифференцирующие элементы 62-Ги 62-2, элементы ИЛИ 63-1 - 63-4.

Первый блок 21 разрешения записи (фиг. 9) содержит элемент И 64, элемент 65 памяти, блоки 66 и 67 совпадения. Второй блок 22 разрешения записи (фиг. 10) содержит элемент И 68 элемент 69 памяти, блок 70 разрешения. Блок 24 пилот-сигнала (фиг. 11) содержит элементы ИЛИ-НЕ 71 - 74, элементы 75 и 76 памяти, элементы НЕ 77 и 78, элементы ИЛИ--НЕ 79 и 80, элемент-ИЛИ 81. Третий блок 25 разрешения записи (фиг. 12) содержит элементы ИЛИ-НЕ 82-84, элементы 85 и 86 памяти, элементы НЕ 87 и 88 элемент ИЛИ 89, элементы ИЛИ-НЕ 90-96, элемент ИЛИ 97.

Второй блок 12 коммутации(фиг. 13 содержит блоки 98-100 разрешения для младших разрядов, каждьй из которых состоит из элементов ИЛИ-НЕ 101-1 - 101-4.

Второй блок 26 памяти (фиг. 14) содержит элементы ИЛИ-НЕ 102-1 - 102-8, элементы ИЛИ 103-1 - 103-4, элементы памяти 104-1 - 104-4, эле- менты ИЛИ-НЕ 105-1 - 105-2.

Устройство для кодирования теле- .визионных сигналов работает следующим образом.

5

0

Передаваемая с выхода устройства для кодирования телевизионных сигналов информация является результатом двумерной обработки исходного цифрового телевизионного сигнала. Элементы j-й строки передаются в канал связи через отчет (четные отсчеты,) информацией, зависящей от результатов сравнения (i-l)-ro и (i+l)-ro отсчетов этой строки. На первый и второй входы второго блока 14 сравнения поданы четыре старших разряда со второго выхода суммирующего регистра 7 и первого выхода второго регистра 9 памяти. Элементы (1+1)-й строки передаются в канал связи также через отсчет (нечетные отсчеты) информаци- ей, зависящей от результатов сравнения во втором блоке 14 сравнения (i-l)-ro и (i+l)-ro отсчетов j-й строки. На первый и второй входы третьего блока 15 сравнения соответственно поданы четыре разряда со второго выхода пергистра 8 памяти и первого выхода ((i- 1)-й отсчет j-й строки) второго регистра 9 памяти. На первый и второй входы четвертого блока 16 сравнения

0 поданы четыре старших разряда с первых выходов второго 9 ((1-1)-й отсчет j-й строки) и третьего 10 (i-й отсчет J-и строки) регистров памяти. ЕСЛИ в результате сравнения (i-l)-ro и (i+l)- го отсчетов j-й строки окажется, что хотя бы в одном из четьфех старших разрядов есть изменения, то в (1-1)-м отсчете j-й строки и в i-м отсчете (j+l)-й строки передается информация

Q об истинном состоянии четырех старших разрядов этих отсчетов. Недостающие элементы восстанавливаются на приемной стороне: i-й элемент j-й строки воспроизводится как i-й элемент

5 ( строки, а (i-l)-й элемент

(j+l)-й строки повторяется как (i-1)-й элемент j-й строки. Этой ситуации присваивается до полнит ел ь ная кодовая комбинация 00.

Если в результате сравнения (i-1)- го и (i+l)-ro отсчетов j-й строки окажется, что нет отличий в старших разрядах кода и в результате сравнения (i-1)-го отсчета j-й строки и i-ro отсчета (j+I)-й строки также не будет изменений, то в (i-l)-OM отсчете j-й , строки передается информация об истинном состоянии четырех старших разрядов исходного кода этого отсче-

0

5

та, в i-OM отсчете (j+l)-ft строки передается информация об истинном состоянии двух следующих по старшен- ству разрядов (i-l)-ro отсчета j-й строки и информация об изменении символов младших разрядов j-ro отсчета {j+l)-ft строки относительно (i-1)- FO отсчета j-и строки, в (1+1)-ом отсчет е J-й строки передается информация об изменении символов младших разрядов {i-)-ro отсчета (j+l)-ft строки относительно (i-l)-ro отсчета j-й строки, которая занимает два бита информации в кодовом слове, и информация об изменении символов младших разрядов i-ro отсчета j-й строки относительно (i-)-ro отсчета этой же строки. Эта информация также занимает 2 бита в кодовом слове. Этой ситуации присваивается дополнительная кодовая комбинация 11. Восстановление недостающих элементов на приемной стороне происходит как и в предыдущем случае.

Если в результате сравнения (1-1 )- го и (i+l)-ro отсчетов j-й строки нет отличий в старших разрядах, а в результате сравнения старших разрядов .(i-l)-ro отсчета j-й строки и i-ro отсчета (j+I)-й строки изменения обнаружены, то производится сравнение старших разрядов (i-l)-ro и i-ro от1356259б

же строки, а i-й отсчет (j+l)-й стро ки повторяется как (1-1)-й отсчет этой же строки. Этой ситуации присва-

(- ивается дополнительная кодовая комбинация 01.

В результате, когда входной телевизионный аналоговый сигнал поступает на входы блока 1 установки опор10 ного уровня и блока 2 аналого-цифрового преобразования, селектор блока установки опорного уровня выделяет из аналогового сигнала синхросмесь и вырабатывает по переднему фронту

15 синхроимпульсов положительные импульсы (фиг. 15а), служащие для установки делителя 31 тактовой частоты (фиг. 15в) формирователя 3 интервалов времени, блок 46 формирования адреса

20 элемента 6 задержки и элементов 61-1- 61-3 памяти блока 19 памяти в исходное состояние и получения полустроч- ной частоты делителя 32 строчной частоты формирователя 3 интервалов вре25 мени. Импульс также поступает на

вход формирователя 5 кода синхронизации, представляющего собой мультиплексор, который за время этого импульса вырабатывает специальные ко-

30 довые посылки,, обозначающие начало строки. В канал связи эти посылки передаются первым блоком 4 коммутации через шифратор 20, Аналого-цифровой преобразователь 27 блока 2

счетов j-й строки. Если при этом будут обнаружены изменения, что с боль-, gg аналого-цифрового, преобразования преобразует входной аналоговый сигнал в цифровую форму. Семиразрядный параллельный код поступает на выход блока 2 аналого-цифрового преобразо- 40 вания с тактовой частотой, задаваемой тактовым генератором 29 (фиг, 17а). Формирователь 30 коротких импульсов вырабатывает короткие импульсы (фиг. 156) из тактовой час- 45 тоты, которая поступает на второй тактовый выход. Эти импульсы поступают на первый: тактовый выход и служат для запуска блока 46 формирова- ,ния адреса элемента 6 задержки, дпя - 50 получения полутактовой частоты . (фиг. 16в) делителем 31 тактовой частоты формирователя 3 интервалов времени. Формирователь 3 посредством цифровой линии 33 задержки осущест- 55 вляет синхронизацию всего устройства импульсами ,с первого второго, третьего, четвертого, пятого и седьмого выходов (фиг. 15 г-3), Шестой выход цифровой линии 33 задержки( фиг. 15и,к)

шой вероятностью говорит о появлении в изображении вертикальной границы яркости, то в i-OM отсчете (j+l)-й строки передается информация об истинном состоянии четырех старших разрядов исходного кода этого отсчета, а в (1+1)-ом отсчете j-й строки передается информация об истив:ном состоянии двух следующих; по старшенст- ву младших разрядов - (i-l)-ro отсчета j-й строки и i-ro отсчета (j+l)-й строки. Алгоритм восстановления недостающих элементов не меняется. Этой ситуации присваивается дополнительная кодовая комбинация 10, В противном случае, т.е. когда в старших разрядах (i-l)-ro и i-ro отсчетов j-й строки нет отличий, что говорит о появлении в сигнале гори™ зонтальногр перепада яркости, характер передачи сохраняется, но восстановление недостающих элементов будет иным: (i-l)-й отсчет (j+I)-й строки воспроизводится как i-й отсчет этой

служит для установки в исходное состояние элементов 65 памяти первого блока 21 разрешения записи элементов (фиг. 17в,и) 69 памяти второго блока 22 разрешения записи (фиг. 18а,ж) и элементов 75 и 76 памяти блока 24 пилот-сигнала. Выходами полутактовой и полустрочной частоты формирователя 3 являются выходы 38 и 37. Блок 6 задержки записывает информацию о состоянии разрядов с выхода блока 2 аналого-цифрового преобразования во время отрицательной полуволны на управляю-

20

30

35

щем входе блока 6 задержки и разреша- g да .суммирующего регистра 7 и первого ет считывать информацию во время положительной полуволны. Таким образом, на входах суммирующего регистра 7 памяти одновременно имеется информация о j-й строки с выхода блока 6 задержки и информация о (з+1)-й строке с выхода блока 2 аналого-цифрового преобразования. Управляющие сигналы на первом, втором и третьих входах суммирующего регистра 7 (фиг. 16а,б,в); объединяясь на элементах ИЛИ 50 и 51 (фиг. 16г,д), посредством блока 52 разрешения записи, разрешающего запись в элемент 54 памяти (фиг. 16з), состоящий из набора триггеров, по сихроимпульсу (фиг. 16и,к) записывают четные отсчеты j-й строки и нечетные отсчеты (j+l)-й строки (фиг. 16е,ж). Одновременно комбинации сигналов на управляющих входах третьего и четвертого регистров 10 и 11 памяти, которые состоят из линейки D-триггеров, позволяет записать в них по синхроим пульсу соответственно семь разрядов нечетных отсчетов j-й строки с выхода блока 2 аналого-цифрового преобразования и три младших разряда четных отсчетов (j+й)-й строки с выхода блока 6 задержки. Информация с выхода суммирующего регистра 7 памяти последовательно переписывается в первый и второй регистры 8 и 9 памяти. Таким образом, одновременно имеется информация об (i-1)-ом, i-ом (i+l)-OM отсчетах j-й строки (соответственно во втором и третьем регистрах 9 и 10 памяти и в суммирующем регистре 7 памяти), i-ом отсчете (j+l)-й строки (в первом регистре 8 памяти) и трех младших разрядах (i-l)-ro отсчета (j+l)-й строки (в четвертом регистре 11 памяти). Первыми входами суммирующего регистра 7, первого и второго регистров 8 и

выхода второго регистра 9 памяти, го ворит о наличии изменения символа хотя бы в одном из разрядов, то в (i-l)-OM отсчете j-й строки передает ся информация об истинных значениях четырех старших разрядов исходного кода первым блоком 4 коммутации, вто рой вход которого соединен с первым выходом второго регистра 9 памяти 25 посредством блоков 39, 42 - 44 выбора разряда кодов канала, которые состоят из элементов ИЛИ-НЕ 40-1 - 40-3, объединенных на элементе ИЛИ- НЕ 40-4, и блока 45 памяти кода канала. Одновременно эта же информация через блок 66 совпадения первого бло ка 21 разрешения записи (фиг. 17ж) записывается через элементы ИЛИ 60-1 60-4 в элементы 61-1 памяти четырех старших разрядов кода первого блока 19 памяти. Младшие разряды первого блока 19 памяти устанавливаются в со ответствии с принятым алгоритмом эле ментами установки младших разрядов 57-1 - 57-2 блока 18 управления памя тью. Элементы 56-1 - 56-6 запрета выбирают самый старший из разрядов, в котором произошло изменение при за писи четырех старших разрядов кода, для чего выходы элементов 61-1 - 61- памяти первого 19 блока памяти диффе ренцируются цифровыми дифференцирующими элементами 62-1 и 62-2 и подают ся на входы элементов 56-1 - 56-6 за прета. Выходы элементов 57-1 - 57-2 установки младших разрядов заведены на входы триггеров элементов 61-2 и 61-3 памяти таким образом, что при изменении старшего из изменившихся разрядов О - 1 младшие разряды устанавливаются в О и наоборот. В i-ом отсчете (j+l)-й строки передается информация об истинном состоянии четырех разряд ов исходного кода блоком

40

45

50

55

9 памяти являются выходы всех семи разрядов кода, вторыми выходами суммирующего регистра 7 и первого регистра 8 и первым выходом третьего 10 .и выходом четвертого 11 регистров, памяти являются выходы трех младших разрядов.

Информация в канал связи передается на место четных отсчетов j-й строки и нечетных отсчетов (.j+1 )-й строки. Если второй блок 14 сравнения, на входы которого поступают по четыре старших разряда со второго выхо-

да .суммирующего регистра 7 и первого

выхода второго регистра 9 памяти, говорит о наличии изменения символа хотя бы в одном из разрядов, то в (i-l)-OM отсчете j-й строки передается информация об истинных значениях четырех старших разрядов исходного кода первым блоком 4 коммутации, второй вход которого соединен с первым выходом второго регистра 9 памяти посредством блоков 39, 42 - 44 выбора разряда кодов канала, которые состоят из элементов ИЛИ-НЕ 40-1 - 40-3, объединенных на элементе ИЛИ- НЕ 40-4, и блока 45 памяти кода канала. Одновременно эта же информация через блок 66 совпадения первого блока 21 разрешения записи (фиг. 17ж) записывается через элементы ИЛИ 60-1 60-4 в элементы 61-1 памяти четырех старших разрядов кода первого блока 19 памяти. Младшие разряды первого блока 19 памяти устанавливаются в соответствии с принятым алгоритмом элементами установки младших разрядов 57-1 - 57-2 блока 18 управления памятью. Элементы 56-1 - 56-6 запрета выбирают самый старший из разрядов, в котором произошло изменение при записи четырех старших разрядов кода, для чего выходы элементов 61-1 - 61-3 памяти первого 19 блока памяти дифференцируются цифровыми дифференцирующими элементами 62-1 и 62-2 и подаются на входы элементов 56-1 - 56-6 запрета. Выходы элементов 57-1 - 57-2 установки младших разрядов заведены на входы триггеров элементов 61-2 и 61-3 памяти таким образом, что при изменении старшего из изменившихся разрядов О - 1 младшие разряды устанавливаются в О и наоборот. В i-ом отсчете (j+l)-й строки передается информация об истинном состоянии четырех разряд ов исходного кода блоком

70 разрешения второго блока. 22 разрешения записи (фиг, 186,ж), выход которой соединен с четвертым входом первого блока 4 коммутации. Одновременно эта же информация записывается в элементы 61-3 памяти через элементы ИЛИ 60-1 первого блока 19 памяти, а все более младшие разряды устанавливаются по цепи: первый блок 19 памяти - блок 18 управления памятью - первый блок Г9 памяти. В этой ситуации на третий управляющий вход блока 24 пилот-сигнала поступает уровень логической едини1уз1 с выхода второго блока 14 сравнения ( фиг. 19г) и посредством элементов ИЛИ-НЕ 72 и 74 в элементы памяти 75 и 76 записывается кодовая комбинация 00 (фиг. 19а,ж,з)5 а посредством элементов ИЛИ-НЕ 79 и 80, ИЛИ 81 и элемента НЕ 78 эта комбинация передается в канал связи последовательно один бит в одном отсчете, другой в другом (фиг. 1 9б,в ,и).

10

135625910

блока 23 памяти-мла/даих разрядов. При этом совпадение сигналов на управляющих входах элемента И 68 второго блока 22 разрешения записи (фиг. 18в,г,д,е) переводит триггер элемента 69 памяти в другое состояние (фиг. 18ж) и запрещает прохождение сигнала через второй блок 22 разрешения записи. Вместе с информацией о двух младших разрядах в i-ом отсчете (,j+l)-й строки передается информация об изменении символг младших разрядов i-ro отсчета (+1)-й строки относительно (i-)-ro отсчета j-й строки. Для этого в третьем блоке 25 разрешения записи на элементе ИЛИ-НЕ 83 происходит совпадение сигналов от второго 14 и третьего 15 блоков.сравнения сигнала с синхровхода и полутактовой частоты (фиг. 20б,д,е5ж), триггер элемента 86 памяти, предварительно установленный импульсом с установочного входа (фиг. 20г), переходит в 25 другое состояние (фиг. 20и), и сигнал с выхода элемента ИЛИ 89 разрешает (фиг. 20м) через второй блок 12 ком

15

20

35

40

Если второй блок 14 сравнения говорит об отсутствии изменений, то производится дополнительное сравнение

в третьем блоке 15 сравнения, на вхо-зо рого регистра 9 памяти и первого ды которого подаются четыре старших разряда со второго выхода второго регистра 9 памяти. При этом в (i-1)- ом отсчете j-й строки передается информация об истинном состоянии четы рех старших разрядов этого отсчета как и в предыдущем случае. И если на первом выходе третьего блока 15 сравнения, который состоит из объединенных по ИЛИ элементов ИСКШОЧА- КЩЕЕ ИЛИ, уровень логического нуля (отсутствие изменений) то в первом блоке 21 разрешения записи на-элементе И 64 происходит совпадение соотв.ет - ствующих сигналов (фиг. 17б,г,д,е,з) и триггер элемента памяти 65 разрешает запись через блок 67 совпадения (фиг. 17и) в первый блок 19 памяти кроме старших разрядов, которые были записаны через блок 66 совпадения двух следующих по старшенству разрядов. Одновременно эти же дв-а разряда записываются в блок 23 памяти младших разрядов, который представляет собой два D-триггера, и с его выхода в следующем отсчете информация об этих разрядах передается в канал связи первым блоком 4 коммутации, тре тий -вход которого соединен с выходом

45

50

55

мутации, элементы ИЛИ-НЕ 101-I, 101-4 сравнение трех младших разрядов вто-

блока 19 памяти в первом блоке 13 сравнения. Информация о всех изменениях поступает на вход блока 17 выбора передаваемых символов, который посредством элементов ИЛИ-НЕ/ИЛИ (17-1 и 17-2) выбирает старший из изменившихся разрядов, а затем посредством блоков 58-1 - 58-6 выбора установки младших разрядов блока 18 управления памятью устанавливает младшие разряды в соответствующее состояние по принятому алгоритму,. Шифратор 20 кодирует номер изменившегося разряда двоичным кодом и переходит в канал связи первым блоком 4 коммутации. При этом блок 24 пилот-сигнала выбирает дополнительную кодовую комбина™ цию 11 (фиг. 19г,д,и) и передает ее в канал связи. Поскольку в (1+1)-ом отсчете j-й строки нет необходимости передавать информацию об этом отсчете она повторяет (1-1)-й отсчет этой же строки), то во время этого отсчета передается информация о предыдущих отсчетах. Совпадение сигналов на входах элемента ИЛИ-НЕ/ИЛИ (93) третьего блока 25 разрешения записи разрешает (фиг. 20а,б,з,п) сравнение трех младших разрядов первого блока

5

0

о рого регистра 9 памяти и первого

5

0

5

мутации, элементы ИЛИ-НЕ 101-I, 101-4 сравнение трех младших разрядов вто-

блока 19 памяти в первом блоке 13 сравнения. Информация о всех изменениях поступает на вход блока 17 выбора передаваемых символов, который посредством элементов ИЛИ-НЕ/ИЛИ (17-1 и 17-2) выбирает старший из изменившихся разрядов, а затем посредством блоков 58-1 - 58-6 выбора установки младших разрядов блока 18 управления памятью устанавливает младшие разряды в соответствующее состояние по принятому алгоритму,. Шифратор 20 кодирует номер изменившегося разряда двоичным кодом и переходит в канал связи первым блоком 4 коммутации. При этом блок 24 пилот-сигнала выбирает дополнительную кодовую комбина™ цию 11 (фиг. 19г,д,и) и передает ее в канал связи. Поскольку в (1+1)-ом отсчете j-й строки нет необходимости передавать информацию об этом отсчете она повторяет (1-1)-й отсчет этой же строки), то во время этого отсчета передается информация о предыдущих отсчетах. Совпадение сигналов на входах элемента ИЛИ-НЕ/ИЛИ (93) третьего блока 25 разрешения записи разрешает (фиг. 20а,б,з,п) сравнение трех младших разрядов первого блока

19 памяти и .четвертого регистра 11 памяти ((1-1)-й отсчет j-й строки и (1-1)-й отсчет (j+1)-й строки) в первом блоке 13 сравнения. Блок 17 выбора передаваемых символов выбирает самый старший из изменившихся разрядов, а шифратор 20 кодирует его номер. Информация с выхода шифратора, записывается через элементы ИЛИ-НЕ 102-1 и 102-3 и элементы ИЛИ 103-1 и 103-2 в элементы 104-1 и 104-2 памяти второго блока 26 памяти. Аналогично элементы ИЛИ-НЕ/ИЛИ (92) третьего блока 25 разрешения записи разрешают сравнение (фиг. 20з,к) в первом блоке 13 сравнения младших разрядов первого блока 19 памяти и третьего регистра 10 памяти через второй блок 12 коммутации ((1-1)-и и i-й отсчеты j-й строки. Результат сравнения через блок 17 выбора передаваемых символов и шифратор 20 записывается во второй блок 12 памяти.

10

падение сигналов на элементе ИЛИ-НЕ 82 третьего блока 25 разрешения записи в обоих случаях переводит в дру гое состояние. триггер элемента 85 памяти, который своим выходом (фиг. 20д,е,н,о) совместно с сигнало разрешения, формируемым на элементах ИЛИ-НЕ 94, 95, 96 (фиг. 20п), разрешает запись во второй блок 26 памяти двух младших разрядов (i--l)-ro отсчета J-й строки (элементы 104-1 и 104-2) и двух младших разрядов i-ro отсчета (j+l)-й строки (элементы с 104-3 и 104-4), которые по сигналу разрешения (фиг. 20р) записываются в первый коммутации в (1+1)-о отсчете. Одновременно через элементы ШШ-НЕ 105-1 и 105-2 второго блока 2 памяти они записываются в первый блок 19 памяти в своих отсчетах.

Вся поступающая на входы первого блока 4 коммутации информация записывается в блок 45 памяти кода кана-

20

При этом на элементе ИЛИ 97 третьего 25 а по синхроимпульсу (фиг. 20в) и с

блока 25 разрешения записи формируется сигнал запрета (фиг. 20л), запре- щаюощй установку младших разрядов первого блока 19 памяти, а элементы ИЛИ-НЕ 90 и 91 формируют сигнал, разрешающий считывать информацию из второго блока 25 памяти в первый блок 4 коммутации (фиг. 20р) во время (i-l)-ro отсчета.

Если третий блок 15 сравнения говорит о наличии изменений хотя бы в одном из четырех старших разрядов, то работа устройства определяется четвертым блоком 16 сравнения, на вход которого поданы четыре старших разряда с первых выходов второго 9 и третьего 10 регистров памяти. Эта ситуация определяется элементом И 68 второго блока 22 разрешения записи, и триггер элемента памяти 69 разрешает запись информации четырех старших разрядах в первый блок 19 памяти в i-oM отсчете, которая передается в канал связи первым блоком 4 коммутации. &1ХОДНОЙ сигнал четвертого блока 16 сравнения служит для формирования дополнительных кодовых комбинаций в блоке 24 пилот-сигнала. Если четвертый блок 16 сравнения говорит о наличии изменений, то вырабатывается дополнительная кодовая комбинация 10 (фиг. 19г,д,е,ж,з), в противном случае вырабатывается дополнительная кодовая комбинация 01. Кроме того, сов

падение сигналов на элементе ИЛИ-НЕ 82 третьего блока 25 разрешения записи в обоих случаях переводит в другое состояние. триггер элемента 85 памяти, который своим выходом (фиг. 20д,е,н,о) совместно с сигналом разрешения, формируемым на элементах ИЛИ-НЕ 94, 95, 96 (фиг. 20п), разрешает запись во второй блок 26 памяти двух младших разрядов (i--l)-ro отсчета J-й строки (элементы 104-1 и 104-2) и двух младших разрядов i-ro отсчета (j+l)-й строки (элементы с 104-3 и 104-4), которые по сигналу разрешения (фиг. 20р) записываются в первый коммутации в (1+1)-ом отсчете. Одновременно через элементы ШШ-НЕ 105-1 и 105-2 второго блока 26 памяти они записываются в первый блок 19 памяти в своих отсчетах.

Вся поступающая на входы первого блока 4 коммутации информация записывается в блок 45 памяти кода кана-

0

5

его вых-ода считывается на выход устройства для кодирования телевизионных сигналов.

При использовании предлагаемого Q устройства при том же количестве передаваемой информации значительно уменьшаются искажения восстановительного телевизионного сигнала при передаче малоконтрастных изменений яркости (в + 1-ом отсчете передается информация о младших разрядах передаваемых отсчетов). Формула изобретения

Устройство для кодирования телевизионных сигналов, содержащее блок установки опорного уровня и блок аналого-цифрового преобразования, входы которых объединены и являются входом устройства, последовательно соединен- j- le блок задержки, суммирующий регистр памяти, первый регистр памяти, второй регистр памяти, последовательно соединенные первый блок сравнения, блок выбора передаваемых символов, блок управления памятью и первый блок памяти, первый выход которого соединен с другим входом первого блока сравнения, а второй выход - с вторым входом блока управления памятью, а также первый и второй блоки коммутации, второй, третий и четвертый блоки сравнения, формирователь кода синхронизации, первый и второй блоки разрешения записи.

0

5

блок пилот-сигнала, блок памяти младших разрядов, шифратор и третий регистр памяти, при этом установочный вход первого блока памяти обтэединен с входом формирователя кода синхронизации, с установочными входами блока задержки и формирователя интервалов времени и соединен с выходом блока установки опорного уровня, выход формирователя кода синхронизации соединен с первым входом шифратора, - второй вход которого соединен с другим выходЬм блока выбора передаваемых символов, а выход соединен с первым сигналышм входом первого блока коммутации, выход которого является выходом устройства, первый тактовый выход блока аналого-цифрового преобразования соединен с тактовыми входами блока задержки и формирователя интервалов времени, прямой и инверсный выходы полустрочной частоты и выход полутактовой частоты которого соединены соответственно с управляющим входом блока задержки, с первыми управляющими входами третьего регистра памяти и суммирующего регистра памяти, инверсный выход полутактовой частоты соединен с первым управляющим входом первого блока коммутации, с вторыми управлякядими входами третьего регистра памяти и суммирующего регистра памяти и с первым управляющим входом второго блока разрешения записи, третий управляющий вход суммирующего регистра памяти соединен с вторым управляющим входом первого блока коммутации, с первыми управля- кяцими входами блока памяти младших разрядов, первого блока разрешения записи, блока пилот-сигнала и соединен с инверсным выходом полутактовой частоты формирователя интервалов времени, первый сигнальный выход которого соединен с синхровходами первого блока коммутации, третьего регистра

памяти и суммирующего регистра памяти, второй сигнальньй выход - с син-

хровходом первого регистра памяти.

I

третий сигнальный выход - с синхровходом второго регистра памяти, четвертый сигнальньй выход - с синхро- входами блока пилот-сигнала и первого и второго блоков разрешения записи, пятьш сигнальньй выход - с синхро- входами первого блока памяти и блока п амяти младших разрядов, шестой сигнальный выход - с установочными вхо

5

0

дами блока пилот-сигнала и первого и второго блоков разрешения записи, второй выход суммирующего регистра памяти соединен с первым входом второго блока сравнения, второй выход первого регистра памяти - с первым входом третьего блока сравнения, первый выход второго регистра памяти-с вторыми входами второго и третьего блоков сравнения, с первым входом четвертого блока сравнения, с вторым сигнальным входом первого блока коммутации и с сигнальными входами первого и второго блоков разрешения записи, второй вход четвертого блока сравнения соединен с первым выходом третьего регистра памяти, а выход - с вторым управляющим входом блока пилот-сигнала, выход второго блока сравнения соединен с вторьми управляющими входами первого и второго блоков разрешения записи и с третьим управляющим входом блока пи- 5 лот-сигнала, четвертый управляющий вход которого объединен с третьим управляющим входом второго блока разрешения записи и соединен с первым выходом третьего блока сравнения, вто- второй вход которого соединен с третьим управляющим входом, первого блока разрешения записи, первый и второй первого блока разрешения записи соединены соответственно с вторым сигнальным входом и с третьим входом первого блока памяти и с сигнальным входом блока памяти мларших разрядов выход которого соединен с третьим сигнальным входом первого блока коммутации, а выход второго блока разрешения записи соединен с четвертыми сигнальными входами первого блока памяти и первого блока коммутации, пятый сигнальный вход которого соединен с выходом блока пилот-сигнала, отличающееся тем, что, с целью увеличения объема кодируемой информации, введены второй блок памяти, третий блок разрешения записи и четвертый регистр памяти, при зтом сигнальньй выход блока аналого-цифрового преобразования соединен с сигнальными входами блока задержки, третьего регистра памяти и вторым сигнальным входом суммирующего регистра памяти, выход блока задержки соединен с сигнальным входом четвертого регистра памяти, первый управляющий вход которого соединен с прямым выходом

0

5

5

0

5

полустрочной-частоты формирователя интервалов времени, второй управляющий вход - с инверсным выходом полутактовой частоты формирователя интер- валов времени, а синхровход - с вторым сигнальным выходом формирователя интервалов времени, первый, второй и третий сигнальные входы второго блока коммутации соединены соответственно с выходом второго регистра памяти, объединенного с первым сигнальным входом второго блока памяти, с выходами четвертого и третьего регистров па-- мяти, с первого по пятый сигнальные входы третьего блока разрешения записи соединены соответственно с выходом второго блока сравнения, с первым и вторьы выходами третьего блока сравнения, с инверсным выходом полу- тактовой частоты формирователя интервалов времени и вторым тактовым выходом аналого-цифрового преобразователя синхровход и установочный вход третьего блока разрешения записи соединены соответственно с четвертым и пятым сигнальными выходами формирователя интервалов времени, первый выход соединен с первым управляющим йхрдом

второго блока коммутации, второй выход - с вторым управляющим входом второго блока коммутации и первым управляющим входом второго блока памяти, третий выход - с третьим управляющим входом второго блока коммутации и вторым управляющим входом второго блока памяти, четвертый выход - с управляющим входом блока управления памятью, пятый выход - с третьим управляющим входом второго блока памяти, шестой выход - с четвертым управляющим входом второго блока памяти, а седьмой выход - с третьим управляющим входом первого блока коммутации, синхровход второго блока памяти соединен с седьмым сигнальньш выходом формирователя интервалов времени, второй сигнальный вход второго блока памяти соединен с выходом шифратора, а первый и второй выходы - соответственно с пятым сигнальным входом первого блока памяти и шестым сигнальньм входом первого входа коммутации , а вход второго блока коммутации соединен с вторым входом первого блока сравнения.

Z7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия цифровых телевизионных сигналов | 1984 |

|

SU1243159A2 |

| Устройство для сжатия цифрового телевизионного сигнала | 1985 |

|

SU1285626A1 |

| Устройство для сжатия цифровых телевизионных сигналов | 1982 |

|

SU1059702A1 |

| Устройство для сжатия цифровых телевизионных сигналов | 1984 |

|

SU1238268A2 |

| Устройство для разделения коррелограмм | 1987 |

|

SU1432558A1 |

| Устройство управления процессора двухмерного преобразования Фурье | 1982 |

|

SU1121677A1 |

| Адресное устройство для цифрового фильтра | 1985 |

|

SU1298859A1 |

| Двухкаскадное устройство для ранговой фильтрации | 1985 |

|

SU1304036A1 |

| Запоминающее устройство | 1987 |

|

SU1443029A1 |

| Коммутационное устройство | 1990 |

|

SU1730635A1 |

Изобретение относится к телевидению. Цель изобретения - увеличение объема кодируемой информации. Устройство содержит блок.1 установки опорного уровня, блок 2 аналого-цифрового преобразования, формирователь 3 интервалов времени, блоки 4 и 12 коммутации, формирователь 5 кода синхронизации, блок 6 задержки, сумми- (Л С

фиг. 2

fc X) I

Э

31

- Л}f

фигЗ

JO / f1A2A MA5A6ATJe/l3AtO

Т

tS

so

S

52

53-1 S3-г

su

S.с

13

LLn. jJL1Ц ;

;j-f13-2f5-5

-

. Z-u бы х

,. 5И

I l . 1 . . ,

м-г ss-31 |5g-

I I I I

H

; 55

Щ

фиг. 6

Т

. Z-u бы ход

SB-2

56-i

5ff-455-5 I I gg-S

i I

57- I I 57-2

Я

фие.в

(pus.9

(

С

4iLiiL N/ Ь8

Ni/ NJ/ 69

Ж

70

W

Cf3us.rO

3Z

72

73

74

ЧУ / /

ж

еригП

фиг. 12

фиё. /4

5814/56

Тираж 636Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для сжатия цифровых телевизионных сигналов | 1980 |

|

SU944145A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для сжатия цифрового телевизионного сигнала | 1985 |

|

SU1285626A1 |

Авторы

Даты

1987-11-30—Публикация

1986-05-26—Подача