разонания. С его выхода семиразряд- нь1й параллельный код поступает на суммирующий регистр памяти (РП) 7 . непосредственно, через элемент задержки 6 - на строку и на РП 10. Код с суммирующего РП 7 переписывается последовательно и РП 8 и 9. Информа- , передаваемая в канал связи через коммутатор 4, зависит от результатов сравнения четырех старших разрядов соответствующих отсчетов соответствующих строк в блоках сравнения (БС) П-14. Элементы j -и строки передаются четными отсчетами информацией об истинных значениях разрядов исходного кода. Элементы (j + O-й строки-передаются через отсчет информацией, зависящей от результатов сравнения в БС 12, на который подаются (1-1)-й и (1+1)-й отсчеты j-и строки , в БС 13, на который подаются (1-1)-й отсчет

, Изобретение относится к электросвязи, в частности к системам передачи телевизионных изображений, и .может быть использовано также в телеграфии, а именно в устройствах с преобразованием кода внутри передатчика, и,является усовершенствованием устройства по авт. св. № 1146831 .

Цель изобретения - уменьшение искажений телевизионного сигнала за счет уменьшения искажений наклоных контуров.

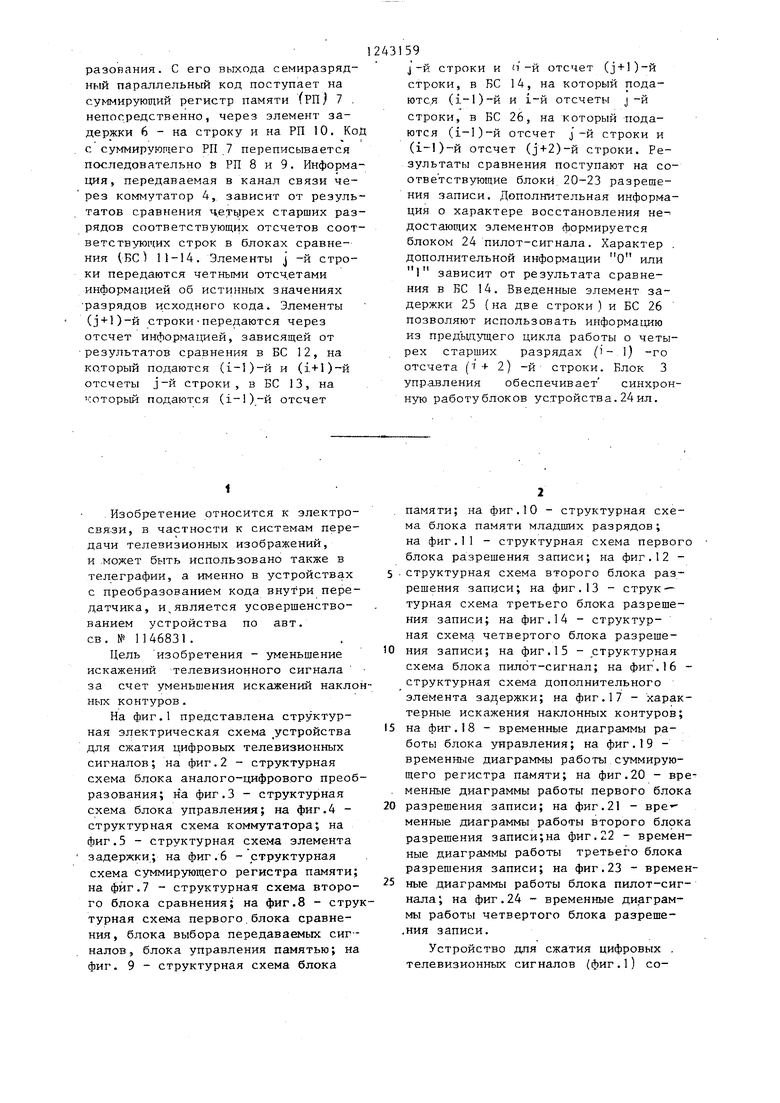

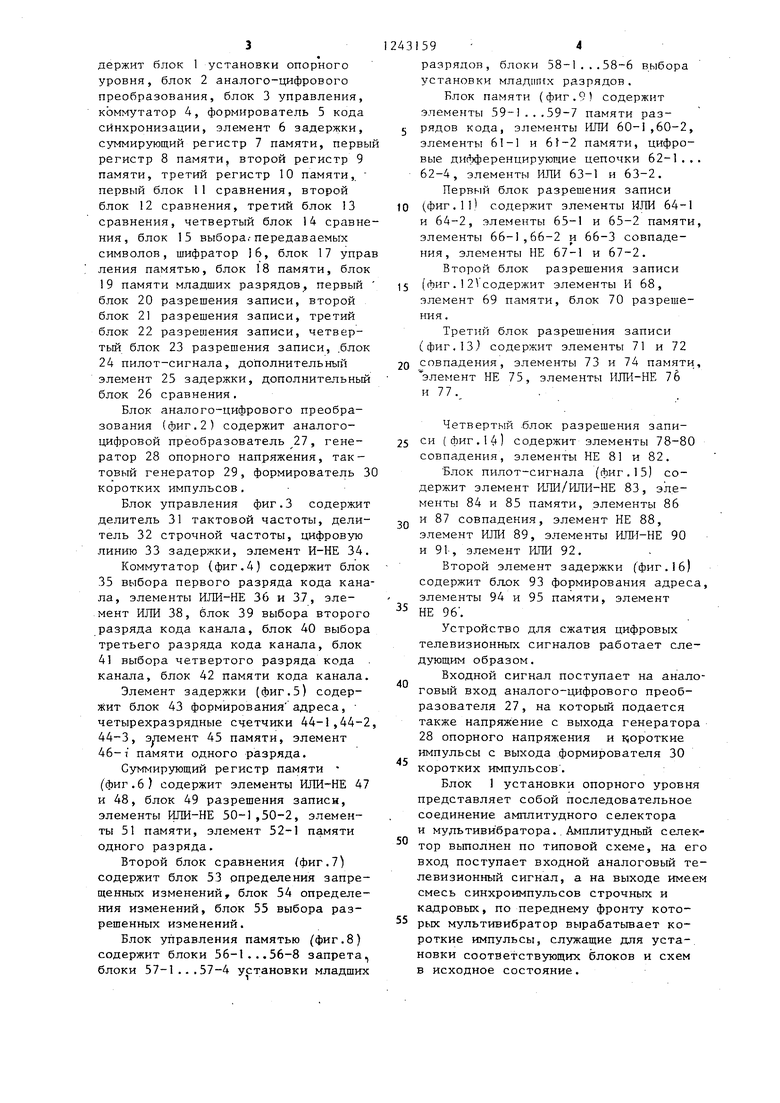

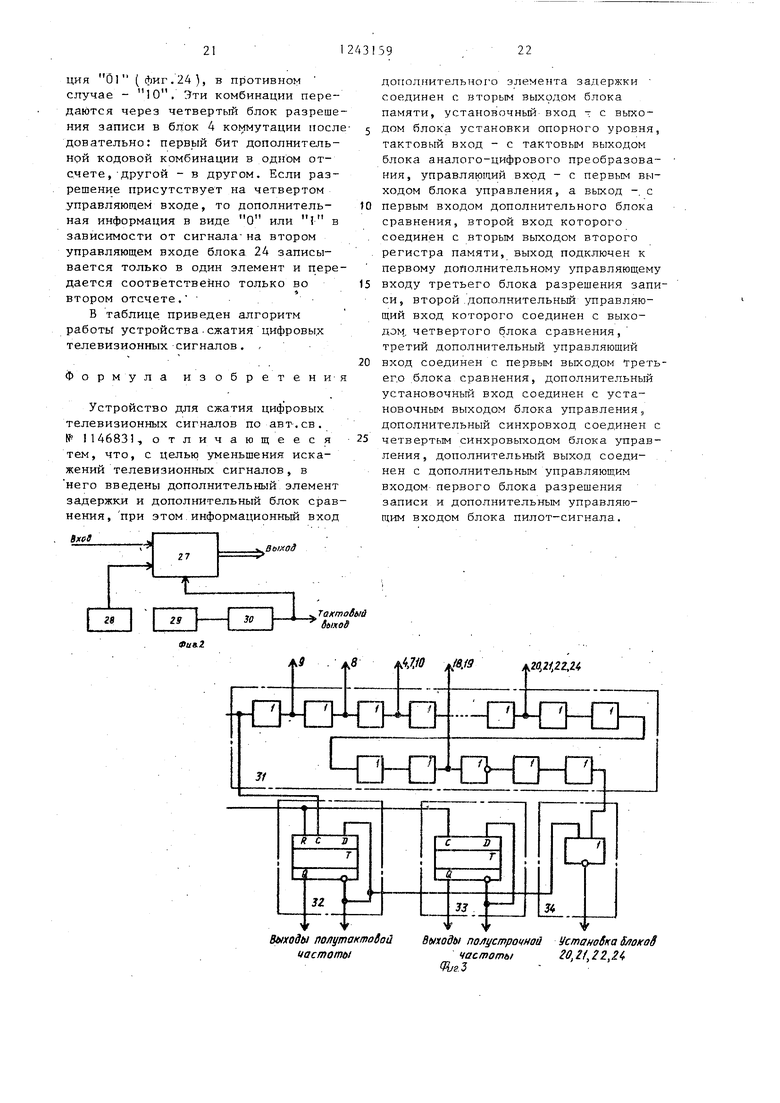

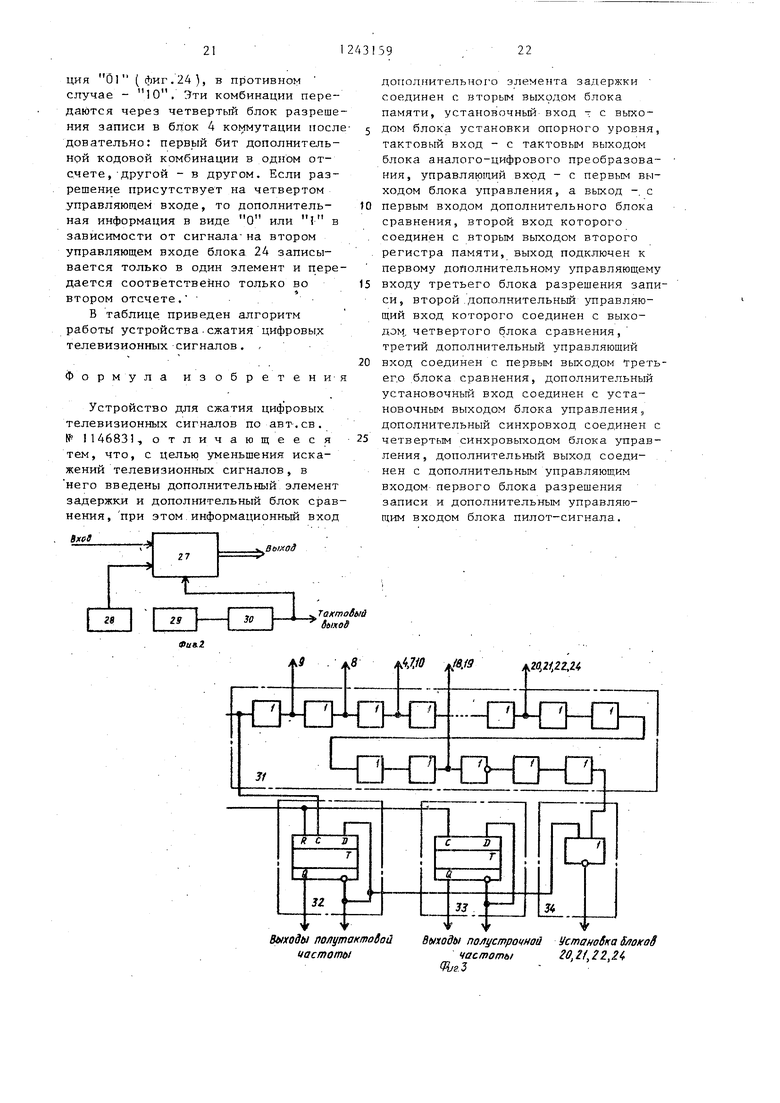

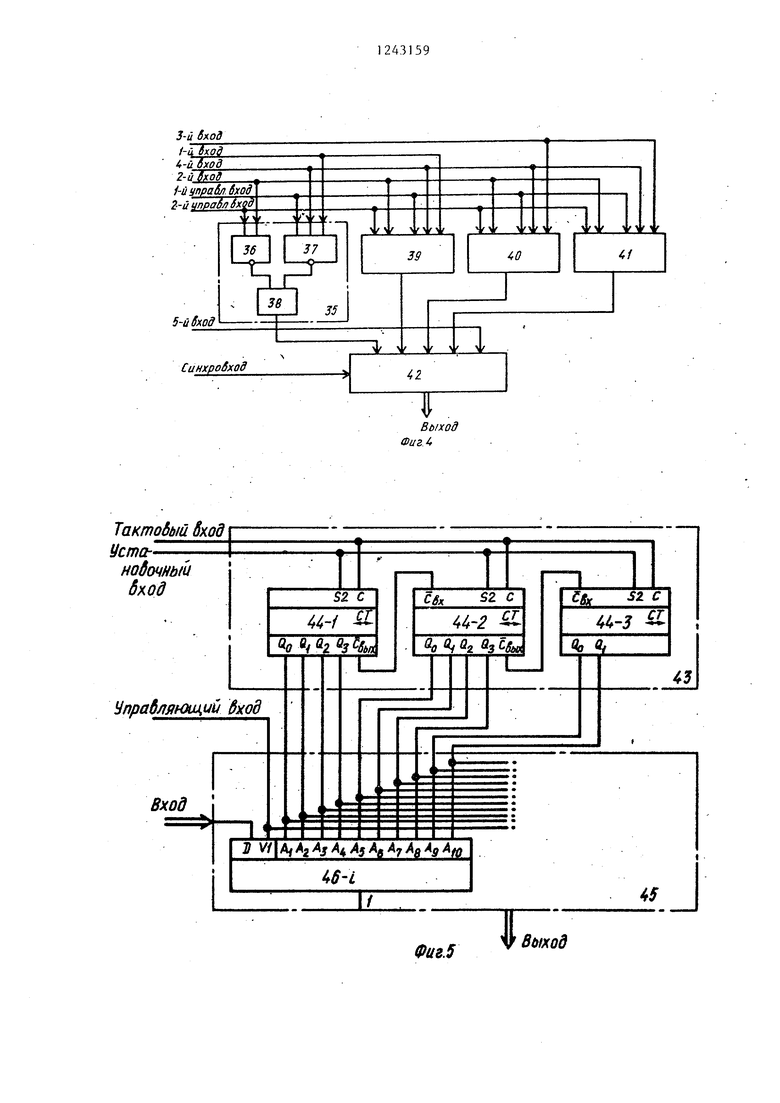

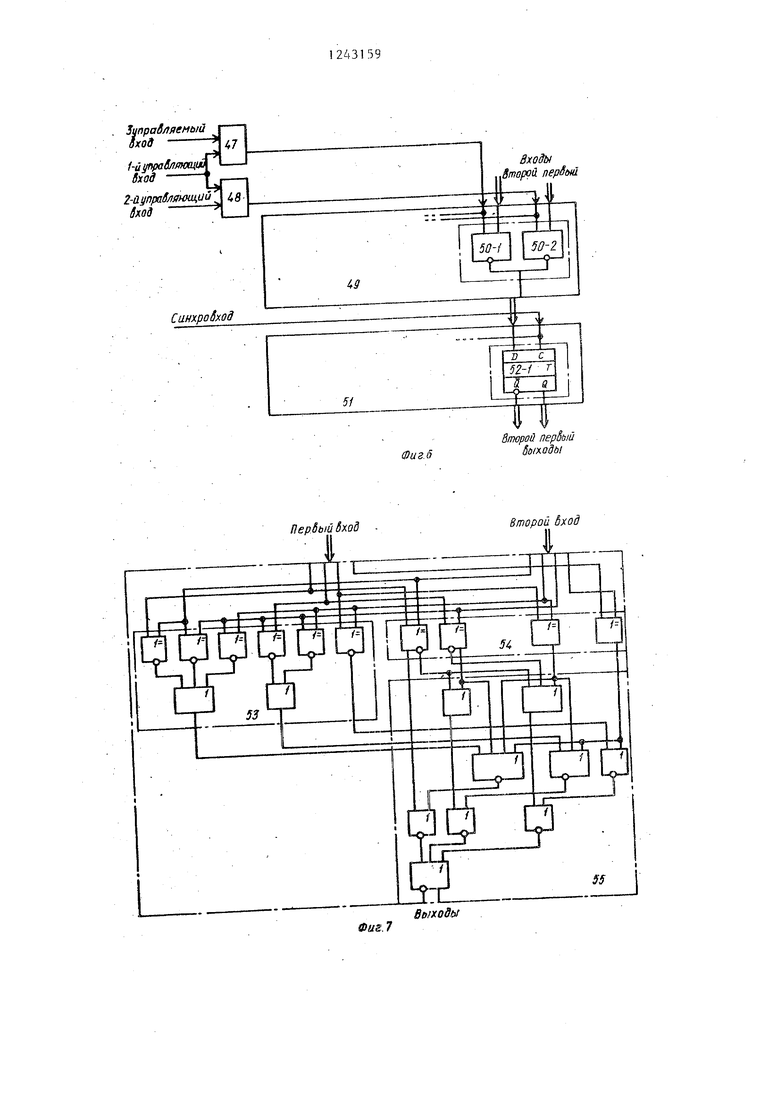

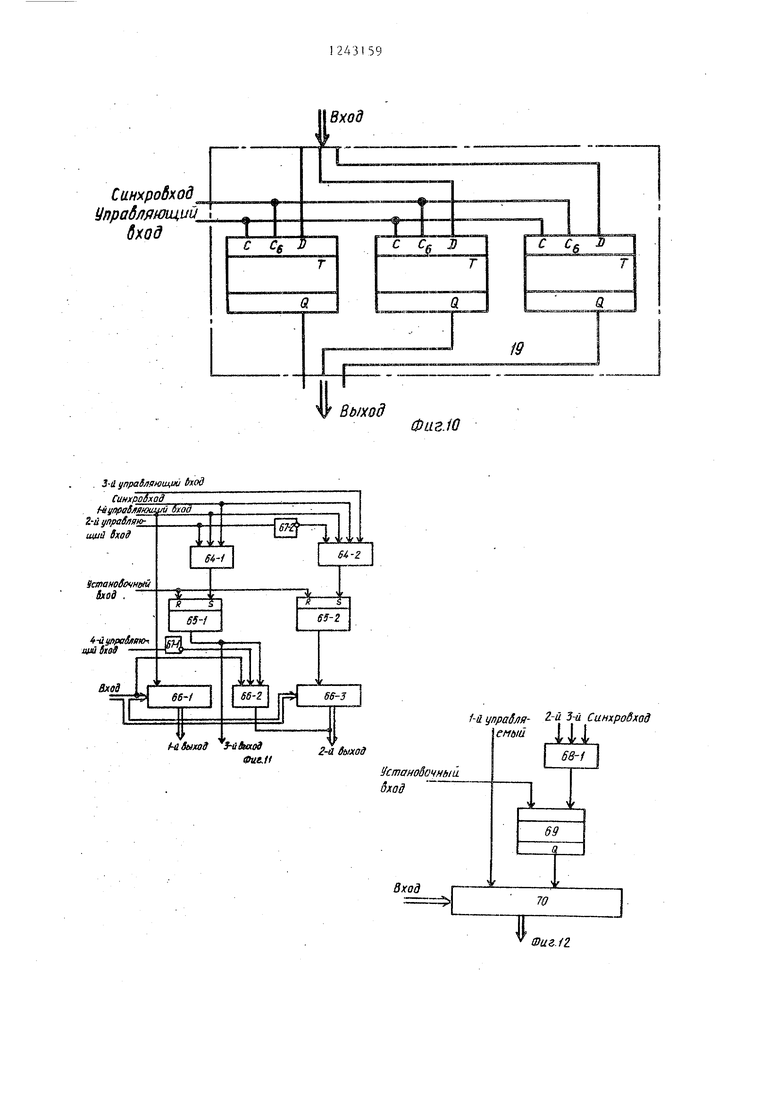

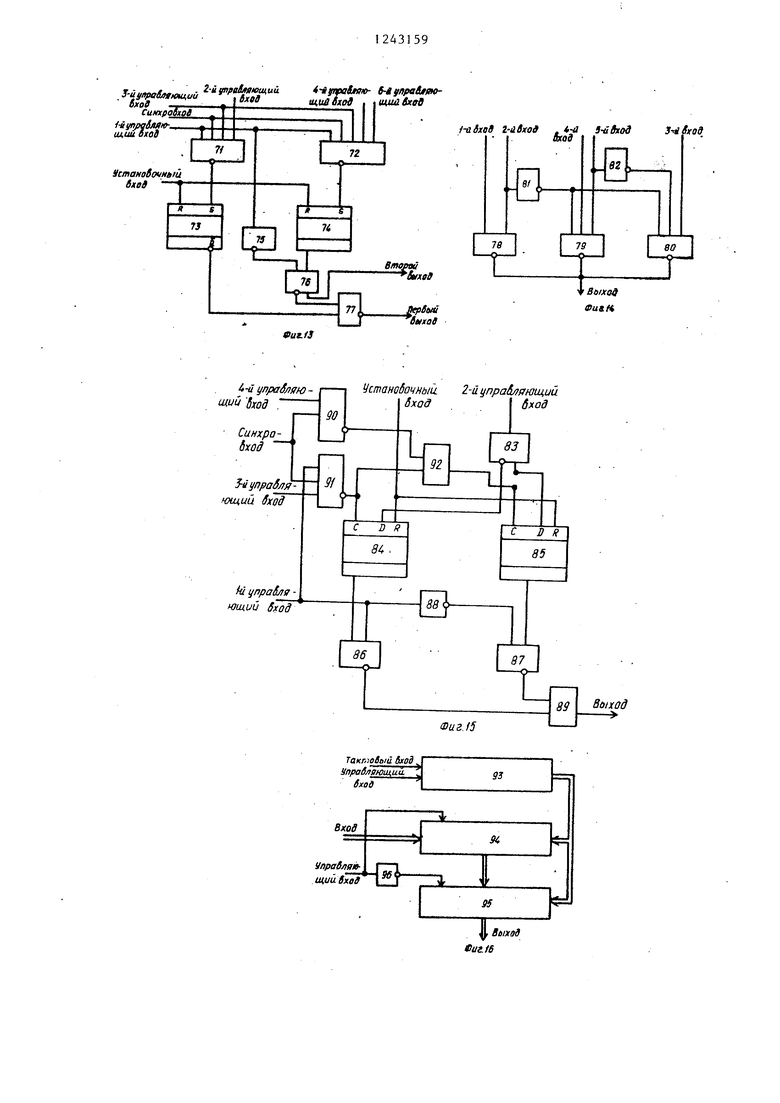

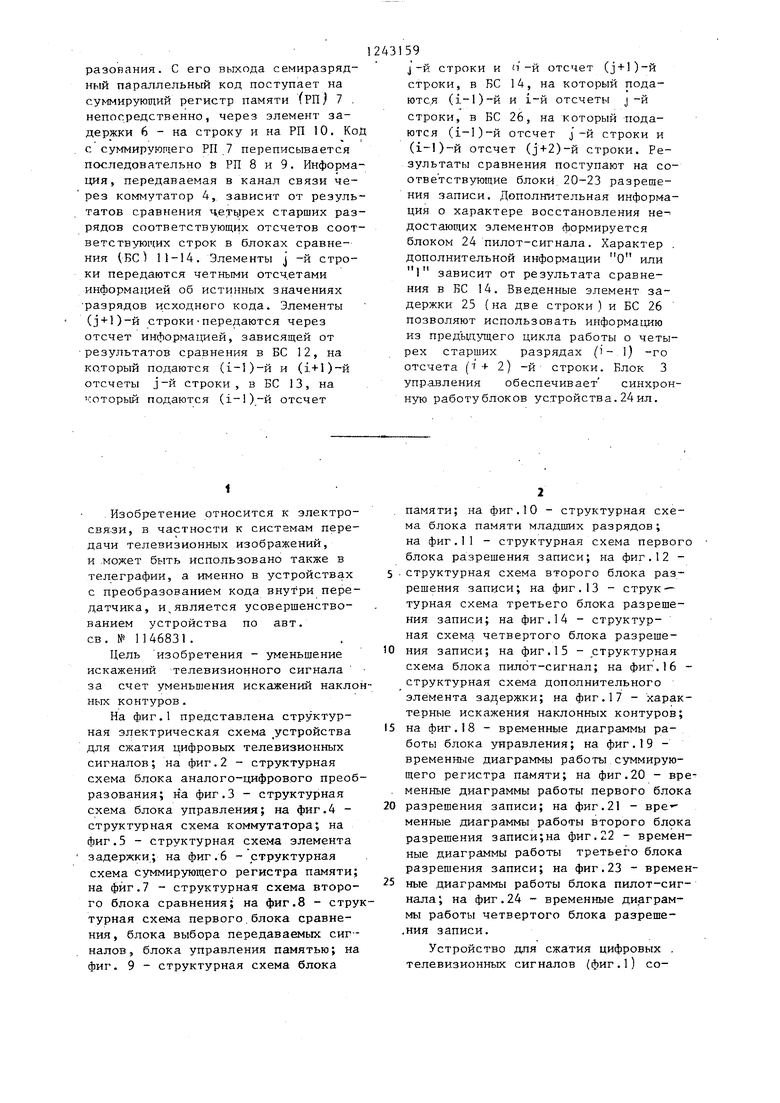

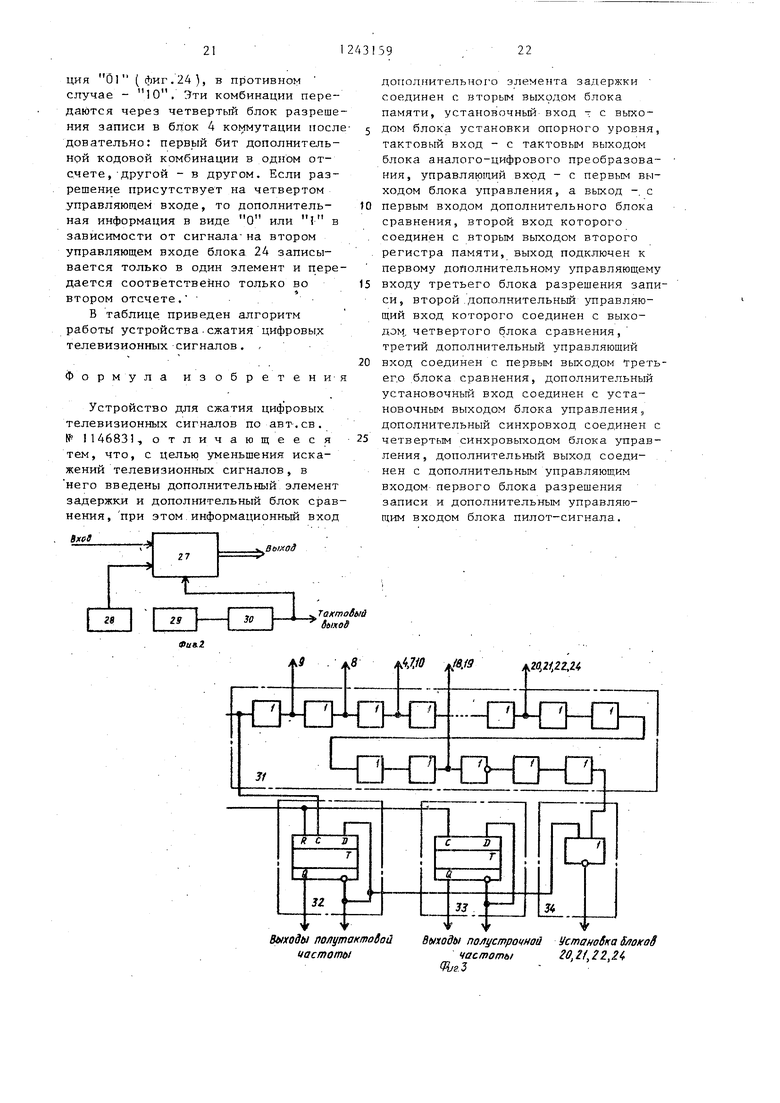

На фиг.1 представлена структурная электрическая схема устройства для сжатия цифровых телевизионных сигналов; на фиг.2 - структурная схема блока аналого-цифрового преобразования; на фиг.З - структурная схема блока управления; на фиг.4 - структурная схема коммутатора; на фиг.5 - структурная схема элемента задержки; на фиг.6 - структурная схема суммирующего регистра памяти; на фиг.7 - структурная схема второго блока сравнения; на фиг.З - струтурная схема первого.блока сравнения , блока выбора передаваемых сиг-налов, блока управления памятью; на фиг. 9 - структурная схема блока

43159

j-и строки и п -и отсчет (д + 1)-й строки, в БС 14, на который подаются (1-1)-й и i-й отсчеты j -и строки, в БС 26, на который подаются (1-)-й отсчет J й строки и (1-1)-й отсчет (5+2)-й строки. Результаты сравнения поступают на соответствующие блоки, 20-23 разрешения записи. Дополнительная информация о характере восстановления не достаюпщх элементов формируется блоком 24 пилот-сигнала. Характер дополнительной информации О или 1 зависит от результата сравнения в БС 14. Введенные элемент задержки 25 (на две строки) и БС 26 позволяют использовать информацию из предыдущего цикла работы о четырех старших разрядах (i- 1) -го отсчета (т + 2) -и строки. Блок 3 упр,авления обеспечивает синхронную работу блоков устройства.24 ил.

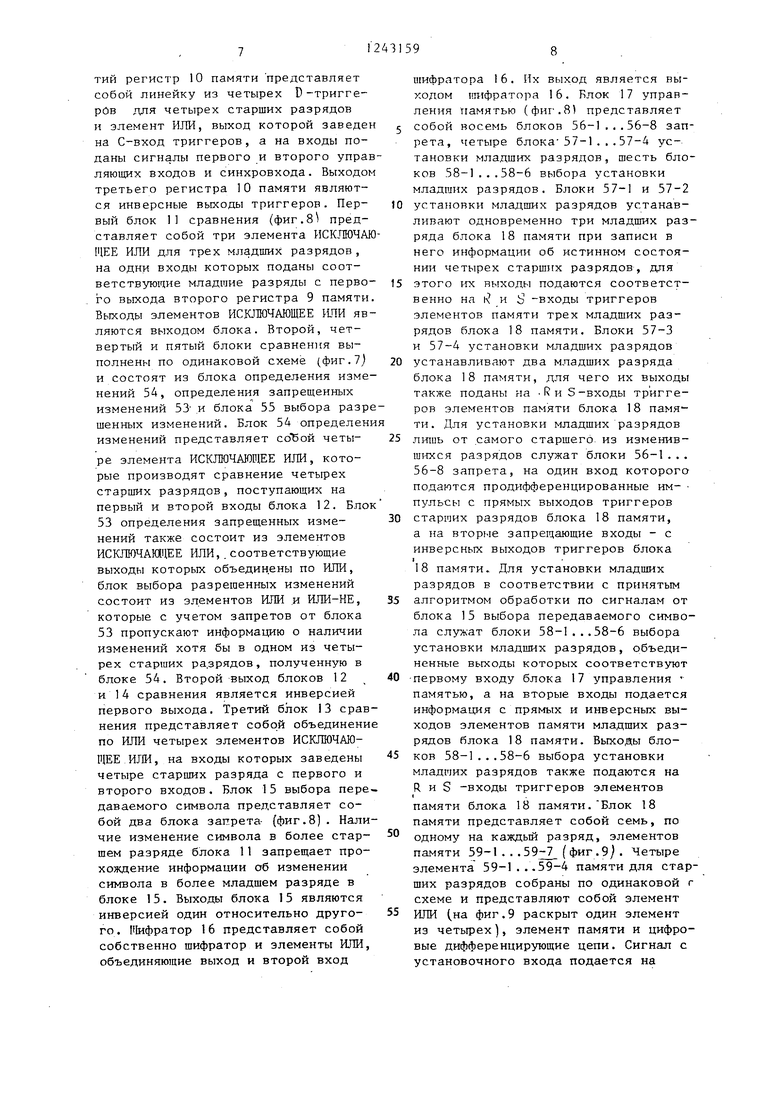

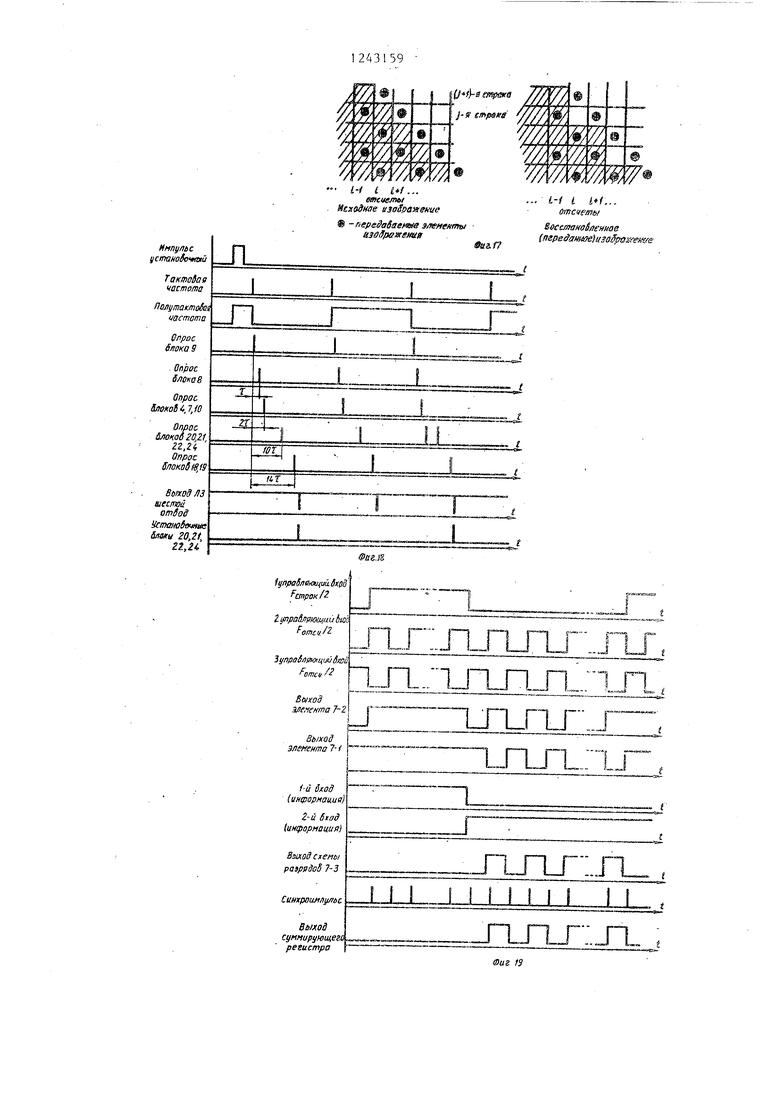

памяти; на фиг.10 - структурная схема блока памяти младших разрядов; на фиг.11 - структурная схема первого блока разрешения записи; на фиг.12 структурная схема второго блока разрешения записи; на фиг. 13 - структурная схема третьего блока разрешения записи; на фиг.14 - структурная схема четвертого блока разрешения записи; на фиг. 1 5 - структурная схема блока пилот-сигнал; на фиг.16 - структурная схема дополнительного элемента за ержки; на фиг. 17 - характерные искажения наклонных контуров;

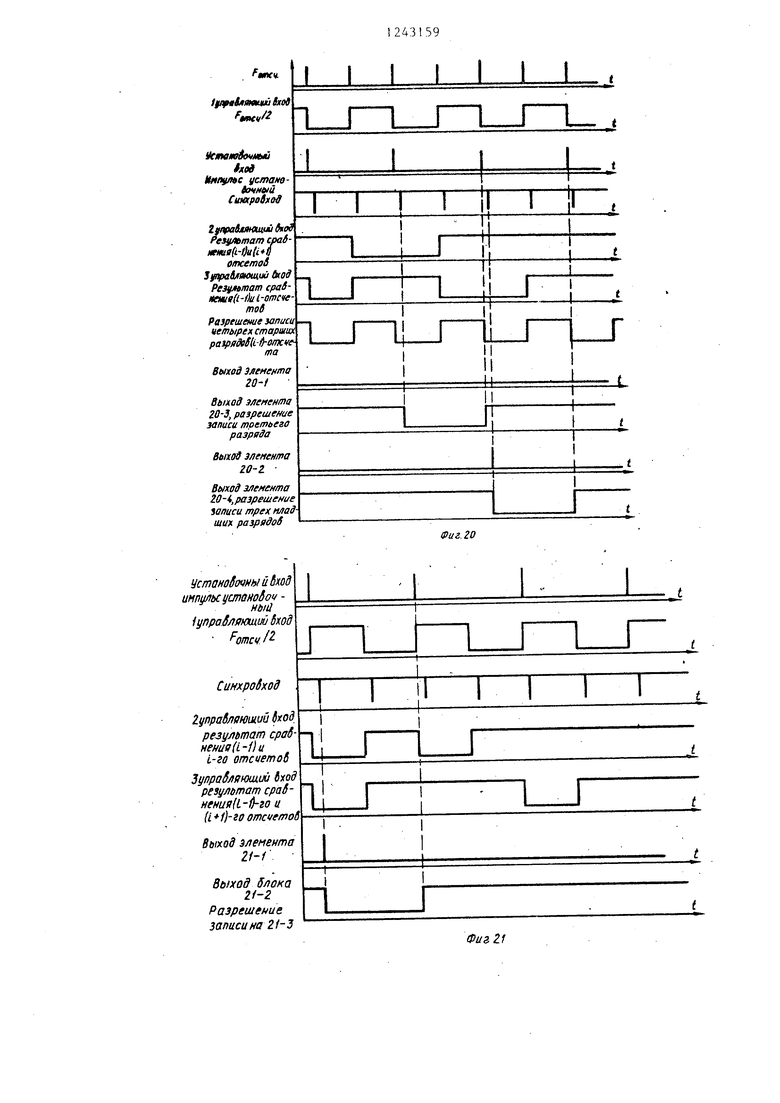

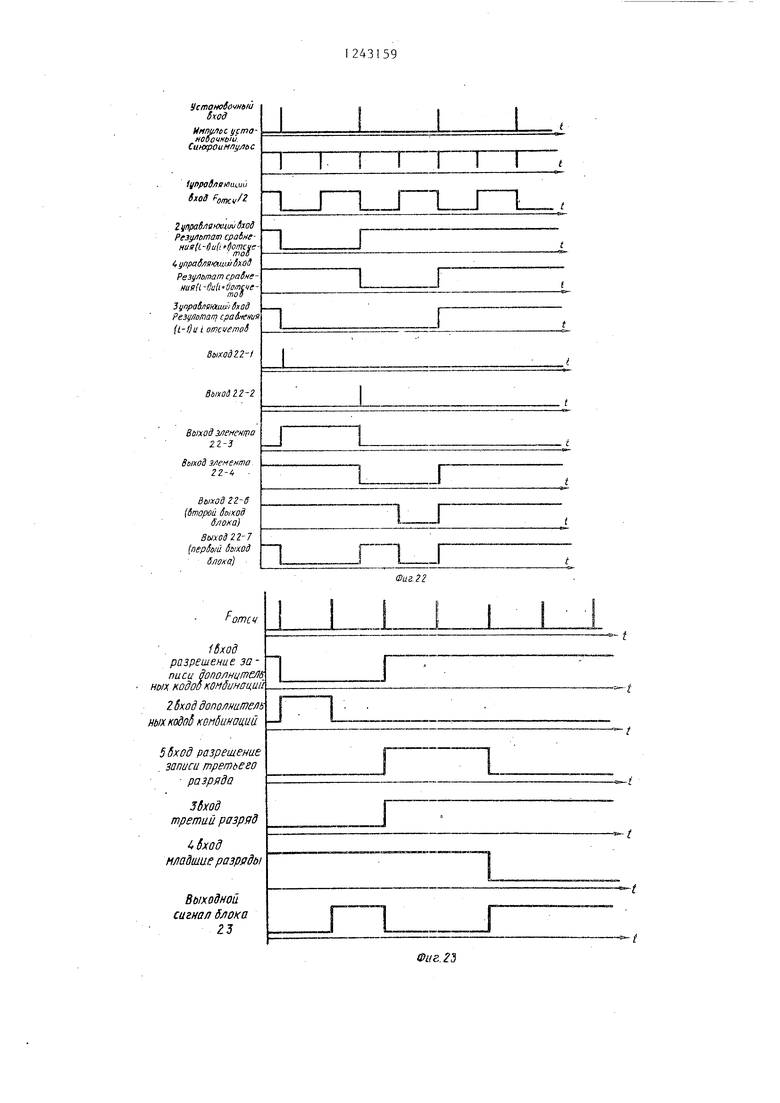

на фиг.18 - временные диаграммы работы блока управления; на фиг.19 - временные диаграммы работы.суммирующего регистра памяти; на фиг.20 - вре- менные диаграммы работы первого блока

разрешения записи; на фиг.21 - вре менные диаграммы работы второго блока разрешения записи;на фиг.22 - временные диаграммы работы третьего блока разрешения записи; на фиг.23 - временные диаграммы работы блока пилот-сигнала; на фиг.24 - временные диаграммы работы четвертого блока разреше- .ния записи.

Устройство для сжатия цифровых . телевизионных сигналов (фиг.1) содержит блок 1 установки опорного уровня, блок 2 аналого-цифрового преобразования, блок 3 управления, коммутатор 4, формирователь 5 кода синхронизации, элемент 6 задержки, суммирующий регистр 7 памяти, первы регистр 8 памяти, второй регистр 9 памяти, третий регистр 10 памяти, первый блок 11 сравнения, второй блок 12 сравнения, третий блок 13 сравнения, четвертый блок 14 сравнения, блок 15 выбора,-передаваемых символов, шифратор 16, блок 17 упра ления памятью, блок 18 памяти, блок 19 памяти младших разрядов, первый блок 20 разрешения записи, второй блок 21 разрешения записи, третий блок 22 разрешения записи, четвертый блок 23 разрешения записи, .блок 24 пилот-сигнала, дополнительный элемент 25 задержки, дополнительный блок 26 сравнения,

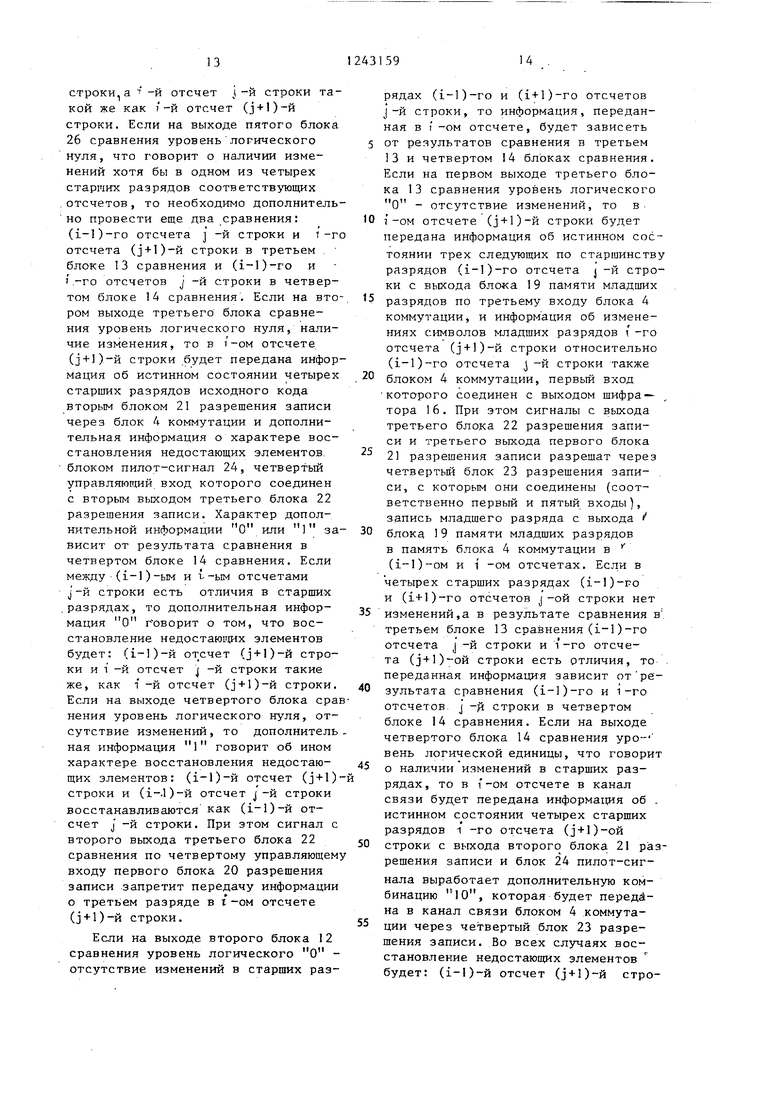

Блок аналого-цифрового преобразования (фиг.2) содержит аналого- цифровой преобразователь 27, генератор 28 опорного напряжения, тактовый генератор 29, формирователь 3 коротких импульсов,

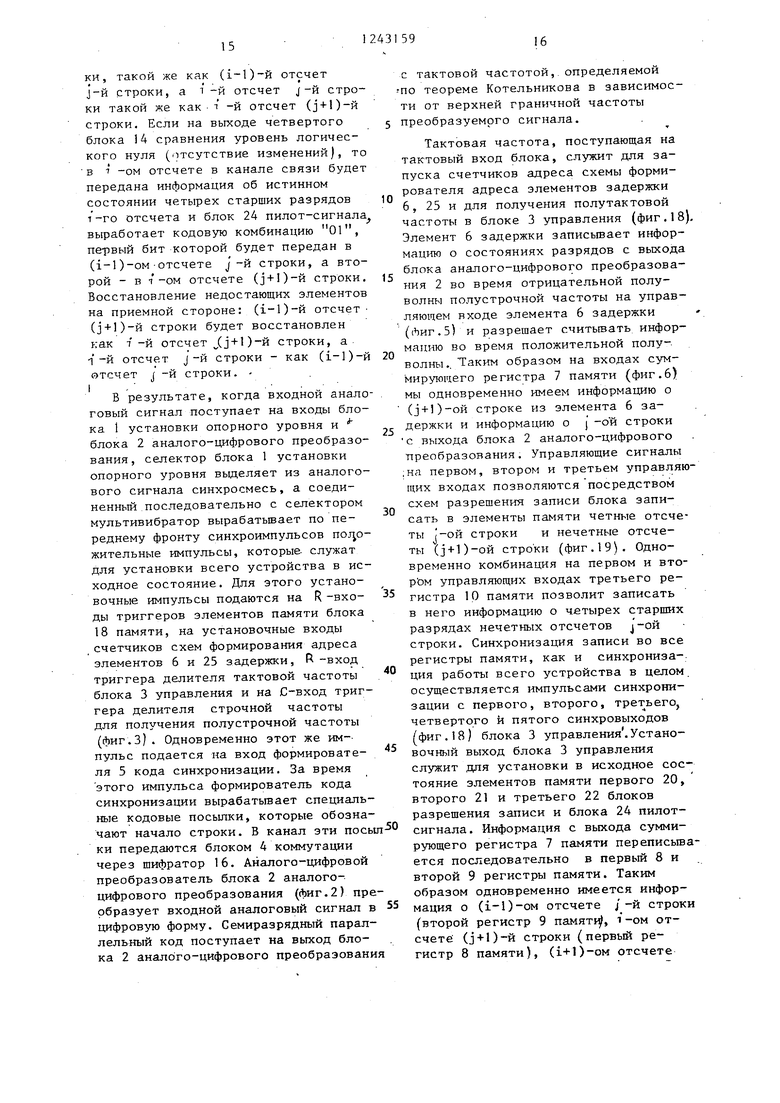

Блок управления фиг.З содержит делитель 31 тактовой частоты, делитель 32 строчной частоты, цифровую линию 33 задержки, элемент И-НЕ 34.

Коммутатор (фиг.4) содержит блок 35 выбора первого разряда кода канала, элементы ИЛИ-НЕ 36 и 37, элемент ИЛИ 38, блок 39 выбора второго разряда кода канала, блок 40 выбора третьего разряда кода канала, блок 41 выбора четвертого разряда кода . канала, блок 42 памяти кода канала.

Элемент задержки (фиг.5) содержит блок 43 формирования адреса, четырехразрядные счетчики 44-1,44-2 44-3, элемент 45 памяти, элемент 46-7 памяти одного разряда.

Суммирующий регистр памяти (фиг.6) содержит элементы ИЛИ-НЕ 47 и 48, блок 49 разрешения записи, элементы ИЛИ-НЕ 50-1,50-2, элементы 51 памяти, элемент 52-1 памяти одного разряда.

Второй блок сравнения (фиг.7) содержит блок 53 определения запрещенных изменений, блок 54 определения изменений, блок 55 выбора разрешенных изменений.

Блок управления памятью (фиг.З) содержит блоки 56-1...56-8 запрета., блоки 57-1...57-4 установки младших

43159 4

разрядов, блоки 58-1...58-6 выбора установки младпшх разрядов.

Блок памяти (фиг.9) содержит элементы 59-1...59-7 памяти раз- 5 рядов кода, элементы ИЛИ 60-1,60-2, элементы 61-1 и 61-2 памяти, цифровые дифференцирующие цепочки 62-1... 62-4, элементы ИЛИ 63-1 и 63-2.

Первый блок разрешения записи 10 (фиг.11) содержит элементы ИЛИ 64-1 и 64-2, элементы 65-1 и 65-2 памяти, элементы 66-1,66-2 и 66-3 совпадения, элементы НЕ 67-1 и 67-2.

Второй блок разрешения записи 15 (фиг.121 содержит элементы И 68,

элемент 69 памяти, блок 70 разрешения .

Третий блок разрешения записи (фиг.13) содержит элементы 71 и 72 20 совпадения, элементы 73 и 74 памяти, НЕ 75, элементы ИЛИ-НЕ 76 и 77. .

Четвертый блок разрешения запи- 25 си (фиг.14) содержит элементы 78-80 совпадения, элементы НЕ 81 и 82.

Блок пилот-сигнала (фиг. 15) содержит элемент ИЛИ/ИЛИ-НЕ 83, элементы 84 и 85 памяти, элементы 86 2Q и 87 совпадения, элемент НЕ 88, элемент ИЛИ 89, элементы ИЛИ-НЕ 90 и 91, элемент ИЛИ 92.

Второй элемент задержки (фиг.16) содержит бл.ок 93 формирования адреса, элементы 94 и 95 памяти, элемент НЕ 96.

Устройство для сжатия цифровых телевизионных сигналов работает следующим образом.

Входной сигнал поступает на аналоговый вход аналого-цифрового преобразователя 27, на который подается также напряжение с выхода генератора 28 опорного напряжения и к ороткие импульсы с выхода формирователя 30 коротких импульсов .

Блок 1 установки опорного уровня представляет собой последовательное соединение амплитудного селектора и мультивибратора.. Амплитудньй селектор выполнен по типовой схеме, на его вход поступает входной аналоговый телевизионный сигнал, а на выходе имеем смесь синхроимпульсов строчных и кадровых, по переднему фронту кото- рых мультивибратор вырабатьгоает короткие импульсы, служащие для установки соответствующих блоков и схем в исходное состояние.

40

5

Блок 3 управления содержит делители строчной 32 и тактовой 31 частоты. Делители собраны на 13 -триггерах в счетном режиме. На R-вход делите - § ля 31 тактовой частоты поступает установочный сигнал с выхода блока 1 установки опорного уровня, этот же сигнал поступает на С-вход делителя 32 строчной частоты. Выходные сигна- 10 лы снимаются с прямых и инверсных выходов триггеров. Одновременно тактовая частота поступает на вход цифровой линии 33 задержки, которая представляет собой последовательное 5 соединение элементов ИЛИ с отводами. Установочньй выход получается, при совпадении на элементе И-НЕ 34 шестого отвода цифровой линии задержки и инверсного выхода делителя 20 31 тактовой частоты. Коммутатор состоит из блоков выбора разрядов кода канала 35,39,40,41 и блока 42 памяти кода канала. Общий вход двух- . входовых элементов ИЛИ 35, 39,40,41 соответствует второму управляющему входу блока 4 коммутации, общий вход трехвходовых элементов ИЛИ 35,39,40, 41 соответствует первому управляющему входу блока 4 коммутации, с вто- 30 рым управляющим входом по ИЛИ объединяются разряды с второго входа блока 4 коммутации, с сигналом на первом управляющем входе объеди- . няются в блоках 35, 39, 40, 4 сигна- 35 лы с четвертого входа блока 4 коммутации. Кроме того, в блоках 35, 39 дополнительно объединены сигналы первого входа блока 4 коммутации, а а схемах 40 и 41 сигналы с третьего 40 входа блока 4 коммутации. Блок 42 амяти кода канала представляет собой линейку из пяти D -триггеров, на -входы которых заведены выходы блоков выбора разрядов кода каналов 35, 45 39, 40, 41, на пятый триггер сигнал с пятого вхада блока 4 коммутации, а на С-входы заведен синхро-сигнал синхровхода блока 4 коммутации. Выходы триггеров блока 42 памяти кода 50 канала являются выходами блока 4 коммутации и всего устройства. Фор- мирователь 5 кода синхронизации представляет собой мультиплексор, на входе которого задан определен- 55 ный код и которьй списьшается в«канал связи при прохождении установочных импульсов с выхода блока 1 установки (зпорного уровня. Первый элемент 6 задержки собран на элементах памяти объемом 1024 бита по одному на кажлый разряд и блоке 43 формирования адреса. Блок 43 формирования адреса представляет собой десятиразрядньй счетчик,последовательное соединение трех четырехразрядных, счетчиков, установка в исходное состояние которого производится импульсом с установочного входа элемента 6 задержки, а запуск - с, тактового входа. Выходы счетчиков подключены к соответствующим адресным входам элементов памяти. Перевод из режима записи в режим считывания производится по сигналу с управляющего входа, который соединен входом управления элементов памяти. Суымируюгчий регистр 7 (фиг. 6) представляет собой два элемента ИЛИ-НЕ 47 и 48, блок 49 разрещения записи, и элемент 51 памяти. На общий вход элементов ИЛИ-НЕ подан сигнал с первого управляющего входа суммирующего регистра 7 памяти, на два других входа поданы соответственно сигналы второго и третьего управляющих входов. Блок 49 разрешения записи представляет собой семь элементов ИЛИ-НЕ. На общие входы элементов поданы управляющие сигналы с выходо элементов ИЛИ-НЕ 47 и 48, а на другие входы информация с соответствующих выходов блока 2 аналого-циф- рового преобразования и элемента 6 задержки, выходы схемы 49 разреше-, ния записи поступают в элемент 51 памяти, представляющий собой линейку Т) -триггеров 52-1 , по одному на каждый разряд, входным является D-вход триггеров, на С-вход которых подан синхросигнал с синхровхода. Первый выход суммирующего регистра 7 памяти соответствует прямым выходам триггеров элемента 51 памяти, а второй выход - инверсным выходам D-триггеров. Первый 8 и второй 9 регистры памяти представляют собой линейки триггеров по одному на каждый разряд. Запись информации происходит по D-входу при поступлении на синхровход (С-вход триггеров) синх.росигнайов. Прямые выходы триггеров являются первыми выходами регистров, инверсные выходы - вторыми выходами регистров 8 и 9 памяти. Третий регистр 10 памяти представляет собой линейку из четырех D-триггеров для четырех старших разрядов и элемент ИЛИ, выход которой заведен на С-вход триггеров, а на входы поданы сигналы первого и второго управляющих входов и синхровхода. Выходом третьего регистра 10 памяти являются инверсные выходы триггеров. Пер- вый блок 1 сравнения (фиг.8 представляет собой три элемента Р1СКЛЮЧАЮ ЩЕЕ ИЛИ для трех младших разрядов , на одни входы которых поданы соответствующие младшие разряды с перво- го выхода второго регистра 9 памяти Выходы элементов ИСКЛЮЧАЮЩЕЕ ЯНН являются выходом блока. Второй, четвертый и пятый блоки сравнения выполнены по одинаковой схеме (фиг.7) и состоят из блока определения изменений 54, определения запрещенных изменений 53 и блока 55 выбора разрешенных изменений. Блок 54 определени изменений представляет со бой четы-

ре элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, которые производят сравнение четырех старших разрядов, поступающих на первый и второй входы блока 12. Блок 53 определения запрещенных изме- нений также состоит из элементов ИСКЛЮЧАЮ ЦЕЕ ИЛИ,. соответствующие выходы которых объединены по ИЛИ, блок выбора разрешенных изменений состоит из элементов ИЛИ и ИЛИ-НЕ, которые с учетом запретов от блока 53 пропускают информацию о наличии изменений хотя бы в одном из четырех старших ра.зрядов, полученную в блоке 54. Второй выход блоков 12 и 14 сравнения является инверсией первого выхода. Третий блок 13 сравнения представляет собой объединение по ИЛИ четырех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, на входы которых заведены четыре старших разряда с первого и второго входов. Блок 15 выбора передаваемого символа представляет собой два блока запрета- {фиг.В) . Наличие изменение символа в более стар- шем разряде блока 11 запрещает прохождение информации об изменении символа в более младшем разряде в блоке 15. Выходы блока 15 являются инверсией один относительно друго- го. 11 ифратор 16 представляет собой собственно шифратор и элементы ИЛИ, объединяющие выход и второй вход

шифратора 16. Их выход является выходом 1 тифратора 16. Блок 17 управления памятью (фиг.81 представляет собой восемь блоков 56-1...56-8 запрета, четыре блока 57-1 ... 57-4 установки младших разрядов, шесть блоков 58-1 .. .58-6 выбора установки младших разрядов. Блоки 57-1 и 57-2 установки младших разрядов устанавливают одновременно три младших разряда блока 18 памяти при записи в него информации об истинном состоянии четырех старших разрядов, для этого их выходы подаются соответственно на R и S -входы триггеров элементов памяти трех младших разрядов блока 18 памяти. Блоки 57-3 и 57-4 установки младших разрядов устанавливают два младших разряда блока 18 памяти, для чего их выходы также поданы на R и S-входы триггеров элементов памяти блока 18 ти. Для установки младших разрядов лишь от самого старшего, из изменив- Ш1-ГХСЯ разрядов служат блоки 56-1 . . . 56-8 запрета, на один вход которого подаются продифференцированные им- пульсы с прямых выходов триггеров старших разрядов блока 18 памяти, а на вторые запрещающие входы - с

инверсных выходов триггеров блока

I

18 памяти. Для установки младших

разрядов в соответствии с принятым алгоритмом обработки по сигналам от блока 15 выбора передаваемого символа слул.-ат блоки 58-1...58-6 выбора установки младших разрядов, объединенные выходы которых соответствуют первому входу блока 17 управления памятью, а на вторые входы подается информация с прямых и инверсных выходов элементов памяти младших разрядов блока 18 памяти. Выходы блоков 58-1...58-6 выбора установки младших разрядов также подаются на

R и S -входы триггеров элементов I

памяти блока 18 памяти. Блок 18 памяти представляет собой семь, по одному на каждьш разряд, элементов памяти 59-1 .. .59 (фиг .9) . Четыре элемента 59-1...59-4 памяти для старших разрядов собраны по одинаковой г схеме И представляют собой элемент ИЛИ (на фиг.9 раскрыт один элемент из четырех), элемент памяти и цифровые дифференцирующие цепи. Сигнал с установочного входа подается на

ft-вход триггеров , на которых собраны элементы памяти, на С-вход подан сигнал с синхровхода, на D -вход подается сигнал с выхода элемента ИЛИ, на вход которого заведены.сигналы с второго и четвертого входов блока 18 памяти. Выходы элемента памяти подключены к дифровЫм дифференцирующим цепочкам, выполнены по Типовой.схеме. Элементы памяти для младших разрядов 59-5.,,59-7 отличаются добавлением элементов 1-1ЛИ для третьего разряда, расширяющими возможность установки триггеров эле- ментов памяти в нужное состояние по R и S -входам. У элементов 59-6 и 59-7 памяти отсутствуют цифровые дифференцирующие цепочки. Входным сигналом для них является третий вход блока 18 памяти, Первый выход блока 8 памяти образуют прямые выходы триггеров элементов 59-5,59-6,Г 59-7 памяти. Второй выход блока 18 памяти образуют выходы цифровых диф- ференцирующих цепочек элементов 59-1.,-.59-5 памяти прямые и инверсные входы триггеров элементов 59-5. 59-7 памяти.Блок 19 памяти младших разрядов представляет собой линейку (фиг,10) из трех триггеров, на D-входы которых поданы младшие раз- .ряды кода с второго выхода первого блока 2П. Первый блок 20 разрешения записи представляет собой (фиг,11) два элемента И 64-1, 64-2, два элемента 65-1 и 65-2 памяти, три блока 66-1,66-2,66-3 совпадения и элемент НЕ 67-1, На оба элемента И подаются сигналы с синхровхода, первого и второго управляющих входов, на элемент 64-2 еще подан сигнал с третьего управляющего входа. Выходы элементов И 64-1 и 64-2 подключены к S-входам триггеров элементов 65-1 и 65-2 гсамяти, на R -входы которых заведен сигнал с установочного входа. Первый блок совпадения пропускает на выход четыре старших разряда с выхода первого блока 20 разрешения записи при совпадении их с сигналом на первом управляющем входе, второй блок совпадения пропускает третий разряд при разрешении на выходе элемента 65-1 памяти и четвер- том управляющем входе, третий блок совпадения пропускает три младших разряда при соответствующем состоя

5 0 . 5 0 5 5 5

0

0

НИИ элемента 65-2 памяти, выходы третьего разряда схем 66-2 и 66-3 объединены и вместе с выходами остальных двух младших разрядов схемы 66-3 являются вторым выходом первого блока 20 разрешения записи. Выход элемента 65-1 памяти является третьим выходом первого блока 20 . разрешения записи. Второй блок 21 разрешения записи представляюет собой (фиг, 12,) элемент И 68, элемент 69 памяти и блок 70 разрешения. На входы элемента .И подаются сигналы с второго и третьего блока. Выход элемента И подается на -вход р-триггера элемента 68 памяти, на R-вход которого подается сигнал с .установочного входа.блока. Выход триггера и сигнал первого управляющего входа является разрешающим сиг-, налом для блока 70 разрешения, который представляет собой четыре схемы ШШ-НЕ., но одной па каждый разряд, на один вход которых подан сигнал с выхода блока 69, а на другие входы - сигнал с первого управляющего входа и входа второго блока 21 разрешения записи,, выходом которого являются . выходы элементов ИЛИ-НЕ блока 70 разрешения,- Третий блок, разрешения записи (фиг,13) представляет собой два блока 71 и 72 совпадения, два элем:ента 73 и 74 памяти, элемент НЕ, два элемента ИЛИ-НЕ. При совпадении на первой 71 или второй 72 схеме совпадения на их выходе получается короткий импульс, который управляет триггером элемента 73 или 74 памяти. Установка их в исходное состояние производится импульсами с установочного входа, который заведен на R-вход триггеров. Выходы триггеров элементов 73 и 74 памяти объединены по Р-ШИ согласно схеме (фиг, 13),. Четвертый блок 23 разрешения записи

(фиг.14) представляет собой два элемента НЕ 81 и 82 и три блока 78 - 80 совпадения, выходы которых объединены по ИЛИ и являются .выходом блока 23. На входы первого блока 78 совпадения поданы сигналы второго и первого входов блока 23, . на второй блок 80 совпадения поданы сигналы третьего и проинвертирован- ных сигналов первого и пятого входов, на третий блок совпадения поданы сигналы четвертого, пятого и проинвертированного первого входа блока 23. Блок пилот-сигнал а 24 ( фиг . 1 5 представляет собой элемент {-ШИ/ИЛИ- НЕ 83, два элемента 84 и 85 памяти, два элемента ИЛИ-НЕ 90 и 91, два блока 86 и 87 совпадения, элемент НЕ 88 два элемента ИЛИ 89 и 92. На вход элемента 83 подается сигнал с -второго управляющего входа блока 24 пи- лот-сигнала, а выходы его прямой и инверсный подаются на D -входы триггеров элементов 84 и 85 памяти, на С-входы 84 подан сигнал с выхода блока 90, а на С-вход 85 подан объе- диненный по ИЛИ на блок 92 сигнала блоков 90 и 91. На R -входы подан установочный сигнал, выходы элементов 84 и 85 памяти поданы на блоки 86 и 87 совпадения, на вторые входы которых подан сигнал с первого управляющего входа блока 86, проинверти- рованный сигнал с первого управляющего входа блока 87. Выходы блоков совпадения объединены по ИЛИ на элементе 89. Второй элемент 25 задержки (фиг.16) представляет собой блок 93 формирования адреса, два элемента и 95 памяти, элемент НЕ 96. Управление блоком 93 формиро- вания адреса JH ее соединения с элеметами памяти аналогичное как и у первого элемента 6 задержки (фиг.5). Элемент 96 управляет режимом Запись считывание элементов памяти. -

Информация, передаваемая в канал связи, зависит от результатов сравнения четырех старших разрядов соответствующих отсчетов, соответствующих строк во втором, третьем и четвертом и пятом блоках 11 - 14 сра нения, и является результатом двумерной обработки исходного, цифрового сигнала. Элементы j -и строки передаются в канал связи через четные отсчеты информацией об истинных значениях разрядов исходного кода коммутатора 4, второй вход которого соединен с вторым выходом второго регистра 9 памяти. Элементы (+1)-й строки передаются в канал связи- коммутатором 4 также через отсчет информацией, зависящей от результатов сравнения: во втором блоке 12 сравнения на первый и второй входы кото- ррго поданы с вторых выходов второго регистра 9 памяти и суммирующего регистра 7 памяти соответственно

5 0 5 0 5 0 5

0

5

четыре старших разряда (j-l)-ro и (j+l)-ro отсчетов j -ей строки; в третьем блоке 13 сравнения, на первый вход и второй вход которого поданы четыре cTapmix разряда с вторых выходов второго и первого регистров 9 и 8 памяти соответственно (i- l)-ro отсчета j -и строки и 1-го отсчета (j+l)-й строки; в четвертом блоке 14 сравнения на первый . и второй входы которого поданы четыре старших разряда с второго выхода второго регистра 9 памяти и . выхода третьего регистра 10 памяти соответственно (i-l)-ro и i-ro отсчетов J -и строки, а также в дополнительном блоке 26 сравнения на первый и второй входы которого поданы четыре старших разряда с второго выхода второго регистра 9 памяти и выхода второго элемента задержки соответственно (1-1)-й отсчет j -и строки и (1-1)-й отсчет (+2)-й строки. Если в результате сравнения (i-l)-ro и (i+l)-ro отсчетов j-и строки окажется, что хотя бы в одном из старших разрядов есть изменения, то в (i-l)-oM отсчете j -и строки будет передана информация об истинном состоянии пяти старших разрядов кода. Информация о пятом разряде будет передана .вместе с информацией об истинном состоянии четырех старших разрядов четвертым блоком 23 разрешения записи, третий вход которого соединен с вторым выходом второго регистра 9 памяти, а выход соединен с третьим входом блока 4 коммутации. В i -ом отсчете (j+l)-й строки также будет передана информация об истинном состоянии пяти разрядов исходного кода. Если пятый блок сравнения имеет на выходе уровень логической единицы, это говорит о том, что между (1-1)-ми отсчетами j-й и (+2)-й строки нет отличий в четырех старших разрядах. При этом четыре старших разряда передаются блоком 4 коммутации, четвертый вход которого соединен с выходом второго блока 21 разрешения з а писи, а пятый разряд будет передан также, как и в предьщущем случае. При этом восстановление недостающих элементов будет следующим: (1-1)-й отсчет (+1)-й строки восстанавливается как 1 -и отсчет J -и

строки а -и отсчет j -и строки такой же как ; -и отсчет (j + l)-ft строки. Если на выходе пятого блока 26 сравнения уровень логического нуля, что говорит о наличии изменений хотя бы в одном из четырех старших разрядов соответствующих отсчетов, то необходимо дополнительно провести еще два сравнения: (i-l)-ro отсчета -и строки и 1-г отсчета (j+l)-A строки в третьем , блоке 13 сравнения и (i-l)-ro и .-го отсчетов j -и строки в четвертом блоке 14 сравнения. Если на вто ром выходе третьего блока сравнения уровень логического нуля, наличие изменения, то в /-ом отсчете. (д+)-й строки будет передана информация об истинном состоянии четырех старших разрядов исходного кода вторым блоком 21 разрещения записи через блок 4 коммутации и дополнительная информация о характере восстановления недостающих элементов. блоком пилот-сигнал 24, четвертый управляющий вход которого соединен с вторым выходом третьего блока 22 разрешения записи. Характер дополнительной информации О или 1 за висит от результата сравнения в четвертом блоке 14 сравнения. Если между (i-l)-ым и t-ым отсчетами J-й строки есть отличия в старших .разрядах, то дополнительная инфор- мация О Говорит о том, что восстановление недостаю1цих элементов будет: (i-l)-и (j + l)-й строки и 1 -и отсчет J -и строки такие же, как 1 -и отсчет (з+1)-й строки. Если на выходе четвертого блока сранения уровень логического нуля, отсутствие изменений, то дополнительная информация 1 говорит об ином характере восстановления недостаю- щих элементов: (i-l)-и отсчет (+1) строки и (i-Л)-й отсчет j-и строки восстанавливаются как (i-l)-и отсчет J -и строки. При этом сигнал с второго выхода третьего блока 22 сравнения по четвертому управляющем входу первого блока 20 разрешения записи запретит передачу информации о третьем разряде в t-ом отсчете ( + 1)-й строки.

Если на выходе второго блока 12 сравнения уровень логического О - отсутствие изменений в старших разрядах (i-l)-ro и (i+l)-ro отсчетов J-и строки, то информация, переданная в f -ом отсчете, будет зависеть от результатов сравнения в третьем 13 и четвертом 14 блоках сравнения. Если на первом выходе третьего блока 13 сравнения уровень логического О - отсутствие изменений, то в- 1-ом отсчете (+1)-й строки будет передана информация об истинном состоянии трех следующих по старшинств разрядов (i-l)-го отсчета j -и строки с выхода блока 19 памяти младших разрядов по третьему входу блока 4 коммутации, и информация об изменениях символов младших разрядов ( -го отсчета (+)-й строки относительно (i-l)-го отсчета j -и строки также блоком 4 коммутации, первый вход которого соединен с выходом шифратора 16. При этом сигналы с выхода третьего блока 22 разрешения записи и третьего выхода первого блока 21 разрешения записи разрешат через четвертьп блок 23 разрешения записи, с которым они соединены (соответственно первый и пятый входы), запись младшего разряда с выхода блока 19 памяти младших разрядов в память блока 4 коммутации в (i-l)-ом и 1 -ом отсчетах. Если в четырех старших разрядах (i-l)-Fo и (i+l)-ro отсчетов j-ой строки нет изменений,а в результате сравнения в третьем блоке 13 сравнения (i-l)-го отсчета j -и строки и 1-го отсчета (з+1)-ой строки есть отличия, то переданная информация зависит от ре - зультата сравнения (i-l)-го и i-го отсчетов, j -fi строки в четвертом блоке 14 сравнения. Если на выходе четвертого блока 14 сравнения уро- вень логической единицы, что говорит о наличии изменений в старших разрядах, то в i -ом отсчете в канал связи будет передана информа1;ия об . истинном состоянии четырех старших разрядов 1 -го отсчета ()-oй строки с выхода второго блока. 21 разрешения записи и блок 24 пилот-сигнала выработает дополнительную комбинацию 10, которая будет передй- на в канал связи блоком 4 коммутации через четвертый блок 23 разрешения записи. Во всех случаях восстановление недостающих элементов будет: (i-I)-й отсчет (з+1)-й стро

ки, такой же как (1-1)-й отсчет j-й строки, а 1-й отсчет j-и строки такой же как т -и отсчет (з + 1)-й строки. Если иа выходе четвертого блока 14 сравнения уровень логического нуля (отсутствие изменений), то В 1 -ом отсчете в канале связи будет передана информация об истинном состоянии четырех старших разрядов 1-го Отсчета и блок 24 пилот-сигнала выработает кодовую комбинацию 01, пе-рвый бит которой будет передан в (i-1 )-ом-отсчете J-й строки, а второй - в ч -ом отсчете (з + 1)-й строки. Восстановление недостающих элементов на приемной стороне: (1-1)-й отсчет (д+1)-й строки будет восстановлен как 7 -и отсчет +1)-й строки, а -{-и отсчет J-й строки - как (i-1)-и отсчет J -и строки. I . - - .

В результате, когда входной аналоговый сигнал поступает на входы блока 1 установки опорного уровня и блока 2 аналого-цифрового преобразования, селектор блока 1 установки опорного уровня вьщеляет из аналогового сигнала синхросмесь, а соединенный .последовательно с селектором мультивибратор вырабатьшает по переднему фронту синхроимпульсов жительные импульсы, которые- служат для установки всего устройства в исходное состояние. Для этого установочные импульсы подаются на R-вхо- ды триггеров элементов памяти блока 18 памяти, на установочные входы счетчиков схем формирования адреса элементов 6 и 25 задержки, R -вход триггера делителя тактовой частоты блока 3 управления и на С-вход триггера делителя строчной частоты для получения полустрочной частоты (Лиг.З). Одновременно этот же им-- пульс подается на вход формирователя 5 кода синхронизации. За время этого импульса формирователь кода синхронизации вырабатьгоает специальные кодовые посьтки, которые обозначают начало строки. В канал эти посы ки передаются блоком 4 коммутации через шифратор 16. Аналого-цифровой преобразователь блока 2 аналого- цифрового преобразования (фиг.2) преобразует входной аналоговый сигнал в цифровую форму. Семиразрядный параллельный код поступает на выход блока 2 аналого-цифрового преобразовани

5

j Ю 15 0

5 О 5

0

0

5

с тактовой частотой, определяемой -по теореме Котельникова в зависимости от верхней гранично; частоты преобразуемого сигнала.

т

Тактовая частота, поступающая на тактовый вход блока, служит для запуска счетчиков адреса схемы формирователя адреса элементов задержки 6, 25 и для получения полутактовой частоты в блоке 3 управления (фиг . 1 8), Элемент 6 задержки записьшает информацию о состояниях разрядов с выхода блока аналого-цифрового преобразования 2 во время отрицательной полуволны полустрочной частоты на управляющем входе элемента 6 задержки (Лиг.5) и разрешает считывать информацию во время положительной полуволны., Таким образом на входах сум- мируюгаего регистра 7 памяти (фиг.6) мы одновременно имеем информацию о (з-ь1)-ой строке из элемента 6 задержки и информацию о j -ои строки

с выхода блока 2 аналого-цифрового преобразования. Управляющие сигналы

;на первом, втором и третьем управляющих входах позволяются посредством схем разрешения записи блока записать в элементы памяти четные отсчеты ( строки и нечетные отсчеты ()-ой строки (фиг. 19). Одновременно комбинация на первом и вто- р ом управляющих входах третьего регистра 10 памяти позволит записать в него информацию о четырех старших разрядах нечетных отсчетов j-ой строки. Синхронизация записи во все регистры памяти, как и синхрониза-. ция работы всего устройства в целом осуществляется импульсами синхронизации с первого, второго, третьего, четвертого и пятого синхровыходов (фиг. 18) блока 3 управления .Установочный выход блока 3 управления служит для установки в исходное состояние элементов памяти первого 20, второго 21 и третьего 22 блоков разрешения записи и блока 24 пилот- сигнала. Информация с выхода суммирующего регистра 7 памяти переписьгоа- ется последовательно в первый 8 и второй 9 регистры памяти. Таким образом одновременно имеется информация о (i-i)-OM отсчете j -и строки (второй регистр 9 памят, i-ом отсчете (+1)-й строки (первый регистр 8 памяти), (i+l)-OM отсчете

j-й строки (суммирующий регистр 7 памяти), четыре старших разрядах V-го отсчета j-ой строки (третий регистр 10 памяти). При этом во вто- ром элементе 25 задержки хранится информация из предыдущего цикла - работы о четырех старших разрядах (i-l)-ro отсчета (j+2)-й строки. Задержку на время, равное длитель ности двух строк, позволяют осуществить два (фиг.16} элемента 94 и 95 памяти.

Дальнейшая работа устройства зависит от результатов сравнения во втором 12, третьем 13, четвертом 14 и дополнительном 26 блоках сравнения .

Если на первом выходе блока 12 сравнения, на первый и второй входы которого поданы четыре старших разряда с вторых выходов соответственно суммирующего регистра 7 памяти и второго регистра 9 памяти, уровень логического О, что говорит о наличии изменений хотя бы в одном из старших разрядов, а на выходе пятого блока 26 сравнения, на входы которого поданы четыре старших разряда с выхода второго элемента задержки 25 и второго выхода второго регистра 9 памяти соответственно (i-l)-e отсчеты Сз+2)-ой и /-Й строк, уровень логической единицы (отсутствие изменений), то первый блок ,20-разрешения записи (фиг.11) через блоки 66-1 и 66-2 совпадения (фиг.20) запрппет в блок 18 памяти информацию об истинном состоянии пяти разрядов исходного кода. При этом оставшиеся два младших разряда будут установлены в состояние в соответствии с принятым алгоритмом по кольцу обратной связи:второй выход блока 18 памяти - второй вход блока 17 управления памятью - блок 18 памяти. Установку двух младших разрядов будут производить блоки установки младших разрядов (фиг.8.Блоки 56-1,...,56-8 запрета выбирают самый старший из разрядов, В котором произошло изменение :при записи истинного состояния пяти разрядов кода, а выходы блоков 57-3 и 57-4 установки млад гаих разрядов заведены на ft и S -входы триггеров элементов памяти (фиг.9) через элементы ИЛИ таким

обра.зом, что при изменении состояния старшего из изменившихся разрядов О - 1, младшие разряды устанавли- 5 ваются в О и наоборот. Одновремен- но в канал связи посредством четвертого блока 23 (фиг.14) разрешения записи, на третий вход которого заведена информация о третьем разря- 10 де и на пятый вход которого заведена информация с элемента 65-1 памяти первого блока 20 разрешения записи, с второг.о выхода второго регистра 9 памяти будет также передана информа- ция об истинном состоянии пяти разрядов кода. Поскольку данный результат сравнения во втором блоке 12 сравнения запоминается на элементе 65-1 памяти в первом блоке 20 разре- 20 шения . записи на два отсчета, то в следующем отсчете характер работы устройства сохраняется. При этом сле- дует уч:есть, что при сравнении четырех старших разрядов во втором бло- 25 ке 12 сравнения, как и в четвертом 14 и пятом 26 блоках сравнения, сравнение происходит с учетом запрещенных изменений. Запрещенные изменения определяются блоком 53 (фиг.7) 0 блока 12. В качестве запрещенных считаются изменения символов старших разрядов между двумя отсчетами сле- дующего вида:

1000-0111, 0111-1000, 0100-0011, 5 0011-0100, 1100-1011, 1011-1100, 0010-0001, 0001-0010, 0110-0101, 0101-0110, 1010-1001, IOOI-10 IO, inO-llOJ, 1101-1110 и все изменения младшего из четырех старших 1) разрядов.

Если на выходе пятого блока 26 сравнения уровень логического нуля (наличие изменений, то информация, переданная в i-ом отсчете (з + 1)-й

5

строки будет зависеть от результата сравнения (i-l)-ro отсчета J-и строки и 1-го отсчета (з+1)-й строки, которое производится третьим блоком 14 сравнения. Если в этих

отсчетах есть изменения хотя бы в одном из старших разрядов, то в i-OM отсчете j-и строки будет передана информация об истинном состоянии четырех старших разрядов вторым

блоком 21 разрешения записи (фиг.21). Пятый бит этой кодовой посыпки будет занят на передачу дополнительной информации, зависящей от результата

сравнения в (1-)-ом и г -ом отсче так J -и строки. Для этого в третье блоке 22 разрешения записи (фиг.13) произойдет совпадение сигналов и сработает элемент 74 памяти. Сигнал с второго выхода этого блока запретит передачу третьего разряда в блок 18 памяти и в канал связи, для этого второй выход блока 22 соединен с четвертым управляющим входом первого блока 21 разрешения записи, и одновременно разрешит запись допо нительной кодовой комбинации в блок 24 пилот-сигнала. При этом передается дополнительная информация в виде О, если между (i-l)-biM и i-ым отсчетами J-ой строки нет отличий, в противном случае передается 1. Если второй блок 12 сравнения говорит об отсутствии измене ний в четырех старших разрядах (уровень логического О на втором выходе и логической J на первом выходе, то работа устройства будет зависеть от результата сравнения в третьем блоке 13 сравнения, на входы которого соответственно поданы четыре старши разряда с вторых выходов первого 8 и второго 9 регистров памяти. Если на первом выходе третьего блока 13 сравнения уровень логического О (отсутствие изменений),что в первом блоке 20 разрешения записи на элементе И 64-2 произойдет совпадение соответствующих сигналов и триггер элемента 65-2 памяти разрешит через блок 66-3 совпадения запись в блок 18 памяти, кроме четырех старших разрядов, которые записываются через блок 66-1 совпадения, трех следующих по старшинству разрядов (фиг.20. Одновременно эти же три разряда будут записаны в блок 19 памяти младших разрядов и с его выхода в следующем отсчете информация об этих разрядах будет переда- на в канал связи блоком 4 коммутации, третий выход которого соединен с выходом блока 19 памяти младших разрядов. Причем четвертый блок 23 разрешения записи передает запись информации о третьем разряде в кана связи дважды, в этом и следующем отсчете.

Разрешающими сигналами являются сигналы с третьего выхода первого блока 20 разрешения записи и выхода

второго блока 21 разрешения записи. Вместе с информацией о трех младших разрядах в следующем отсчете будет 5 передана информация об изменениях символов, в трех младших, разрядах. Для этого в первом блоке 11 сравнения (фиг.в) производится сравнение трех младших разрядов блока 18 памя0 ти и второго регистра 9 памяти. Информация о всех изменениях с выхода первого блока 11 сравнения поступает на вход блока 15 выбора передаваемого символа, который выбирает стар5 ший из изменившихся разрядов, а затем посредством блока управления памятью схемами выбора установки младших разрядов установит младшие разряды в соответствующее состояние. Шифра0 тор 16 кодирует номер изменившегося разряда двоичным кодом и передает в канал связи блоком 4 коммутации. Если третий блок сравнения говорит о наличии изменений хотя бы в одном

5 из четырех старших разрядов, то

работа устройства определяется чет- вертьтм блоком 14 сравнения, на которого поданы четыре старших разряда с второго выхода второго регист0 ра 9 памяти и выхода третьего регистра 10 памяти. Эта ситуация выделяется элементом И (фиг.22) второго блока 21 (фиг.12 ) разрешения записи и запоминается элементом памяти, ко- 5 торый разрешает запись информации о четырех старших разрядах в блок 18 памяти и в канал связи через блок 4 коммутации, четвертый вход которого соединен с выходом второго блока 21

0 разрешения записи, в этом и следую/

щем отсчетах независимо от выхода четвертого блока 14 сравнения. Выход-, ной сигнал четвертого блока 14 сравнения служит для формирования допол5 нительных кодовых комбинаций в блоке 24 пилот-сигнала ( фиг.15|. Для этого на вход D-триггеров элементов памяти подается сигнал с выхода четвертого блока 14 сравнения. Синхросигнал

0 на С-вход триггеров поступает при соответствующем разрешении с выходов третьего блока разрешения записи. Таким образом, если на входе четвертого блока сравнения уровень логичес5 кого нуля и на третьем управляющем входе также уровень логического нуля, то в элементах памяти будет записана дополнительная кодовая информация 01 (фиг.24), в противном случае - 10, Эти комбинации передаются через четвертый блок разрешения записи в блок 4 коммутации последовательно: первый бит дополнительной кодовой комбинации в одном отсчете, другой - в другом. Если разрешение присутствует на четвертом управляющем входе, то дополнительная информация в виде О или Г в зависимости от сигнала на втором управляющем входе блока 24 записывается только в один элемент и передается соответственно только во втором отсчете,

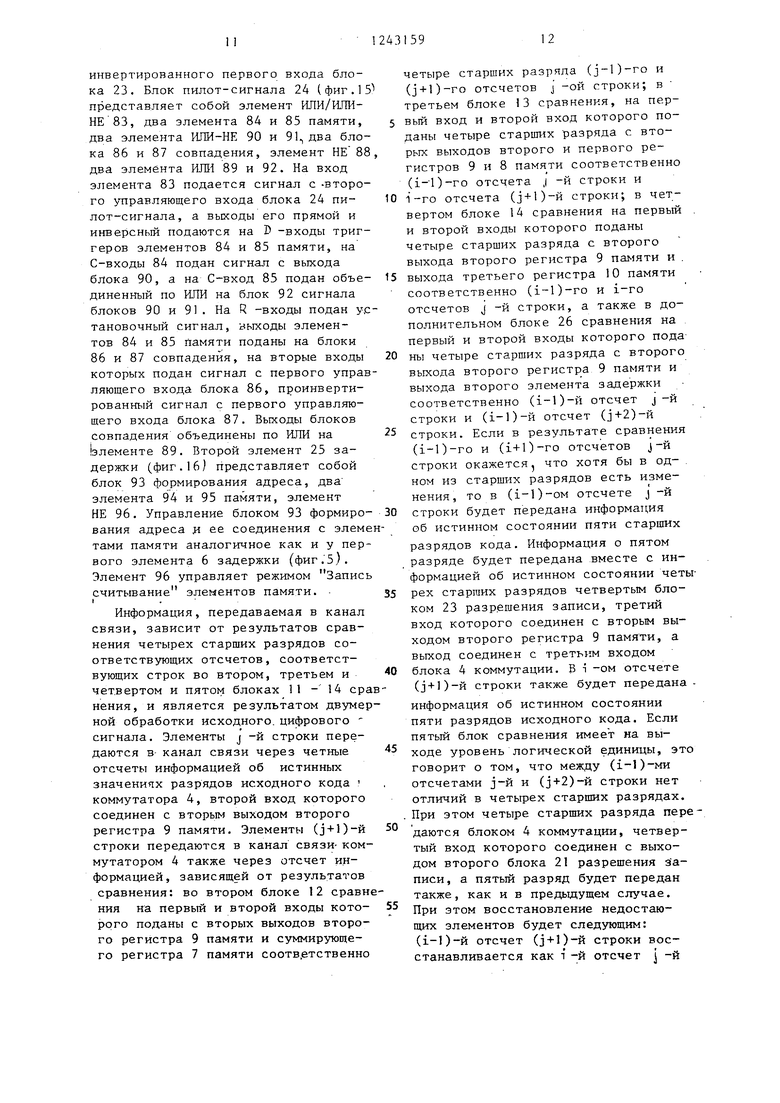

В таблице приведен алгоритм работы устройствасжатия цифровых телевизионных сигналов.

Формула изобретени Я

Устройство для сжатия циф ровых телевизионных сигналов по авт,св. № 1146831, отличающееся тем, что, с цельк: уменьшения искажений телевизионных сигналов, в него введены дополнительный элемент задержки и дополнительный блок сравнения, при этом информационный вход

догюлнительног о элемента задержки соединен с вторым выходом блока памяти, установочный вход - с выхо- дом блока установки опорного уровня, тактовый вход - с тактовым выходом блока аналого-цифрового преобразования, управляющий вход - с nepBbtNt выходом блока управления, а вькод -. с

первым входом дополнительного блока

сравнения, второй вход которого соединен с вторым выходом второго регистра памяти, выход подключен к первому дополнительному управляющему

входу третьего блока разрешения записи, второй .дополнительный управляющий вход которого соединен с выходом., четвертого блока сравнения, третий дополнительный управляющий

вход соединен с первым выходом третьего .блока сравнения, дополнительный установочный вход соединен с установочным выходом блока управления, дополнительный синхровход соединен с

четвертым синхровыходом блока управления, дополнительный выход соединен с дополнительным управляющим входом первого блока разрешения записи и дополнительным управляющим входом блока пилот-сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для кодирования телевизионных сигналов | 1986 |

|

SU1356259A1 |

| Устройство для сжатия цифрового телевизионного сигнала | 1985 |

|

SU1285626A1 |

| Устройство для сжатия цифровых телевизионных сигналов | 1982 |

|

SU1059702A1 |

| Устройство для сжатия цифровых телевизионных сигналов | 1984 |

|

SU1238268A2 |

| Устройство управления процессора двухмерного преобразования Фурье | 1982 |

|

SU1121677A1 |

| Преобразователь телевизионных стандартов | 1987 |

|

SU1506591A1 |

| АССОЦИАТИВНЫЙ ПРОЦЕССОР | 1988 |

|

SU1521118A1 |

| Устройство для разделения коррелограмм | 1987 |

|

SU1432558A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1522272A1 |

Изобретение является дополнительным к устройству по. основному авт.св. № 1146831. Уменьшаются искажения телевизионного сигнала за счет уменьшения искажений наклонных контуров. Входной сигнал поступает . на блок 1 установки опорного уровня и на блок 2 аналого-цифрового преоб« (Л to 4 оо ел N0

Фив.2

Гакгпобый быхой

SJk8i .JJO ,iej9

jk.ZO,Zi,2Z,24

Выходы поаутактавой nacmomoi

Вшоды полустрочнои Устанобка частоты20,Zf,2Z,2

%г5

3-й бход

бход 4-й бход 2-й бхоУ Нупрабл.бход 2--U tinpa6/ SxQd

5-uSxod

Синхробход

52 с

44-f

SzVSbu

Упра6/ яЮ{цчй ход

Вход

С

Дг

44-

44-J

сг

ДдС&й

% L

л

6-L

I

d

W-JTJ

Зиправляемый ход

t

i-uyt S/Jj Sxod

2-йупра / Янщий Sxod

входы .Smofou пербый.

I

Санхробход

50-f

50-2

4S

-r

ГР

5ГГ 1

51

I a

Фиг. a

Второй перёша 5iiixodb

Пердый Sxod

1

Второй Ёход

I

Фиг. 7

ttfttiu впав в/порей

Фиг.9

ШоЬ

L

Санхробход ynpa6/ffftotnuu д)(0д

с CK И

а

Вытд

. 3-й упрадлиюш бход

1

с Cg JO

с с,, ю

а

а

Фаг.Ю

Shit,i1

2-й выход

1-0. упрадля- 2.-U 3-й Синхробхад ,tu III

Устанобочныи. вход

Вход

Фиг. (2.

, . , . Z-йуяри&п вш,ий 3-ии1т ем1ош,ии Sxoa

бжоО

Ситеоочод шииоход

1-&ущйля о- Til

ш,ш ВходJ Т

HcmaHoBovHbiu ixef

771Ap/Ja«

.,.

Вб1хо9 Фили

1 станабачныч Z-uупра6/ 7ющий

бхад

3-й ynpaS/jff- чядии Sxod

fa ynpaSjjff юш.ий Sxod

7ющий

бхад

Boixod

Фиг. 15

21

/LWSm.

H i ...

KKcvemtf Kty tdnae изобретение

® - riefieffaSaennfe sflfftfKinot язодреяемй

.

7

;...«p../ mg

nwm

L i I I f... йтсчекы

9sa.f

(mpeSa№«}e}u3aSpa fnc e

| Авторское свидетельство СССР № 1146831, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-07-07—Публикация

1984-07-04—Подача