Изобретение относится к вычислительной технике и может быть использовано в аналоговых вычислительных системах, машинах и устройствах хранения и переработки информации.

Цель изобретения - повьшение т оч- но сти интегрирования и увеличение времени интегрирования без снижения точности.

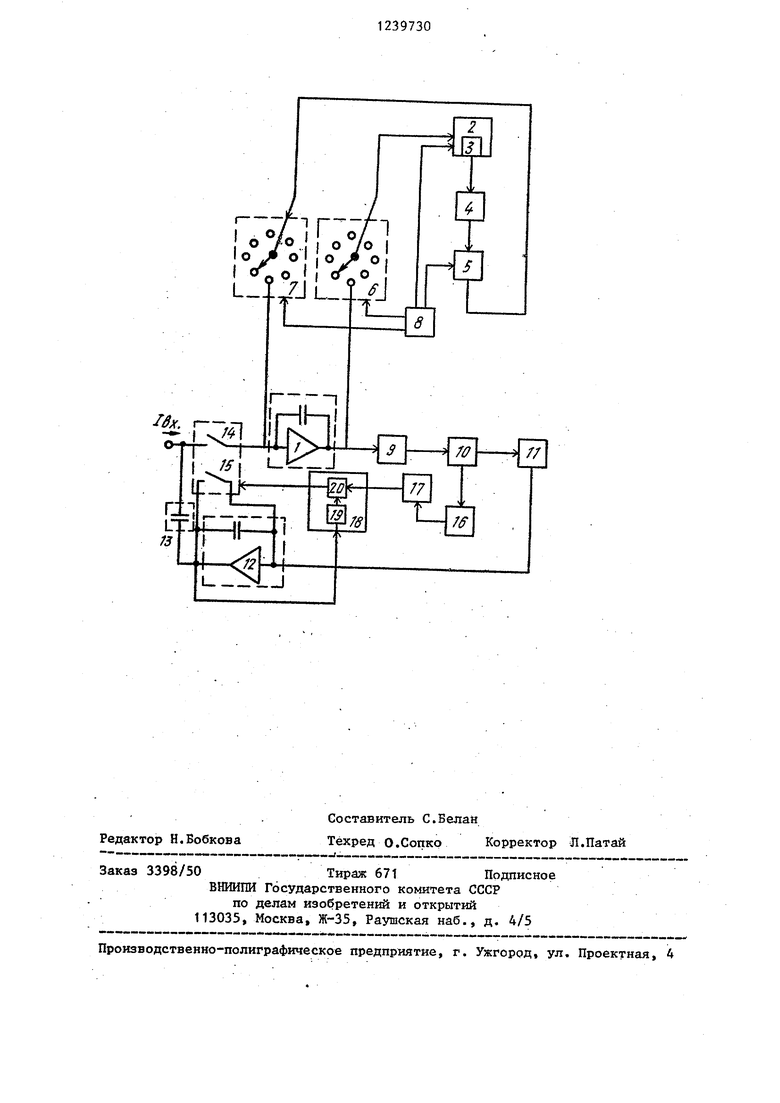

На чертеже представлена схема ана- логового интегратора для случая одного интегрирующего усилителя.

Интегратор содержит п интегрирующих усилителей 1, аналого-цифровой преобразователь 2 с йыходами младших разрядов 3, цифроаналоговый преобразователь 4, блок 5 формирования корректирующих импульсов, два п-позиционных переключателя 6 и 7, генератор 8 так- т.овых импульсов, а также для каждого интегрирующего усилителя по одному фильтру 9 нижних частот, блоку 10 дифференцирования, экстраполятору 11, дополнительному интегрирующему усилителю 12, электрометрическому конденсатору 13, паре синхронно управляющих ключей 14 и 15, выпрямителю 16, триггеру Шмитта 17, формирова.телю 18 управляющих импульсов, содержащему, например, выпрямительное звено 19 и эле- мент И 20.

. Интегратор работает следующим образом.

теле 1„

При отсутствии входного тика в иде-35 жение на каждом интегрирующем усили- альном случае выходные напряжения на выходах интегрирующих усилителей 1 должны оставаться постоянными. Однако из-за неидеальности интегрирующих конденсаторов, а также из-за не рав- 40 ных нулю внутренних входных токов one- ,рационных усилителей и из-за паразит- HijDc токов утечек имеет место дрейф или уход этих напряжений.

С приходом очередного импульса на управляющий вход переключателя 6 последний срабатывает и осзтцествляет пе-.

Описанная коррекция имеет место лишь при медленном самопроизвольном изменении выходных напряжений интегрирующих усилителей. Коррекция ограничена по амплитуде: она влияет лишь на последний разряд цифрового эквива лента выходного напряжения электронных интеграторов, т. е. может изменить напряжение соответствующего интегрирующего усилителя лишь на тысяч ные доли процента за один цикл работы переключателей 6 и 7. Длительност одного цикла определяется временем, в течение которого самопроизвольный уход напряжения имеет порядок величи ны разрешающей способности аналого- цифрового преобразователя 2.

реключение входа аналого-цифрового преобразователя 2 на выход следующего интегрирующего усилителя 1. Под дей- 50 ствием тактового импульса с генератора 8 аналого-цифровой преобразователь 2 запускается и начинает преобразовывать аналоговое значение напряжения интегрирующего усилителя 1 в цифровое, 55 так что при наличии полного регистра

результата в блоке 2 в нем по окончании цикла преобразования зафиксирован

цифровой эквивалент упомянутого напряжения.

Пусть, например, цифровой эквивалент напряжения оказался равным 74,2315 В, причем в группу старших разрядов входит код из первых пяти цифр, а в группу младших разрядов на выходе младших разрядов 3 входит последняя, шестая цифра, в данном примере эта цифра 5. Аналоговый эквивалент этого кода (цифры 5) может быть принят равным опорному напряжению в блоке 5, так что их разность равна нулю и корректирующий импульс в этом случае нулевой (т. е. отсутствует). В одном из. следующих циклов в работе переключателей 6 и 7 на выходе этого же интегрирующего усилителя 1 за счет дрейфа напряжение может несколько измениться, например оно составляет 74,2317 В, так что все старшие разряды остаются теми же, а самый 1 Шадший разряд несколько изменяется,, в данном случае на две единицы, и корректирующий импульс с выхода блока 5 поступает на вход соответ- ствукщето интегрирующего усилителя 1. Таким образом, поскольку величина корректирующего импульса пропорциональна отклонению кода младших разрядов от некоторого опорного, то напряжение снова становится равным исходному на данном интегрирующем усилителе. Таким образом, сохраняется напрятеле 1„

жение на

жение на каждом интегрирующем усили-

Описанная коррекция имеет место лишь при медленном самопроизвольном изменении выходных напряжений интегрирующих усилителей. Коррекция ограничена по амплитуде: она влияет лишь на последний разряд цифрового эквивалента выходного напряжения электронных интеграторов, т. е. может изменить напряжение соответствующего интегрирующего усилителя лишь на тысячные доли процента за один цикл работы переключателей 6 и 7. Длительность одного цикла определяется временем, в течение которого самопроизвольный уход напряжения имеет порядок величины разрешающей способности аналого- цифрового преобразователя 2.

При больших интегрируемых токах напряжение изменяется в старших разрядах цифрового эквивалента и описанная коррекция на это не влияет.

3

Однако, когда интегрируемые токи по порядку ветчины близки к токам утечек и дрейфа, их непосредственна подача на интегрирующие усилители 1 не позволяет осуществить интегрирование с высокой точностью, так как помимо собственной погрешности интегрирующих усилителей, появляется еще погрешность, обусловленная цепями кор- ,3 екции в виде блоков 2-8 интегратора которые по крайней мере часть полезного сигнала воспринимают как дрейф и его компенсируют. В этом случае вводятся в работу еще блоки 9-18, крторыми снабжен каждый интегрирующий усилитель 1. При малых токах интегрирования сигнал на выходе блока дифференцирования оказывается малым по абсолютной величине, которую вьще деляет блок 16, и Шмитта 17 срабатывает, запуская формирователь 1В управляющих импульсов на режим размыкания ключей 14 и 15. При этом входной ток, подлежащий интегрированию, поступает на электрометрическую обкладку конденсатора 13. На интервалах времени, когда ключ 14 разомкнут, соответствующий интегрирующий усилитель 1 работает в режиме корек- ции дрейфа, т. е. сохраняет значение выходной величины неизменной. Напряжние на электрометрическом конденсато ре 13 при этом определ:яется интегралом от входного тока с момента размыкания ключей 14 и 15. Заряд на электрометрической обкладке этого конденсатора в точности равен интегралу от входного тока, так как при разомкнутом ключе 14 никаких других цепей к этой обкладке не присоединено. Теоретически, конденсатор 13 имеет некоторую утечкуа заряда, обус- ловленнзгю неидеальностью изоляции. Однако эта утечка ничтожно мала по сравнению с утечкой в интегрирующем конденсаторе соответствующего интегрирующего усилителя 1. Дополнительный интегрирующий усилитель 12 в значительной мере компенсирует уход потенциала. На его вход поступает сигнал, соответствующий предсказанному значению входного тока, так что напряжение .на конденсаторе 13 компенсируется напряжением с вьпсода дополнительного ин

егрирующего усилителя 12 (частично или полностью) и потенциал электрометрического конденсатора со стороны его .обкладки, связанной с входными цепя-

0

0

5

ми и ключом 14, поддерживается близ- . КИМ к нулевому.

Когда ожидаемое напряжение на конденсаторе 13 оказывается большим заданной предельной величины, формирователь 18 дает короткий импульс на замыкание ключей 14 и 15. При этом заряд с конденсатора 13 переходит на конденсатор в цепи обратной связи интегрирующего усилителя 1. Если, в силу ограниченности времени замкнутого . состояния ключей 14 и 15, этот заряд переходит не полностью, это также не вносит существенной погрейности в рат 5 боту устройства, так как этот заряд переходит на следующий цикл. Точно также не вносят значительной погрешности и другие обычные помехи. Например, при размыкании ключей обычно возникает паразитный заряд. Этот случай сводится к предыдущему, где рассматривается остаточный заряд из-за ограниченности времени разряда. Благодаря тому, что малый интегрируемый ток накапливается в конденсаторе 13 значительное время, при разряде добавка напряжения в интегрирующем усилителе 1 касается старщих разрядов, так что этот разрядный импульс не нейтрализован цепями коррекции дрейфа 2-8. Час- тота циклов разряда зависит от величины входного тока, точнее, предсказанного входного тока, и с увеличением частоты циклов при увеличении входного интегрируемого тока период накопления заряда на конденсаторе 13 уменьшается, приближаясь к периоду об-. хода интегрирующих усилителей переклю-. чателями 6 и 7. При этом формирователь 18 переходит в режим постоянно. ...замк- нутых ключей 14 и 15, и блоки 9-18 перестают оказывать влияние на работу интегратора.

Такиг- образом, осуществляется автоматический выбор режима, обеспечи- вающего наибольшую точность решения.

Формула изобретения

0

5

0

50

Аналоговый интегратор, содержащий основной интегрирующий усилитель, аналого-цифровой преобразователь, выходы младших разрядов которого через циф- роаналоговьй преобразователь подключены к информационному входу блока 55 формирования корректирующих импульсов , и генератор тактовых и тульсов,

первый и второй выходы которого подключены к входам синхронизации анало51239730 . 4 .

го-цифрового преобразователя и блока нительного интегрирующего усилителя, формирования корректирующих импульсов, между входом и выходом которого вклю- отличающийся тем, что, с чей второй ключ пары синхронно управ- целью повьшения точности интегрирова-. ляемых ключей, выход каждого основно- ния и увеличения времени интегрирова- j го интегрирующего усилителя полключен ния без снижения, точности, в него вне- к соответствующему переключаемому кон- дены п-1 основных интегрирующих уси- такту второго п-позициоиного переклю- лителей, п фильтров нижних частот, п чателя и через по следовательно соеди- блоков дифференцирования, п экстрапо- ненные фильтр нижних частот, блок диф- ляторов, п выпрямителей, п триггеров 10 ференцирования и экстраполятор соеди- Шмитта, п формирователей управляющих . иены с входом соответствукнцего допол- импульсов, п пар синхронно управляе- нительного интегрирующего усилителя, мых ключей, п электрометрических кон- выход которого подключен к первому денсаторов, п дополнительных интегри- входу соответствующего формирователя рующих усилителей и два п-позиционных 15 управлянлцих импульсов, выходом среди- переключателя, управляющие входы ко- ненного с управляющим входом соответ- торых подключены соответственно к тре- ствующей пары синхронно управляемых тьему и четвертому выходам генератора ключей, выход каждого блока дифферен- , тактовых импул сов, каждый переключа- цирования через последовательно соеди- емый контакт первого п-позициоиного 20 кенные выпрямитель и триггер Шмитта переключателя подключен к входу соот- подключен к второму входу еоответст- ветствующего интегрирующего усилителя, вующего формирователя управляющих им- соединенному через первый ключ соот- пульсов, а переключающие контакты пер.ветствующей пары синхронно управляе- вого и второго п позиционных переклю- мых ключей с входом аналогового инте- 25 чателей соединены соответственно с вы- гратора, подключенным через соответ- ходом блока формирования корректирукз- ствующий электрометрический конденса- щих импульсов и входом аналого-цифро- тор к выходу соответствующего допол- вого преобразователя.

Редактор Н.Вобкова

Составитель С.Белай

Техред О.Сопко Корректор Л.Патай

Заказ 3398/50Тираж 671 Подписное

ВНИИШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

,д,,д.,.ГТ-,--.-. --

Производственно-полиграфическое предприятие, г. Ужгород. Ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ОЦИФРОВКИ АНАЛОГОВОЙ ВЕЛИЧИНЫ, ОЦИФРОВЫВАЮЩЕЕ УСТРОЙСТВО, ОСУЩЕСТВЛЯЮЩЕЕ УКАЗАННЫЙ СПОСОБ, И ДЕТЕКТОР ЭЛЕКТРОМАГНИТНОГО ИЗЛУЧЕНИЯ, СОДЕРЖАЩИЙ ТАКОЕ УСТРОЙСТВО | 2008 |

|

RU2430465C2 |

| Аналого-цифровой преобразователь сопротивления | 1983 |

|

SU1108369A1 |

| Интегратор | 1982 |

|

SU1062726A1 |

| Устройство для интегрирования электрического сигнала | 1982 |

|

SU1115066A1 |

| Аналого-цифровое интергрирующее устройство | 1985 |

|

SU1339591A1 |

| Интегрирующий аналого-цифровой преобразователь | 1985 |

|

SU1279069A1 |

| Интегратор | 1979 |

|

SU847330A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Интегрирующий преобразователь постоянного напряжения вов временной интервал | 1970 |

|

SU734875A1 |

| Аналого-цифровой интегратор | 1981 |

|

SU1013978A1 |

Изобретение относится к аналоговой вычислительной технике. Цель изобретения - повышение точности и увеличение времени интегрирования. Интегратор содержит п основных интегрирующих усилителей, аналого-цифровой преобразователь с выходами младших раз- рядов, цйфроаналоговый преобразователь, блок формирования корректирующих импульсов, два п-позиционных переключателя , генератор тактовых, импульсов, а также для каждого интегрирующего усилителя по одному фильтру нижних частот, блоку дифференцирования, экстраполятору, дополнительному интегрирующему усилителю,электрометрическому конденсатору,паре синхронно , управляемьк ключей, выпрямителю, триггеру Шмитта, формирователю управляющих импульсов. Повьшгение точности .достигнуто за счет введения режима, при котором входной ток интегрируется пассивным электрометрическим конденсатором, заряд которого циклически передается основному интегрирующему усилителю. В интервалах накопления заряда электрометрическим конденсатором напряжение на основном интегрирующем усилителе поддерживается неизменным за счет применения коррекции. 1 ил. (О to |00 оо

| Смолов В.Б | |||

| Аналоговые вычислительные машины.- М..: Связь, 1972, с.20 | |||

| Вычислительная техника /Под ред | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Синхронизирующее устройство для аппарата, служащего для передачи изображений на расстояние | 1920 |

|

SU225A1 |

| Патент США № 3784919, кл | |||

| Способ переработки сплавов меди и цинка (латуни) | 1922 |

|

SU328A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

Авторы

Даты

1986-06-23—Публикация

1983-09-12—Подача