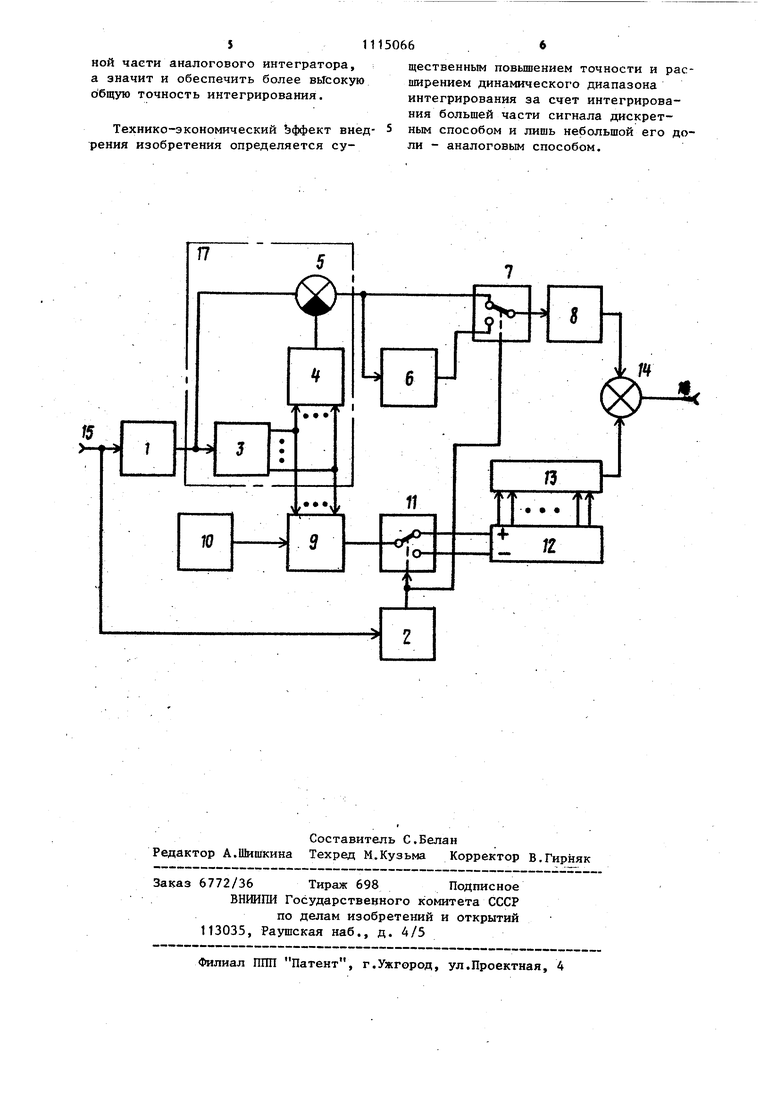

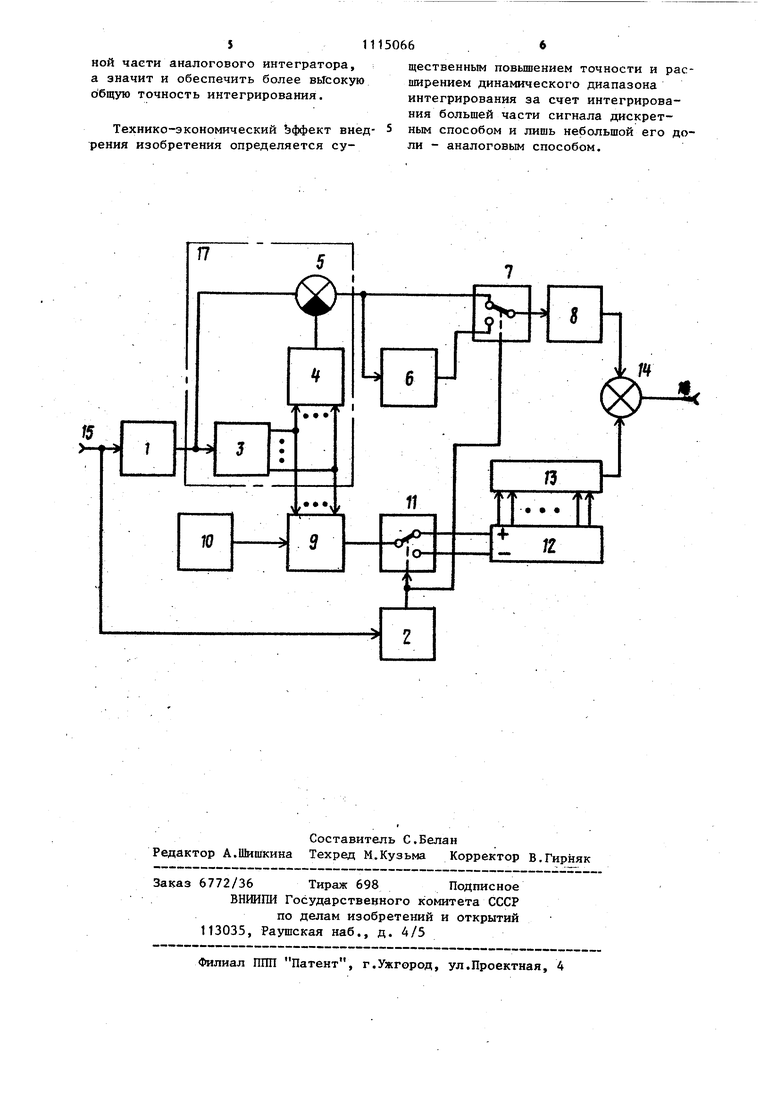

Изобретение относится к аналоговой вычислительной технике и может быть использовано в системах и уст ройствах автоматики и измерительной техники. Известно устройство для интегрирования электрического сигнала, содержащее интегрирующую емкость, включенную в цепь обратной связи операционного усилителя, и сопротивление, подключенное к входу последне го, задающее постоянную времени интегрирования 11. Недостатком устройства является низкая точность интегрирования из-за утечки интегрирующей емкости и дрейфа операционного усилителя. Наиболее близким к изобретению по технической сущности является уст ройство для интегрирования электрического сигнала, содержащее аналоговый интегратор, реверсивный счетчик, цифроаналоговый преобразователь, бло определения знака, ключевую схему и сумматор, причем вход блока определе ния знака соединен с входом устройства, а выход подключен к управляюще . му входу к.лючевой схемь:, первый и второй выходы ключевой схемы подключены соответственно к суммирующему и вычитающему входам реверсивного счетчика, выход последнего соединен с входом цифроаналогового преобразователя, выход которого подключен к одному из входов сумматора, второй вход сумматора соединен с выходом ан логового интегратора, выход сумматора является выходом устройства 12. В известном устройстве весь входной сигнал вначале проходит через аналоговый интегратор, обладаюпщй значительно погрешностью из-за утеч |ки интегрирующей емкости и дрейфа 1операционного усилителя. В результат момент окончания цикла интегрирования в аналоговом интеграторе определяется с низкой точностью и погрешность последнего, многократно накопленная в счетчике, существенным обра зом влияет на общий результат интегр рования . Целью изобретения является повышение точности и расширение динамического диапазона интегрирования. Поставленная цель достигается тем что в устройство для интегрирования электрического сигнала, содержащее аналоговый интегратор, выходом соеди ненный с первым входом сумматора. второй вход которого подключен к выходу цифроаналогового преобразователя, а выход является выходом устройства, лок определения знака, выход которого подключен к управляющему входу первого переключателя, выходами соединенного с суммирующим и вычитающим входами реверсивного счетчика , выходы которого соединены с входами цифроаналогового преобразователя, второй переключатель и инвертор, введены блок формирования гибридного кода, генератор импульсов, управляемый делитель частоты и блок вьщеления модуля, вход которого является входом устройства и соединен с входом блока определения знака, а выход подключен к входу блока фор рования гибридного кода, аналоговый выход которого непосредственно и через инвертор подключен к первому и второму информационным входам второго переключателя, выходом соединенного с входом аналогового интегратора , цифровой выход блока формирования гибридного кода подключен к группе входов управления управляемого делителя частоты, частотньй вход которого соединен с выходом генератора импульсов, а выход - с информационным входом первого переключателя, причем управляющий вход второго переключателя подключен к выходу блока определения знака. На чертеже представлена структурная схема предлагаемого устройства. Устройство для интегрирования электрического ригнала содержит блок 1 вьщеления модуля, блок 2 определения знака, аналого-цифровой преобразователь 3, второй цифроаналоговый преобразователь 4, блок 5 вычитания, инвертор 6, второй переключатель 7, аналоговьй интегратор 8, управляемый делитель 9 частоты, генератор 10 импульсов, первый переключатель 11, реверсивный счетчик 12, цифроаналоговый преобразователь 13, сумматор 14, вход 15 и выход 16, причем аналого-цифровой преобразователь 3, второй цифроаналоговый преобразователь 4 и блок 5 вычитания образуют блок 17 формирования гибридного кода, вход которого подключен к выходу блока 1 вьщеления модуля, аналоговый выход через инвертор 6 непосредственно соединен с входами переключателя 7, подключенного к анайоговому интегратору 8. Цифровой выход 31 блока 17 формирования гибридного кода соединен с управляющими входами управляемого делителя 9 частоты, включенного между генератором 10 импульсов и переключателем 11, выходами соединенным с входами реверсивного счетчика 12, подключенного через цифроаналоговьй преобразователь 13 к входу сумматора 14, вторым входом соединенного с выходом аналогового интегратора 8, Вход 15 устрой ства через блок 2 определения знака соединен с управляющими входами пеое ключателей 11 и 7. Устоойство работает следующим образом. Подлежащий интегрированию входной сигнал преобразуют в гибридный код .блоком i7 формирования гибридного кода, для чего интегрируемый сигнал с входа 15 устройства поступает на входы блока 1 выделения модуля и бло ка 2 определения знака. С выхода бло ка 1 выделенный однополярный сигнал X подается на вход аналого-цифрово го преобразователя 3, в котором осуществляется его сравнение с дискретным рядом опорных напряжений, равномерно распределенных по всему рабочему диапазону устройства. Результат сравнения представляет собой дискрет ную часть входного сигнала, вьфаженную в виде цифрового кода N. Послед ний поступает на вход цифроаналогового преобразователя 4, где преобразуется в аналоговую форму 1 и далее - на вычитающий вход блока 5 вычитания, на второй вход которого по дается сигнал |Х| с выхода блока 1. На выходе блока 5-вычитания образует ся аналоговый сигнал |Хо|, представляющий собой разность между входным сигналом и его дискретной частью ( . Полученный остаток /Хо/ подается непосредственно на один из входов, и через инвертор 6 - на другой вход переключателя 7, который управляется сигналом с вЕ 1хода блока 2 определения знака. Переключатель 7 обеспечивает поступление аналогового сигна ла на вход аналогового интегратора 8 со знаком, соответствующим знаку входного сигнала: при при . На выходе аналогового интегратора 8 образуется сиг-. 66 нал, пропорциональный интегралу остатка ,dt, где Т - постоянная времени аналогового интегратора. С выхода аналого-цифрового преобразователя 3 код дискретной части интегрируемого сигнала Na поступает на управляющий вход управляемого делителя 9 частоты, на частотный вход которого поступает непрерывная импульсная последовательность частотой fo с выхода генератора 10 импульсов. Частота на выходе делителя 9, пропорциональная дискретной части интегрируемого сигнала . fo, поступает на вход переключателя 11, осуществляемого ее подключение к одному из входов реверсивного счетчика 12 в зависимости от знакр. входного сигнала: при fg поступает на суммирующий, а при X-tO - на вычитающий вход счетчика. ЧИсло, записанное в счетчике, пропорционально интегралу дискретной части входного сигнала , . Хз t, где Y-5 - интеграл дискретной части входного сигнала; к,к - масштабные коэффициенты. С выхода цифроаналогового преобразователя 13 число NC преобразуется в аналоговый сигнал Y-p, который далее поступает на вход сумматора 14, на другой вхрд которого подается интеграл остатка Y,. На выходе сумматора 14 образуется интеграл входного сигнала X устройства, состоящий из суммы интегралов дискрет юй части и остатка .X5t+irX3dt. Таким образом, в устройстве для интегрирования преобразование входного интегрируемого сигнала в частоту импульсов осуществляется без участия аналогового интегратора с использованием дополнительно введенных блока выделения модуля, блока формирования гибридного кода, инвертора, переключателя, генератора импульсов и управляемого делителя частоты. При этом устройство, хотя и усложняется, зато позволяет получить более высокую точность дискретного интегриро- , вания за счет исключения из дискреТ

51115066 . 6

ной части аналогового интегратора, щественным повьшением точности и раса значит и обеспечить более высокую ширением динамического диапазона Ьбщую точность интегрирования. интегрирования за счет интегрироваТехнико-экономический Ьффект внед- 5 ным способом и лишь небольшой его дорения изобретения определяется су- ли - аналоговым способом. ния большей части сигнала дискрет

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой интегратор | 1982 |

|

SU1037280A1 |

| Устройство для интегрирования функций | 1982 |

|

SU1070570A1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Устройство управления | 1984 |

|

SU1229721A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1478331A1 |

| Устройство для управления вибрацией | 1981 |

|

SU1003017A1 |

| Устройство для интегрирования функций | 1984 |

|

SU1242993A1 |

| Устройство для формирования векторов | 1983 |

|

SU1091215A1 |

| Универсальный калибратор тока | 1985 |

|

SU1308969A1 |

| Функциональный преобразователь | 1981 |

|

SU1018127A1 |

УСТРОЙСТВО ДЛЯ ИНТЕГРИРОВАНИЯ ЭЛЕКТРИЧЕСКОГО СИГНАЛА, содержащее аналоговый интегратор, вь ходом соединенный с первым взводом сумматора, второй вход которого подключен к выходу цифроаналогового преобразователя, а выход.является выходом устройства, блок определения знака, выход которого подключен к управляющему входу первого переключателя, , выходами соединенного с суммирукицим и вычитающим входами реверсивного счетчика, выходы которого соединены с входами цифроаналогового преобразователя, второй переключатель и инвертор, отличающееся тем, что, с целью повышения точности и расширения динамического диапазона интегрирования, в него введены блок формирования гибридного кода, генератор импульсов, управляе ш делитель частоты и блок вьщеления модуля, вход которого является входом устройства и соединен с входом блока определения знака, а выход поцключен к входу блока формирования гибридного кода, аналоговый выход которого непосредственно и через инi вертор подключен к первому и второму информационным входам второго переключателя, выходом соединенного с входом аналогового интегратора, цифровой выход блока формирования гибридного кода подключен к группе входов управления управляемого делителя частоты, частотный вход которого соединен с выходом генератора импульсов, а выход - с информационным входом перО1 вого переключателя, причем управляющий вход второго переключателя подо. ключен к выходу блока определения 9 знака. Од

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Проектирование и применение операционных усилителей | |||

| Под ред | |||

| Дж | |||

| Грэма, Дж | |||

| Тоби и др | |||

| М.,Мир, 1974, с | |||

| Крутильный аппарат | 1922 |

|

SU233A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| I ВСГГСО'ЭЗНЛЯ I ДИСКРЕТНО-АНАЛОГОВЫЙ ИНТЕГРАТОР]|]ДТГ[{Т! Л :'Тк;^;Г v-^:^ | 0 |

|

SU370614A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-09-23—Публикация

1982-11-26—Подача