4ik 1

СП)

сл

Изобретение относится к радиотехнике и может использоваться для синтеза частот и сигналов в радиолокационной связной и измерительной аппаратуре.

Цель изобретения расширение диапазона частот синтезируемых сигналов .

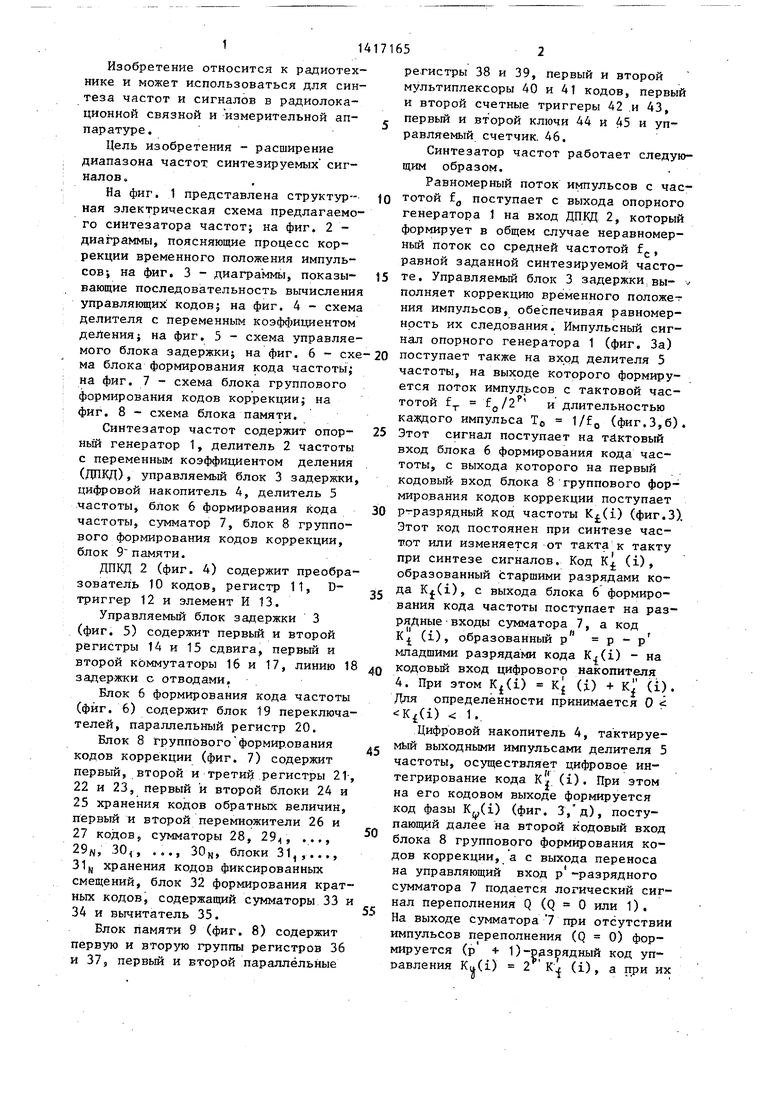

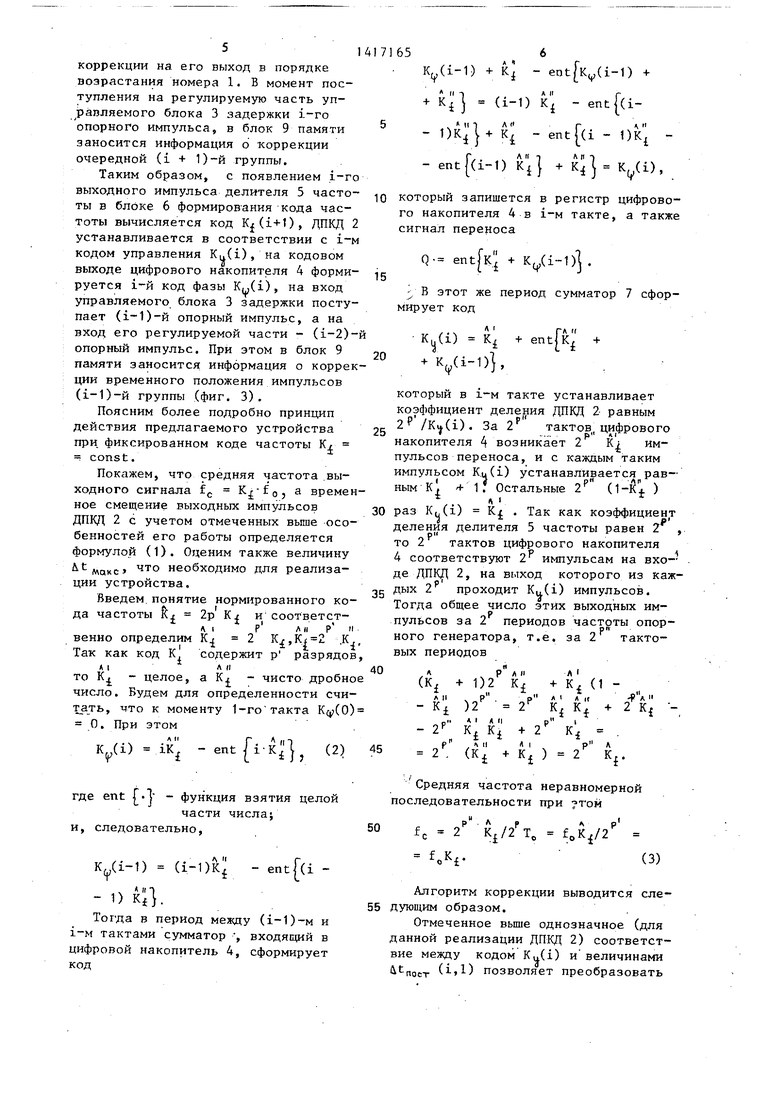

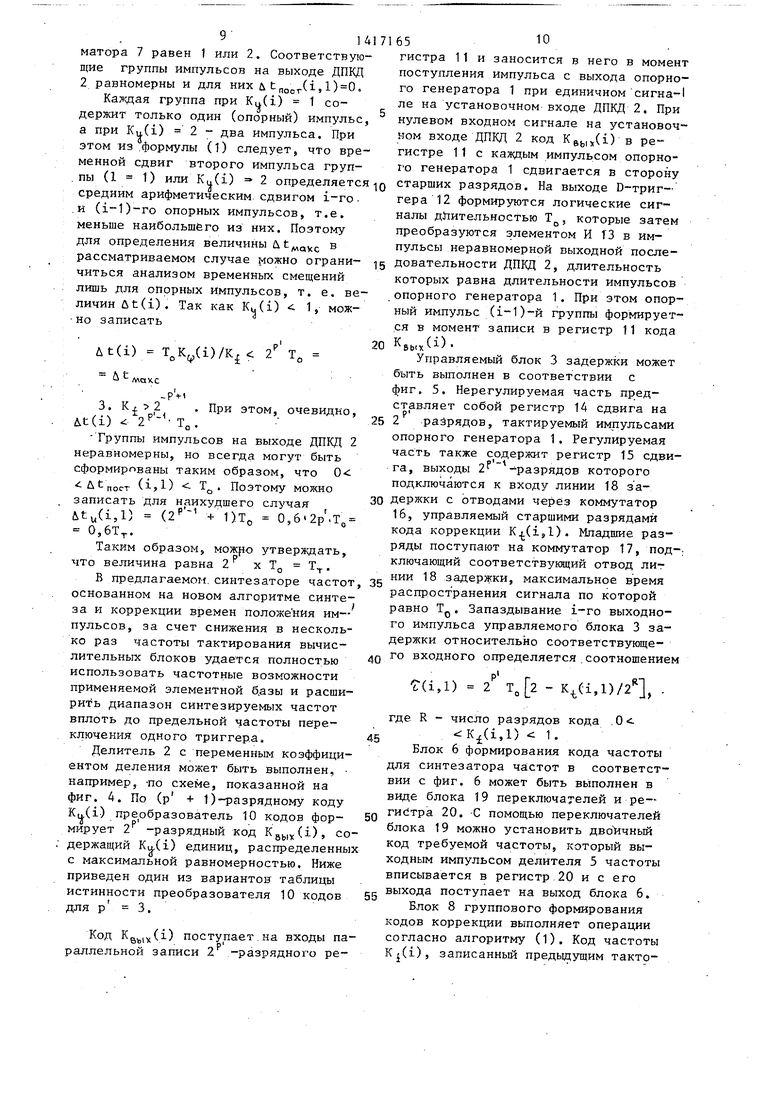

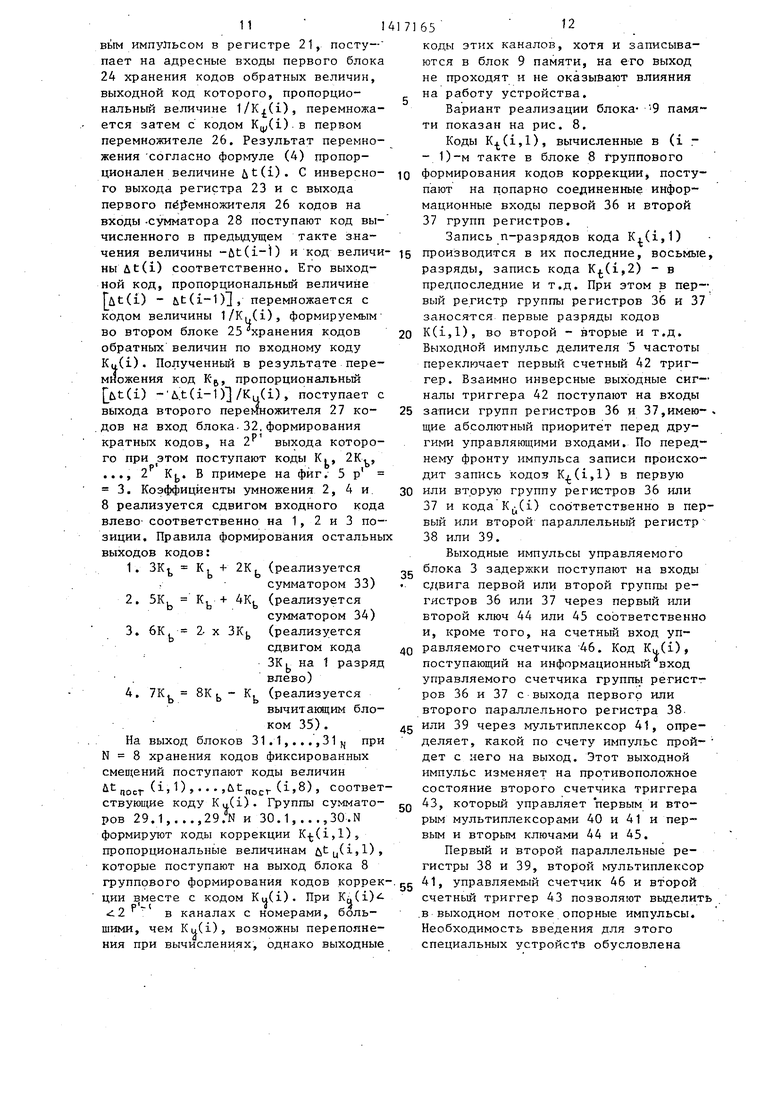

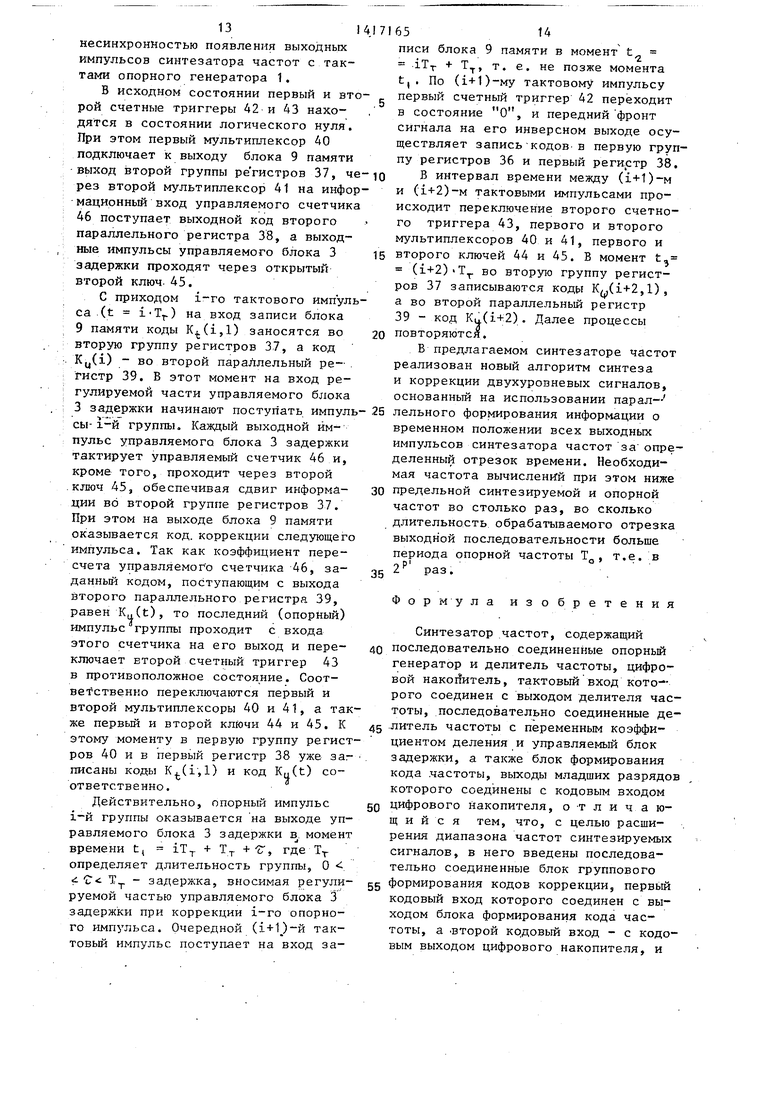

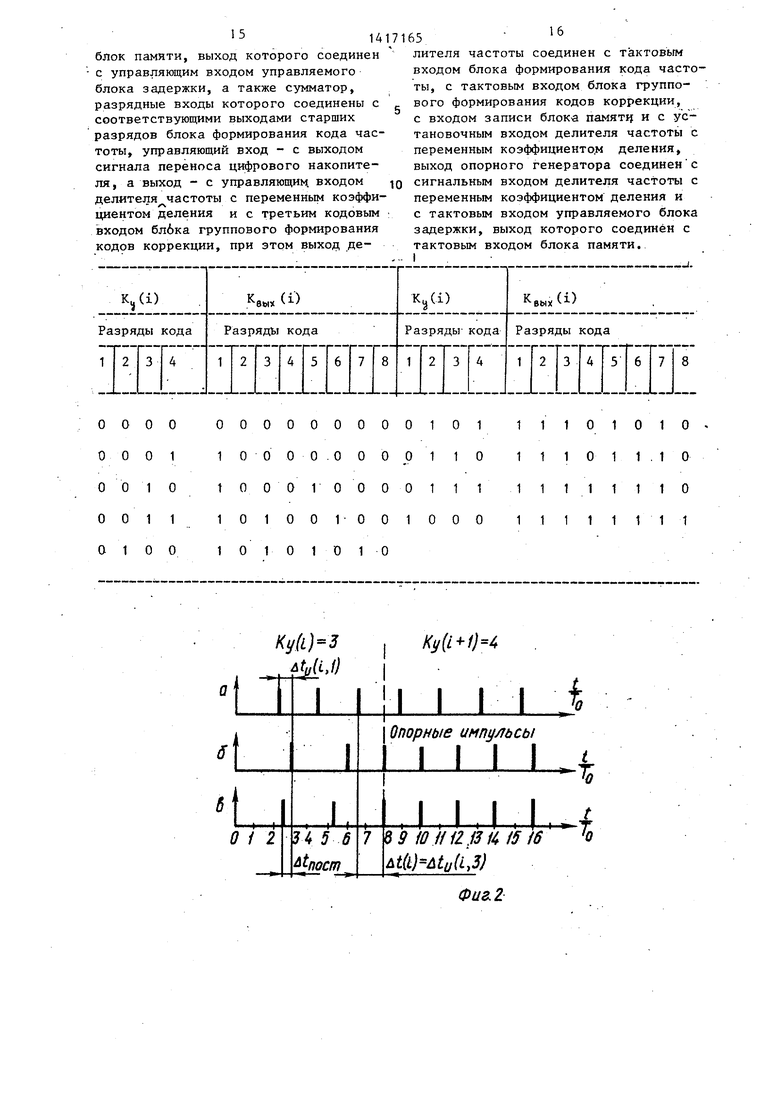

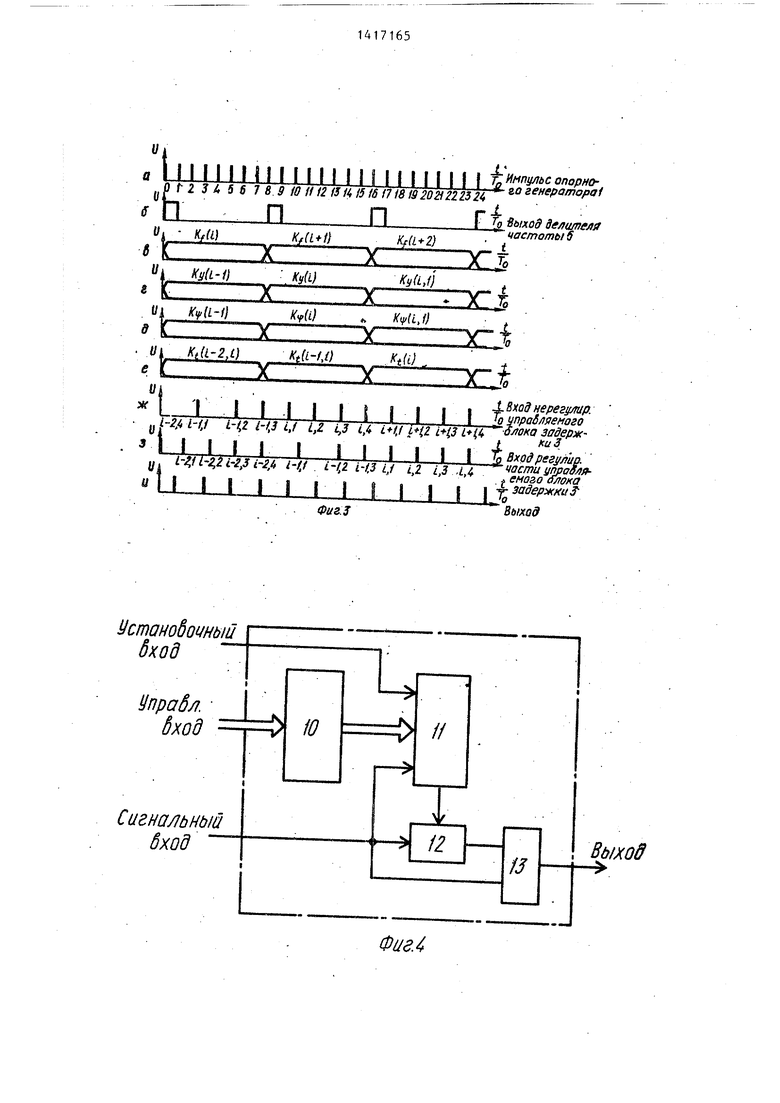

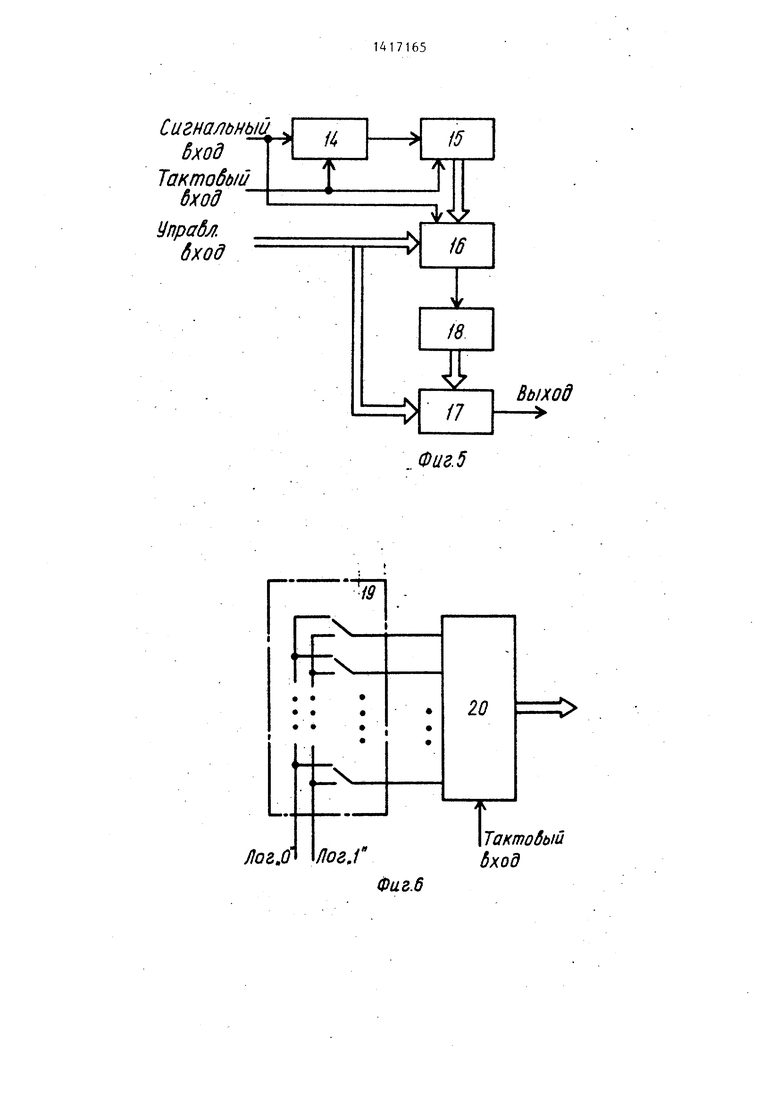

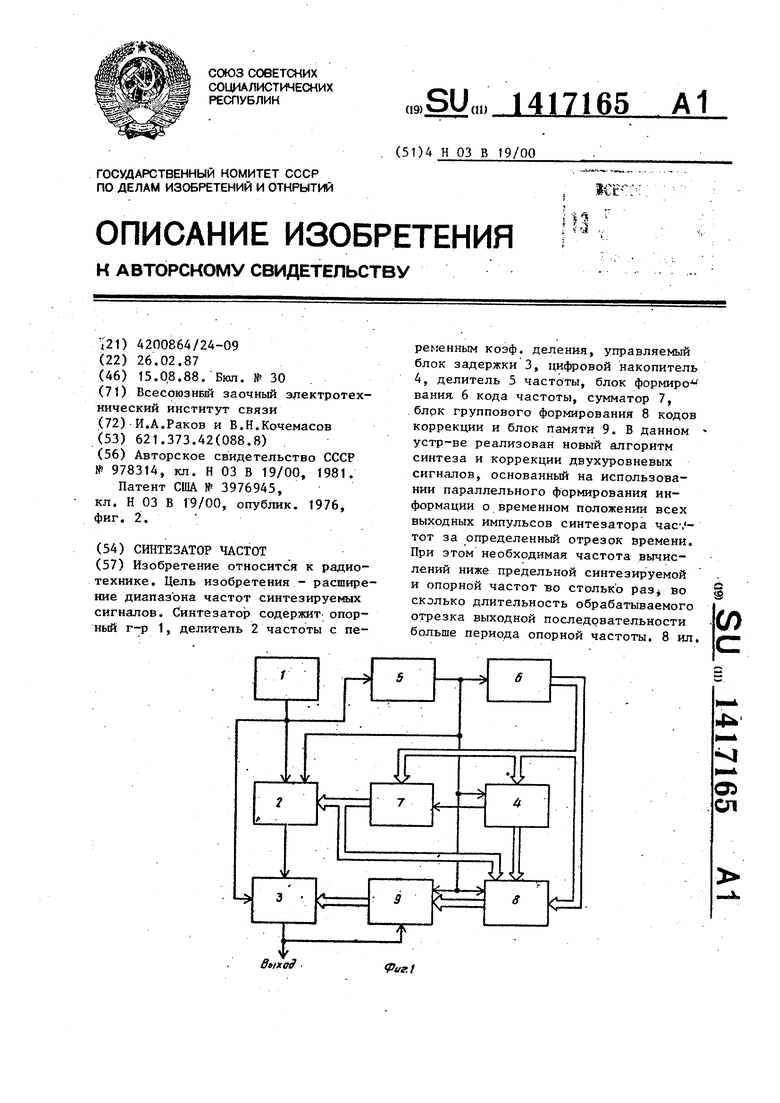

На фиг. 1 представлена структурная электрическая схема предлагаемого синтезатора частот; на фиг. 2 - диаграммы, поясняющие процесс коррекции временного положения импульсов; на фиг, 3 - диаграммы, показы- вающие последовательность вычисления управляющих кодов; на фиг. 4 - схема делителя с переменным коэффициентом деления} на фиг. 5 - схема управляемого блока задержки; на фиг. 6 - схе ма блока формирования кода частоты; на фиг. 7 - схема блока группового формирования кодов коррекции; на фиг. 8 - схема блока памяти.

Синтезатор частот содержит опор- ньй генератор 1, делитель 2 частоты с переменным коэффициентом деления (ДПКД), управляемый блок 3 задержки, цифровой накопитель 4, делитель 5 частоты, блок 6 формирования кода частоты, сумматор 7, блок 8 группового формирования кодов коррекции, блок 9 памяти.

ДПКД 2 (фиг. 4) содержит преобразователь 10 кодов, регистр 11, D- триггер 12 и элемент И 13.

Управляемый блок задержки 3 (фиг. 5) содержит первый и второй регистры 14 и 15 сдвига, первый и второй коммутаторы 16 и 17, линию 18 задержки с отводами.

Блок 6 формирования кода частоты (фиг. 6) содержит блок 19 переключателей, параллельный регистр 20.

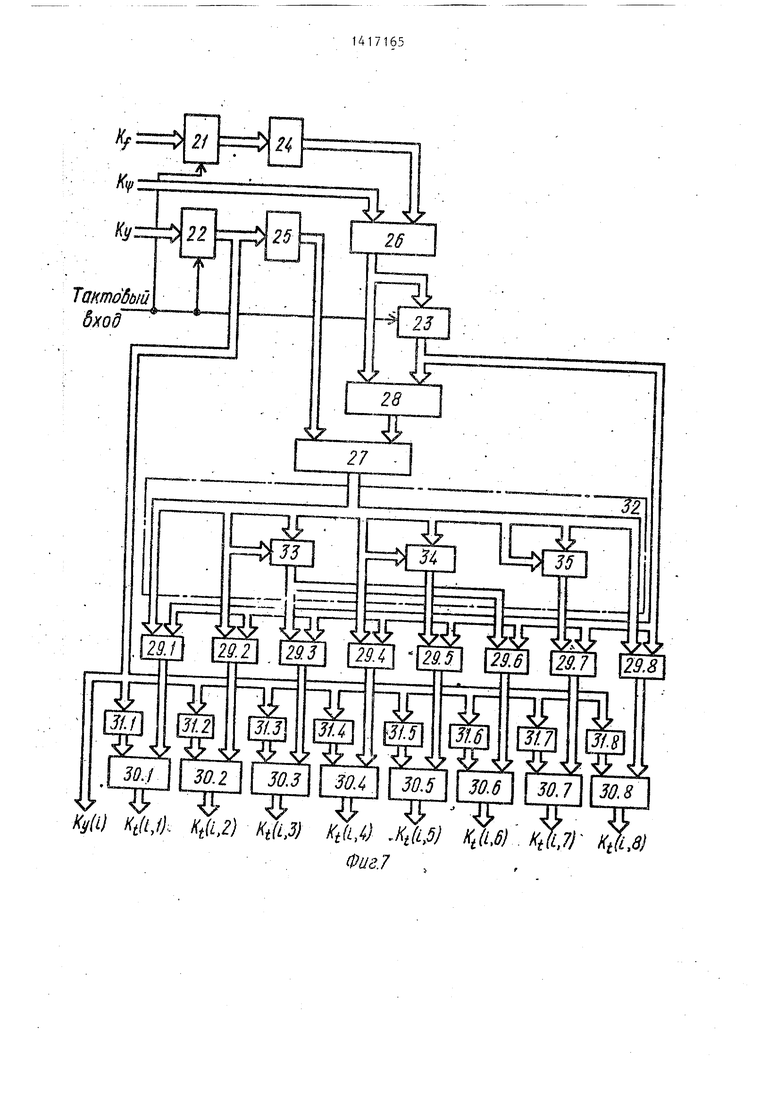

Блок 8 группового формир.ования кодов коррекции (фиг. 7) содержит первый, второй и третий регистры 21-, 22 и 23, первый и второй блоки 24 и 25 хранения кодов обратных величин, первый и второй перемножители 26 и 27 кодов, сумматоры 28, 29, ..., 29/4, 30,, ..., 30ц, блоки 31,,..., 31, хранения кодов фиксированных смещений, блок 32 формирования кратных кодов, содержащий сумматоры 33 и 34 и вычитатель 35.

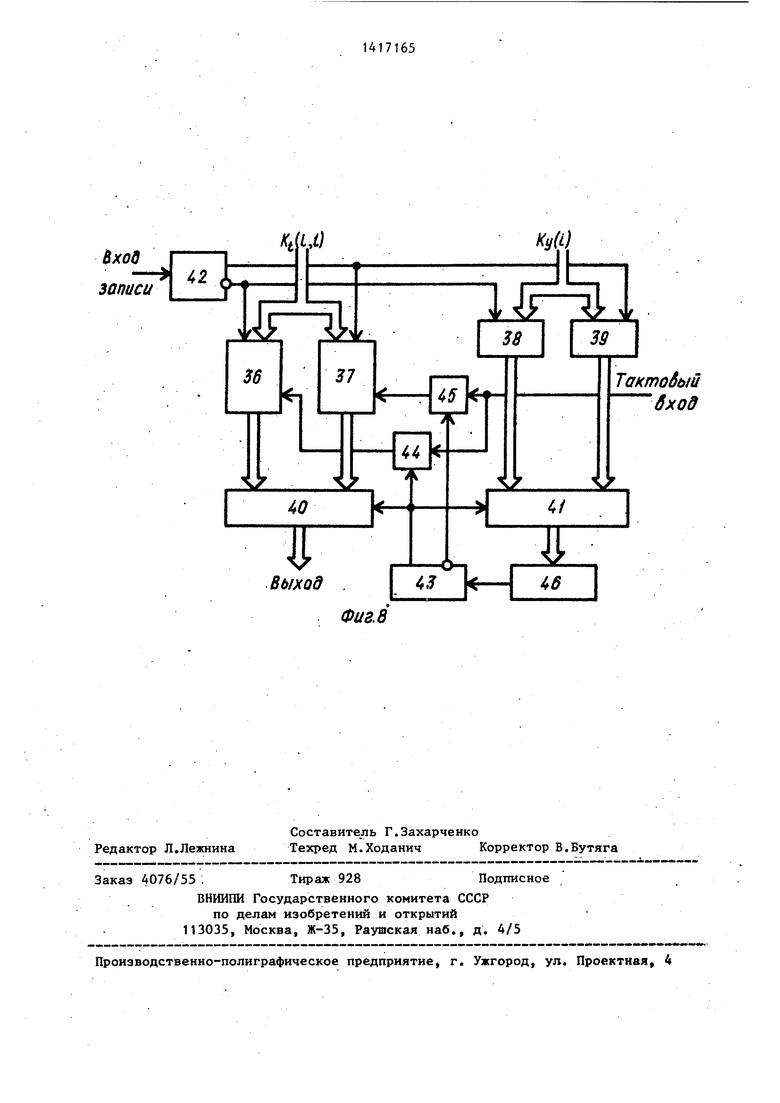

Блок памяти 9 (фиг. 8) содержит первую и вторую группы регистров 36 и 37J первый и второй параллельные

10

20

25

30

15

35

40

45

50

55

регистры 38 и 39, первый и второй мультиплексоры 40 и 41 кодов, первый и второй счетные триггеры 42 .и 43, первый и второй ключи 44 и 45 и управляемый счетчик. 46.

Синтезатор частот работает следующим образом.

Равномерный поток импульсов с частотой f(, поступает с выхода опорного генератора 1 на вход ДПКД 2, который формирует в общем случае неравномерный поток со средней частотой f j., равной заданной синтезируемой частоте. Управляемый блок 3 задержки,вы- v полняет коррекцию временного положе-г ния импульсов, обеспечивая равномерность их следования. Импульсный сигнал опорного генератора 1 (фиг. За) поступает также на вход делителя 5 частоты, на выходе которого формируется поток импульсов с тактовой частотой f f(j/2 и длительностью каждого импульса TO l/f,, (фиг.3,6). Этот сигнал поступает на тйктовый вход блока 6 формирования кода частоты, с выхода которого на первый кодовый- вход блока 8 группового формирования кодов коррекции поступает ртразрядный код частоты K(i) (фиг.З). Этот код постоянен при синтезе частот или изменяется от такта к такту при синтезе сигналов. Код К (i), образованный старшими разрядами кода Ki(i), с выхода блока 6 формирования кода частоты поступает на разрядные входы сумматора 7, а код К (i), образованный р р - р младшими разрядами кода K(i) - на кодовый вход цифрового накопителя 4. При этом K(i) K (i) + (i). Для определённости принимается О iKfd) 1..

Цифровой накопитель 4, тактируемый выходными импульсами делителя 5 частоты, осуществляет цифровое интегрирование кода KI (i). При этом на его кодовом выходе формируется код фазы Kj(i) (фиг. 3, д), поступающий далее на второй кодовый вход блока 8 группового формирования кодов коррекции, а с выхода переноса на управляющий вход р -разрядного сумматора 7 подается логический сигнал переполнения Q (Q О или 1). На выходе сумматора 7 при отсутствии импульсов переполнения (Q 0) формируется (р равления

(р 4- 1)-разрядный код уп- K(i) 2 Kj (i), а при их

что если Ku(i) т О, 1ЖДЫХ Ku(i) выходных

, о,3. 14

аличии -(Q 1) - код K,(i) (i) + «1 . Под действием этого кода ближайий импульс с выхода делителя 5 астоты устанавливает коэффициент

еления ДПКД 2 равным 2 /Кн(1),

.е. из 2 импульсов опорного генеатора 1, поступающих на вход ДПКД 2 в течение периода Т тактовой частоты, на его выход проходит Ku(i) импульсов. При этом ДПКД 2 построен таким образом, последний из каждых импульсов, называемый далее опорным, совпадает по времени с тактовым импульсом. Если код Kf(i) состоит только из единиц и сигнал переноса Q 1, возникает переполнение накапливающего сумматора 7 и код Ku(i) равен при этом 2 , а коэффициент деления ДПКД 2 - единице.

Таким образом, за счет изменения коэффигщента деления, на выходе ПКД 2 формируется отрезок неравномерной последовательности с заданным законом изменения средней частоты. Код Ku(i) (фиг. 3, г) поступает на третий кодовый вход .блока 8 группового формирования кодов коррекции, где вместе с кодами K(i) и K,(i) используется для получения информации о необходимой коррекции временного положения одновременно для всех выходных импульсов ДПКД 2, сформированных за 1. тактов опорного, генератора 1, т.е. за один период тактовой частоты. Временное смещение 1-го импульса L-го отрезка длительностью 2 Тд Т,, (i-й группы) определяется соотношением

At(i,l) it(i-1) + к (i)

- iit(i-l) + utp (i,l).

гдейЬ(1) - смещение опорного импульса i-й группы относительно соответствующего импульса идеальной равномерной пооледователь- ности (фиг. 2,а) со средней частотой f, Ki(i)-f.

Величина ut(i) определяется .соотношением кодов K,,(i) и K(i). При этом в соотношении (1) положительные значения временных параметров соответствует отставанию реальных им

4

+ ,

17165

пульсов от импульсов требуемой вы- . ходной последовательности.

Смысл параметра tpj3j.T() состоит в следующем. Как показано ранее, за время Т (в течение i-ro периода тактовой частоты) на выходе ДПКД 2 формируется в общем случае неравномерная последовательность Ci-я груп д па), содержащая K,,(i) импульсов

(фиг. 2, б). Расположение импульсов в группе фиксировано для каждого значения Ka(i) и определяется структурой ДПКД 2. Сравним i-ю группу с

г некоторой равномерной последователь- . ностью, имеющей длительностью Т и содержащей K(,(t) импульсов, последний из которых совпадает с последним импульсом i-й группы (фиг. 2,в).

2Q Величина (1,1) определяет временной интервал между 1-ми импульсами сравниваемых последовательностей. Очевидно tnog i,l K(i)J О,кроме того, для равномерных последова25 тельностей (Kij(i) 1,2, А, 8,...) (i,l) 0.

Вычисленные в блоке 8 группового формирования кодов коррекции коды K.(i,l), пропорциональные величинам

2Q it(i,l), поступают на вход блока 9 памяти. С приходом на вход записи блока 9 памяти очередного импульса с выхода делителя 5 частоты эти коды одновременно записываются в его ячейки, а с выхода блока 9 памяти на управляющий вход управляемого блока 3 задержки поступает код коррекции K(i - 1,1) (фиг. 3, е) одного из импульсов предьщущей группы. .Q Управляемый блок 3 задержки состоит из нерегулируемой и регулируемой частей. Входные импульсы вначале поступают на нерегулируе мую часть (фиг. 3, ж), где задерживаются на д5 время X Тр , а затем на регулируемую часть (фиг. 3, з) с временем задержки i(i,l) Ь. - t(i,1), где ut rtoKc максимальная величина At(i,l). При этом обеспечивается необходимое соответствие кода коррекции на управляющем входе управляемого блока 3 задерж- . ки импульсу, поступающему на регулируемую часть.

Импульсы с выхода управляемого блока 3 задержки (фиг. 3,и) поступают на выход синтезатора частот и, кроме того, на вход записи блока 9 памяти, вызывая продвижение кодов

50

55

коррекции на его выход в порядке возрастания номера 1. В момент поступления на регулируемую часть уп- травляемого блока 3 задержки i-ro опорного импульса, в блок 9 памяти заносится информация о коррекции очередной (i + 1)-й группы.

Таким образом, с появлением i-ro выходного импульса делителя 5 часто- ты в блоке 6 формиров ания кода частоты вычисляется код K(i+t), ДПКД 2 устанавливается в соответствии с i-м кодом управления Ku(i), на кодовом выходе цифрового накопителя 4 форми- руется i-й код фазы K,,(i), на вход управляемого блока 3 задержки поступает (1-1)-й опорный импульс, а на вход его регулируемой части - (1-2)опорный импульс. При этом в блок 9 памяти заносится информация о коррекции временного положения импульсов (1-1)-й группы (фиг. 3).

Поясним более подробно принцип действия предлагаемого устройства при. фиксированном коде частоты Кг const.

Покажем, что средняя частота .выходного сигнала f а временное смещение выходных импульсов ДПКД 2 с учетом отмеченных выше особенностей его работы определяется формулой (1). Оценим также величину необходимо для реализации устройства.

Введем.понятие нормированного кода частоты Кг 2р К. и соответст- | 1 р Л11 р м венно определим К 2 К, ,К,

Так как код К, содержит р разрядов

А1л н

то К, - целое, а K - чисто дробно

число. Будем для определенности счи- , что к моменту 1-го такта Kq;(0) 0. При этом

14171656

K((i-1) + к - (i-1) f( (Гр

+ К j (i-1) К - ent(i5 II т л II г и

- 1)K.j J + К - ent(i - 1)К

г АКТ MI Т

- ent(i-1) К|} + К J K((i),

который запишется в регистр цифрового накопителя 4 в i-м такте, а также сигнал переноса

Q- + K((i-1) .

- В этот же период сумматор 7 сформирует код

л гл к K(i) К + +

который в i-M такте устанавливает коэффициент деления ДПКД 2- равным 2 /K(|(i). За 2 тактов, ци фрового накопителя 4 возникает 2 К импульсов переноса, и с каждым таким импульсом K.u(i) устанавливается равным К +1; Остальные 2 (1-К )

, раз К,.(i) К/ . Так как коэффициент

Лр

деления делителя 5 частоты равен 2 ,

р К

то 2 тактов цифрового накопителя 4 соответствуют 2 импульсам на входе ДПКД 2, на выход которого из каждых 2 проходит Kn(i) импульсов. Тогда общее число этих выходных импульсов за 2 периодов частоты опорного генератора, т.е. за 2 тактовых периодов

А р л II л (К, + 1)2 К. + К, (1 лп . ,Р . „р А- А. „-

- к; П 2

K.J К +2 К|

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1982 |

|

SU1084992A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1515364A1 |

| Цифровой синтезатор частот с частотной модуляцией | 1985 |

|

SU1293840A1 |

| Цифровой синтезатор частот | 1989 |

|

SU1691926A1 |

| Цифровой синтезатор частот | 1983 |

|

SU1193803A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2015 |

|

RU2595629C1 |

| Умножитель частоты | 1978 |

|

SU765818A1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| Цифровой измеритель скважности прямоугольных импульсов | 1981 |

|

SU995063A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ИМИТОСТОЙКИХ СИСТЕМ ДИСКРЕТНО-ЧАСТОТНЫХ СИГНАЛОВ С ВРЕМЕННЫМ УПЛОТНЕНИЕМ ИНФОРМАЦИИ | 2011 |

|

RU2451327C1 |

Изобретение относится к радиотехнике. Цель изобретения - расширение диапазона частот синтезируемых сигналов. Синтезатор содержит опорный г-р 1, делитель 2 частоты с переменным коэф. деления, управляемый блок задержки 3, цифровой накопитель 4, делитель 5 частоты, блок формиро вания 6 кода частоты, сумматор 7, .блок группового формирования 8 кодов коррекции и блок Памяти 9. В данном устр-ве реализован новый алгоритм синтеза и коррекции двухуровневых сигналов, основанный на использовании параллельного формирования информации о временном положении всех выходных импульсов синтезатора час-, - тот за определенньй отрезок времени. При этом необходимая частота вычислений ниже предельной синтезируемой и опорной частот во столько раз во сколько длительность обрабатываемого отрезка выходной последовательности больше периода опорной частоты. 8 ил. i (Л

К

,(i) Дк - ent i-Kj, (2) 45

V

где ent - функция взятия цело

части числа; и, следовательно,

K((i-1) (i-DK - ent(i Ли)

- 1) Kf.

Тогда в период между (i-l)-M и i-M тактами сумматор , входящий в цифровой накопитель 4, сформирует код

Г

Средняя частота неравномерной последовательности при jToii

с

f.K

р . л рАр

2 Т, foKf/2

(3)

Алгоритм коррекции выводится следующим образом.

Отмеченное выше однозначное (для данной реализации ДПКД 2) соответствие между кодом „(i) и величинами litnocT () позволяет преобразовать

последовательность выходных импульсов ДПКД 2 в последовательность,состоящую из отрезков длительностью 2 Тд, внутри которых импульсы распределены равномерно. Для реализации этого блок 8 группового формирования кодов коррекции должен содержать 2 блоков хранения кодов фиксированных смещений, по одному для каждого 1, ю в ячейках которых по адресам Ku.(i) записаны коды соответствующих временных смещений d t j,. (1,1) . При этом временной интервал между импульсами внутри i-й группы (отрезка) 15 после коррекции положения каждого иг пульса на . (1,1) равен 2 To/Kxj(i).

Для получения равномерной последовательности из выходной последова- 20 тельности ДПКД 2, импульсы которой смещены на utno. (i,l), необходимо дополнительно -произвести деформацию последней изменением временного масштаба групп с сохранением равномер- 25 ности внутри группы. При этом группы, содержащие K|,(i) К, +1 импульсов следует растяд уть, а содержащие Kii(i) K импульсов сжать. Время, на которое нужно изменить ЗО длительность i-й группы, можно определить по смещениям опорных импульсов, информация с которых содерясит- ся в коде Км(1)- Для доказательства

этого нужно сравнить набег фазы к

35

. л I (К.

« I H-K

ent

(i - entfKi 11

t П т Kf i

+ K. (i).

1-му опорному импульсу реальной неравномерной и идеальной равномерно последовательностей.К этому моменту на вход ДПКД .2 поступит 2 - i импульсов, а на его выход пройдет I

m «

набе г составит tpp-, 27(.Для определения величины ( учитывается, чт за i тактов цифрового накопителя 4 р Л I

его переполнение возникает - i раз. В этих тактах Ku(i)

I- Л1

Kj + 1, а в остальных К„(1) К

Тогда

+ 1) i +

il)}

1 Набег фазы к i-му опорному импульсу равномерного потока J 2ffKfi.

Поэтому для фазовой ошибки &.Cf ;

i-ro опорного импульса можно записать

-8

UQ; ч-и; - л I /- л f Т 1

- (1К + ij)j

г, Г.тт 211 iK - .

Из этого вьфажения с учетом формулы (2) следует, чтоЛср; 2TK((i). Временное смещение i-ro опорного импульса с учетом (3) определяется соотношением

Т.

21Г-К((1) 2 ir

К,

Т

Ky(i)

Кг

(4)

Длительность i-ой, группы изменяется по .сравнению с 2 , Т на (ut(i) -ut(i-l), а расстояние между импульсами внутри группы - соответственно на ut(i) - ut(i-l)/Kud). Тргда для получения равномерного выходного сигнала синтезатора частот импульс, предшествующий опорному

и имеквдий номер 1 Кь(1) - 1, необходимо дополнительно сместить на Ut(i) - ut(i-1)/K(i, K(i) - ;

- на (i) - ut(i-l) /K.(i) и т.д.

Таким образом, алгоритм коррекции можно записать в виде

ut,(i,l) ut(i) -.

ut(i) - ut(i-l) +

K(i)

о

..(«J

0

5

+ tnocT ()

Перегруппировав слагаемью, получим более удобную для реализации формулу ( 1) .р,

Докажем теперь, что .2 ..; TQ Т. Для этого рассмотрим три возможных случая; р

K K Т.е. на разрядные входы накапливающего сумматора 7 поступает нулевой код, а код управления K(L.(i) на его выходе принимает отличное от нуля значение, равное 1, лишь при переполнении цифрового накопителя 4, когда K((i) K . Тогда

ut(i) (i)/K Т„К (i)«

о А ll р

X 2 2 Т„ &t,e.

р -р 4-1

Ku(i) на выходе накапливающего сума

i liJJJ.JJ4X4 t lJtfk /IMI IJ

a при Ku(i) 2 - два импульса, этом из .формулы (1) следует, чт(

9 14

матора 7 равен 1 или 2. Соответствую- дще группы импульсов на выходе ДПКД 2 равномерны и для них л , 1)0.

Каждая группа при ) 1 содержит только один (опорный) импульс,

При

что временной сдвиг второго импульса группы (1 1) или Ku(i) 2 определяется средним арифметическим сдвигом i-ro. .и (i-l)-ro опорных импульсов, т.е. меньше наибольшего из них. Поэтому для определения величины . в рассматриваемом случае можно ограни- читься анализом временных смещений лишь для опорных импульсов, т. е. величин ut(i). Так как Ku(i) 1, можно записать

Д t(i) (i)/K.j 2 TO Q

-Р 3. . При этом, очевидно,

At(i) Т,.

Группы импульсов на выходе ДПКД 2 неравномерны, но всегда могут быть сформированы таким образом, что () Т Поэтому можно записать для наихудшего случая ,l ( + I)TO 0,6 2р .Т„ 0,6Т.

Таким образом, утверждать, что величина равна 2 х Т Т.

В предлагаемом, синтезаторе частот основанном на новом алгоритме синтеза и коррекции времен положе ния импульсов, за счет снижения в несколько раз частоты тактирования вычислительных блоков удается полностью использовать частотные возможности применяемой элементной бдзы и расширить диапазон синтезируемых частот вплоть до предельной частоты переключения одного триггера,

Делитель 2 с переменным коэффициентом деления может быть выполнен, например, -по схеме, показанной на фиг. 4. По (р + 1)-разрядному коду K(i) пре образователь 10 кодов фор- мирует 2 -разрядный код (i), содержащий Ki,,(i) единиц, распределенны с максимальной равномерностью. Ниже приведен один из вариантов таблицы истинности преобразователя 10 кодов для р 3.

Код Kgj,(i) поступает, на входы параллельной записи 2 -разрядного ре65

10

g

0

5

0

5 0 5

0 5

гистра 11 и заносится в него в момент поступления импульса с выхода опорного генератора 1 при единичном сигна-1 ле на установочном входе ДПКД 2. При нулевом входном сигнале на установочном входе ДПКД 2 код K.d) в регистре 11 с каждым импульсом опорного генератора 1 сдвигается в сторону старших разрядов. На выходе D-триг- гера 12 формируются логические сигналы длительностью Т, которые затем преобразуются элементом И ТЗ в импульсы неравномерной выходной последовательности ДПКД 2, длительность которых равна длительности импульсов опорного генератора 1. При этом опорный импульс (1-1)-й группы формируется в момент записи в регистр 11 кода K,,,,(i).

Управляемый блок 3 задержки может быть выполнен в соответствии с фиг. 5. Нерегулируемая часть представляет собой регистр И сдвига на 2 разрядов, тактируемый импульсами опорного генератора 1. Регулируемая часть также содержит регистр 15 сдвига, выходы 2 -разрядов которого подключаются к входу линии 18 задержки с отводами через коммутатор 16, управляемый старшими разрядами кода коррекции K(is,l). Нпадшие разряды поступают на коммутатор 17, под-; ключающий соответствукнций отвод лиг НИИ 18 задержки, максимальное время распрост ранения сигнала по которой равно Тр. Запаздывание i-ro выходного импульса управляемого блока 3 задержки относительно соответствующего входного определяется.соотношением

Td,) 2 т, 2 - K(i,l)/2, .

где R - число разрядов кода . О K.(i,l) 1.

Блок 6 формирования кода частоты для синтезатора частот в соответствии с фиг. 6 может быть выполнен в виде блока 19 переключателей и ре- гиdтpa 20. С помощью переключателей блока 19 можно установить двоичный код требуемой частоты, который выходным импульсом делителя 5 частоты вписывается в регистр 20 и с его выхода поступает на выход блока 6.

Блок 8 группового формирования кодов коррекции выполняет операции согласно алгоритму (1). Код частоты Кг(1), записанный предыдущим тактр11 1 вьгм импульсом в регистре 21, посту- пает на адресные входы первого блока 2А хранения кодов обратных величин, выходной код которого, пропорцио- нальньгй величине 1/K(i), перемножается затем с кодом Ky,(i).B первом перемножителе 26. Результат перемножения согласно формуле (4) пропорционален величине ut(i). С инверсно- го выхода регистра 23 и с выхода первого пёI eмнoжитeля 26 кодов на входы -сумматора 28 поступают код вычисленного в предыдущем такте значения величины -ut(i-t) и код величи мы ut(i) соответственно. Его выходной код, пропорциональный величине ) - &t(i-1)l, перемножается с кодом величины 1/Кц(1), формируемым во втором блоке 25 хранения кодов обратных величин по входному коду Ko(i). Полученньй в результате перемножения код Rj,, пропорциональный ut(i) )/Kyd) , поступает с выхода второго перемножителя 27 ко- дов на вход блока.32, формирования кратньпс кодов, на 2 выхода которого при этом поступают коды Ki, 2К, ..., 2 Kjj. В примере на фиг. 5 р 3. Коэффициенты умножения 2, 4 и. 8 реализуется сдвигом входного кода влево соответственно на 1, 2 и 3 позиции. Правила формирования остальны выходов кодов:

° ь,

. сумматором 33;

ь ь . ьо/

сумматором 34;

сдвигом кода ЗКI на 1 разряд влево)

вычитающим бло ком 35).

На выход блоков 31 .1,... ,31 jij при N 8 хранения кодов фиксированных смещений поступают коды величин (i,1),..-,utnj, (i,8), соответствующие коду Ku(i). Группы суммато- ров 29.1,...,29.N и 30.1,...,30.N формируют коды коррекции ,), пропорциональные величинам utL,() которые поступают на выход блока 8 группового формирования кодов коррек ции вместе с кодом Ku(i). При Ku(i) 2 в каналах с номерами, большими, чем Ku(i)j возможны переполнения при вычислениях, однако выходные

65

12

коды этих каналов, хотя и записываются в блок 9 памяти, на его выход не проходят и не оказывают влияния на работу устройства.

Вариант реализации блока- 9 памяти показан на рис. 8.

Коды K(i,l), вычисленные в (i - - 1)-м такте в блоке 8 группового формирования кодов коррекции поступают на цопарно соединенные информационные входы первой 36 и второй 37 групп регистров.

Запись п-разрядов кода К,(1,1) производится в их последние, восьмые разряды, запись кода K(i,2) - в предпоследние и т.д. При этом в первый регистр группы регистров 36 и 37 заносятся первые разряды кодов K(i,l), во второй - вторые и т.д. Выходной импульс делителя 5 частоты переключает первый счетный 42 триггер. Взаимно инверсные выходные сигналы триггера 42 поступают на входы записи групп регистров 36 и 37,имеющие абсолютный приоритет перед другими управляющими входами. По переднему фронту импульса записи происходит запись кодов Ki(i,l) в первую или вторую группу регистров 36 или

37и кода K(i) соответственно в первый или второй параллельный регистр

38или 39.

Выходные импульсы управляемого блока 3 задержки поступают на входы сдвига первой или второй группы регистров 36 или 37 через первый или второй ключ 44 или 45 соответственно и, кроме того, на счетный вход управляемого счетчика 46. Код Ku(i), поступающий на информационный вход управляемого счетчика группы регистров 36 и 37 с выхода первого или второго параллельного регистра 38. или 39 через мультиплексор 41, определяет, какой по счету импульс прой- дет с него на выход. Этот выходной импульс изменяет на противоположное состояние второго счетчика триггера 43, который управляет первым и вторым мультиплексорами 40 и 41 и первым и вторым ключами 44 и 45.

Первый и второй параллельные регистры 38 и 39, второй мультиплексор 41, управляемый счетчик 46 и второй счетный триггер 43 позволяют вьщелит в выходном потоке опорные импульсы. Необходимость введения для этого специальных устройств обусловлена

13

несинхронностью появления выходных импульсов синтезатора частот с тактами опорного генератора 1.

В исходном состоянии первый и втрой счетные триггеры 42 и 43 находятся в состоянии логического нуля. При этом первый мультиплексор 40 подключает к выходу блока 9 памяти выход второй группы ре гистров 37, ч рез второй мультиплексор 41 на инфомационный вход управляемого счетчик 46 поступает выходной код второго параллельного регистра 38, а выходные импульсы управляемого блока 3 задержки проходят через открытый второй ключ. 45.

С приходом i-ro тактового импулса .(t i T) на вход записи блока 9 памяти коды K(i,l) заносятся во вторую группу регистров 37, а код Кц(1) - во второй параллельный ре- гистр 39. В этот момент на вход регулируемой части управляемого блока 3 задержки начинают поступать импул сы-1-й группы. Каждый выходной импульс управляемого блока 3 задержки тактирует управляемый счетчик 46 и, кроме того, проходит через второй

-КЛЮЧ 45, обеспечивая сдвиг информа- дни во второй группе регистров 37. При этом на выходе блока 9 памяти оказывается код. коррекции следующег импульса. Так как коэффициент пересчета управляемого счетчика 46, за- данный кодом, поступающим с выхода второго параллельного регистра 39, равен Км(t), то последний (опорный) импульс группы проходит с входа этого счетчика на его выход и пере- ключает второй счетный триггер 43 в противоположное состояние. Соот- BefcTBeHHo переключаются первый и второй мультиплексоры 40 и 41, а таже первый и второй ключи 44 и 45. К этому моменту в первую группу регисров 40 и в первый регистр 38 уже за

писаны коды Ko-Ci) и код K,,(t) со

J

ответственно.

Действительно, опорный импульс i-и группы оказывается на выходе управляемого блока 3 задержки в. момен времени t, iT.j. + TT- , где определяет длительность группы, О tTi Т - задержка, вносимая регули руемой частью управляемого блока 3 задержки при коррекции i-ro опорного импульса. Очередной (1--1.)-й так- товьш импульс поступает на вход за

65

14

писи блока 9 памяти в момент t .iT-r + Т, т. е. не позже момента t,. По (1+1)-му тактовому импульсу первый счетный триггер 42 переходит в состояние О, и передний фронт сигнала на его инверсном выходе осуществляет запись КОДОВ-в первую группу регистров 36 и первый регистр 38.

В интервал времени между (i+1)-M и ()-M тактовыми импульсами происходит переключение второго счетного триггера 43, первого и второго мультиплексоров 40 и 41, первого и второго ключей 44 и 45. В момент t, (i+2)«T во вторую группу регистров 37 записываются коды К,,(1+2,1), а во второй параллельный регистр 39 - код Ku(i+2), Далее процессы повторяются.

В предлагаемом синтезаторе частот реализован новый алгоритм синтеза и коррекции двухуровневых сигналов, основанный на использовании парал- лельного формирования информации о временном положении всех выходных импульсов синтезатора частот за определенный отрезок времени. Необходимая частота вычислений при этом ниже предельной синтезируемой и опорной частот во столько раз, во сколько длительность обрабатываемого отрезка выходной последовательности больше периода опорной частоты Т, т.е. в раз.

Фор м у ла изобретения

Синтезатор частот, содержащий последовательно соединенные опорный генератор и делитель частоты, цифровой накопитель, тактовый вход которого соединен с выходом делителя частоты, последовательно соединенные делитель частоты с переменным коэффициентом деления и управляемый блок задержки, а также блок формирования кода .частоты, выходы младших разрядо которого соединены с кодовым входом цифрового накопителя, о Т л и ч а ю- щ и и с я тем, что, с целью расширения диапазона частот синтезируемых сигналов, в него введены последовательно соединенные блок группового формирования кодов коррекции, первый кодовый вход которого соединен с выходом блока формирования кода частоты, а .второй кодовый вход - с кодовым выходом цифрового накопителя, и

1514

блок памяти, выход которого соединен с управляющим входом управляемого блока задержки, а также сумматор, разрядные входы которого соединены с соответствующими выходами старших разрядов блока формирования кода частоты, управляющий вход - с выходом сигнала переноса цифрового накопителя, а выход - с управляющим, входом делителя частоты с переменным коэффициентом деления и с третьим кодовым входом блбка группового формирования кодов коррекции, при этом выход де000000000000101

КуМ-З ML.I)

65

лителя частоты соединен с тактовым входом блока формирования кода частоты, с тактовым входом блока группового формирования кодов коррекции, с входом записи блока памятч и с установочным входом делителя частоты с переменным коэффициентом деления, выход опорного генератора соединен с

сигнальным входом делителя частоты с переменным коэффициентом деления и

с тактовым входом управляемого блока задержки, выход которого соединён с тактовым входом блока памяти.

I .

11101010 1 1 1 01 1.1 о 11111110

11111111

)-4

Фиа2

;|||||||| |HHmi(n(}iW.ff..

г 2 ЗА 56 7 8 S f0ff/2fS/4/S/6f7f8 IS 202122 23 24

Пri

П

fbixo9 дели/пела частоты 9

t /fc

Kfd)

Kud-l)

ЦА KyiL-ll l t f(t(i 2,i)

e

Ц(1}

Кц,(1,

ЗС

KtiL-U)

Ml)

Til II iiinrnir - ; iiiAj -. .- - г -

-I J I .1 I 11 II II

yi-2,4H,/ L-i,Z H,3 i.f L,Z 1,3 i.4 ,f H3 , бмка задерж i B odp eej/ m y 1-2., Hf i-(2 4/ a / 4 SXola

«LI I r I i r I I. 1 I i

Л..- - Выход

ri

Kf()

fbixo9 дели/пела частоты 9

Kyd.n

7Ь

riri

Кц,(1,

ЗС

Ml)

Фиг. 4

Ч

/Joe.f

Фиг. 5

20

Т

Тактобый бход

Фаг.6

f

Тактобшй

5Z

2Щ тм. 1Ш

И

тг

1Л

Iz

1Г

|Ш

J/7.J

j Ч Г К Ч -Ч ,

Ау/// /СА/Л ) Kt{i,2) ((аМ tii.5) .«tljr }(,8)

J(.

J/.5

Фиг.7

| Цифровой синтезатор частот | 1981 |

|

SU978314A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США № 3976945, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1988-08-15—Публикация

1987-02-26—Подача