ел ю

СП

о: со

IS

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ЗАЩИТЫ ИНФОРМАЦИИ В СЕТЯХ СВЯЗИ | 2005 |

|

RU2295195C1 |

| Цифровой синтезатор частот | 1989 |

|

SU1691926A1 |

| Цифровой синтезатор фазоманипулированных сигналов | 2019 |

|

RU2701050C1 |

| Цифровой синтезатор с М-образным законом изменения частоты | 2017 |

|

RU2682847C1 |

| Синтезатор частот | 1987 |

|

SU1417165A1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2014 |

|

RU2566962C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ДВУХУРОВНЕВЫХ СИГНАЛОВ | 2013 |

|

RU2540796C1 |

| Цифровой вычислительный синтезатор двухчастотных частотно-модулированных сигналов | 2024 |

|

RU2826705C1 |

| Цифровой вычислительный синтезатор двухчастотных сигналов | 2019 |

|

RU2710280C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР | 2005 |

|

RU2286645C1 |

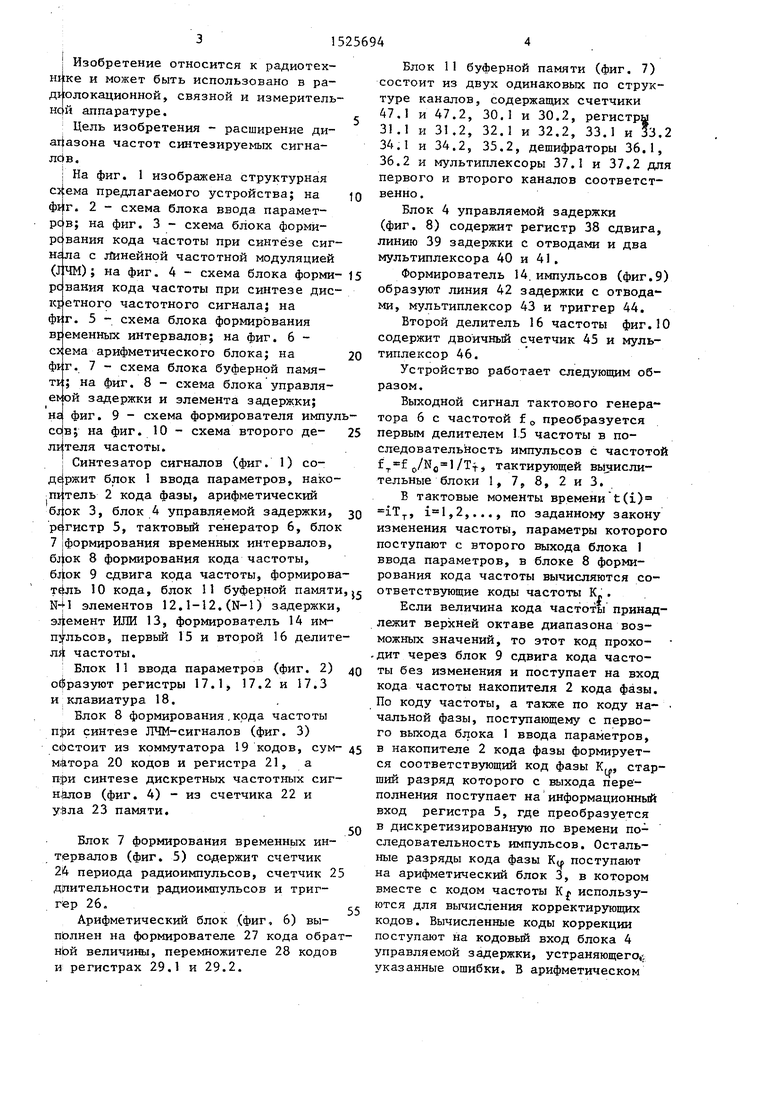

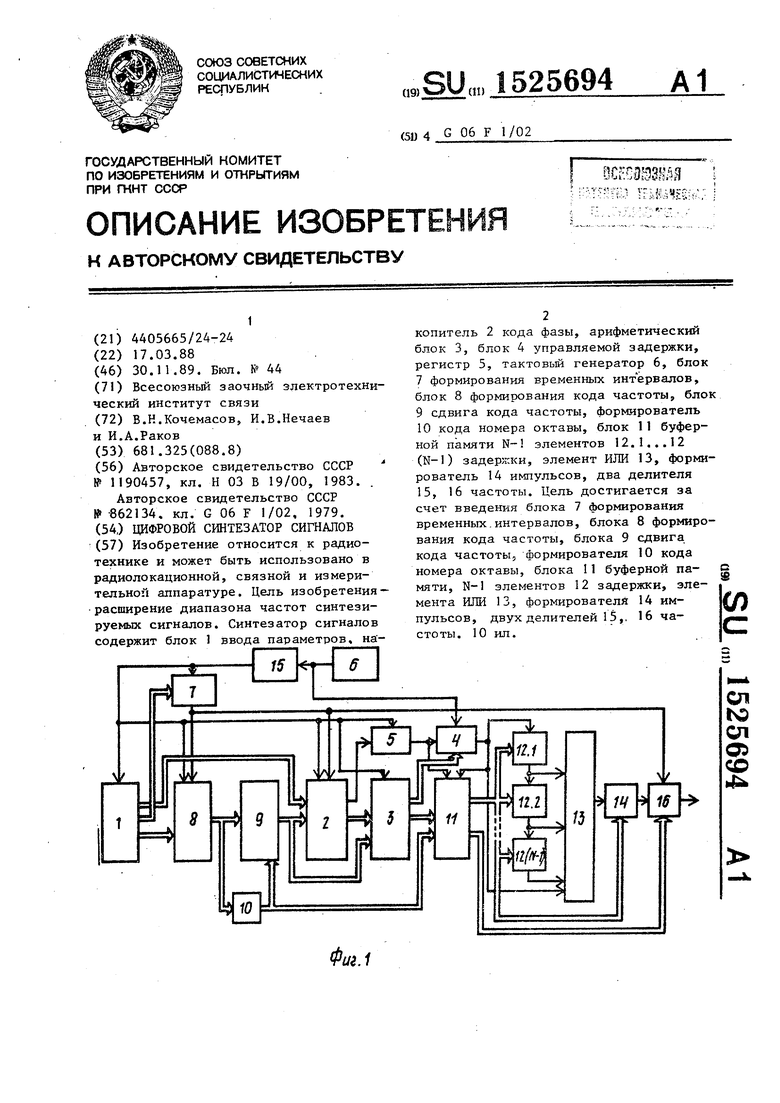

Изобретение относится к радиотехнике и может быть использовано в радиолокационной, связной и измерительной аппаратуре. Цель изобретения - расширение диапазона частот синтезируемых сигналов. Синтезатор сигналов содержит блок 1 ввода параметров, накопитель 2 кода фазы, арифметический блок 3, блок 4 управляемой задержки, регистр 5, тактовый генератор 6, блок 7 формирования временных интервалов, блок 8 формирования кода частоты, блок 9 сдвига кода частоты, формирователь 10 кода номера октавы, блок 11 буферной памяти, N - 1 элементов 12.1... 12 (N - 1) задержки, элемент ИЛИ 13, формирователь 14 импульсов, два делителя 15, 16 частоты. Цель достигается за счет введения блока 7 формирования временных интервалов, блока 8 формирования кода частоты, блока 9 сдвига кода частоты, формирователя 10 кода номера октавы, блока 11 буферной памяти, N - 1 элементов 12 задержки, элемента ИЛИ 13, формирователя 14 импульсов, двух делителей 15, 16 частоты. 10 ил.

fc.f

I Изобретение относится к радиотехнике и может быть использовано в ра- дрюлокационной, связной и измеритель- нсй аппаратуре.

Цель изобретения - расширение ди- аг}азона частот синтезируемых сигналов.

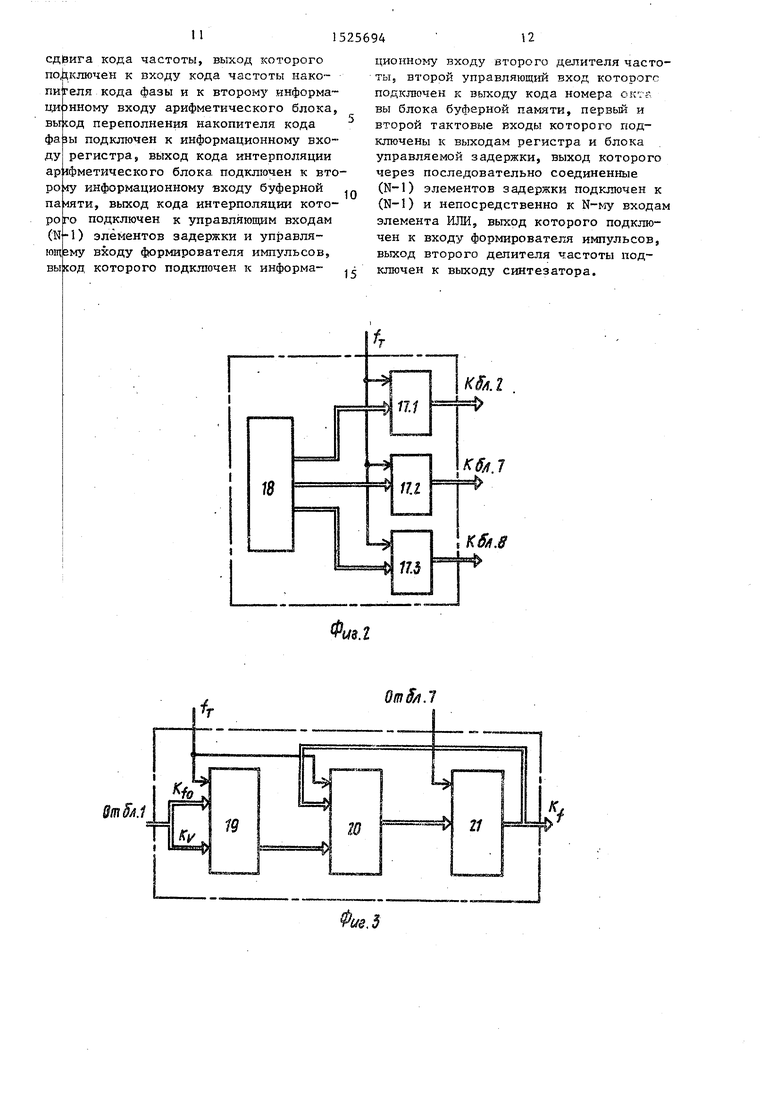

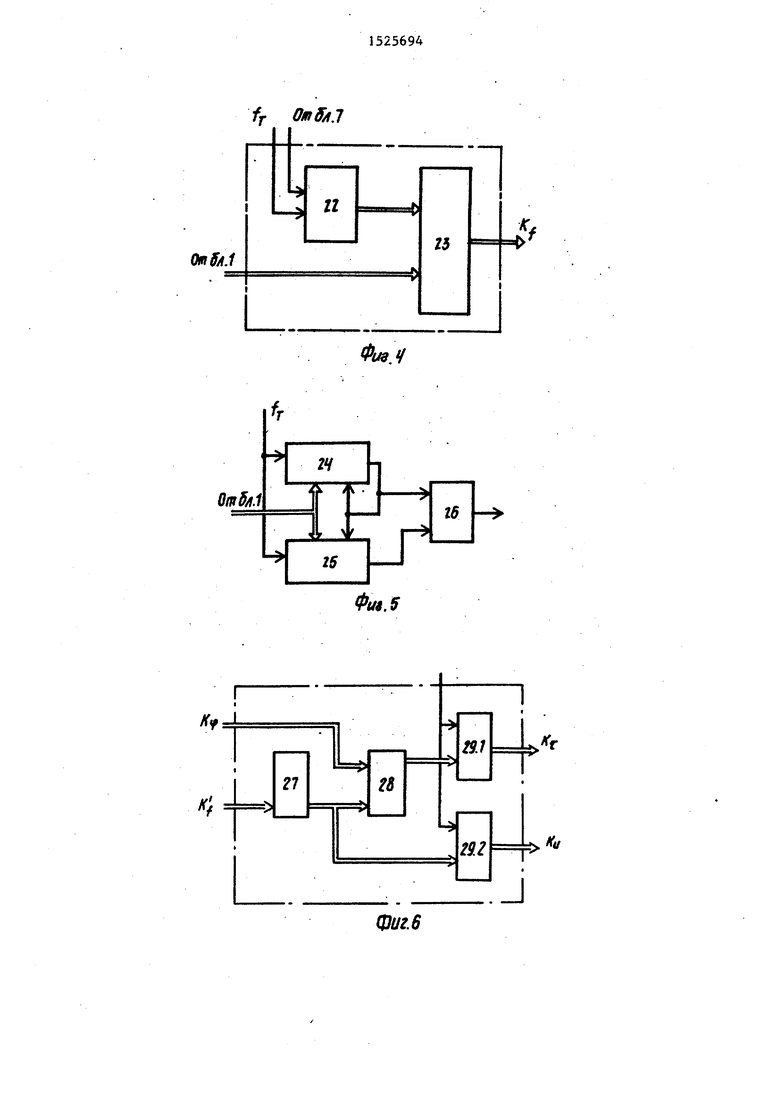

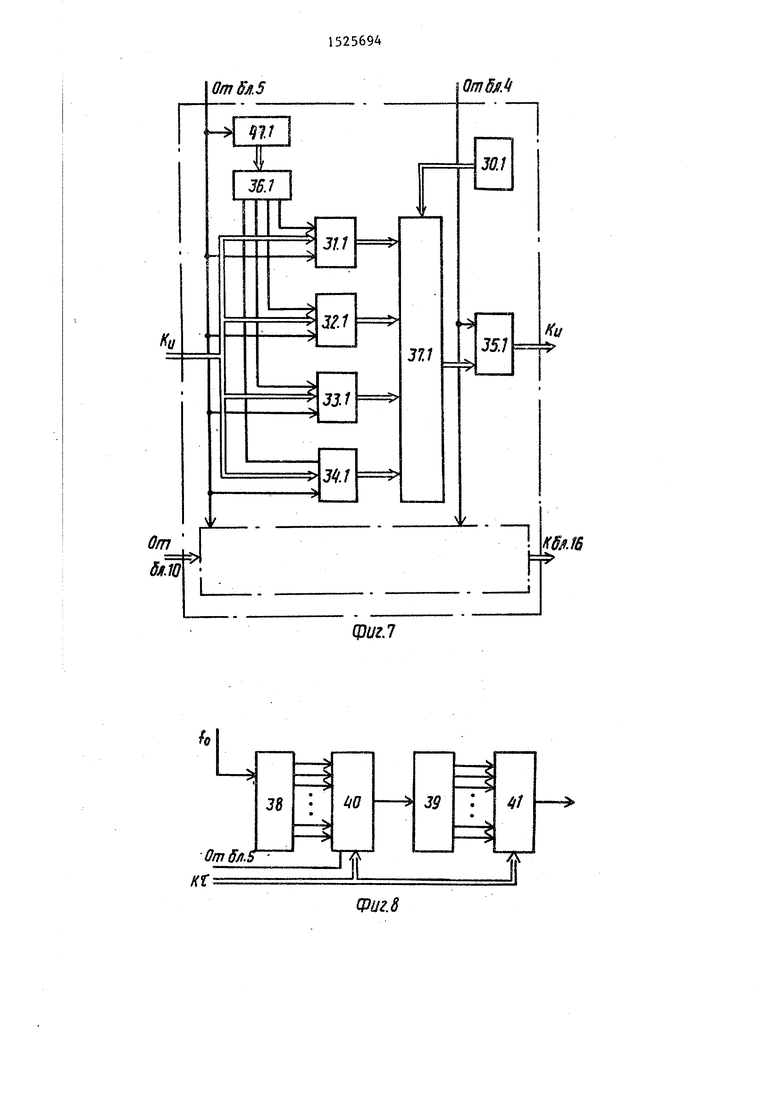

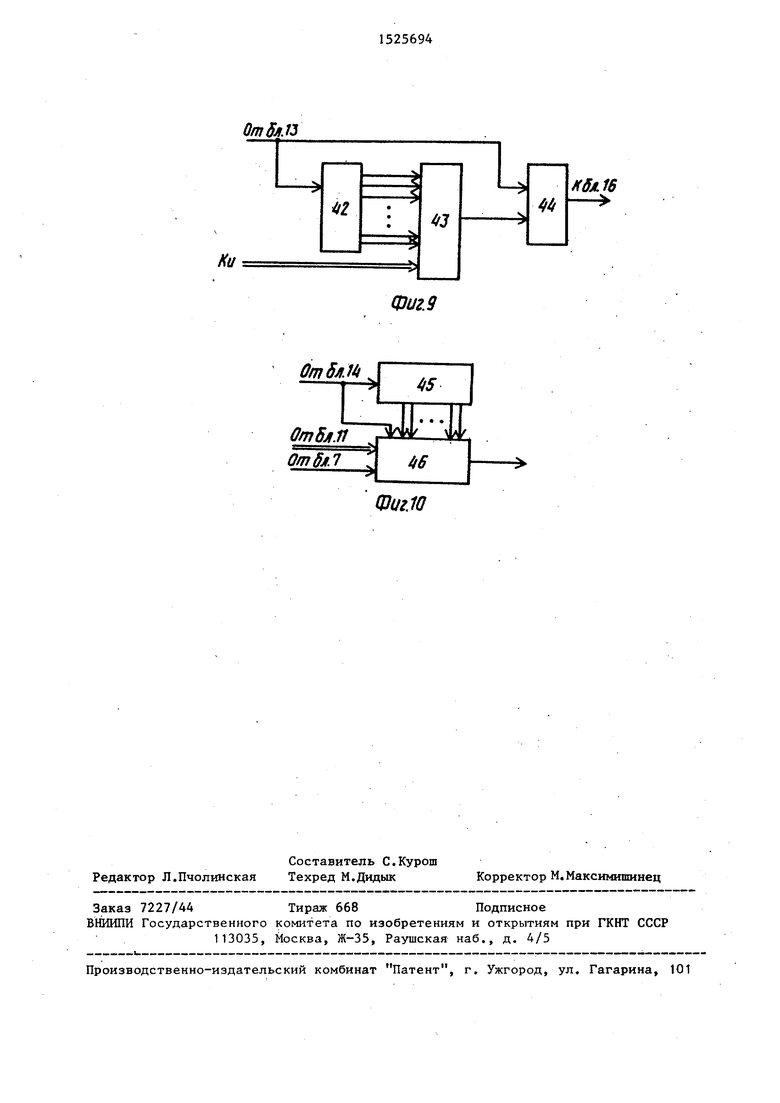

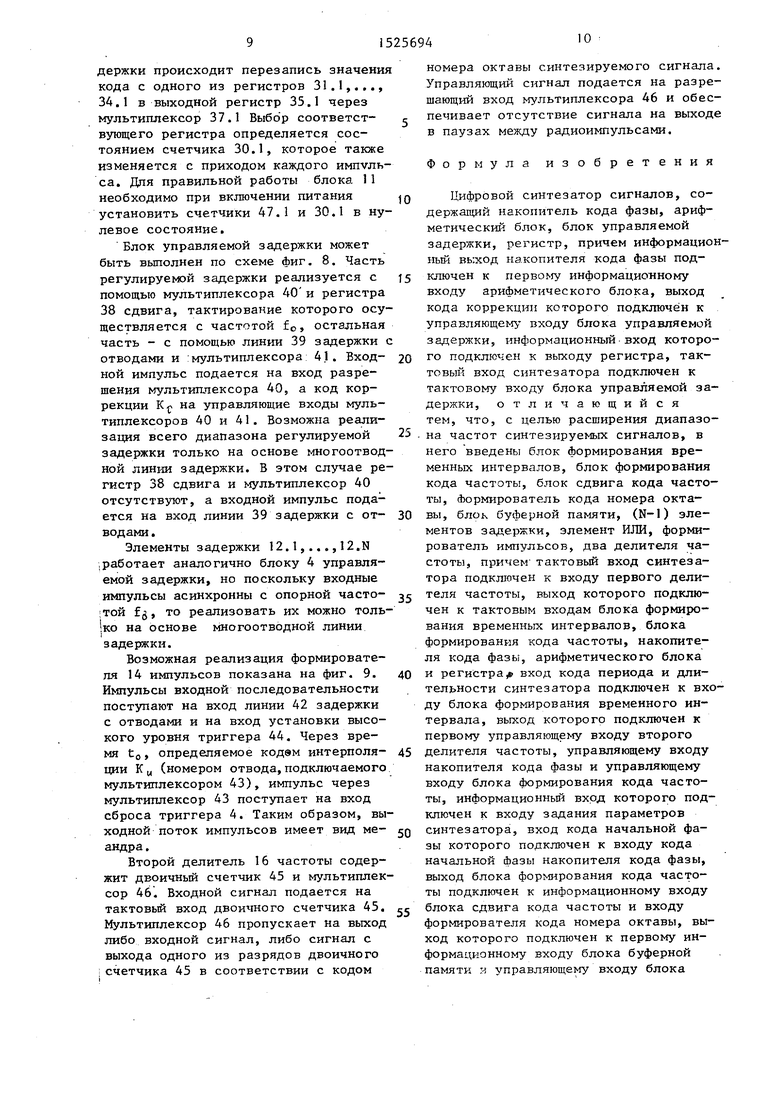

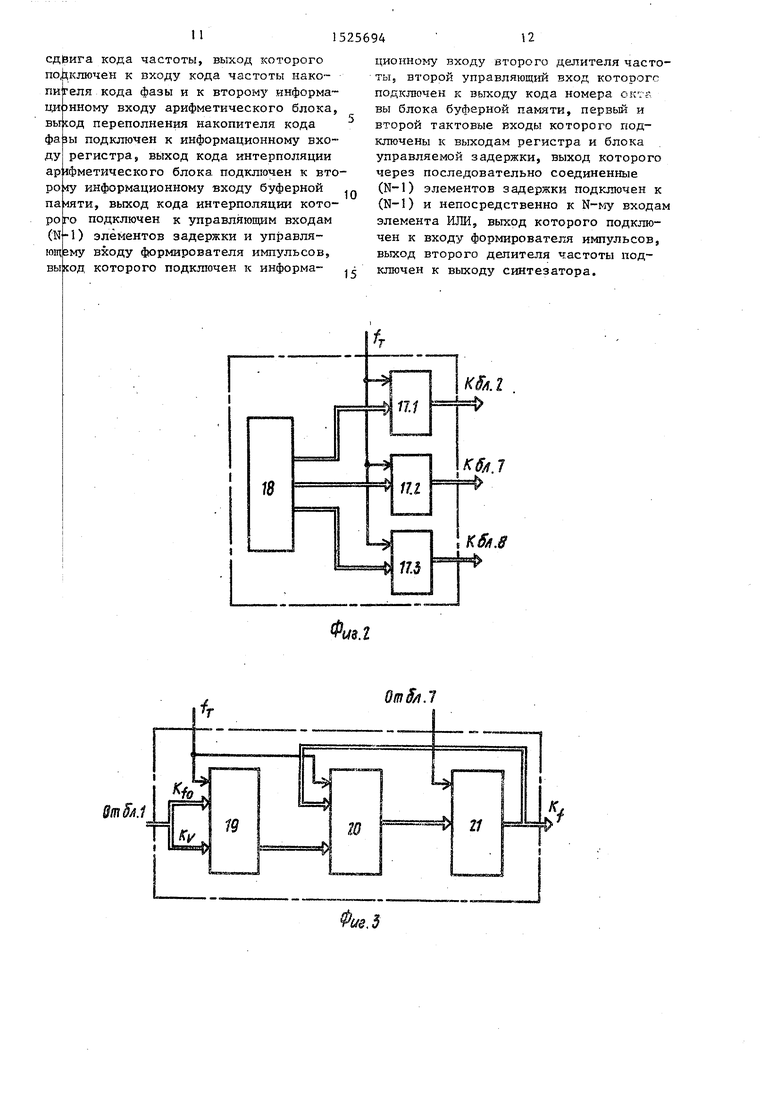

I На фиг. 1 изображена структурная предлагаемого устройства; на ФРГ. 2 - схема блока ввода параметре в; на фиг. 3 - схема блока формй- рсвания кода частоты при синтезе сиг- игла с Jй нeйнoй частотной модуляцией QЧМ); на фиг. 4 - схема блока форми- рсвания кода частоты при синтезе дис- щетного частотного сигнала; на . 5 - схема блока формирования вгеменных интервалов; на фиг. 6 ема арифметического блока; на г. 7 - схема блока буферной памя- на фиг. 8 - схема блока управляс ема арифметического блока; на 20 тк

ейой задержки и элемента задержки; на фиг. 9 - схема формирователя импульсов; на фиг. 10 - схема второго де- 25

ли

теля частоты.

Синтезатор сигналов (фиг. 1) со- дб(ржит блок 1 ввода параметров, нако- П1::тель 2 кода фазы, арифметический 6j;OK 3, блок 4 управляемой задержки, регистр 5, тактовый генератор 6, блок 7 формирования временных интервалов, б4ок 8 формирования кода частоты, 9 сдвига кода частоты, формирова 10 кода, блок П буферной памяти N-fl элементов 12.1-12. (N-1) задержки, элемент ИЛИ 13, формирователь 14 им- п льсов, первый 15 и второй 16 делите л частоты.

Блок 11 ввода параметров (фиг. 2) образуют регистры 17.1, 17.2 и 17.3 и клавиатура 18.

Блок 8 формирования,кода частоты при синтезе ЛЧМ-сигналов (фиг. 3) состоит из коммутатора 19 кодов, сум- матора 20 кодов и регистра 21, а при синтезе дискретных частотных сиг- н,алов (фиг. 4) - из счетчика 22 и у:&ла 23 памяти.

Блок 7 формирования временных интервалов (фиг. 5) содержит счетчик 24 периода радиоимпульсов, счетчик 2 д пительности радиоимпульсов и триггер 26.

Арифметический блок (фиг, 6) выполнен на формирователе 27 кода обра нЬй величины, пepe ffioжитeлe 28 кодов н регистрах 29.1 и 29.2.

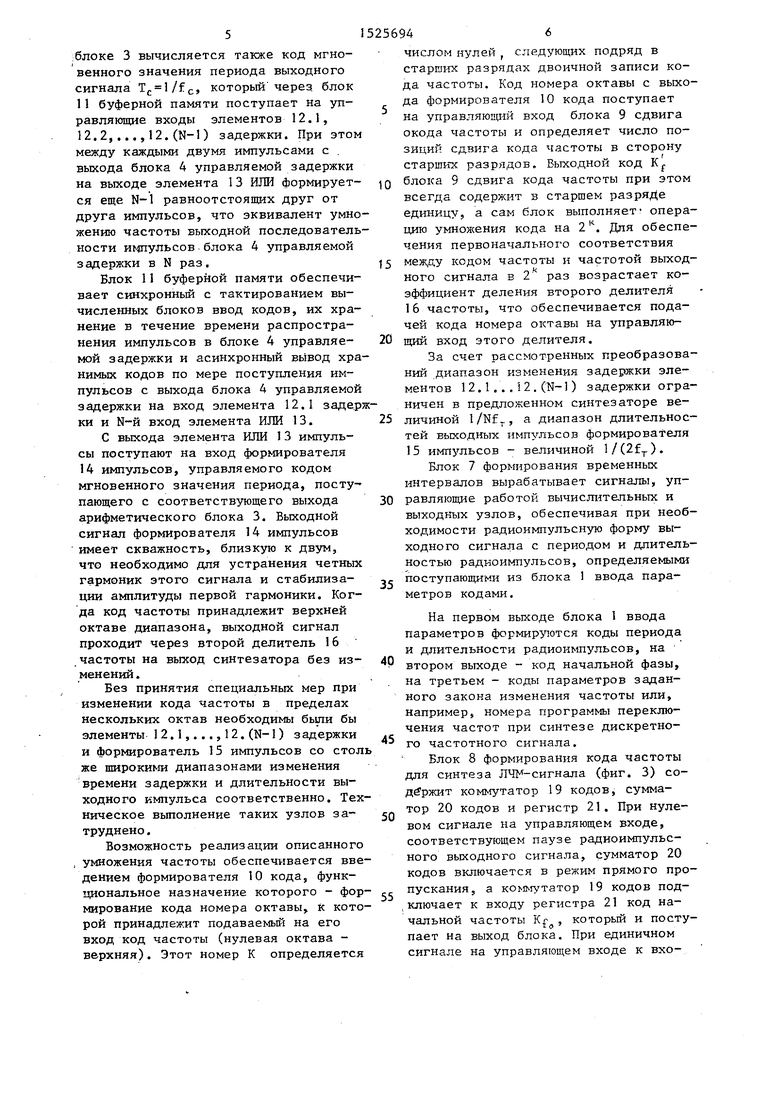

Блок 11 буферной памяти (фиг. 7) состоит из двух одинаковых по структуре каналов, содержащих счетчики 47.1 и 47.2, 30.1 и 30.2, регистры 31.1 и 31.2, 32.1 и 32.2, 33.1 и 33.2

Блок 4 управляемой задержки (фиг. 8) содержит регистр 38 сдвига, линию 39 задержки с отводами и два мультиплексора 40 и 41.

Формирователь 14, импульсов (фиг.9) образуют линия 42 задержки с отводами, мультиплексор 43 и триггер 44.

Второй делитель 16 частоты фиг.10 содержит двоичный счетчик 45 и мультиплексор 46.

Устройство работает следующим образом.

Выходной сигнал тактового генератора 6 с частотой f о преобразуется первым делителем 15 частоты в последовательность импульсов с частотой c,/No l/T-t-, тактирзпощей вычислительные блоки 1, 7, 8, 2иЗ,

В тактовые моменты времени t(i) iT, ,2,..., по заданному закону изменения частоты, параметры которого поступают с второго выхода блока 1 ввода параметров, в блоке 8 формирования кода частоты вычисляются соответствующие коды частоты К„.

Если величина кода частоты принадлежит верхней октаве диапазона возможных значений, то зтот код прохо- дит через блок 9 сдвига кода частоты без изменения и поступает на вход кода частоты накопителя 2 кода фазы. По коду частоты, а также по коду на- чальной фазы, поступающему с первого выхода блока 1 ввода параметров, в накопителе 2 кода фазы формируется соответствующий код фазы К,-,, старший разряд которого с выхода переполнения поступает на информационньй вход регистра 5, где преобразуется в дискретизированную по времени последовательность импульсов. Остальные разряды кода фазы К(| поступают на арифметический блок 3, в котором вместе с кодом частоты К используются для вычисления корректир1тощих кодов. Вычисленные коды коррекции поступают на кодовьй вход блока 4 управляемой задержки, устраняющего,-, указанные ошибки. В арифметическом

10

15

20

блоке 3 вычисляется также код мгновенного значения периода выходного сигнала I /f., который через блок 11 буферной памяти поступает на управляющие входы элементов 12.1, 12.2,...,12.(N-1) задержки. При этом между каждыми двумя импульсами с выхода блока 4 управляемой задержки на выходе элемента 13 ИЛИ формируется еще N-1 равноотстоящих друг от друга импульсов, что эквивалент умножению частоты выходной последовательности импульсов блока 4 управляемой задержки в N раз.

Блок 11 буферной памяти обеспечивает синхронный с тактированием вы- числеьшых блоков ввод кодов, их хранение в течение времени распространения импульсов в блоке 4 управляемой задержки и асинхронный вывод хранимых кодов по мере поступления импульсов с выхода блока 4 управляемой задержки на вход элемента 12.1 задержки и N-й вход элемента ИЛИ 13.

С выхода элемента ИЛИ 13 импульсы поступают на вход формирователя 14 импульсов, управляемого кодом мгновенного значения периода, поступающего с соответствзтощего выхода арифметического блока 3. Выходной сигнал формирователя 14 импульсов имеет скважность, близкую к двум, что необходимо для устранения четных гармоник этого сигнала и стабилизации амплитуды первой гармоники. Когда код частоты принадлежит верхней октаве диапазона, выходной сигнал проходит через второй делитель 16 частоты на выход синтезатора без изменений .

Без принятия специальных мер при изменении кода частоты в пределах нескольких октав необходимы бьши бы элементы 12.1,...,12.(N-I) задержки и формирователь 15 импульсов со столь же широкими диапазонами изменения времени задержки и длительности выходного импульса соответственно. Техническое вьшолнение таких узлов затруднено .

Возможность реализации описанного умножения частоты обеспечивается введением формирователя 10 кода, функциональное назначение которого - фор- гс мирование кода номера октавы, к которой принадлежит подаваемьш на его вход код частоты (нулевая октава - верхняя). Этот номер К определяется

25

30

35

40

45

50

0

5

0

с

числом нулей , следующих подряд в старших разрядах двоичной записи кода частоты. Код номера октавы с выхода формирователя 10 кода поступает на управляюицш вход блока 9 сдвига окода частоты и определяет число позиций сдвига кода частоты в сторону старших разрядов. Выходной код К. блока 9 сдвига кода частоты при этом всегда содержит в старшем разряде единицу, а сам блок выполняет- операцию умножения кода на 2 . Для обеспечения первоначального соответствия между кодом частоты и частотой выходного сигнала в 2 раз возрастает коэффициент деления второго делителя 16 частоты, что обеспечивается подачей кода Номера октавы на управляющий вход этого делителя.

За счет рассмотренных преобразований диапазон изменения задержки элементов 12.1..,12.(N-) задержки ограничен в предложенном синтезаторе ве- 5 личиной I/Nf,, а диапазон длительностей выходных импульсов формирователя 15 импульсов - величиной l/(2f). Блок 7 формирования временных интервалов вырабатывает сигналы, управляющие работой вычислительных и выходных узлов, обеспечивая при необходимости радиоимпульсную форму выходного сигнала с периодом и длительностью радиоимпульсов, определяемыми поступающими из блока 1 ввода параметров кодами.

На первом выходе блока 1 ввода параметров формируются коды периода и длительности радиоимпульсов, на втором выходе - код начальной фазы, на третьем - коды параметров заданного закона изменения частоты или, например, номера программы переключения частот при синтезе дискретного частотного сигнала.

Блок 8 формирования кода частоты для синтеза ЛЧМ-сигнала (фиг. 3) со- дйржит коммутатор 19 кодов, сумматор 20 кодов и регистр 21. При нулевом сигнале на управляющем входе, соответствующем паузе радноимпульс- ного выходного сигнала, сумматор 20 кодов включается в режим прямого пропускания, а комм татор 19 кодов под- , кпючает к входу регистра 21 код начальной частоты Kf , который и поступает на выход блока. При единичном сигнале на управляющем входе к вхо0

5

0

5

0

ду сумматора 20 кодов, переключенного в режим суммирования, коммутато- роЦ 19 подключается код скорости ча- ст|этной модуляции К. При этом сумма гор 20 кодов и регистр 21 образуют накопитель кода, выполняющий цифровое интегрирование кода скорости и формирующий линейно изменяющийся код частоты..

Для синтеза дискретного частотно го сигнала блок 8 формирования кода частоты (фиг. 4) содержит счетчик 22 и узел памяти 23..Нулевым сигналом управления счетчик 22 устанавливается в начальное состояние. При единичном управляющем сигнале разрешается работа счетчика 22, которьй осуществляет последователь- ньй перебор адреса узла 23 памяти.

Не

выходе узла 23 памяти формируется

кед частоты, значение которого изменя ется в соответствии с заданной про- П аммой. Выбор необходимой программы осуществляется кодом йомера програм- мь1, поступающим с блока 1 ввода пара- ,

Блок 7 формирования верменных ин- т« рвалов (фиг. 5) представляет собой счетчик 24 периода радиоимпуль- сов и счетчик 25 длительности радио- шшульсов, выходы переполнения кото- piix подключены к входам триггера 26, Коды периода радиоимпульсов и длителности радиоимпульсов подаются на вхо ды предустановки соответствующих с Ьетчиков. Предустановка осуществляется импульсом переполнения счетчика 24 периода радиоимпульсов, i Накопитель 2 кода фазы выполнен и функционирует аналогично блоку 8 фор мНрования кода частоты для синтеза Л 1-сигнала (фиг. 3). При нулевом сигцале управления на выходе накопителя 2 кода фазы устанавливается код Н1ачальной фазы Ку , а при одиночном сигнале управления формируется код фазы в соответствии с кодом частоты, поступающим на вход.

Код коррекции К, устраняющий сшибки дискретизации, вычисляется в а1рифметическом блоке 3. Этот код определяется как

К.

Ы

Для формирования дополнительных импульсов необходимо знать их период Следования

с Г с

где f - частота сигнала на выходе

элемента ИЛИ 13.

Вычислив код интерполяции , мы можем определить значение необходимого периода следования

т;ь к

N «

0

5

О ,

0

5

0

5

где Т -г - период следования тактовых импульсов.

Код интерполяции К, подается на управляющие входы элементов 12.1,..., 12.(N-1) задержки, которые и обеспечивают формирование дополнительных импульсов в соответствующие моменты времени. Кроме того, код интерполяции Ку управляет формирователем 14 импульсов, который вырабатывает импульсы с длительностью . Вычисление кода интерполяции К у также происходит в арифметическом блоке 3 (фиг. 6).Код частоты К поступает на вход формирователя 27 кода обратной величины, С его выхода код интерполяции К поступает на вход регистра 29.2 и на первый вход перемножителя 28 кодов. На второй вход перемножителя 28 кодов поступает код фазы К, а на выходе формируется код коррекции , который поступает на вход регистра 29.1. Выходы регистров 29.1 и 29.2 являются выходами арифметического блока 3..

Коды на выходе арифметического блока 3 появляются с задержкой на такт относительно момента появления импульса переполнения на выходе накопителя 2 кода фазы. Для задержки этого импульса используется регистр 5.

Блок 11 буферной памяти содержит (фиг. 7) два идентичных канала, один из которых осуществляет задержку кода интерполяции Кц, а другой кода номера октавы формируемого сигнала. Рассмотрим работу одного из каналов. Импульс переполнения осуществляет запись соответствующего ему кода в один из регистров 31.1,...,34.1, номер которого определяется состоянием счетчика 47,1 и дешифратора 36.1. Кроме того, этот импульс увеличивает состояние счетчика на единицу, т.е. осуществляет подготовку схемы к записи следующего значения кода. При появлении импу.пь- са на выходе блока 4 управляемой задержки происходит перезапись значени кода с одного из регистров 31.1,..., 34.1 в выходной регистр 35.1 через мультиплексор 37.1 Выбо р соответст- вующего регистра определяется состоянием счетчика 30.1, которое также изменяется с приходом каждого ИМПУЛЬ са. Для правильной работы блока 11 необходимо при включении питания установить счетчики 47.1 и 30.1 в нулевое состояние.

Блок управляемой задержки может быть выполнен по схеме фиг, 8. Часть регулируемой задержки реализуется с помощью мультиплексора 40 и регистра 38 сдвига, тактирование которого осуществляется с частотой fc, остальная часть - с помощью линии 39 задержки отводами и :мультиплексора: 41. Вход- ной импульс подается на вход разрешения мультиплексора 40, а код коррекции К на управляющие входы мультиплексоров 40 и 41. Возможна реализация всего диапазона регулируемой задержки только на основе многоотводной линии задержки. В этом случае регистр 38 сдвига и мультиплексор 40 отсутствуют, а входной импульс подается на вход линии 39 задержки с от- водами.

Элементы задержки 12.1,...,12.N ;работает аналогично блоку 4 управляемой задержки, но поскольку входные импульсы асинхронны с опорной часто- :Той fg, то реализовать их можно только на основе многоотводной линии задержки.

Возможная реализация формирователя 14 импульсов показана на фиг. 9. Импульсы входной последовательности поступают на вход линии 42 задержки с отводами и на вход установки высокого уровня триггера 44. Через время t, определяемое кодам интерполя- ции К у (номером отвода,подключаемого мультиплексором 43), импульс через мультиплексор 43 поступает на вход сброса триггера 4. Таким образом, выходной поток импульсов имеет вид ме- андра.

Второй делитель 16 частоты содержит двоичный счетчик 45 и мультиплексор 46. Входной сигнал подается на тактовьш вход двоичного счетчика 45. Мультиплексор 46 пропускает на выход либо входной сигнал, либо сигнал с выхода одного из разрядов двоичного :счетчика 45 в соответствии с кодом

номера октавы синтезируемого сигнала Управляющий сигнал подается на разре щающий вход мультиплексора 46 и обеспечивает отсутствие сигнала на выход в паузах между радиоимпульсами.

Формула изобретения

Цифровой синтезатор сигналов, содержащий накопитель кода фазы, арифметический блок, блок управляемой задержки, регистр, причем информационый выход накопителя кода фазы подключен к первоьгу информационному входу арифметического блока, выход кода коррекции которого подключён к управляющему входу блока управляемой задержки, информационный вход которого подключен к выходу регистра, тактовый вход синтезатора подключен к тактовому входу блока управляемой задержки, отличающийся тем, что, с целью расщирения диапазона частот синтезируемых сигналов, в него введены блок формирования временных интервалов, блок формирования кода частоты, блок сдвига кода частоты, (Ьормирователь кода номера октавы, блок буферной памяти, (N-1) элементов задержки, элемент ИЛИ, формирователь импульсов, два делителя частоты, причем тактовьй вход синтезатора подключен к входу первого делителя частоты, выход которого подключен к тактовым входам блока формирования временных интервалов, блока формирования кода частоты, накопителя кода фазы, арифметического блока и регистра у вход кода периода и длительности синтезатора подключен к входу блока формирования временного интервала, выход которого подключен к первому управляющему входу второго делителя частоты, управляющему входу накопителя кода фазы и управляющему входу блока формирования кода частоты, информационньй вход которог;о подключен к входу задания параметров синтезатора, вход кода начальной фазы которого подключен к входу кода начальной фазы накопителя кода фазы, выход блока формирования кода частоты подключен к информационному входу блока сдвига кода частоты и входу формирователя кода номера октавы, выход которого подключен к первому информационному входу блока буферной памяти и управляющему входу блока

сдбига кода частоты, выход которого по ключен к входу кода частоты накопителя кода фазы и к второму информационному входу арифметического блока, вьгй:од переполнения накопителя кода фазы подключен к информационному входу ар

регистра, выход кода интерполяции ифметического блока подключен к вто

po:yiy информационному входу буферной памяти, выход кода интерполяции которого подключен к управляющим входам (N-1) элементов задержки и управля- ющвму входу формирователя импульсов, выкод которого подключен к информа-

.I

ционному входу второго делителя частоты, второй управляющий вход которого подключен к выходу кода номера октй вы блока буферной памяти, первьш и второй тактовые входы которого подключены к выходам регистра и блока управляемой задержки, выход которого через последовательно соединенные (N-1) элементов задержки подключен к (N-I) и непосредственно к входам элемента ИЛИ, выход которого подключен к входу формирователя импульсов, выход второго делителя частоты подключен к выходу синтезатора.

К.

ff OnS/tl

Ц

II

OnS/i.l

L..

Ontd/1.1

A

/Г

ZJ

Фиа,/

Z5

«.y

Ш

/г

/5

ffv

J

От

dm

-1

№/

rf

Ц)иг.7

Цзиг.Ь

/(6Л16

Фиг.9

Ши2,10

| Цифровой синтезатор частот | 1983 |

|

SU1190457A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Телеметрическое устройство | 1940 |

|

SU62134A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-30—Публикация

1988-03-17—Подача