диапазонов шириной L/T и для всей после- довательности { tn} нуль-пересечений формируется из Yi(l0/T) птем весового суммирования:

Y(b 2 wp () у, (k).

I1 I

(3)

02я(сМ)Ј,)

(За)

где d - 1,2,...,Q - номер поддиапазона в диапазоне рабочих частот,

ld lo+(d-1)L /3,Ј+ ,...,/3 + QL-1,

WQ(xi-i)ш ехр(J2 „()

коэффициенты.

Действительно, после подстановки (2) в (3) и замены 0 на ld-(d-1)L получаем I. Q ISKo|.

(Ј) 2, S,exp(.i)exp

11 1 rU 1-1 (Т Учитывая,что

tm. Atm.(m-1)+ + Atm.l

QL NnLAtm. F/QfH«1, приходим к выводу, что вторая экспонента в (За) равна 1. Следовательно:

Y(fe Sexp(-J25r a 1

что совпадает с алгоритмом накопления в(1) за исключением знака аргумента, который не влияет на модуль /Y(ld/T)/.

Для фиксированного значения 0 формула (3) представляет собой Q-точечное дискретное преобразование Фурье -(ДПФ) данных Yi(lo/T). i 1,2....,Q.

Дальнейшие преобразования в предлагаемом устройстве, включающие формирование квадрата модуля Z(ld/T) i Y(d/T)l2 и нахождение оценки частоть сигнала, как частоты td/Т, при которой Z(ld/T) принимает наибольшее из превысивших порог обнаружения значение, идентичны преобразованиям в устройстве-прототипе.

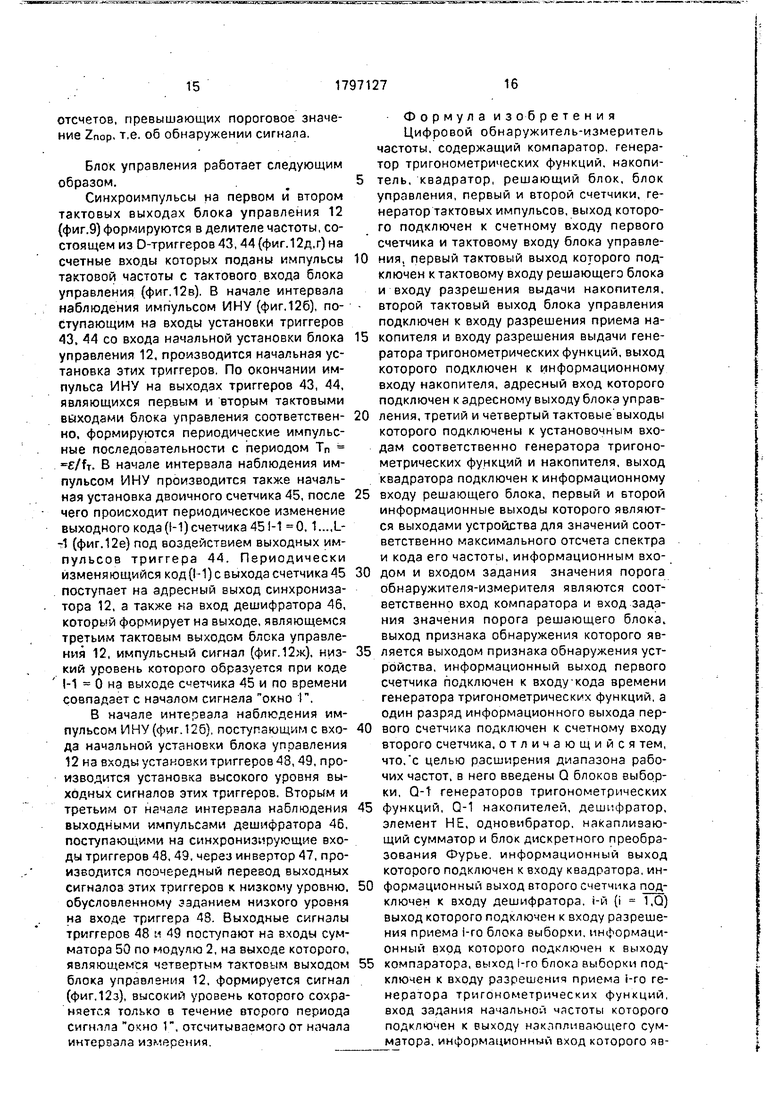

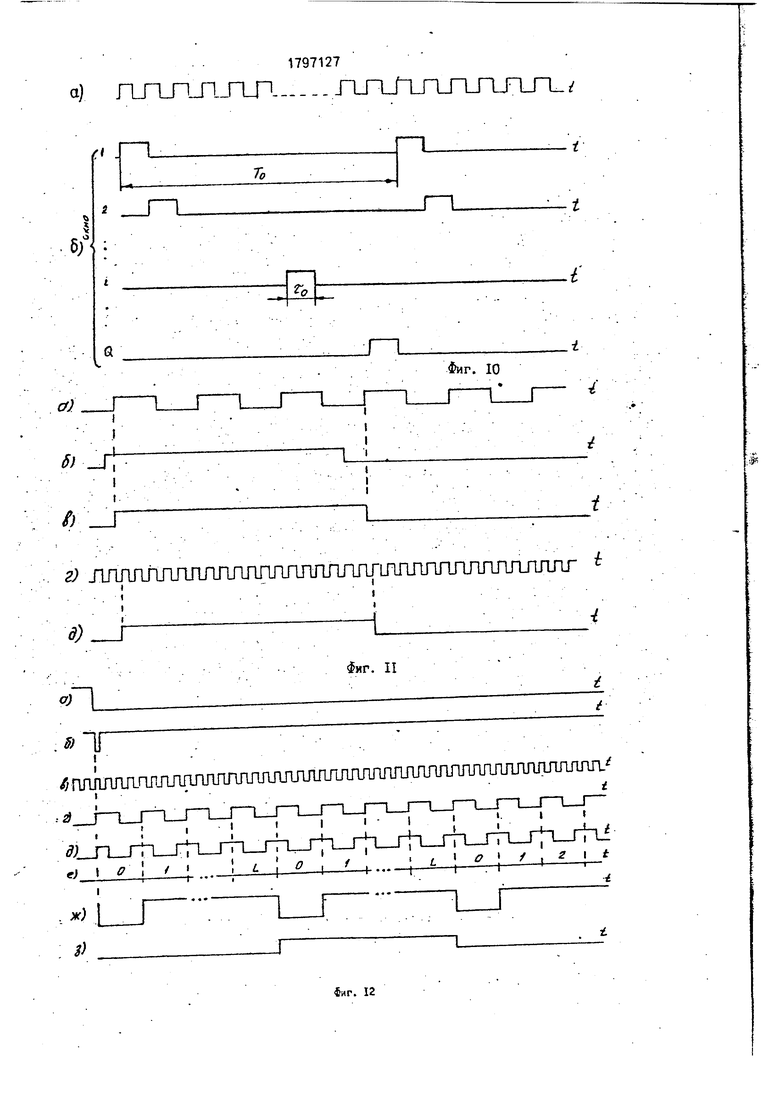

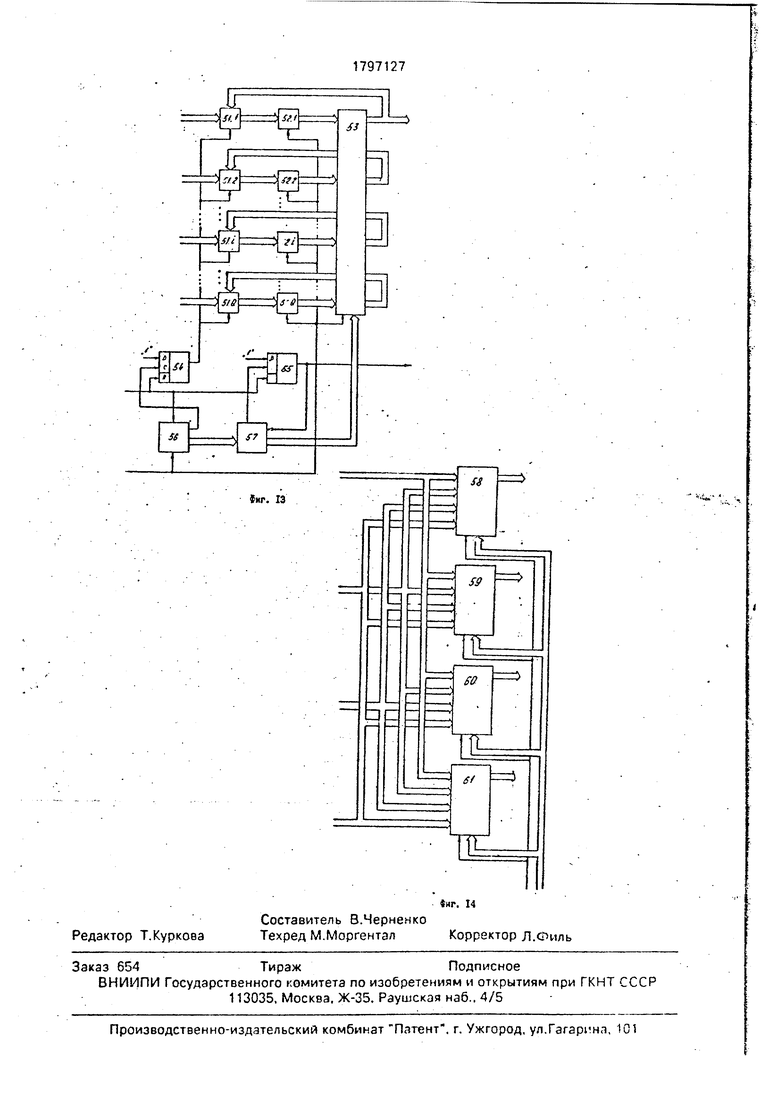

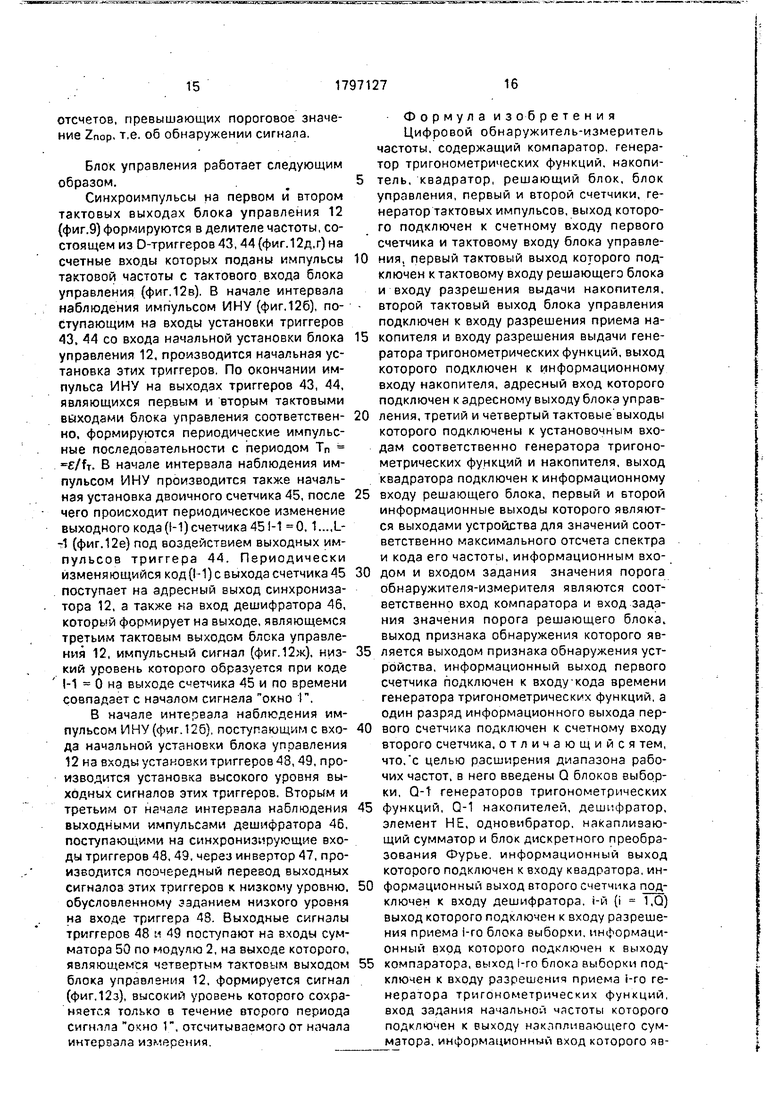

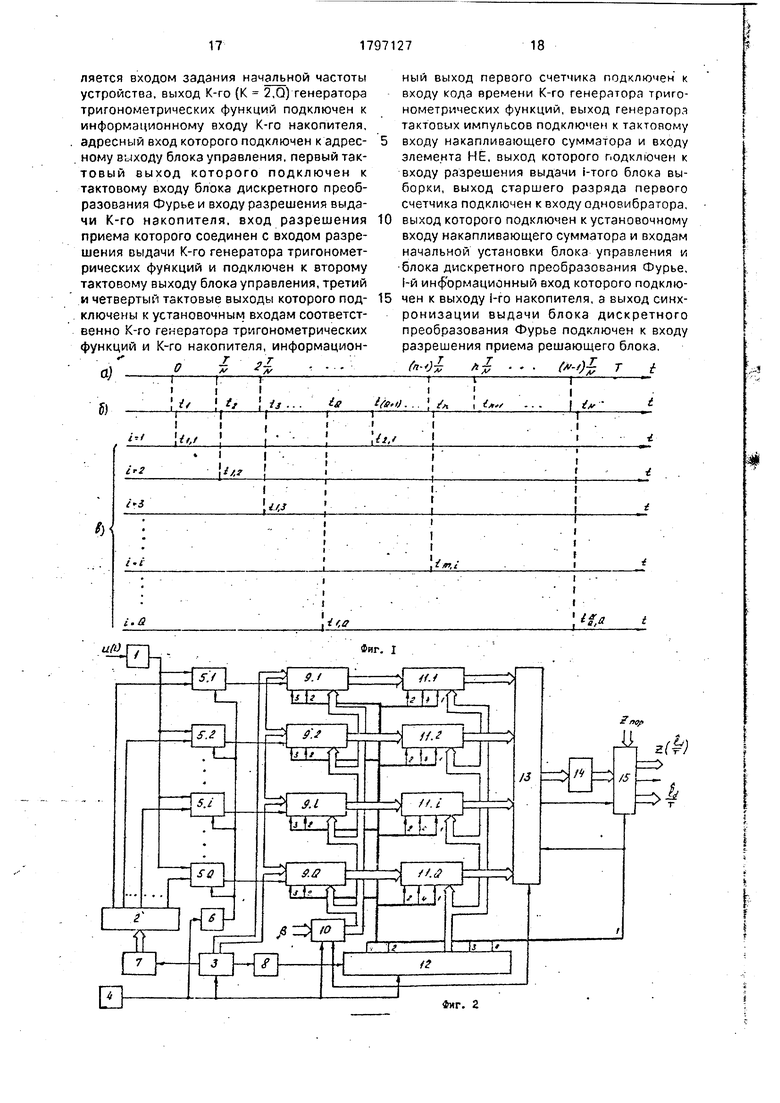

На фиг,2 приведена структурная схема предлагаемого обнаружителя-измерителя частоты, на фиг.З, 4. 5, 6, 7, 8 и 9 - примеры реализации схемы выборки, генератора тригонометрических функций, накопителя, сумматора комплексных чисел, решающего бпока, накапливающего сумматора и блока управления, на фиг.10-12 - эпюры сигналов, поясняющие работу цифрового обнару- жителя измерителя, на фиг.13 и 14 приведены пример реализации ДПФ для Q 4 и пример реализации арифметического устройства.

Цифровой обнаружитель-измеритель (фиг,2) содержит компаратор 1, дешифратор 2, пераый счетчик импульсов 3. генератор тактовых импульсов 4, схемы выборки 5.1 (I

1,2....,Q), элемент НЕ 6, второй счетчик импульсов 7. одновибратор 8, генераторы тригонометрических функций 9.i (i 1,2,....Q), наапливающий сумматор 10, накопители 11.1 (I 1,2,...,Q), блок управления 12, устройство дискретного преобразования Фурье 13, квадратор 14, решающий блок 15, вход задания порога обнаружителя, первый и второй информационные выходы - выходами обнаружителя для значений максимального отсчета спектра и кода его частоты соответственно, а выход признака обнаружения - выходом признака обнаружения сигнала обнаружителя.

5 Схема выборки 5.1 (фиг.З) содержит последовательно соединенные D-триггеры 16 и 17, причем входы С- и D-триггера 16 являются информационным входом и входом разрешения приема схемы выборки соот0 ветственно, а вход С- и выход D-триггера 17 соответственно входом разрешения выдачи и выходом схемы выборки.

Генератор тригонометрических функций 9.i (фиг.4) содержит регистры 18 и 19,

5 сумматор 20, коммутатор 21. регистр 22, регистр 23, блок постоянной памяти 24.

Накопитель 11 (фиг.5) регистр 25, сум- . матор комплексных чисел 26,. коммутатор 27, блок памяти 28 и регистр 29.

0 Сумматор комплексных чисел (фиг.6) содержит два сумматора действительных чисел 26.1 и 26.2.

Решающий блок 15 (фиг.7) содержит регистр 30, коммутатор 31, регистр 32 и ре5 гистр 33, узел сравнения 34. триггер 35, счетчик 36, регистр 37, регистр 38, коммутатор 39, инвертор 40.

Накапливающий сумматор 10 (фиг.З) - сумматор 41 и регистр 42.

0 Блок управления 12 (фиг.9) содержит D- триггер 43, D-триггер 44, счетчик 45, дешифратор 46, инвертор 47, D-триггер 48, D-триггер 49 и сумматор 50 по модулю 2. Блок 13 дискретного преобразования

5 фурье (фиг. 13) содержит Q коммутаторов 51.1. 51.2,...,51.Q, Q цифровых линий задержки 52.1, 52.2.....52.Q, арифметический узел 53, два D-триггера 54,55 и двоичный счетчик 56, узел постоянной памяти 57.

0 Арифметическое устройство, выполняющее вычисления по (3) состоит в общем случае из умножителей и сумматоров и может иметь различную структуру, зависящую как от числа информационных входов, так и

5 от алгоритма реализации Q-точечного ДПФ. В частном случае для Q 4 арифметическое устройство (фиг. 14) содержит 44 - еходовых сумматора 58...61.

Цифровой обнаружитель-измеритель частоты работает следующим обрлзом.

1797127

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель частоты и фазы гармонического сигнала | 1988 |

|

SU1626176A1 |

| Цифровой фильтр | 1987 |

|

SU1390784A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1322172A1 |

| Цифровой анализатор спектра | 1987 |

|

SU1413545A1 |

| Многоканальное устройство ввода информации | 1988 |

|

SU1529238A1 |

| Цифровой фильтр | 1988 |

|

SU1566469A1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1418746A1 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

На вход компаратора 1 (фиг.1) поступает узкополосная смесь сигнала с шумом

U(t) А COS (2 я fc t + Фь) + S(t). (4) где А - амплитуда сигнала;

fc-неизвестная частота сигнала, посто- янкая ка интервале наблюдения длительностью, fc (fH, fH+ 2F);

Фь - начальная фаза сигнала;

S(t) - узкополосный шум.

Такая смесь сигнала с шумом формиру- ется на выходе полосового фильтра с шириной полосы пропускания 2Г, равной диапазону рабочих частот обнаружителя,

Компаратор формирует импульсы нуль- пересечений с частотой следования, равной частоте входного сигнала. Фронта импульсов нуль-пересечения совпадают с моментами пересечения входным сигналом нулевого уровня снизу вверх.

Импульсы нуль-пересечений поступают на информационные входы схем выборки 5.1. 5.2,,..,5.,...,5.0. Количество схем, выборки определяет количество формируемых ими подпоследовательностей нуль-пересечений {tm.i}.

Импульсы тактовой частоты fT, форми- руемые на выходе генератора тактовых импульсов 4 поступают на счетный вход первого счетчика 3 импульсов, На выходе старшего А-roo разряда счетчика формируется импульсный сигнал с периодом Т 2/VfT, определяющим длительность интервала наблюдения. По срезу этого сигнала (фиг.12а), соответствующему началу интервала наблюдения, одновибратор 8 вырабатывает импульс начальной установки И НУ (сиг. 126). Выходной код А первого счетчика 3 импульсов численно равен количеству импульсов тактовой частоты, поступивших на вход счетчика 3 от начала интервала наблюдения.

Импульсы тактовой частоты с выхода генератора тактовых импульсов 4 поступают также на тактовый вход накапливающего сумматора 10, формирующего коды /3 А путем А-краткого суммирования кода /3 начальной частоты поданного на информационный вход накапливающего сумматора. Импульсом ПНУ, поступающим на вход установки в О регистра 42 (фиг.8) являющийся входом начальной установки накапливающего сумматора 10, последний устанавливается з нулевое состояние в начале интервала наблюдения.

Импульсы сигнала с тактового выхода

f (H-ro (H . loga yp) разряда) первогоо счетчика 3 импульсов (фиг. 10а) поступают на счетный вход второго счетчика 7 импульсов. По фронтам этих импульсов, образующим

периодическую временную последовательность {ton} (рис.1 а) происходит изменение выходного кода i счетчика 7 импульсов.

Из кодов I 1,2,...,Q дешифратором 2 формируются сигналы окна (фиг. 106), которые подаются на входы разрешения приема блоков выборки 5.. Длительность каждого сигнала окно г0 2H/fT . 1/2F превышает период 1/fc входного сигнала, что гарантирует попадание хотя бы одного импульса нуль-пересечений в окно. Количество окон, поступающих с каждого из Q выходов дешифратора 2 на вход разрешения приема каждого блока выборки 5,i в течение интервала наблюдения Т, равно N/Q. Период следования окон на каждом выходе дешифратора 2 равен

н

fT

°-Ј(5)

0

5 0 5

5

0

5

0

На вход разрешения выдачи каждого блока выборки поступают импульсы тактовой частоты fT с выхода генератора тактовых импульсов 4 через элемент НЕ 6.

Блок выборки 5 (фиг.З) работает следующим образом. На синхровход D-триггера 16с информационного входа блока выборки поступают импульсы нуль-пересечений (фиг. 11 а). На вход D этого же триггера 16 с входа разрешения приема блока выборки поступают импульсы сигнала окно (фиг.116) причем i-той схеме выборки соответствует сигнал окно i D-триггер 16 устанавливается в состояние логической единицы фронтом первого из импульсов нуль-пересечений, поступившего во время окна на синхровход этого триггера (фиг.11в). По окончании окна происходит переключение D-триггера 16 в состояние логического нуля фронтом первого следующего за срезом окна импульса нуль- пересечений. В D-триггере 17 происходит синхронизация выходного сигнала D-триггера 16 по фронтам сигнала тактовой частоты (фиг.11г), поступающего на синхровход D-триггера 17 с входа разрешения выдачи блока выборки. Такая синхронизация необходима для исключения состязаний в последующих цепях. Таким образом, на выходе каждого блока выборки 5 формируется подпоследовательность импульсов (фиг.11д), совпадающих по фронту (без учета малой задержки в D-триггере 17 на величину, не превышающую периода тактовой частоты) с прореженными импульсами нуль-пересечений. Временные положения фронтов выходных импульсов блоков выборки 5.i на интервале наблюдения образуют Q временных подпоследовательностей {tm.i} (фиг.1 в), где m 1,2.....N/Q - порядкевый номер нуль-пересечения в подпоследовательности от начала интервала наблюдения. Период следования импульсов в каждой подпоследовательности примерно равен периоду Т0 следования окон, т.е. в раз больше, чем в последовательности {tn} прореженных импульсов нуль-пересечений устройства-прототипа. Благодаря этому в Q раз увеличивается время, отводимое генератору тригонометричевских функций для формирования комплексных

экспонент ехр { - J 2 я у-tm.i) по каждому

моменту tm,i и накопителю для формирования промежуточных сумм, что и позволяет расширить диапазон рабочих частот по .сравнению с устройстеом-прототипом.Каж- дая i-тая подпоследовательность {tm,i} поступает на вход разрешения приема 1-го генератора 9 тригонометрических функций. Генератор 9 тригонометрических функций предназначен для формирования комплексных экспонент ехр(- j 2 я у tm.i) из кодов

А текущего времени и / А , поступающих с выходов счетчика 3 импульсов и накапливающего сумматора 10 соответственно на вход кода времени и вход задания частоты генератора 9 тригонометрических функций. В начале интервала наблюдения в течение первого периода сигнала окно 1 фронтами прореженных и синхронизированных в. блоках выборки 5.i импульсов нуль-пересечений в моменты времени tu, производится запись кодов AI.I «ш/Лти/ -Ai, t) м.|, где AI.I - код текущего времени на выходе счетчика 3 импульсов в момент времени ti.j. в регистры 18 и 22 генераторов 9 тригонометрических функций (фиг.4) соответственно. Погрешность представления моментов времени ti.i кодом AI.I не превышает периода At 1/fr тактовой частоты и может быть получена достаточно малой, т.е. меньше чем флуктуации моментов времени ti.i под действием шумов S(t). путем увеличения такто- -вой частоты fT. В начале 2-го периода сигнала окно 1 нулевым уровнем сигнала с третьего тгктоаого выхода блскэ управления 12 (фиг.12ж) коммутаторы 21 генераторов 9 тригонометрических функций устанавливаются на пропускание выходного сигнала регистра 22 ко входу регистра 23. В это время фронтом синхроимпульса со второго тактового выхода блока 12 (фиг. 12г) содержимое регистра 22 записывается в регистр 23. Фронтом сигнала с третьего тактового выхода блока управления 12 содержимое регистра 18 записывается в регистр 19. а уровнем логической единицы это0

5

0

5

0

5

0

го сигнала коммутатор 21 подключает вход регистра 23 к выходу сумматора 20. Содержимое регистра 23, которым после первого синхроимпульса со второго тактового выхода блока управления 12 является код / AI.I поступет на второй вход сумматора 20, где суммируется с кодом AI.I , поступающим на первый вход сумматора с выхода регистра 19. Запись результата сложения осуществляется вторым синхроимпульсом со второго тактового выхода блока управления 12, отсчитываемым от начала периода сигнала окно 1. Результат сложения р AI.I + Ai,i с выхода регистра 23 поступает на второй вход сумматора 20, где образуется сумма 03 AI.I +Ai,i) + AI.I записываемая в регистр 23 третьим синхроимпульсом со второ- готактового выхода блока управления 12. И так далее в течение периода сигнала окно 1. Таким образом, в течение второго периода сигнала окно .1 на выходе регистра 23 образуются последовательно коды ,.i+At,i:/3 -Ао + 2 AU :... ; ,i + (I - 1) AU ;... ;/SAi.i + (L - 1)Ai.i ; где I 1,2....,L - номер синхроимпульса со второго тактового выхода блока управления 12, отсчитываемый от начала периода сигнала окно 1. В это же время в регистрах 18 и 22 фронтами импульсов нуль-пересечений t2.i ФИКСИРУЮТСЯ КОДЫ A2,./At

и / A2.I () t2.i соответственно.

. В течение третьего периода сигнала окно 1 на выходе регистра 23 образуются коды /3 fa : fik. i + А21; / А21 + 2 Аг i;...; ,i+(l-1)A2.i,-... :/3A2,i+(L-1)A2.i; а в регистрах 18 и 22 фиксируются коды Аз t3.i/A t и /ЗАзл OS/A t) t3;i. В течение (лп+1)-го периода сигнала окно 1 на выходе регистра 23 образуются коды

Kl.m.i Ј Am.l + (I - l)Am.i / + (I - 1) X

5

v tm.i i tm.i i 1 r,

At loAt

L:

0

5

o /,Ј + .... ./3+L-1.(6)

Эти коды последовательно подаются с выхода регистра 23 на вход постоянного запоминэю щего устройства (ПЗУ) 24, на выходе которого каждому коду Kt.m.i ставится в соответствие код комплексного числа

Ki.m.i cos Ki.m.i-.

AtI

- j sin 2 я - Ki.m.i exp - j 2 я у tm.i.

Причем каждая из двух квадратурных частей комплексного числа считывается с половины разрядов зыхода ПЗУ 24.

Код Ki.m.i можно представить как сумму двух чисел.

Kl,

m.l n.m.l

At

+ «l.m.l

где ri.m.r

.m.l rl

0,1,2...

O.rn.l Kl.m.l fl.m.l дТ I

Int целая часть числа X. Слагаемое n.m.i д-r можно отбросить,

т.к. на выходе постоянного запоминающего устройства 24.

Sin 2 Я-у- (Г|.т.| -jL + GU.I )

«Sin (2ягГ|.т.1 4- ,т.|)

sin 2 .m.i(8)

-г

. COS 2 ЯГ-у- (П.т.1 + ffl.m.l) COS2 Я-у«|.т,1

(9)

вследствие периодичности функций sin x и cos х с период 2 я. Отсюда следует, что в накапливающем сумматоре 10, счетчике 3 импульсов, а также в сумматоре 20 генератора 9 триго- неметрических функций достаточно иметь Я разрядов для ограничения объема перечисленных узлов величиной Т T/At.

Коды ехр (- 1 л -у- oi.m.i) exp(- j 2

tm.i) с выхода постоянного запоминающего устройства 24, являющегося выходом

. 1-го генератора 9 тригонометрических функций, поступают на информационный вход 1-го накопителя 11, где фиксируются в регистре 25 (фиг.5) синхроимпульсом со второго тактового выхода (фиг. 12г) блока управления 12. Во время второго периода сигнала окно 1, когда на выходе генератора тригонометрических функций формируются, а в

. регистре 25 фиксируются коды ехр (- j 2

05,1.1), 1.2.....L, высоким уровнем сиг

я

нала с четвертого тактового выхода блока управления 12 (фиг.12з) коммутатор 27 накопителя 11, устанавливается на пропускание выходного сигнала регистра 25 ко входу данных оперативного запоминающего устройства (ОЗУ) 28. Эти коды записываются в ОЗУ 28 низким уровнем сигнала со второго тактового выхода блока управления 12. поступающего на вход записи ОЗУ 28 по адресам (1-1) 0,1.,...(L-1) формируемым на адресном выходе блока управления 12 и поступающим на адресный вход ОЗУ 28. Причем в половину разрядов ОЗУ записывается

„At код cos 2 я-ytti.i.i. а в другую половину

1797127

10

10

15

20

25 30

35

40

45

50

55

разрядов - sin 2 я-у «i.i.i. Период повторения кодов адреса равен периоду То повторения сигнала окно 1. В течение третьего периода сигнала окно 1. когда на выходе генератора 9 тригонометрических функций

формируются коды ехр (- j 2 .2.1), низким уровнем сигнала с четвертого тактового выхода блока управления 12 коммутатор 27 подключает- вход данных ОЗУ 28 к выходу сумматора 26 комплексных чисел. Высоким .уровнем первого, считая от начала периода сигна/га окно 1, синхроимпульса со второго тактового выхода блока управления 12 ОЗУ 28 переводится в режим считывания информации по нулевому адресу. Извлеченная по этому адресу в начала третьего периода сигнала окно 1 пара кодов cos 2x

хя-у «ил и sin 0:1,1.1 с выхода ОЗУ28

поступает на вход регистра 29. где фиксируется фронтом синхроимпульса, поданного на синхронизирующий вход регистра 29 с первого тактового выхода блока управления 12 (фиг.12д). С выхода регистра 29 код

ехр (-J 2 я-у «i,i,i) подается на второй вход

сумматора 26 комплексных чисел. На первый вход сумматора в это время подается

код ехр (-j 2 «1,2,i). зафиксированный в

регистре 25 фронтом сигнала со второго тактового выхода блока управения 12 (фиг. 12г).

Сумматор 26 комплексных чисел состоит из двух сумматоров 26,1 и 26.2 (фиг.6). На первые входы сумматоров 26.1 и 26.2,яаля- ющиеся первым входом сумматора 26, поступают соответственно дзйствительная и мнимая составляющие выходного кода регистра 25

ехр( -j 2 я -у- «1.2,i) cos 2 л -у- п.г. -jslfl 2 Я г-СС1.2.

На вторые входы сумматоров 26.1 и 26.2, являющиеся вторым входом сумматора 26. поступают соответственно действительная и мнимая составляющие выходного

кода регистра 29, т.е. cos 2л:-у rzi.i.j и stnx .

х 2я-уС1.1.|.

Результаты суммирования с выходов сумматоров 26.1 и 26.2 являющихся выходом сумматора 26 комплексных чисел.

COS 2 .1,1 + COS 2 Я -. | 2 И

т1

т

sin 2 я-у ai.i.i + sin 2 я-у- a.i.через коммутатор 27 подаются на первый вход ОЗУ и записываются по нулевому адресу низким уровнем сигнала со второго тактового выхода блока управления 12. Переходом от низкого уровня к высокому второго от начала периода сигнала окно 1 синхроимпульса со второго тактового выхода блока управления 12 адрес ОЗУ (сигнал с адресного выхода блока управления 12) увеличивается на 1 и становится равным единице, а в регистре 25 формируется очередной

код ехр (- j 2 п -у- 02,2.0. п° адресу единица из

А +

ОЗУ 28 считывается код ехр (- j 2 я-у 05.1,1),

фиксируемый в регистре 29. По этому же адресу записывается и новый результат суммирования комплексных чисел

ехр (- J 2 я ct2.i.i) + ехр (-J 2 я- 05,2.1).

И так далее в течение всего третьего и .последующих периодов сигнала окно 1. К концу (гп+1}-го период сигнал окно 1 в I- том ОЗУ 28 по нулевому адресу будут записаны комплексные результаты накопления.

ехр (- j2 n ai.i.i) + ехр (- 2. я-у- «1.2.1) + +

.. . +

по первому адресу ехр (- j 2 я-у ai.m.t):

ехр(- 2я- С2.1.0 + ехр( 05.2.1

+ ... + exp(-j2 л-у02.т.О;

по (1-1}-му адресу

exp(-j 2я-у au.i) + exp{-J 2 .2.0 +

+ ...+ expH-T-«i.m.O.

(10)

К началу второго периода сигнала окно 1 на следующем после рассматриваемого интервала наблюдения (Т, 2 Т), в i-том 03Y28 будут содержаться комплексные результаты накопления.

N/Qлт

2 ехр(.т.1

т 1

WQ, . , -2 exp(.,(f)

т I

Во время второго периода сигнала окно 1 на следующем после рассматриваемого интервала наблюдения при высоком уровне синхроимпульсов со второго такто- вого выхода блока управления 12 производится считывание результатов накопления из всех L адресов Иого ОЗУ 28 через регистр 29, выход которого является выходом

(11)

накопителя 11, а при низком уровне синхроимпульсов с второго тактового выхода блока управления 12 - запись в ОЗУ 28 выходных

с данных ехр (- j 1 л - ti.i) регистра 25, подаваемых на вход данных ОЗУ 28 через коммутатор 27 и соответствующих первому нуль-пересечению i-той подпоследовательности следующего интервала наблюдения,

10 т.е. обработка нуль-пересечений по (2) осуществляется в реальном масштабе времени.

Выходные данные YI (-) всех Q накопителей 11 поступают на Q информационных

15 входов блока 13 дискретного преобразования Фурье. Импульсом начальной установки (фиг.126) поступившим в начале интервала наблюдения на установочный вход блока ДПФ произвелась установка

20 низкого уровня сигналов на выходах триггеров 54, 55, а также обнуление двоичного счетчика 56. Низким уровнем сигнала на выходе триггера 54 коммутаторы 51.1,...,51.0установлены на пропускание

25 сигналов с информационных входов блока ДПФ на цифровые линии задержки. (ЦЛЗ) 52.1,...,52.0. Переходом от низкого уровня к высокому сигнала на выходе r-того (г log2X x2L) разряда двоичного счетчика, свидетель30 ствующим об окончании прохождения всех L-отсчетов во время второго окна (фиг.12ж) на интервале наблюдения через коммутаторы 51.1,...,51.0, производится переключение триггера 54.

35 Высоким уровнем сигнала с выхода триггера 54 коммутаторы 51.1,...,51.0 устанавливаются на пропускание сигналов с выходов арифметического устройства. Поочередно появляющиеся после этого на

40

выходах ЦЛЗ данные YJ (-) участвуют в вычислении по программе, хранящейся в ПЗУ 57, арифметическим устройством 53 спект45 ра Y (-), отсчеты которого переписываются

в освобождающиеся по мере вычислений ячейки цифровых линий задержки 52.1,...,52.0.

По окончании вычисления всех Q L

50

комплексных отсчетов спектра на тактовом

выходе ПЗУ фopмv1pyeтcя переход от низкого уровня к высокому сигнала, приводящий к переключению триггера 55. Высокий уровень сигнала с выхода триггера 55 поступа- 55 ет, как и двоичный код с выхода счетчика 56, на адресный оход ПЗУ 57 и переводится это ПЗУ от программы вычисления спектра к программе, по которой арифметическое устройство пропускает без изменений на вы13

ходе сигналы с k-тых (k 2,3,...,Q), входов и их подачу вновь на входы линий задержки, т.е. сумматор 58 (фиг. 14) переводится в режим поочередного пропускания на выход отсчетов спектра со всех входов. Таким образом, через Q L периодов тактового сиг- нала, управляющего продвижением отсчетов через цифровые линии задержки и арифметическое устройство, произойдет поочередная выгрузка отсчетов комплексного спектра Y ()

Id

Действительные ReY (-) и мнимые tmYx

х() части спектра Y (-) последовательно

для всех частот Id/T с выхода устройства 13 ДПФ поступают на вход квадратора 14. Квадратор 14 может быть реализован на постоянном запоминающем устройстве (ПЗУ), на одну половину адресных входов которого

Id

подается действительная ReY (-), а на другую половину - мнимая ImY (-) части Y (-) .

На выходе квадратора образуется последовательность чисел

поступающая на первый информационный вход решающего блока 15.

. Одновременно с выгрузкой чисел Yx

х(у) из устройства 13 для ДПФ на его выходе синхронизации выдачи формируется высокий уровень сигнала, поступающего на установочный вход решающего блока 15. Перед выгрузкой на выходе синхронизации выдачи устройства 13 ДПФ устанавливается низкий уровень сигнала, которым производится обнуление двоичного счетчика 36, регистра 30 и триггера 35 решающего блока (фиг.7). Этим же уровнем коммутатор 31 устанавливается на пропускание кода порога Znop с входа задания порога решающего блока 15 на информационный вход регистра 32, а коммутатор 39 устанавливается на пропускание синхроимпульсов с тактового входа решающего блока на синхронизирующий вход регистра 32. Перед вы. |. грузкой отсчетов Y (-) из устройства 13 для

ДПФ производится запись кода порога Znop в регистр 32 выходными импульсами коммутатора 39. Высоким уровнем сигнала с выхода синхронизации выдачи устройства ДПФ, коммутатор 31 устанавливается на пропускание выходных данных регистра 30 на информационный вход регистра 32, а

1797127

14

коммутатор 39 устанавливается на пропускание сигнала с выхода схемы сравнения 34 на синхронизирующий вход регистра 32.

Входные данные Z (-} решающего блока 15 фиксируются в регистре 30 фронтами синхроимпульсов (фиг.12д) с первого тактового выхода блока управления 12, поступающих на тактовый вход решающего блока

(Y) в регистре 30 превышает код порога, то

выходной сигнал схемы сравнения 34 устанавливается в состояние высокого уровня.

Переходом от низкого уровня к высокому выходного сигнала схемы сравнения 34, прошедшего через коммутатор 39 на синхронизирующий вход регистра 32, производится запись содержимого регистра 30 в

регистр 32, после чего устанавливается низкий уровень выходного сигнала схемы сравнения. Этим же импульсом с выхода схемы сравнения 34 производится запись выходного кода счетчика 36 в регистр 37. Все

7,ск

последующие значения Z (-) сравниваются

уже с превысившим порог значением Z () заместившим код порога в регистре 32.

Выходной код счетчика 36 изменяется под воздействием синхроимпульсов, поступающих с первого тактового выхода блока управления 12 на тактовый вход решающего блока 15, и на каждом шаге сравнения соответствует номеоу Id рабочей частоты Id/T,

т.е. номеру отсчета Z (-) поступающего на

схему сравнения 34.

По окончании выгрузки всех Q L отсче. |d

тов Y (-) в регистре 32 оказывается записанным наибольшее значение, а в регистре соответствующий ему номер . Коды Z(d/T) и Id переписываются в регистры 33 и

38 соответственно срззом сигнала, прошедшего через инвертор 40 с выхода синхронизации выдачи устройства 13 ДПФ, т.е. по окончании выгрузки.

Триггер 35 переводится в состояние логической единицы первым из выходных импульсов схемы сравнения 34, полученных во время выгрузки отсчетов из устройства 13 для ДПФ. Высокий уровень выходного сигнала триггера 35 свидетельствует о наличии

отсчетов, превышающих пороговое значение Znop, т.е. об обнаружении сигнала.

Блок управления работает следующим образом.

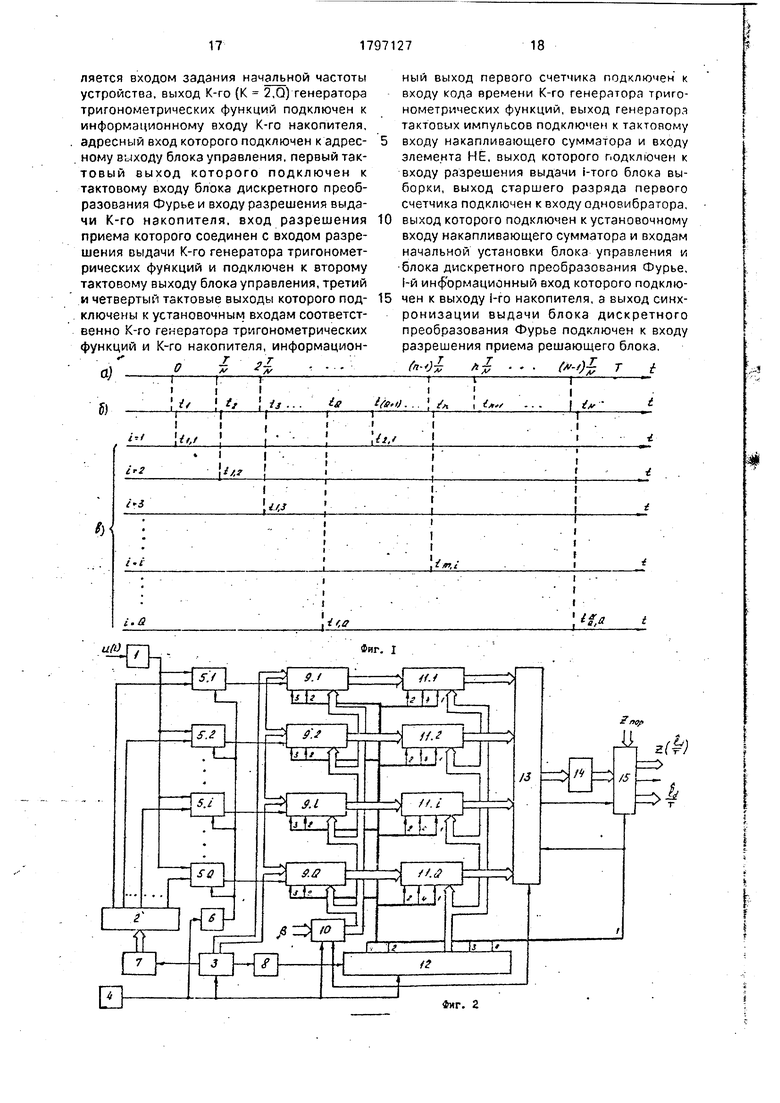

Синхроимпульсы на первом и втором тактовых выходах блока управлейия 12 (фиг.9) формируются в делителе частоты, состоящем из 0-триггеров43, 44(фиг.12д,г)на счетные входы которых поданы импульсы тактовой частоты с тактового входа блока управления (фиг,12в). В начале интервала наблюдения импульсом ИНУ (фиг. 126), поступающим на входы установки триггеров 43, 44 со входа начальной установки блока управления 12, производится начальная установка этих триггеров. По окончании импульса ИНУ на выходах триггеров 43, 44, являющихся первым и вторым тактовыми выходами блока управления соответственно, формируются периодические импульсные последовательности с периодом Тп Ј/fr. В начале интервала наблюдения импульсом ИНУ производится также начальная установка двоичного счетчика 45, после чего происходит периодическое изменение выходного кода (М) счетчика 451-1 0,1....L- -1 (фиг.12е) под воздействием выходных импульсов триггера 44. Периодически изменяющийся код (1-1) с выхода счетчика 45 поступает на адресный выход синхронизатора 12, а также на вход дешифратора 46, который формирует на выходе, являющемся третьим тактовым выходом блока управления 12, импульсный сигнал (фиг.12ж), низкий уровень которого образуется при коде на выходе счетяика 45 и по времени совпадаете началом сигнала окно 1,

В начале интервала наблюдения импульсом ИНУ (фиг. 126), поступающим с входа начальной установки блока управления 12 на входы установки триггеров 48,49, производится установка высокого уровня выходных сигналов этих триггеров. Вторым и третьим от начала интервала наблюдения выходными импульсами дешифратора 46, поступающими на синхронизирующие входы триггеров 48, 49, через инвертор 47, производится поочередный перевод выходных сигналов этих триггеров к низкому уровню, обусловленному заданием низкого уровня на входе триггера 48. Выходные сигналы триггеров 48 и 49 поступают на входы сумматора 50 по модулю 2, на выходе которого, являющемся четвертым тактовым выходом блока управления 12, формируется сигнал (фиг,12з), высокий уровень которого сохраняется только в течение второго периода сигнала окно 1, отсчитываемого от начала интервала измерения.

Формула из об р е т е н и я Цифровой обнаружитель-измеритель частоты, содержащий компаратор, генератор тригонометрических функций, нэкопитель, квадратор, решающий блок, блок управления, первый и второй счетчики, генератор тактовых импульсов, выход которого подключен к счетному входу первого счетчика и тактовому входу блока управле0 ния, первый тактовый выход которого подключен к тактовому входу решающего блока и входу разрешения выдачи накопителя, второй тактовый выход блока управления подключен к входу разрешения приема на5 копителя и входу разрешения выдачи генератора тригонометрических функций, выход которого подключен к информационному входу накопителя, адресный вход которого подключен к адресному выходу блока управ0 ления, третий и четвертый тактовые выходы которого подключены к установочным входам соответственно генератора тригонометрических функций и накопителя, выход квадратора подключен к информационному

5 входу решающего блока, первый и второй информационные выходы которого являются выходами устройства для значений соответственно максимального отсчета спектра и кода его частоты, информационным вхо0 дом и входом задания значения порога обнаружителя-измерителя являются соответственно вход компаратора и вход задания значения порога решающего блока, выход признака обнаружения которого яв5 ляется выходом признака обнаружения устройства, информационный выход первого счетчика подключен к входукода времени генератора тригонометрических функций, а один разряд информационного выхода пер0 вого счетчика подключен к счетному входу второго счетчика, отличающийся тем, что. с целью расширения диапазона рабочих частот, в него введены Q блоков выборки, Q-t генераторов тригонометрических

5 функций, Q-1 накопителей, дешифратор, элемент НЕ, одновибратор, накапливающий сумматор и блок дискретного преобразования Фурье, информационный выход которого подключен к входу квадратора, ин0 формационный выход второго счетчика подключен к входу дешифратора, i-й (i 1.Q) выход которого подключен к входу разрешения приема i-ro блока выборки, информационный вход которого подключен к выходу

5 компаратора, выход 1-го блока выборки подключен к входу разрешения приема i-ro генератора тригонометрических функций, вход задания начальной частоты которого подключен к выходу накапливающего сумматора, информационный вход которого является входом задания начальной частоты устройства, выход К-го (К 2,0) генератора тригонометрических функций подключен к информационному входу К-ro накопителя, адресный вход которого подключен к адресному выходу блока управления, первый тактовый выход которого подключен к тактовому входу блока дискретного преобразования Фурье и входу разрешения выдачи К-ro накопителя, вход разрешения приема которого соединен с входом разрешения выдачи К-ro генератора тригонометрических функций и подключен к второму тактовому выходу блока управления, третий и четвертый тактовые выходы которого подключены к установочным входам соответственно К-го генератора тригонометрических функций и К-ro накопителя, информациона)

ный выход первого счетчика подключен к входу кода времени К-го генератора тригонометрических функций, выход генератора тактовых импульсов подключен к тактовому

входу накапливающего сумматора и входу элемента НЕ, выход которого подключен к входу разрешения выдачи i-того блока выборки, выход старшего разряда первого счетчика подключен к входу одновибратора,

выход которого подключен к установочному

входу накапливающего сумматора и входам

начальной установки блока управления и

блока дискретного преобразования Фурье,

1-й информационный вход которого подключен к выходу 1-го накопителя, а выход синхронизации выдачи блока дискретного преобразования Фурье подключен к входу разрешения приема решающего блока.

9 МИФ ±

Ъ МИф

с;

С

Тэг

L

гэг

7s

II

U.IL6U

Фиг. 7

Фиг. е

а) ЛJЧJЛJlJгЛ..--...ЛJЧJlJПJПJаЛJl

а)

to

А

г) ллллйаагитги

.я Т :

- .

// пп/шлллдягшлппгишштпппялги

$ИР. 12

Фиг. Ю

i i

Фиг. II

-si. i:

S3

Jf

if.

Не

:| Д,

- .0 sti

Ts

/

./

31

и

Авторы

Даты

1993-02-23—Публикация

1989-04-27—Подача