вого коммутатора и через элемент И с входами дешифратора и сумматора по модулю два, пятый вход формирователя соединен с входами первых блока памяти; и коммутатора, четвертый вход формирователя через соединенные последовательно первые коммутатор и блок памяти соединен с выходом формирователя и входом второго блока памяти, выход регистра через соединенные последовательно схему сравнения и дешифратор соединен с входами элемента ИЛИ и первого триггера, выход которого через сумматор по модулю два соединен с входами первого счетчика и элемента НЕ, выход которого соединен с соответствующим выходом формирователя, входами вторых блока памяти и коммутатора и через соединенные последовательно вторые счетчик, коммутатор и блок памяти - с соответствующим вьжодом формирователя, выход элемента ИЛИ соединен с входами второго триггера и третьего счетчика, выходы которого соединены с входом схемы сравнения и через второй триггер - с 1зходом элемента И, соответствующий выход дешифратора соединен с входом третьего счетчика, а выход первого счетчика - с входом второго коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Генератор псевдослучайных чисел | 1984 |

|

SU1239844A1 |

| Генератор псевдослучайных чисел | 1986 |

|

SU1324091A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Генератор псевдослучайной последовательности импульсов | 1985 |

|

SU1277362A1 |

| Генератор псевдослучайных кодов | 1980 |

|

SU920718A1 |

| Генератор псевдослучайной последовательности импульсов | 1979 |

|

SU866716A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| УСТРОЙСТВО ПОИСКА ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1990 |

|

RU2020766C1 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ, содержащее блок ввода, первый выход которого через схему сравнения соединен с первым входом блока синхронизации, генератор импульсов, первый выход которого соединен с входом генератора псевдослучайных чисел, сумматор, выход которого через регистр сдвига соединен со своим входом, с входами схемы сравнения и блока индикации, отличающееся тем, что, с целью повышения полноты контроля и быстродействия, в него введены блок сравнения, три коммутатора, регистр, блок памяти, триггер, два дешифратора, группа триггеров, два счетчика, формирователь неравновесных кодов, элемент И, причем выходы блока ввода соединены с входами первого коммутатора, блока памяти, блока сравнения, первым входом формирователя неравновесных кодов и через первый дешифратор - с вторым входом формирователя неравновесных кодов и входом первого коммутатора, выход которого через блок памяти соединен с входом второго коммутатора, выход которого через соединенные последовательно регистр, второй дешифратор, группы триггеров и третий коммутатор соединен с выходами устройства, вход которого соединен с входами сумматора и счетчиков, выходы которых соединены с входами блока индикации, выходы генератора псевдослучайных чисел соединены с третьим входом формирователя неравновесных кодов, входом первого коммутатора и через блок сравнения - с чет вертым входом формирователя неравно(/) весных кодов, BxoAa iH блока памяти, первого коммутатора, элемента И и блока синхронизации, выходы которого соединены с входами первого и второго а коммутаторов и пятым входом формиро- , даателя неравновесных кодов, выходы которого соединены с входами второго о коммутатора, а второй выход генератора импульсов через соединенные пос- ,ледовательно триггер и злемент И соепинен с входом триггера и регистра. 2. Устройство по п. 1, отличающееся тем, что формирователь неравновесных кодов содержит два коммутатора, два блока памяти, три счетчика, регистр, дешифратор, схему сравнения, сумматор по модулю два, два триггера, элемент ИЛИ, элемент И, элемент НЕ, причем первый вход формирователя соединен с входом первого блока памяти, второй вход с входами первого коммутатора и регистра, третий вход - с входом пер

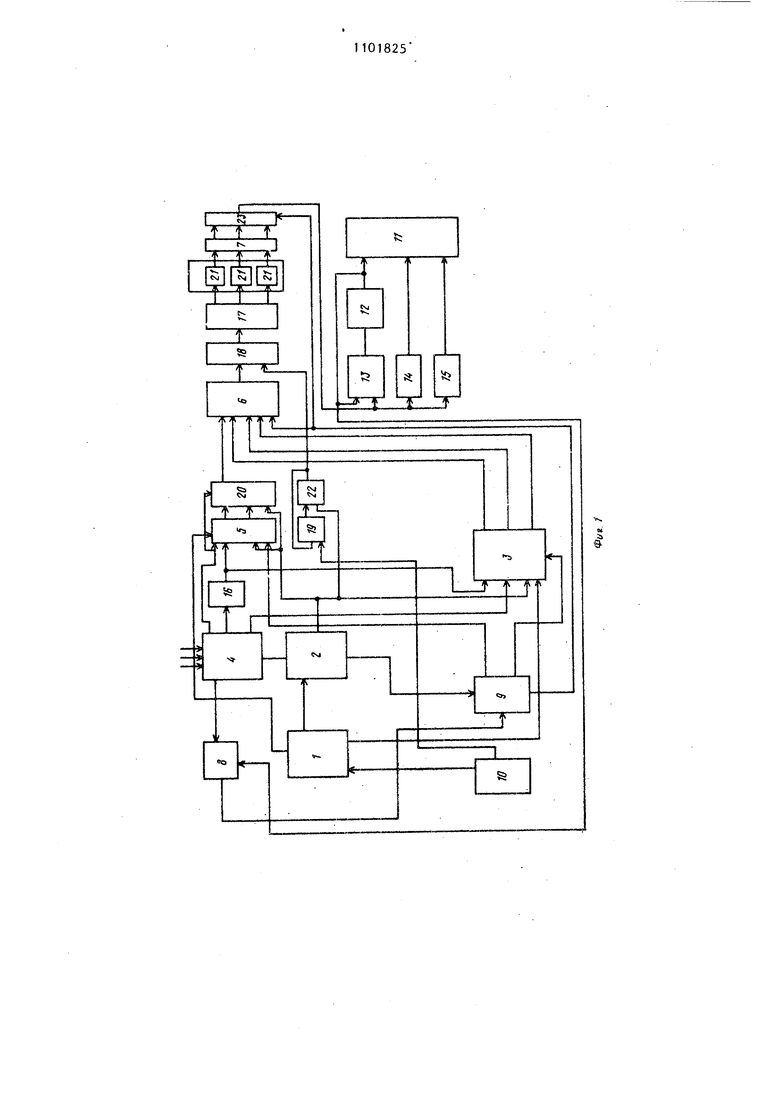

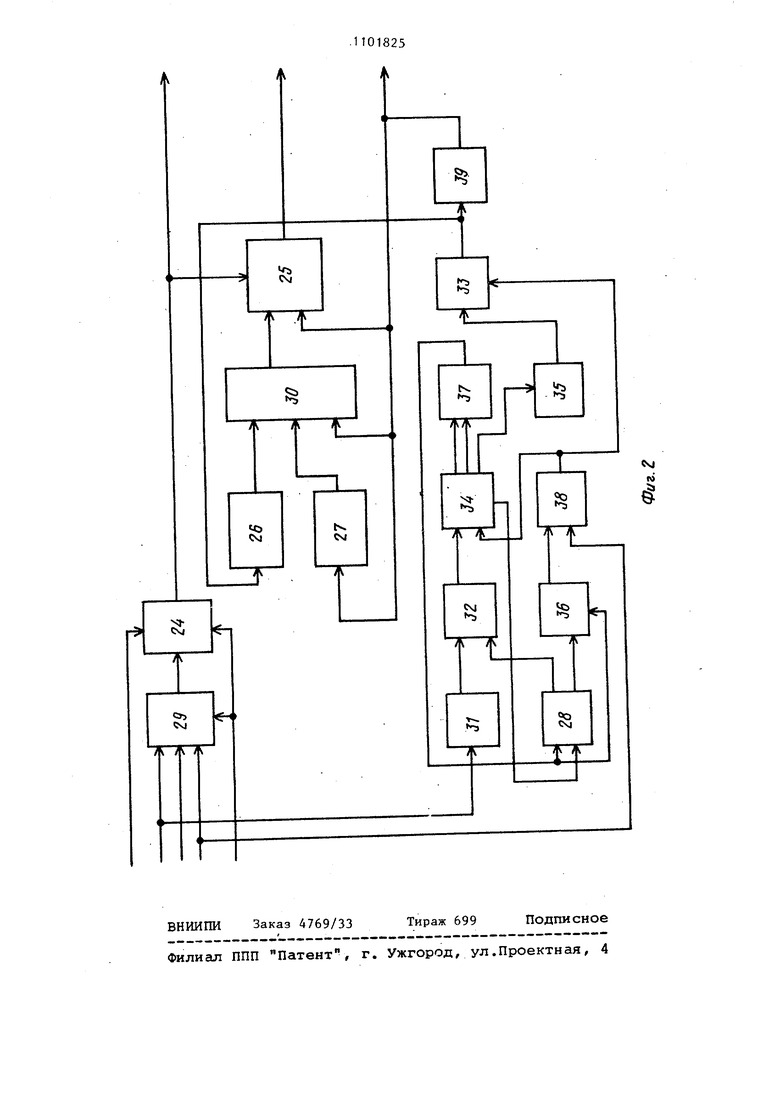

Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано для контроля логических блоков и диагностики неисправностей в процес производства и для периодических проверок в процессе эксплуатации. Известно устройство для автомати зированной проверки цифровых прибор содержашее блок хранения эталонов, таймер, блок формирования команд, блок источников эталонных сигналов, два коммутатора, блок регистрации, регистр, блок синхронизации, блок сравнения, счетчик и блок управлеНИН l Недостатком этого устройства явпяется большой объем оборудования, необходимость в источниках эталонны Сигналов, низкое быстродействие. Наиболее близким по технической сущности к изобретению является уст ройство для контроля интегральных схем, содержащее блок ввода, первый выход которого через схему сравнени соединен с первым входом блока синх ронизации, генератор импульсов, пер вый выход которого соединен с входо генератора псевдослучайных чисел, сумматор, выход которого через регистр сдвига соединен со своим входом, с входами схемы сравнения и блока индикации 2J . Однако известное устройство имеет ограниченную область применения только для контроля простых комбинационных схем и характеризуется значительным увеличением времени контроля с ростом сложности схем. Цель изобретения - повышение полноты контроля и быстродействия. Поставленная цель достигается тем, что в устройство, содержащее блок ввода, первый выход которого через схему сравнения соединен с первым входом блока синхронизации, генератор импульсов, первьм выход которого соединен с входом генератора псевдослучайных чисел, сумматор, выход которого через регистр сдвига соединен со своим входом, с входами схемы сравнения и блока индикации, введены блок сравнения, три коммутатора, регистр, блок памяти, триггер, два дешифратора, группа триггеров, два счетчика, формирователь неравновесных кодов, элемент И, причем выходы блока ввода соединены с входами первого коммутатора, блока памяти, блока сравнения, первым входом формирователя неравновесных кодов к через первый дешифратор с вторым входом формирователя неравновесных кодов и входом первого коммутатора, выход которого через блок памяти соединен с входом второго коммутатора, выход которого через соединенные последова тельно регистр, второй дешифратор, группу триггеров и третий коммутатор соединен с выходами устройства, вход которого соединен с входами сумматора и счетчиков, выходы которых соеди нены с входами блока индикации, выхо ды генератора псевдослучайных чисел соединены с третьим входом формирователя неравновесньос кодов, первого коммутатора и через блок сравнения с четвертым входом формирователя неравновесных кодов, входами блока памяти, первого коммутатора, элемен та И и через блок синхронизации с входами первого и второго коммутаторов и пятым входом формирователя неравновесных кодов, выходы которого соединены с входами-второго коммутатора, второй выход генератора импуль сов через соединенные последовательно триггер и элемент И соединен с вх дом триггера и регистра. При этом формирователь неравновес ных кодов содержит два коммутатора, два блока памяти, три счетчика, регистр, дешифратор, схему сравнения, сумматор по модулю два, два триггера, элемент ИЛИ, элемент И, элемент НЕ, причем первый вход формирователя соединен с входом первого бло ка памяти, второй вход - с входами первого коммутатора и регистра, третий вход - с входом первого коммутатора и через элемент И с входами дешифратора и сумматора по модулю два, пятый вход - с входами первых блока памяти и коммутатора, четвертый вход через соединенные последовательно первые коммутатор и блок памяти с выходом формирователя и входом второго блока памяти, выход регистра через соединенные последовательно схему сравнения и дешифратор соединен с входами элемента ИЛИ и первого триггера, выход которого через сумматор по модулю два соединен с входа ми первого счетчика и элемента НЕ, выход которого соединен с соответствующим выходом формирователя, входами вторых блока памяти, коммутатора и через соединенные последовательно вторые счетчик, коммутатор и блок памяти с соответствующим выходом фор мирователя, вых-од элемента ИЛИ соеди нен с входами второго триггера и третьего счетчика, выходы которого соединены с входами схемы сравнения и через второй триггер с входом элемен 1 254 та И, соответствую1ций выход дешифратора соединен с входом третьего счетчика, а в-.код первого счетчика с входом второго коммутатора. На фиг. 1 представлена функциональ нал схема предлагаемого устройства (группы связей, имеющих одинаковое функциональное назначение, изображены одной линией), на фиг. 2 - функциональная схема формирователя неравновесных кодов. Устройство содержит генератор 1 псевдослучайных чисел, блок 2 сравнения, формирователь 3 неравновесных кодов, блок 4 ввода, коммутаторы 5-7, схему 8 сравнения, блок 9 синхронизации, генератор 10 импуль.сов, блок 11 индикации, регистр 12 сдвига, сумматор 13, счетчики 14 и 15, дешифраторы 16 и 17, регистр 18, триггер 19, блок 20 памяти, триггеры 21 группы, элемент И 22, объект 23 контроля. Формирователь 3 неравновесных кодов содержит два блока 24 и 25 памяти, счетчики 26-28, коммутаторы 29 и 30, регистр 31, схему 32 сравнения, сумматор 33 по модулю два, дешифратор 34, триггеры 35 и 36, элементы ИЛИ 37, И 38, НЕ 39. Устройство работает следующим образом. В блок 4 ввода заносят эталонные свертки для выходных контактов и управляющие слова, определяющие, какие стимулирующие воздействия должны быть поданы на каяздый контакт контролируемого блока. Разряды управляющего слова содержат полную характеристику контакта: его вид (вход или выход) , основное состояние контакта (О или 1), а также являются ли коды, возникающие на контактах, неравновесными (с вероятностью появления О или 1, равной Р 1/4, 1/8, 1/32, 1/64 и т.д.) и частоту переключения для контактов с вероятностью Р 1/2, причем под основньм состоянием контакта подразумевается то, в котором контролируемый контакт должен находиться с большей вероят- ностью Так, например, для контакта с вероятностью появления единицы Р 1/16 основным состоянием будет О,- а маловероятным 1, а для контакта с вероятностью появления единицы Р 15/16 основным состоянием будет 1, а маловероятным - О. Устройство реализует два режима работы : режим подготовки и режим контроля. В режиме подготовки происходит заполнение блоков 20 и 24 памяти формирователя 3. Управляющие слова из блока 4 поступают на дешифратор 16, который формирует сигнал разрешения записи. Запись в блоки 20 и 24 памяти продолжаете яг до их полного заполнения, причем номера равновероятных контактов заносятся в три различные зоны блока 20 памяти в зависимости от реализуемой на них частоты, а номера контактов с неравновесными кодами - в блок 24 памяти таким образом, что, например, номес вероятностью Р 1/4 pa контактов в 8 раз чаще, чем номезаписываютсяс вероятностью Р 1/32 pa контактов Одновременно с этим происходит установка триггеров 21 группы в основное состояние, сброс триггеров 35 и 36 и запись в регистр 31 кода, соответствующего среднему количеству выходов, находящихся в маловероятном состоянии. На счетчиках 26 и 27 устанавливается адрес начальной ячейки второго блока 25 памяти. В режиме контроля генератор t фор мирует с равной вероятностью все возможные двоичные числа, которые поступают в блок 2 сравнения и через коммутатор 5 на адресные входы блока 20 памяти и в формирователь 3. По выбранному адресу считывается код номера выходного канала, который через коьтутатор 6 и регистр 18 поступает на дешифратор 17. Сигнал с выхода дешифратора поступает на счетны вход соответствующего триггера 21 группы, и он переключается в противо положное состояние. Йа входе контролируемого блока возн кает новьй набор стимулирующих сигнало Исправность блока определяет схема 8, которая сравнивает эталонные свертки и свертки, полученные с помо щью сумматора 13 и регистра 12 сдвига из цифровой последовательности, существующей на каждом контролируемом контакте блока, работающего в те чеЕше заданного периода в режиме, за данном управляющими словами. Выбор блока 20 памяти или формирователя 3 осуществляется блоком 2 в зависимост от чисел, которые поступают из блока 4 и от генератора 1. Если число К, записанное.в блоке 4, меньше числа m ,сформированно го генератором 1, выбирается блок 20 памяти и происходит формирование тактовых сигналов, если К, гп , то блоком 20 памяти формируются равновероятные сигналы, когда tn происходит выбор формирователя 3. Тактовые сигналы обеспечивают переход контакта в первом такте из основного состояния в маловероятное и возврат в исходное состояние в последующем такте. Происходит это следуюищм образом. На вход элемента И 22 поступает сигнал от блока 2 сравнения, который формирует на его выходе импульс, переключающий триггер 19 в противоположное состояние и запрещающий запись в следующем такте в регистр 18 нового номера выходного контакта. До сброса триггера 19 сигнал на выходе элемента И 22 не меняется. Сброс триггера происходит от сигнала генератора 10 в конце следующего такта. При выборе формирователя 3 реализуются два режима работы: переключение контакта в основное состояние и переключение его в faлoDepoятнoe состояние. В первом режиме генератор 1 формирует на третьем входе формирователя псевдослучайные числа, которые поступают на адресные входы блока 24 памяти. Считанный из блока памяти код выходного канала поступает на выход формирователя 3 и на информационные входы блолка 25 памяти. Выходной канал, соответствующий выбранному коду, переключается в маловероятное состояние. К адресным входам блока 25 памяти коммутатор 30 подключает выходы счетчика 26. Код выходного контакта, перешедшего в маловероятное состояние, записывается в-блок 25 памяти по адресу, указанному счетчиком 26, после чего сумматор 33 добавляет единицу в счетчик 26. Таким образом, в блок 25 памяти последовательно, по порядку их перехода, записываются номера выходных каналов, перешедших в маловероятное состояние. Переключение контакта в основное состояние производится следующим образом. Коммутатор 30 подключает к адресам блока 25 памяти выходы счетчика 27. Код, считанный из блока 25 памяти, поступает через комму7 . 1 татор 6, регистр 18 на дешифратор 17 и соответствующий коду триггер 21 группы переходит в основное состояние после чего на вход счетчика 27 поступает единица, и блок 25 памяти готов к считыванию следующего кода. Считывание из блока 25 памяти происходит в том же порядке, что и запись в него Выбор режима переключения в основное или маловероятное состояние производится сигналами, формирующимися на выходе сумматора 33 по модулю два и элемента НЕ 39, следующим образом. В первоначальный момент в режиме контроля происходит переключение неравновесного контакта в малофероятное состояние, так как триггер 36 сброшен в О, на элемент И 38 поступает сигнал Запрет, который обеспечивает О на eio выходе и фор мирует сигнал +1 на входе счетчика 26, на вход дешифратора 34 поступает О со схемы 32, так как в счет чике 28 записан О, а в регистре 31 - число N, заданное блоком А На выходе дешифратора 34 формируется сигнал +1 в счетчик 28. Он пере водит триггер 36 в единичное состояние, разрешая прохождение через элемент И 38 сигнала, поступающего с ге нератора 1. В дальнейшем выбор режима работы определяется псевдослучайными числами, формируемыми генератором 1, причем с вероятностью 3/4 выбирается режим перехода в маловероятное состояние, так как на вход элемента И 3 поступают от генератора 1 по крайней мере два сигнала с вероятностью Р 1/2, таким o6p,TJOM единица на выходе элемента И 38 возникает с вероятностью 1 /4 . Когда значение счетч тка 28 достигает числа, записанного в регистре 31 , с вероятностью Р 3/4 возникает сигнал на выходе дешифратора 34 который переключает триггер 35 в противоположное состояние. Сумматор инвертирует сигналы, поступающие с элемента И 38, и с вероятностью 3/4 выбирается режим перехода в.основное состояние. Сигналы на вход счетчи-ка 28 поступают с дешифратора, и зна чение счетчика 28 колеблется от О до 2N. Если в счетчике 28 возникает переноса, т.е. число, записанное 25 в нем, отрицательно, триггер 36 переключается, подавая сигнал запрета для элемента И 38, и независимо от сигналов генератора 1 выбирается режим перехода в основное состояние. Таким образом, выбор режима работы формирователя 3 зависит от общего количества г) выходных каналов, находящихся в маловероятном состоянии. При П О происходит переключение соответствующего канала в маловероятное состояние. При О п - NQ, где NO - число, записанное в регистре 66, режим переключения в маловероятное состояние выбирается случайным образом с вероятностью Р 3/4, а при с вероятностью 1/4. Среднее время нахождения любого выходного канала в маловероятном состоянии определяется величиной Mj, , которая служит для настройки формирователя 3, а среднее время между переходами из основного состояния в маловероятное обратно пропорционально количеству ячеек памяти, в которых записан код этого канала. Поскольку вероятность нахождения выходного канала в маловероятном состоянии определяется отношением двух указанных времен, то надлежащим выбором WQ (общим для всех каналов) и количеством ячеек в блоке 25 памяти (индивидуальным для каждого канала) может быть реализована любая вероятность в широких пределах с малой дискретностью. Устройство предусматривает также переключение триггеров 21 группы закономерным образом в зависимости от теста, введенного в блок 4, что позволяет сформировать на некоторых контактах фиксированные цифровые последовательности ограниченной длины. Счетчики 14 и 15 служат для определения количества единиц и переключений на любом контакте контролируемой схемы в процессе диагностики неисправностей, а также для оценки полноты контроля на этапе подготовки. Таким образом, предлагаемое изобретение позволяет значительно расширить функциональные возможности устройства контроля за счет расширения класса контролируемых схем вплоть до схем с двунаправленными выводами, уменьшает время подготовки контроля и сокращает объем оборудования.

в

Cs м)

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Плавучий цепной ветро-водяной двигатель | 1923 |

|

SU913A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля интегральных схем | 1978 |

|

SU744579A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-07—Публикация

1983-01-13—Подача