последовательностей, цифровой формирователь задержки, блок цифровых формирователей задержки и аналоговый сумматор, выход которого является информационным выходом устройства, вход соединен с аналоговым выходом генератора пqeвдocлyчaйныx последовательностей, а группа входов соединена с группой выходов блока аналоговых ключей, цифровой выход генератора псевдослучайных последовательностей соединен с входом цифрового формирователя задержки, выход которого соединен с третьим входом блока управления умножением, а адресный выход соединен с вторым входом второго блока памяти, группа )ровых выходов блока генераторов псевдослучайных последовательностей соединена с группой входов блока цифровых формирователей задержки, группа выходов которого соединена с группой входов блока управления умножением, а группа адресных выходов соединена с группой входов второго блока памяти, группа выходов блока управления генераторами псевдослучайных последовательностей соединена с группой управляющих входов блока генератора псевдослучайных последовательностей, группа аналоговых выходов которого соединена с группой входов блока аналоговых ключей, четвертый выход блока управления соединен с первой группой управляющих входов блока цифровых формирователей задержки, с

с первой и второй группами входов блока управления генераторами псевдслучайных последовательностей, с управляющим входом генератора псевдслучайных последовательностей и с первым управляющим входом цифрового формирователя задержки, пятый выход блока уп|эавления соединен с второй группой управляющих входов блока цифровых формирователей задержки, шестой выход блока управления соединен с группой управляющи в)содов блока аналоговых ключей, второй управляющий вход цифрового формирователя задержки подключен ;К третьему выходу блока управления.

2. Устройство по п. 1, отличающееся тем, что цифровой формирователь задержки содержит бло регистров сдвига, цифровой коммутатор и счетчик адреса, первый выход которого является адресным выходом формирователя, второй выход счетчик адреса соединен с управляющим входо цифрового коммутатора, информационный вход которого соединен с выходом блока регистров сдвига, а выход является выходом формирователя, информационный и управляющий входы блока регистров сдвига являются соответственно входом и первым управляющим входом формирователя, вторым управляющим входом формирователя является вход счетчика адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения среднеквадратического значения переменного сигнала | 1989 |

|

SU1781686A1 |

| Многоканальный аналого-цифровой процессор | 1983 |

|

SU1120375A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Устройство для измерения параметров магнитных лент | 1986 |

|

SU1434376A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Устройство для определения коэффициентов линейной регрессии | 1981 |

|

SU993291A1 |

| Устройство для воспроизведения с носителя магнитной записи | 1985 |

|

SU1278934A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU960837A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

1

Изобретение относится к области контрольно-измерительной техники и может быть использовано для измерения импульсных переходных характеристик (ядер нелинейных объектов, описываемых при помощи функциональных рядов Вольтерра.

f

Известныустройства ГО - Сэ Известное устройство для определения ядер Вольтера содержит последовательно соединенные генератор псевдослучайной троичной последовательности, объект измерения, множительное устройство и аналоговый интегра тор, а также две линии задержки, входы которых подключены к выходу гене2

ратора, а выходы - к входам множител ного устройства СО

К недостаткам известного устройства является длительное время измерения и низкая точность измерения диагональных значений ядер Вольтера.

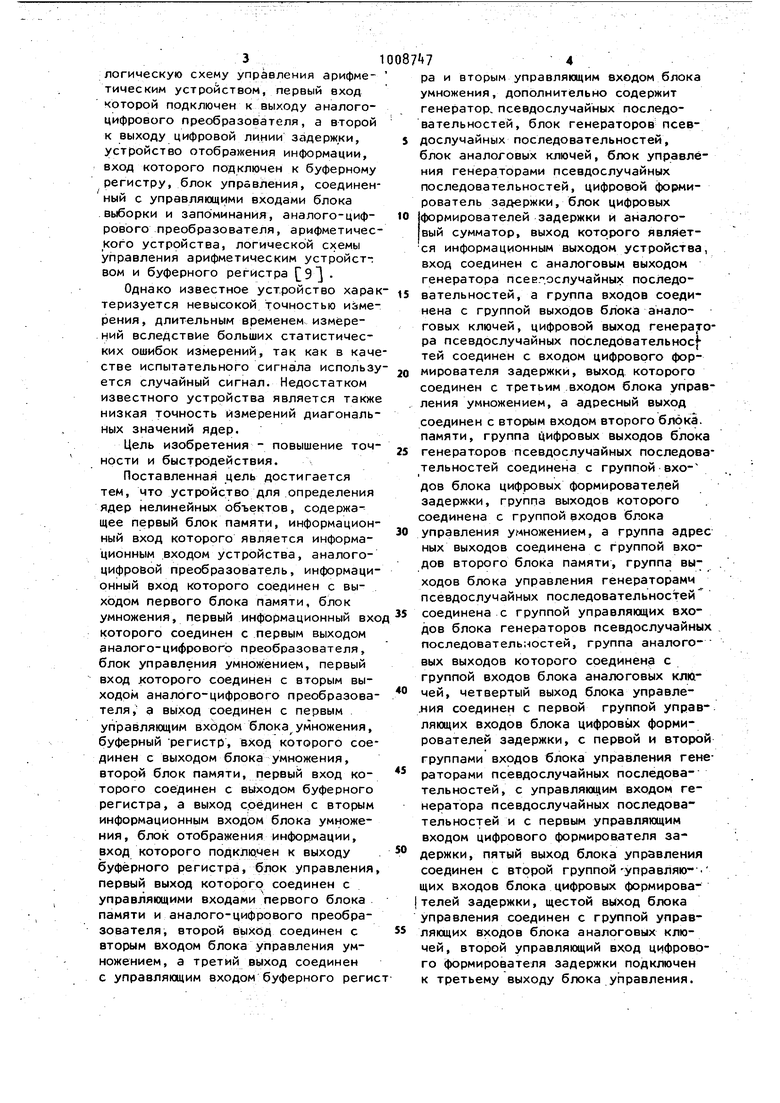

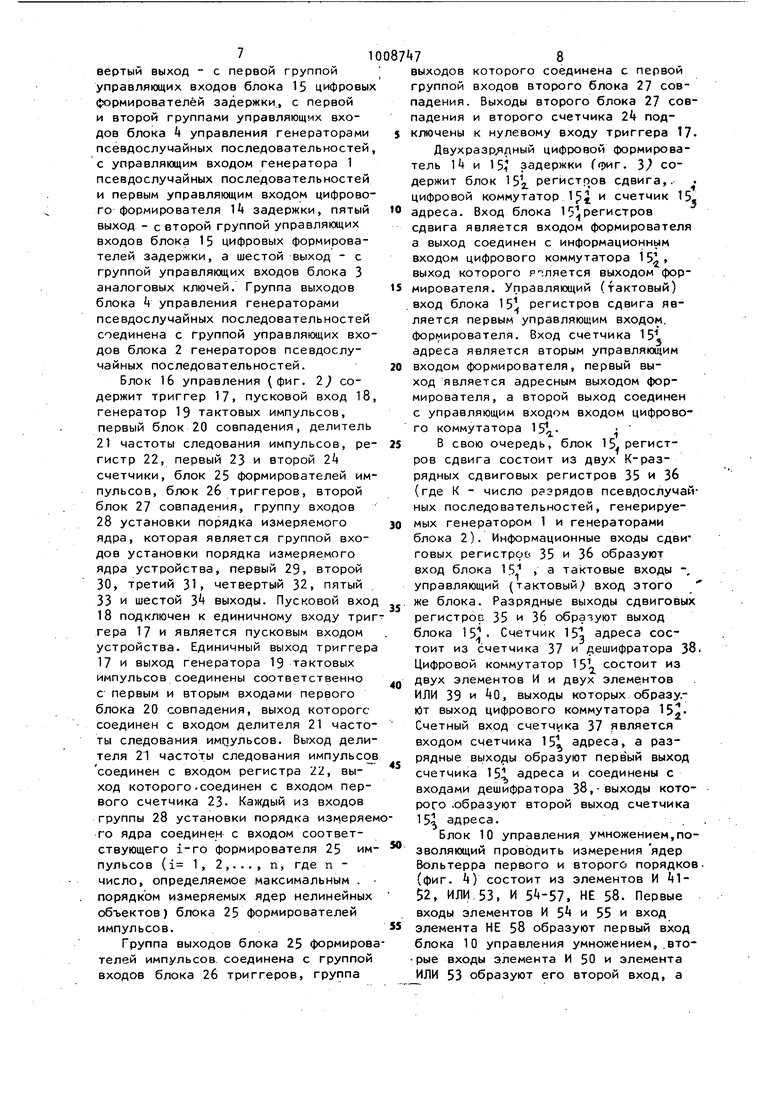

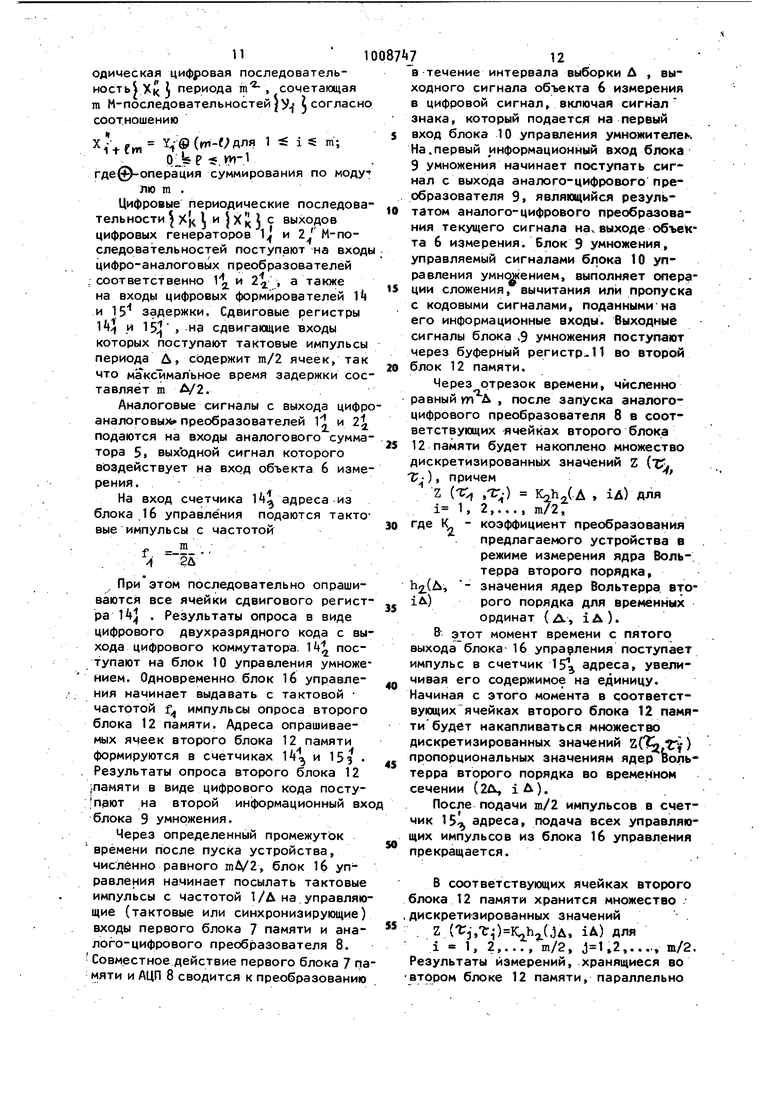

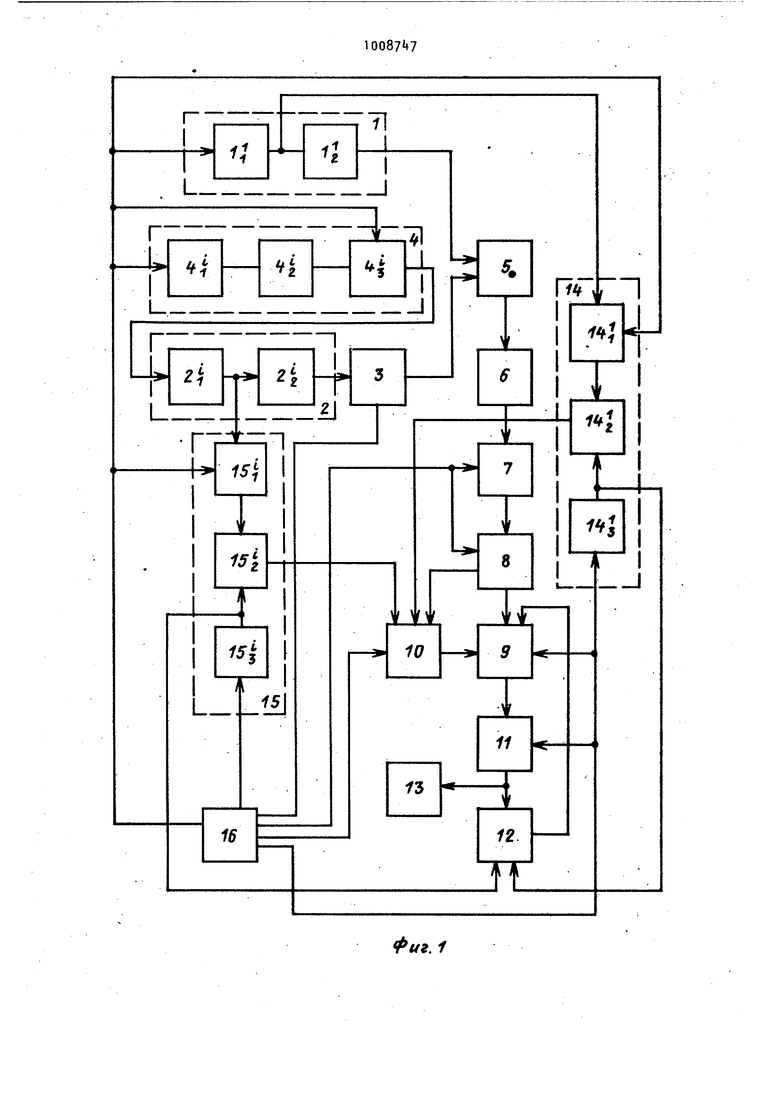

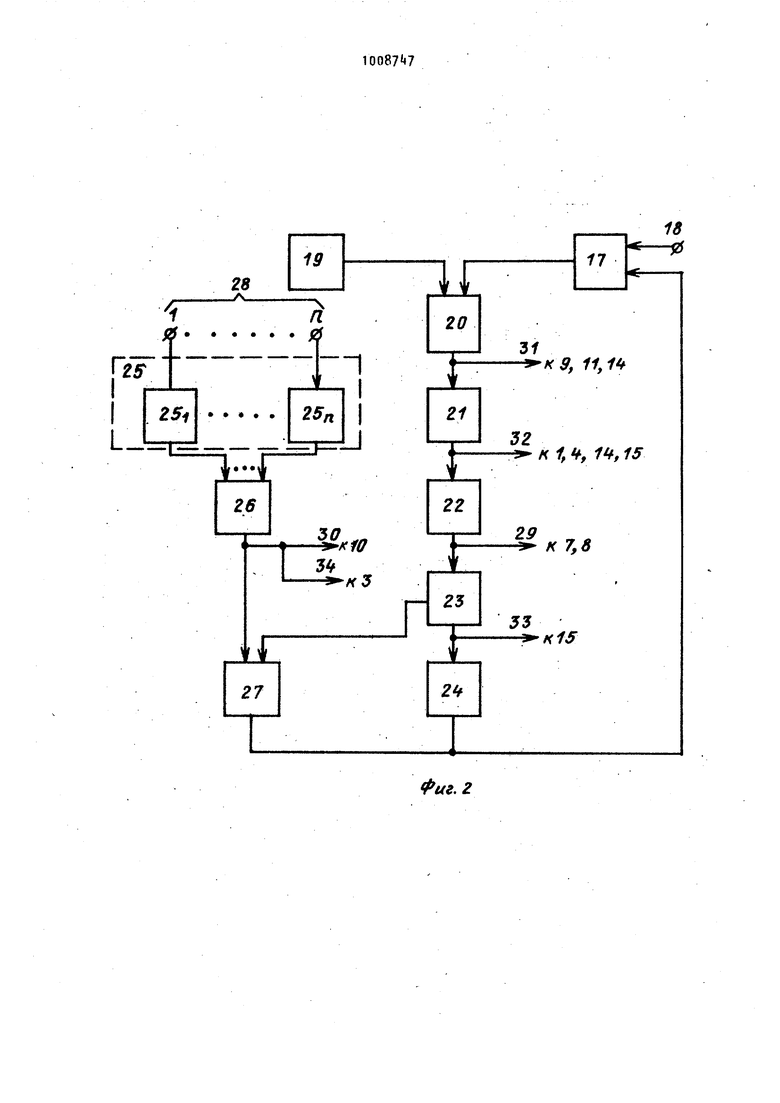

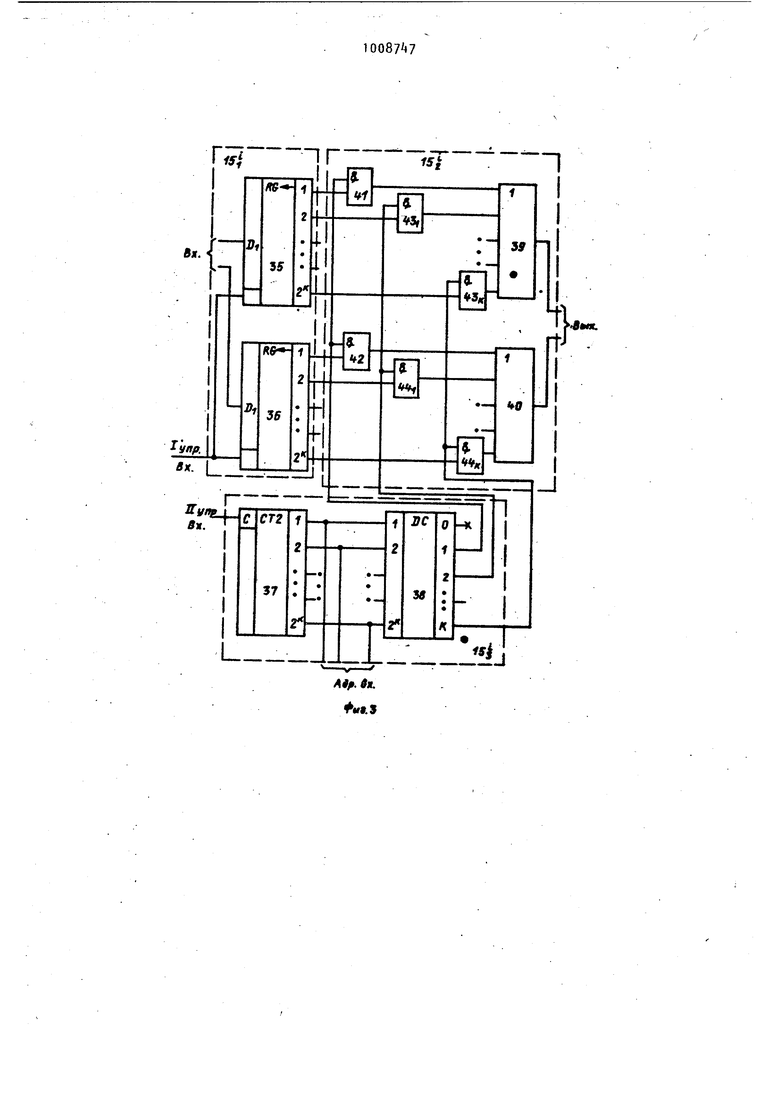

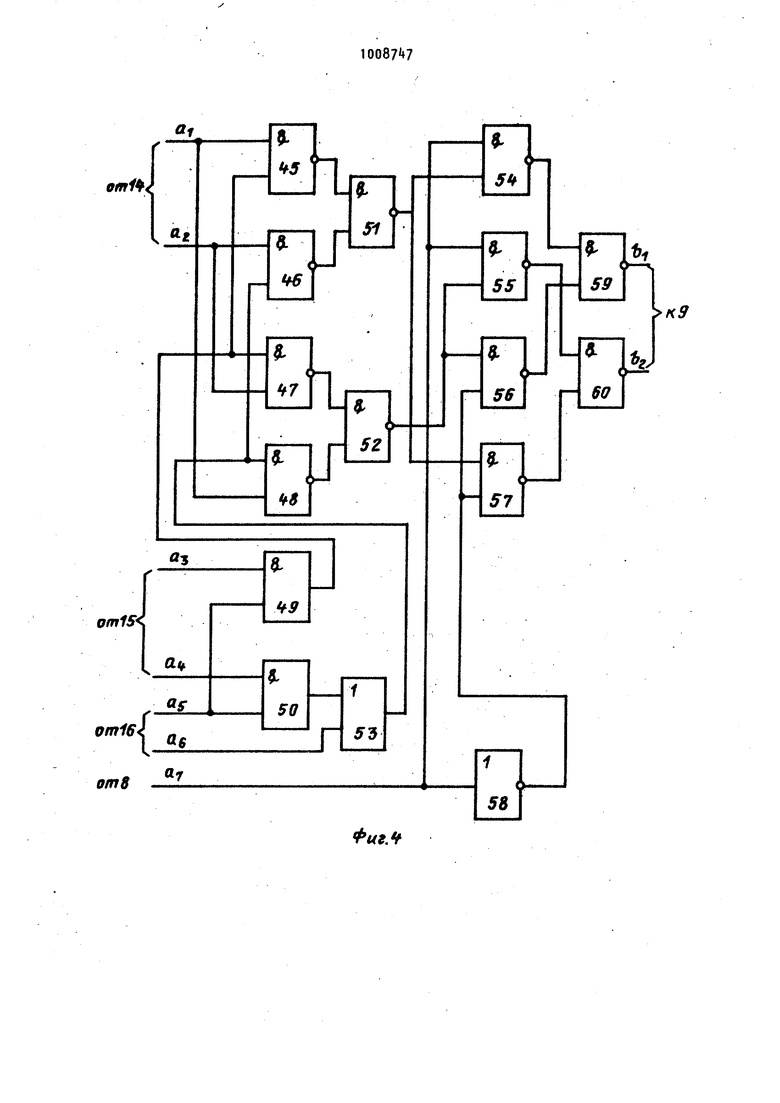

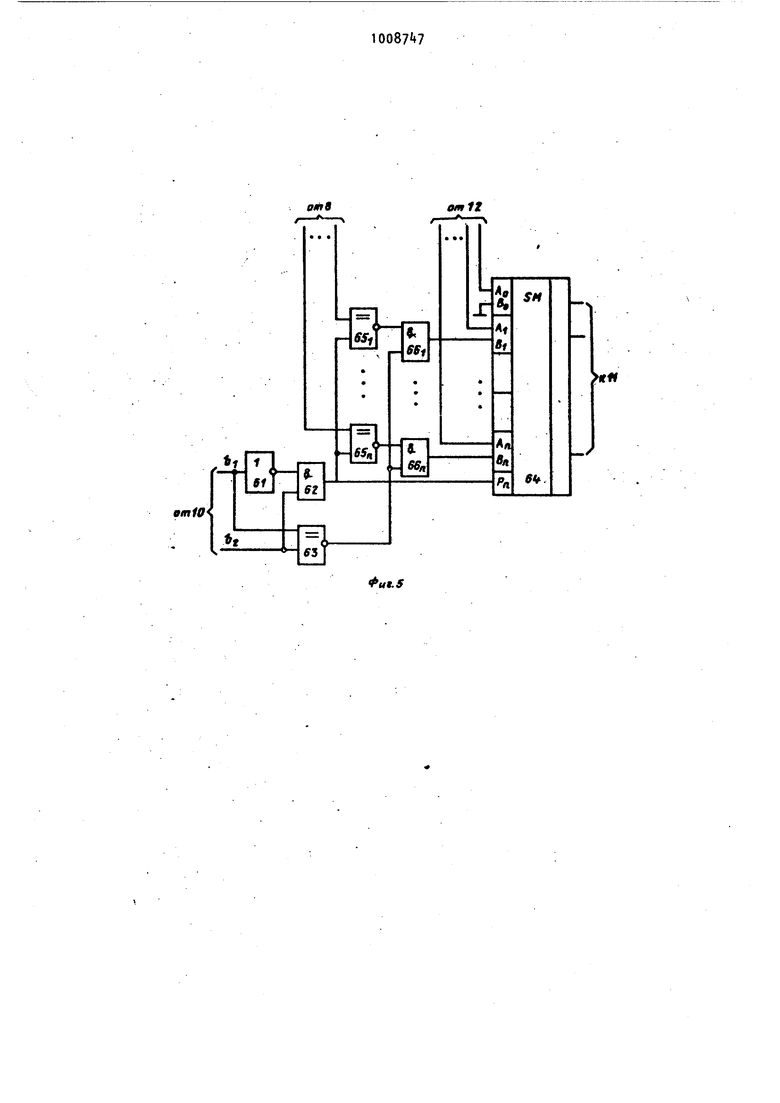

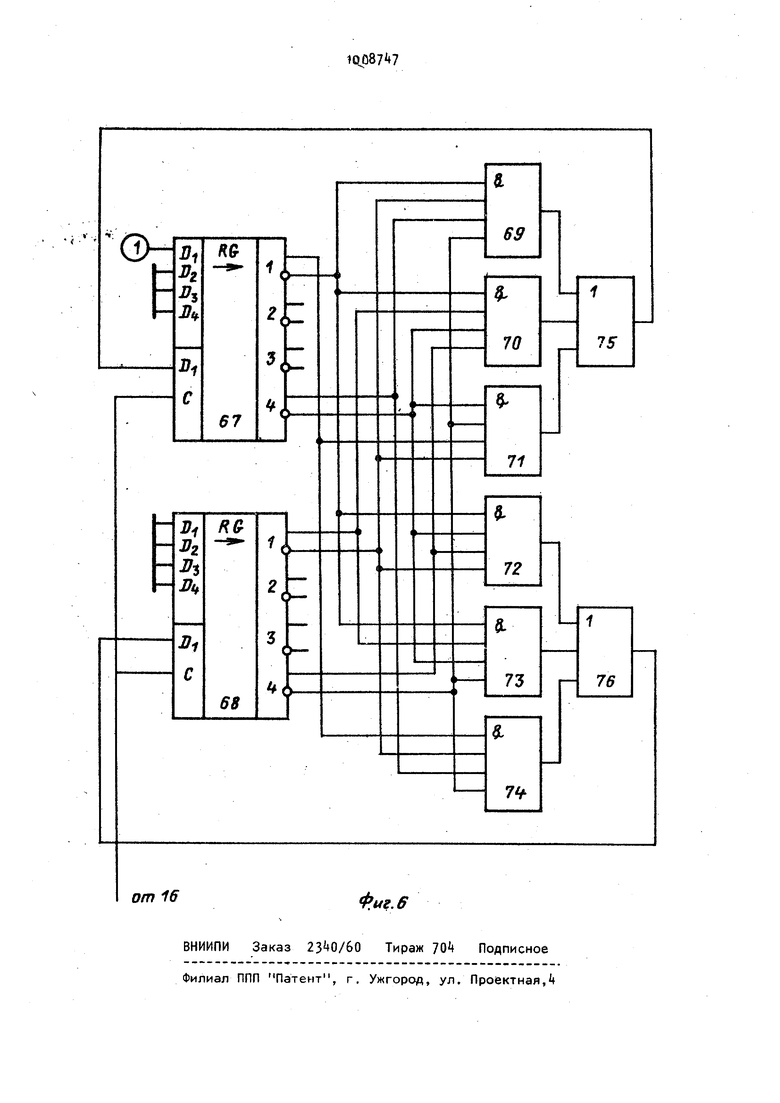

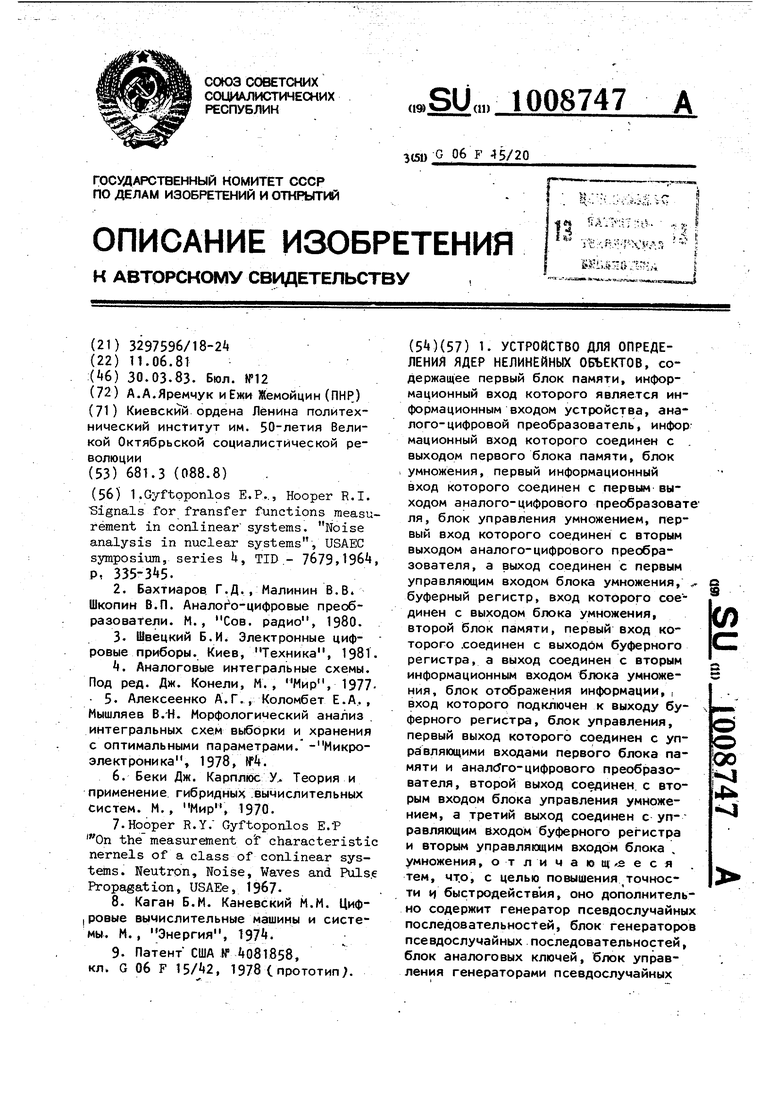

Наиболее близким по технической сущности является, устройство для определения ядер Винера, содержащее . последовательно соединенные блок выборки и запоминания, подключенный к выходу нелинейного объекта, аналого-цифровой преобразователь, арифметическое устройство, буферный регистр и запоминающее устройство, выход которого подключен к входу арифметического устройства, кроме того логическую схему управления арифметическим устройством, первый вход которой подключен к выходу аналогоцифрового преобразователя, а второй к выходу цифровой линии задержки, устройство отображения информации, вход которого подключен к буферному регистру, блок управления, соединен ный с управляющими входами блока .выборки и запоминания, аналого-цифрового преобразователя, арифметичес кого устройства, логической схемы управления арифметическим устройством и буферного регистра Однако известное устройство хара теризуется невысокой точностью изме рения , длительным временем, измереНИИ вследствие больших статистических ошибок измерений, так как в кач стве испытательного сигнала использ ется случайный сигнал. Недостатком известного устройства является такж низкая точность измерений диагональ ных значений ядер. Цель изобретения - повышение точ ности и быстродействия. Поставленная цель достигается тем, что устройство для определения ядер нелинейных объектов, содержащее первый блок памяти, информацион ный вход которого является информационным входом устройства, аналогоцифровой преобразователь, информаци онный вход которого соединен с выходом первого блока памяти, блок умножения, первый информационный вх которого соединен с первым выходом аналого-цифрового преобразователя, блок управления умножением, первый вход которого соединен с вторым выходом аналого-цифрового преобразова теля, а выход соединен с первым . управляющим вхбдом блока умножения, буферный регистр, вход которого сое динен с выходом блока умножения, второй блок памяти, первый вход которого соединен с выходом буферного регистра, а выход срёдинен с вторым информационным входом блока умножения, блок отображения информации, вход которого подключен к выходу буферного регистра, бпок управления первый выход которого соединен с управляющими входами первого блока памяти и аналого-цифрового преобразователя, второй вь1ход соединен с вторым входом блока управления умножением, а третий выход соединен с управляющим входом буферного регис ра и вторым управляющим входом блока умножения, дополнительно содержит генератор, псевдослучайных последовательностей, блок генераторов псевдослучайных последовательностей, блок аналоговых ключей, блок управления генераторами псевдослучайных последовательностей, цифровой формирователь задержки, блок цифровых формирователей задержки и аналоговый сумматор, выход которого является информационным выходом устройства, вход соединен с аналоговым выходом генератора псевдослучайных последовательностей, а группа входов соединена с группой выходов блока аналоговых ключей, цифровой выход генера ора псевдослучайных пбследбвательнос тей соединен с входом цифрового формирователя задержки, выход которого соединен с третьим входом блока управления умножением, а адресный выход соединен с вторым входом второго блока, памяти, группа цифровых выходов блока генераторов псевдослучайных последовательностей соединена с группой входов блока цифровых формирователей задержки, группа выходов которюго соединена с группой входов блока управления умножением, а группа адрес ных выходов соединена с группой входов второго блока памяти, группа выходов блока управления генераторами псевдослучайных последовательностей соединена с группой управляющих входов блока генераторов псевдослучайных последовательностей, группа аналоговых выходов которого соединен с группой входов блока ана;юговых ключей, четвертый выход блока управле.ния соединен с первой группой управляющих входов блока цифровых формирователей задержки, с первой и второй группами входов блока управления генераторами псевдослучайных последовательностей, с управляющим входом генератора псевдослучайных последовательностей и с первым управляющим входом цифрового формирователя задержки, пятый выход блока управления соединен с второй группой-управляю- щих входов блока цифровых формирователей задержки, щестой выход блока управления соединен с группой управляющих входов блока аналоговых ключей, второй управляющий вход цифрового формирователя задержки подключен к третьему выходу блока управления. Кроме того, цифровой формирователь задержки содержит блок регистров сдвига, цифровой коммутатор и счетчик адреса, первый выход которого является адресным выходом формиро вателя, второй выход счетчика адреса соединен с управляющим входом цифрового коммутатора, информационный вход которого соединен с выходом блока регистров сдвига, а выход является выходом формирователя, информационный и управляющий входы блока регистров сдвига являются соответственно входом и первым управляющим входом формирователя, вторым управля ющим входом формирователя является вход счетчика адреса. ® На фиг. 1 представлена блок-схема устройства; на фиг. 2 - приведена блок-схема блока управления (схема этого блока аналогична схеме блока управления прототипа 9 и техническая реализация подобных блоков доста точно подробно изложена в , на фиг. 3 представлена блок-схема двухразрядного цифрового формирователя задержки (этому формирователю идентичны как любой из цифровых формирователей задержки блока, так PI цифровой формирователь задержки ; на фиг. k приведена блок-схема, поясняющая принцип реализации блока управления умножением на примере, поЗ воляющем проводить измерения ядер Вольтерра только первого и второго порядков, техническая реализация таких схем достаточно подробно изложена в 81 I на фиг.5 приведена блок-схема блока умножения (техничес кая реализация таких схем достаточно подробно изложена в L83 ; на фиг. 6 приведена блок-схема цифрового генератора троичной М-последовательности (такие генераторы подробно рассмотрены в . Устройство для определения ядер нелинейных объектов .1) содержит генератор 1 псевдослучайных последовательностей, блок 2 генераторов псевдослучайных последовательностей, блок 3 аналоговых ключей, блок 4 управления генераторами псевдослучайных последовательностей, аналоговый сумматор 5, объект 6 измерения, первый блок 7 памяти, аналого-цифровой преобразователь (,ДЦП) 8, блок 9 умножения, блок 10 управления умножени ем, буферный регистр 11, второй блок 12 памяти, блок 13 г)тображения информации, цифровой формирователь И задержки, блок 15 цифровых формирователей задержки, блок 1б управления. Группа аналоговых выходов блока 2 генераторов псевдослучайных последовательностей соединен с группой входов блока 3 аналоговых ключей, группа выходов которого вместе с аналоговым выходом генератора 1 псевдослучайных последовательностей соединена соответственно с группой входов и входом аналогового сумматора 5. Выход аналогового сумматора 5 является информационным выходом устройства и подключен к входу объекта 6 измерения, выход которого подключен к информационному входу первого блока 7 памяти. Выход первого блока 7 памяти соединен с информационным входом АЦП В, первый вход которого соединен с первым информационным входом б-лока 9 умножения, а второй выход соединен с первым входом блока 10 управления умножением. Выход блока 10 управления умножением соединен с первым управляющим входом блока 9 умножения, второй информационный вход которого соединен с выходом второго блока 12 памяти, а выхОд соединен с входом буферного регистра П. Выход буферного регистра 11 соединен с первым входом второго . блока 12 памяти и с входом блока 13 отображения информации. Цифровой выход генератора 1 псевдослучайных последовательностей соединен с входом цифрового формирователя 14 задержки, выход которого соединен с третьим входом блока 10 управления умножением, а адресный выход соединен с вторым входом второго блока 12 памяти. Группа цифровых выходов блока 2 генераторов псевдослучайных последовательностей соединена с группой входов блока 15 цифровых формирователей задержки, группа выходов которого соединена с группой входов блока 10 управления умножением, а группа адресных выходов соединена с группой входов второго блока 12 памяти. Первый выход блока 16 управления соединен с управляющими входами первого блока 7 памяти и АЦП , 8, второй выход с вторым входом блока 10 управления умножением, третий выход с управляющим входом буферного регистра 11 и вторыми управляющими |Входами блока 9 умножения и цифровоо формирователя задержки, четвертыи выход - с первой группой управляющих входов блока 15 цифровых формирователей задержки., с Первой и второй группами управляющих входов блока управления генераторами псевдослучайных последовательностей с управляющим входом генератора 1 псевдослучайных последовательностей и первым управляющим входом цифрового формирователя 1 задержки, пятый выход - с второй группой управляющих входов блока 15 цифровых формирователей задержки, а шестой выход - с группой управляющих входов блока 3 аналоговых ключей. Группа выходов блока k управления генераторами псевдослучайных последовательностей соединена с группой управляющих входов блока 2 генераторов псевдослучайных последовательностей. Блок 16 управления (фиг. 2) содержит триггер 17I пусковой вход 18 генератор 19 тактовых импульсов, первый блок 20 совпадения, делитель 21 частоты следования импульсов, регистр 22, первый 23 и второй 2k счетчики, блок 25 формирователей импульсов, блок 26 триггеров, второй блок 27 совпадения, группу входов 28 установки порядка измеряемого ядра, которая является группой входов установки порядка измеряемого ядра устройства, первый 29, второй 30, третий 31, четвертый 32, пятый 33 и шестой выходы. Пусковой вход 18 подключен к единичному входу триг гера 17 и является пусковым входом устройства. Единичный выход триггера 17 и выход генератора 19 тактовых импульсов соединены соответственно с первым и вторым входами первого блока 20 совпадения, выход которого соединен с входом делителя 21 частоты следования имцульсов. Выход делителя 21 частоты следования импульс(эв соединен с входом регистра 22, выход которого-соединен с входом первого счетчика 23- Каждый из входов группы 28 установки порядка измеряе го ядра соединен с входом соответствующего i-ro формирователя 25 им пульсов (i 1, 2,..., п, где п число, определяемое максимальным . порядком измеряемых ядер нелинейных объектов) бхюка 25 формирователей импульсов. Группа выходов блока 25 формиров телей импульсов, соединена с группой входов блока 26 триггеров, группа 1 7 которого соединена с первой выходов группой входов второго блока 27 совпадения. Выходы второго блока 27 совпадения и второго счетчика 2k подключены к нулевому входу триггера 17Двухразрядный цифровой формирователь 1+ и 15i задержки Гфиг. 3) содержит блок 152. Регистр ов сдвига,, цифровой коммутатор и счетчик 15. адреса. Вход блока 15 регистров сдвига является входом формирователя а выход соединен с информационным входом цифрового коммутатора 15 выход которого р- -ляется выходом формирователя. Управляющий (тактовый) вход блока 151 регистров сдвига является первым управляющим входом, формирователя. Вход счетчика 151 адреса является вторым управляющим входом формирователя, первый выход является адресным выходом формирователя, а второй выход соединен с управляющим входом входом цифрового коммутатора ISlj. В свою очередь, блок 15. регистров сдвига состоит из двух К-разрядных сдвиговых регистров 35 и 36 (где К - число разрядов псевдослучайных последовательностей, генерируемых генератором 1 и генераторами блока 2). Информационные входы сдвиговых регистров 35 и 36 образуют вход блока 15. . а тактовые входы -, управляющий (тактовый; вход этого же блока. Разрядные выходы сдвиговых регистров 35 и 36 образуют выход блока 15. Счетчик 15 адреса состоит из счетчика 37 и дешифратора ЗВ. Цифровой коммутатор состоит из двух элементов И и двух элементов ИЛИ 39 и 40, выходы которых образу.Ют выход цифрового коммутатора 15л Счетный вход счетчика 37 является входом счетчика 15 адреса, а разрядные выходы образуют первый выход счетчика 151 адреса и соединены с входами дешифратора 38,-выходы которого .образуют второй выход счетчика 15 адреса.. . Блок 10 управления умножением,позволяющий проводить измерения ядер Вольтерра первого и второго порядков, (фиг, k состоит из элементов И itl52, ИЛИ.53, И , НЕ 58. Первые входы элементов И 5 и 55 и вход элемента НЕ 58 образуют первый вход блока 10 управления умножением, .вторые входы элемента И 50 и элемента ИЛИ 53 образуют его второй вход, а первые входы элементов И 5 и tS и вторые входы элементов И и iS образуют третий вход: . Первые входы элементов И kS и 50 образуют первый из группывходов блока 10 управления умножением, а выходы элементов И 59 и 60 образуют его выход. Блок 9 умножения ( фиг. 5) состоит из элемента НЕ 61, элемента И б2, сумматора 63 по модулю два, сумматора , группысумматоров 65 по модул два и группы элементов И 66. Входы группы сумматоров б5 по модулю два образуют первый информационный вход блока 9 умножения, а входы сумматора 6 образуют второй информационный вход этого блока. Вход НЕ 61 и входы сумматора 63 по модулю два образуют первый управляющий вход блока 9 умножения. Тактовый вход сумматора 6k является вторым управля ющим входом блока 9 умножения, а выходы .сумматора б являются выходом этого блока. Каждый генератор псевдослучайных последовательностей ( генератор 1 и любой из генераторов блока 2) состоит из последовательно соединенных цифрового генератора 2(1) троичной ,М-последовательности и цифро-. аналогового преобразователя ЦАП 2 Uj.) Управляющий в-ход цифрового ген ратора троичной М-последовательности является управляющим входом генерато ра псевдослучайных последовательностей, а выход является цифровым выхо дом того же генератора. Выход цифроаналогового преобразователя является аналоговым выходом генератора псевдослучайных последовательностей, Цифровой генератор троичной М-последовательности (фиг. 6) состоит .из двух сдвиговых регистров б7 и 68, шести элементов И 69- и двух элементов ИЛИ 75-76. Каждая группа элементов (одна элементы И и ИЛИ 75 и другая элементы И 12-lk и ИЛИ 7б) образует сумматоры по модулю три, которые включены в цепи обратной связи сдвиговых регистров 67 и 68. Блок 4 управления генераторами псев дослучайных последовательностей состоит из п независимых друг от друга управляющих элементов, каждый из которых в свою очередь состоит из последовательно соединенных счетчика k , элемента НЕ t и б.лока V.J совпадения. Вход счет,чика t является первым управляющим ВХОДОМ, а первый вход блока сов- i падения является вторым управляющим входом управляющего элемента. Выход блока f совпадения является выходом -управляющего элемента. Совокупности входов и выходов управляющих элементов составляют соответствующие группы входов и выходов блока k управления генераторами псевдослучайных последовательностей. Суть измерения ядер Вольтерра Рго порядка где Р- порядок нелинейности объекта измерения) в предлагаемом устройстве заключается в подаче на вход объекта измерения суммы Р входных испытательных сигналов и усреднений в те.чение определенного времени произведения выходного сигнала объекта измерения с Р задержанными входными испытательными сигналами. Рассмотрим работу предлагаемого устройства в режиме измерения ядра Вольтерра второго порядка. I Режим измерения ядра Вольтерра второго порядка задается по входу 28 блока 16 управления установкой в 1 соответствующего триггера блока 2б. При этом по сигналу с шестого выхода блока 16 управления открывается соответствующий аналоговый ключ в блоке 3. После поступления сигнала Пуск на вход 18 блока 16 управления триггер 17 устанавливается в Ч, и тактовые импульсы из блока 16 управления начинают поступать на блоки устройства. На выходе Цифрового генератора 1 М-последовательности появится трехуровневая Т1ифровая периодическая последовательность |х|(,,Т периода га .образованная с помощью троичной М-последовательности 1V.. I длины m , согласно соотношению, « 1 1 г т; О 1 т-Г v где 5,- - значение сигнала в момент . времени 1 А , Ь. - период тактовых импульсов. Первый управляющий элемент блока i управления генераторами псевдослучайных последовательностей блокирует поступление каждого т-го так-гового импульса на вход соответствующего (первого) цифрового генератора 2 М-последовательности, на выходе котоporo появляется трехуровневая периодическая цифровая последовательность J Хц J периода т , сочетающая m М-последовательностейJv согласно соотношению X,- f ( 1 i т; QL Р -s. где@-операция суммирования по моду лю m . Цифровые периодические последовательности х и IX М с выходов цифровых генераторов и М-последовательностеи поступают на входы цифро-аналоговых преобразователей соответственно 12 и 2 , а также на входы цифровых формирователей 14 Сдвиговые регистры и 15 задержки , на сдвигающие входы которых поступаю т тактовые импульсы периода Д, содержит т/2 ячеек, так что ма ксТ1мальное время задержки составляет m А2. Аналоговые сигналы с выхода цифро аналоговых преобразователей Т и подаются на входы аналогового сумматора 5. выхЪдной сигнал которого воздействует на вход объекта 6 измерения. На вход счетчика 14 адреса из блока 16 управления подаются тактовые импульсы с частотой f . Е-.; л 2Л При этом последовательно опрашиваются все ячейки сдвигового регистра 14;J . Результаты опроса в виде цифрового двухразрядного кода с выхода цифрового коммутатора. 1 t поступают на блок 10 управления умноже нием. Одновременно блок 16 управления начинает выдавать с тактовой частотой f импульсы опроса второго блока 12 памяти. Адреса опрашиваемых ячеек второго блока 12 памяти формируются в счетчиках 14 и 15з Результаты опроса второго блока 12 ;.памяти в виде цифрового кода посту|пают на второй информационный вх блока 9 умножения. Через определенный промежуток времени после пуска устройства, численно равного тЛ/2 блок 16 управления начинает посылать тактовые импульсы с частотой 1/Д на.управляю щие (тактовые или синхронизирующие) входы первого блока 7 памяти и аналого-цифрового преобразователя 8. Совместное действие первого блока 7 па мяти и АЦП 8 сводится к преобразованию 8течение интервала выборки Д , выходного сигнала объекта 6 измерения в цифровой сигнал, включая сигнал знака, который подается на первый вход блока 10 управления умножителем На.первый информационный вход блока 9умножения начинает поступать сигнал с выхода аналого-цифрового преобразователя 9, являющийся результатом аналого-цифрового преобразования текущего сигнала на выходе объекта 6 измерения. Блок 9 умножения, управляемый сигналами блока 10 управления умнсжением, выполняет сложения, вычитания или пропуска с кодовыми сигналами, поданнымина его информационные входы. Выходные сигналы блока ,9 умножения поступают через буферный регистр,11 во второй блок 12 памяти. Через отрезок времени, численно равный , после запуска аналогоцифрового преобразователя 8 в соответствующих ячейках второго блока 12 памяти будет накоплено множество дискретизированных значений Z (С. Т-) причем Z (Xt .-Г;) КаЬ,(.Д , 1Д) для 1 1, 2,..., т/2, где К - коэффициент преобразования предлагаемого устройства в режиме измерения ядра Воль-, терра второго порядка, Ь2(Д, - значения ядер Вольтерра. вто1) рого порядка для врененНых ординат (д, 1Л). & этот момент времени с пятого выхода блока 16 управления поступает импульс в счетчик 15 адреса, увеличивая его содержимое на единицу. Начиная с этого момента в соответствующих ячейках второго блока 12 памяти накапливаться множество дискретизированных значений zC ) пропорциональных значениям ядер Воль терра второго порядка во временном сечении (2Д, 1Д). После подачи т/2 импульсов в счетчик 15 адреса, подача всех управляющих импульсов из блока 16 управления прекращается. В соответствующих ячейках второго блока 12 памяти хранится множество / дискретизированных значений . Z(t3,t)K,h,(jA, iA) ДЛЯ i 1, 2,..., m/2, ,2,...., m/2. Результаты измерений, хранящиеся во втором блоке 12 памяти, параллельно

фиксируются в блоке 13 отображения : информации.

Режим измерения ядра Вольтерра . первого порядка (импульсной переходной характеристики первого порядка) $ задается по входу 28 блока 16 управления. При этом по сигналу с шестого выхода блока 16 управления закрывается блок 3 аналоговых ключей, тем самым прекращая поступление испыта- 0 тельного сигнала с группы аналоговых выходов блока 2 генераторов псевдослучайных последовательностей на вход аналогового сумматора 5После команды Пуск блок 16 управ-1$ ления вырабатывает последовательность управляющих команд, аналогичную случаю измерения ядра второго порядка. Спустя время, численно равное тД/2 на первый информационный вход блока 20 9 умножения начинает поступать кодовый сигнал с выхода аналого-цифрового преобразователя 8.

В течение интервала вь1борки Дна второй информационный вход блока 9 . 25 |yмнo)t(eния поочередно поступает кодо1вый сигнал, являющийся результатом последовательного опроса ячеек второго блока 12 памяти, в которых накапли вается информация о значениях измеря-jjj емых ядер. Адреса опрашиваемых ячеек второго блока 12 памяти определяются содержимым счетчика Й адреса. Блок 9 умножения, управляемый сигналами блока 10 управления умножением, выполняет операции сложения, вычитания -или пропуска с кодовыми сигналами, поданными на его два входа.

Через время, численно равноеКя Д после запуска аналого-цифрового преобразователя 8, блок 16 управления прекращает выдачу всех управляющих сигналов ( единичное состояние счетчика 23 вызывает срабатывание блока

27 совпадения). В соответствующих ячейках второго блока 12 памяти нахо дится множество дискретизированных значений

Z (0,) K(i ) для i 1,2...m/2

где К - коэффициент преобразования предложенного устройства в режиме измерения ядра Вольтерра первого порядка.

Результаты измерений, хранящиеся во втором бло.ке 12 памяти параллельно фиксируются в блоке 13 отображения информации.

Предлагаемое устройство по сравнению с прототипом позволяет значительно повысить точность и быстродействи измерений ядер (импульсных переход|Ных характеристик) нелинейных объектов.

Поскольку в прототипе в качестве генератора испытательных сигналов используется генератор белого шума с ограниченной полосой частот, то ему присущи погрешности из-за конечного времениусреднения, что приводи к большим статическим флуктуациям результатов измерений. Предлагаемое же устройство свободно от этого недостатка, так как в нем в качестве источников испытательных сигналов используются генераторы псевдослучайных последовательностей.

При одинаковой суммарной погрешности измерения время измерений при использований предлагаемого устройства будет в k раза меньше по сравнению с временем измерения при использовании прототипа. Это означает, что в четыре раза возрастает производительность измерений.

Фи9. 1

Фиг, г

Atf. вя.

L| J 49.9

fut.f

О1п9

omit

| I.Gyftpponlos Е.Р.., Hooper R.I | |||

| Signals for Transfer functions raeasurement in conlinear systems | |||

| Noise analysis in nuclear systems, USAEC symposium, series U, TID - 7679J96, P, 335-345 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Шкопин В.П | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| М., Сов | |||

| радио, 1980 | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Электронные циф- ровые приборы | |||

| Киев, Техника, 198Т | |||

| Ц | |||

| Аналоговые интегральные схемы | |||

| Под ред | |||

| Дж | |||

| Конели, М., Мир, 1977 5 | |||

| Алексеенко А.Г., Коломбет Е.А. | |||

| , Мышляев В.-Н | |||

| Морфологический анализ интегральных схем выборки и хранения с оптимальными параметрами | |||

| - Микроэлектроника, 1978, № | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Беки Дж | |||

| Карплюс У Теория и применение гибридных ;вычислительных систем | |||

| М., Мир, 1970 | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| R.Y | |||

| Gyftoponlos Е.Р the measurement of characteristic nernels of a class of conlinear systems | |||

| Neutron, Noise, Waves and Puls.e Propagation, USAEe, 19678.Каган Б.М | |||

| Каневский М.М | |||

| ЦифIровые вычислительные машины и системы | |||

| М | |||

| , Энергия, 197 | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| G Об F , 1978 (прототип;. | |||

Авторы

Даты

1983-03-30—Публикация

1981-06-11—Подача