Фиг

11

Изобретение относится к технике связи и может использоваться в устройствах помехоустойчивого кодирования при передаче дискретной информа- даи.

Цель изобретения - повьшение помехоустойчивости устройства.

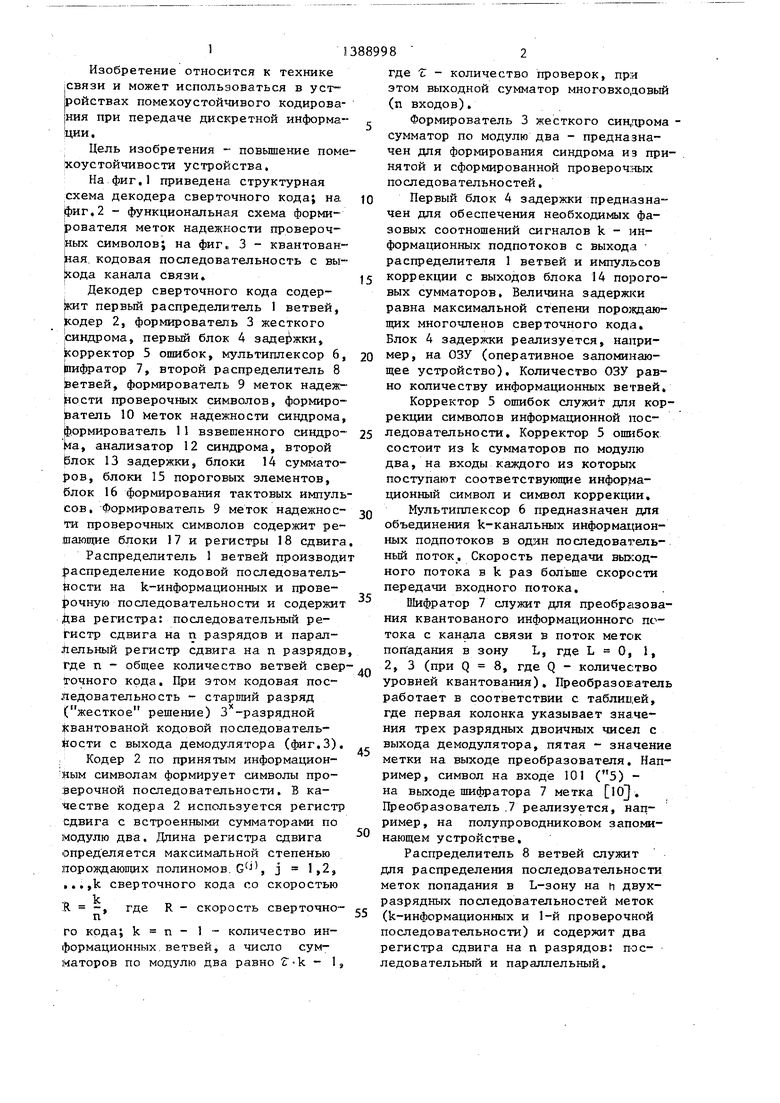

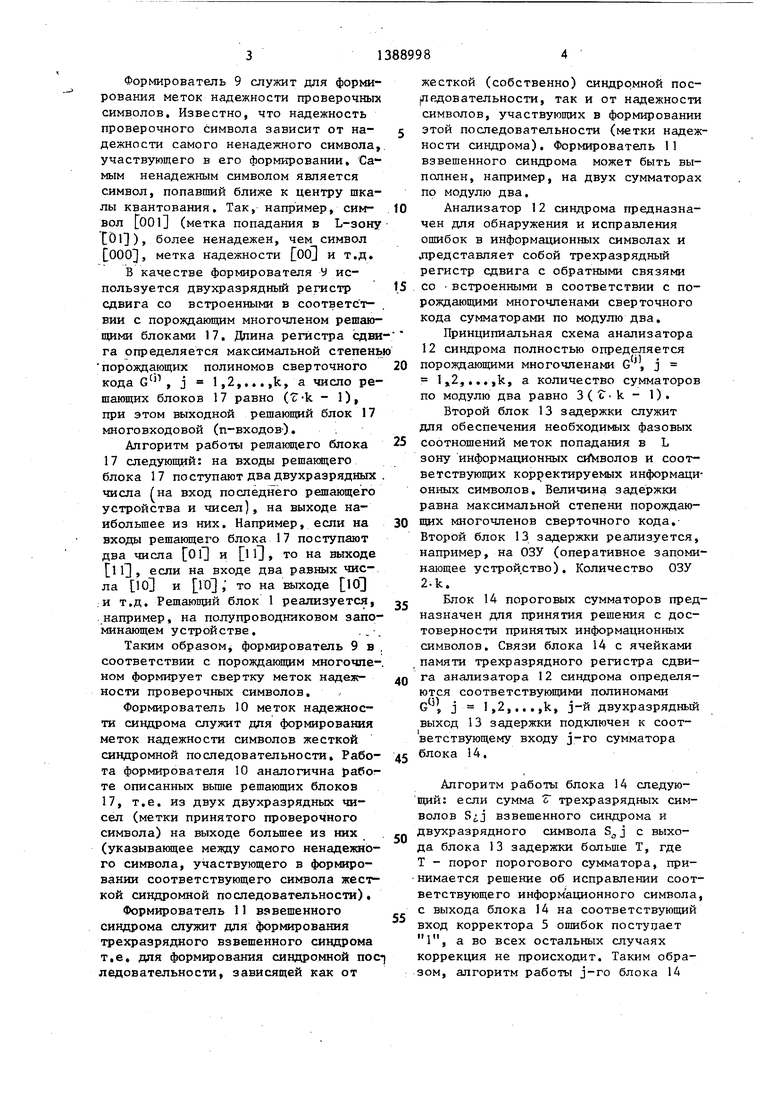

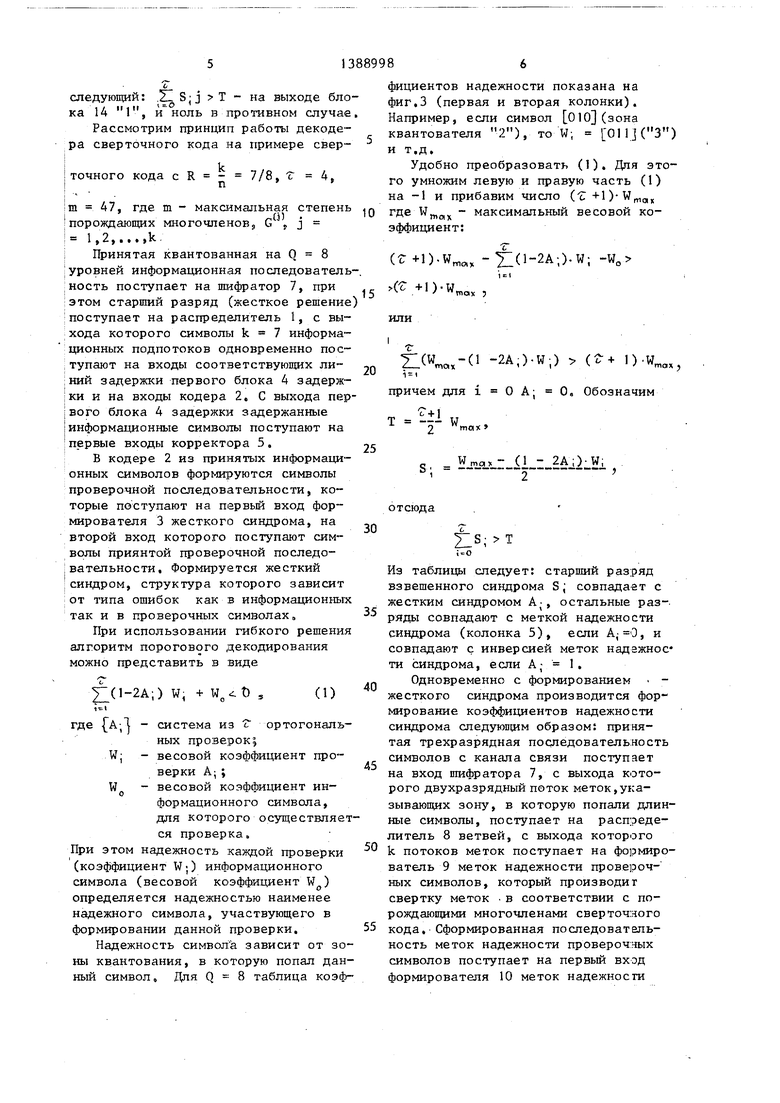

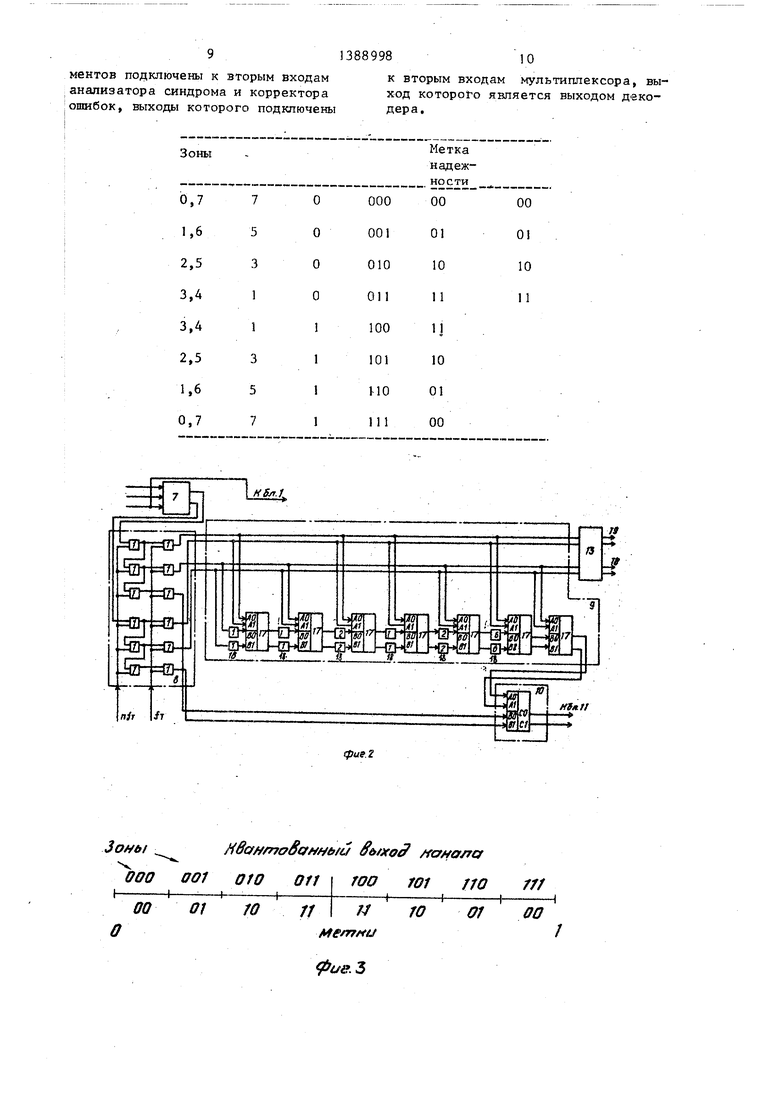

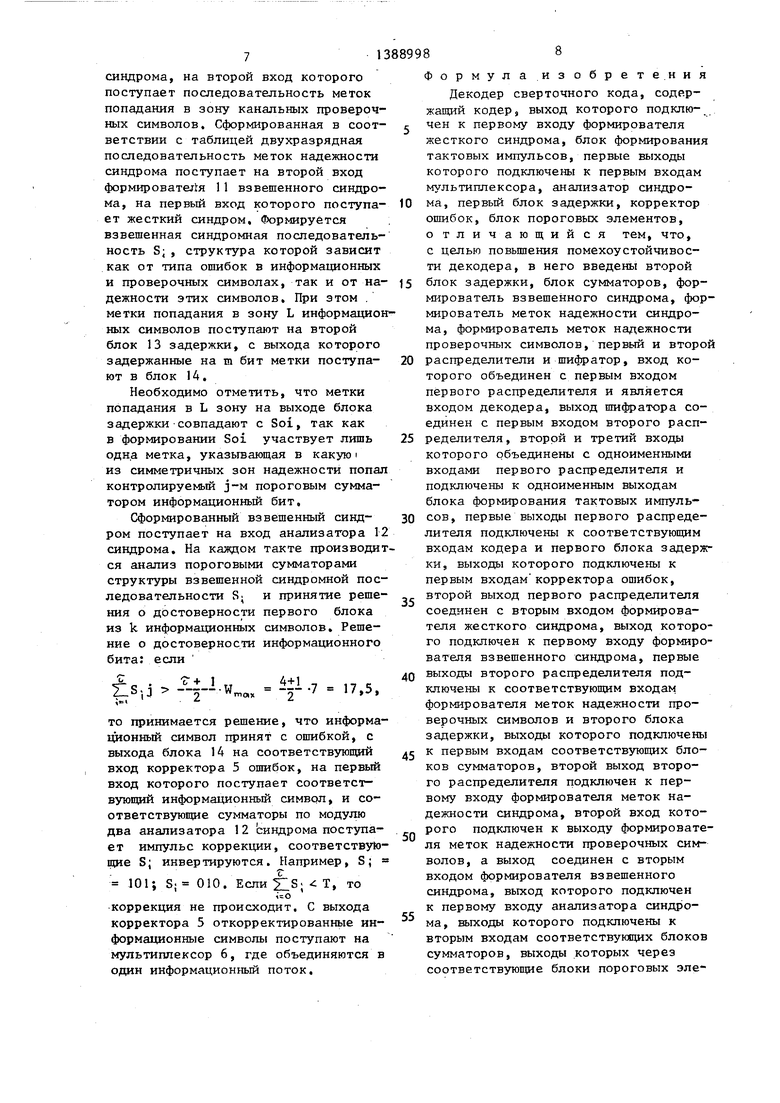

На фиг,1 приведена структурная схема декодера сверточного кода; на фиг,2 - функциональная схема формирователя меток надежности провероч- ых символов; на фиг, 3 - квантован- ая. кодовая последовательность с вы- рсода канала Связи,

Декодер сверточного кода содер- т первый распределитель 1 ветвей, содер 2, формирователь 3 жесткого Шндрома, первый блок 4 задержки, корректор 5 ошибок, мультиплексор 6 (пифратор 7, второй распределитель 8 етвей, форютрователь 9 меток надеж- ости проверочных символов, формиро- |ватель 10 меток надежности синдрома формирователь 11 взвешенного синдро- jwa, анализатор 12 синдрома, второй Ьлок 13 задержки, блоки 14 суммато

ров, блоки 15 пороговых элементов, блок 16 формирования тактовых импульсов. Формирователь 9 меток надежное- ти проверочных символов содержит решающие блоки 17 и регистры 18 сдвига

Распределитель 1 ветвей производи распределение кодовой последователь- Йости на k-информационных и проверочную последовательности и содержит |iiBa регистра: последовательный регистр сдвига на п разрядов и параллельный регистр сдвига на п разрядов Где п - общее количество ветвей сверточного кода. При этом кодовая последовательность - старпшй разряд (жесткое решение) 3 -разрядной Квантованой кодовой последователь- Йости с выхода демодулятора (фиг,3).

Кодер 2 по принятым информацион- символам формирует символы про- :Верочной последовательности, В качестве кодера 2 используется регистр Сдвига с встроенными сумматорами по модулю два. Длина регистра сдвига Определяется максимальной степенью порождаюпшх полиномов. G J , j 1,2, ,,,,k сверточного кода со скоростью

где R - скорость сверточно-

R - п

Го кода; k п - 1 - количество информационных, ветвей, а число сумматоров по модулю два равно -k - 1,

0 5

5

0

Q

5

0

5

где 6 - количество проверок, при этом выходной сумматор многовходовый (п входов),

Формирователь 3 жесткого син,гфома - сумматор по модулю два - предназначен для формирования синдрома из принятой и сформированной провероч:яых последовательностей.

Первый блок 4 задержки предназначен для обеспечения необходимых фазовых соотношений сигналов k - информационных подпотоков с выхода распределителя 1 ветвей и импульсов коррекции с выходов блока 14 пороговых сумматоров. Величина задержки равна максимальной степени порозкдаю- щих многочленов сверточного кода. Блок 4 задержки реализуется, например, на ОЗУ (оперативное запоминающее устройство). Количество ОЗУ равно количеству информационных ветвей.

Корректор 5 ошибок служит для коррекции символов информационной последовательности. Корректор 5 ошибок состоит из k сумматоров по модулю два, на входы каждого из которьпс поступают соответствующие информационный символ и символ коррекции,

Мультиплексор 6 предназначен для объединения k-канальных информационных подпотоков в один последовательный поток. Скорость передачи вькод- ного потока в k раз бсльше скорости передачи входного потока.

Шифратор 7 служит для преобразования квантованого информационного пс- тока с канала связи в поток меток попадания в зону L, где L О, 1, 2, 3 (при Q 8, где Q - количество уровней квантования). Преобразователь работает в соответствии с таблицей, где первая колонка указывает значения трех разрядных двоичных чисел с выхода демодулятора, пятая - значение метки на выходе преобразователя. Например, символ на входе 101 (5) - на выходе шифратора 7 метка . Преобразователь .7 реализуется, например, на полупроводниковом запоминающем устройстве.

Распределитель 8 ветвей служит для распределения последовательности меток попадания в L-зону на и двухразрядных последовательностей меток (k-информационных и 1-й проверочной последовательности) и содержит два регистра сдвига на п разрядов: последовательный и параллельный.

Формирователь 9 служит для формирования меток надежности проверочных символов. Известно, что надежность проверочного символа зависит от на- дежности самого ненадежного символа, участвующего в его формировании, Самым ненадежным символом является символ, попавший ближе к центру шкалы квантования. Так, например, сим- вол 001 (метка попадания в Ъ-зону 013), более ненадежен, чем символ 000, метка надежности OOj и т,д,

В качестве формирователя У используется двухразрядный регистр сдвига со встроенными в соответс т- вии с порождающим многочленом решающими блоками 17. Длина регистра сдай га определяется максимальной степень порождающих полиномов сверточного кода G j 1,2,,,, ,k, а число решающих блоков 17 равно (c-k - 1), при этом выходной решающий блок 17

МНОГОВХОДОВОЙ (п-ВХОДОВ ) .

Алгоритм работы решающего блока 17 следующий: на входы решакяцего блока 17 поступают два двухразрядных числа (на вход последнего решающего устройства и чисел), на выходе наибольшее из них. Например, если на входы решающего блока 17 поступают два числа OQ и l О, то на выходе l 1 , если на входе два равных числа 10 и то на выходе 10 .и т,д, Решаюишй блок 1 реализуется, .например, на полупроводниковом запоминающем устройстве,..-,

Таким образом формирователь 9 в соответствии с порождающим многочленом формирует свертку меток надеж- ности проверочных символов.

Формирователь 10 меток надежности синдрома служит для формирования меток надежности символов жесткой синдромной последовательности, Рабо- та формирователя 10 аналогична рабог- те описанных выше решающих блоков 17, т,е, из двух двухразрядных чисел (метки принятого проверочного символа) на выходе большее из них (указывающее между самого ненадежного символа, участвующего в формировании соответствующего символа жесткой синдромной последовательности),

Формирователь 11 взвешенного синдрома служит для формирования лрехразрядного взвешенного синдрома т,е, для формирования синдромной пос ледовательности, зависящей как от

j 10

15 20

5 30 5

0

дз CQ

5

жесткой (собственно) синдромной пос- ледовательности, так и от надежности символов, участвующих в формировании этой последовательности (метки надежности синдрома), Формирователь 11 взвешенного синдрома может быть выполнен, например, на двух сумматорах по модулю два.

Анализатор 12 синдрома предназначен для обнаружения и исправления ошибок в информационных символах и представляет собой трехразрядный регистр сдвига с обратными связями со встроенными в соответствии с порождающими многочленами сверточного кода сумматорами по модулю два.

Принципиальная схема анализатора 12 синдрома полностью определяется порождающими многочленами G , j l,2,,,,,k, а количество сумматоров по модулю два равно 3( c.k - 1),

Второй блок 13 задержки служит для обеспечения необходимых фазовых соотношений меток попадания в L зону информационных аЛ1волов и соответствующих корректируемых информационных символов. Величина задержки равна максимальной степени порождающих многочленов сверточного кода. Второй блок 13 задержки реализуется, например, на ОЗУ (оперативное запоминающее устройство). Количество ОЗУ 2.k,

Блок 14 пороговых сумматоров предназначен для принятия решения с достоверности принятых информационных символов. Связи блока 14 с ячейками памяти трехразрядного регистра сдвига анализатора 12 синдрома определяются соответствующими полиномами G j l,2,.,,,k, j-й двухразрядный выход 13 задержки подключен к соответствующему входу j-ro сумматора блока 14,

Алгоритм работы блока 14 следующий: если сумма Т трехразрядных символов взвешенного синдрома и двухразрядного символа с выхода блока 13 задержки больше Т, где Т - порог порогового сумматора, принимается решение об исправлении соответствующего информационного символа, с выхода блока 14 на соответствующий вход корректора 5 ошибок поступает 1, а во всех остальных случаях коррекция не происходит. Таким образом, алгоритм работы j-ro блока 14

следующий: .ZI S;j Т - на выходе блока 14 1, и ноль в противном случае. Рассмотрим принвдп работы декодера сверточного кода на примере свер-

точного кода с R

7/8, Г 4,

m 47, где m - максимальная степень порождающих многочленовд G% j - l,,«t i Принятая квантованная на Q 8 уровней информационная последователь ность поступает на шифратор 7, при этом старший разряд (жесткое решение поступает на распред1глитель 1, с выхода которого символы k 7 информационных подпотоков одновременно поступают на входы соответствующих ли- НИИ задержки первого блока 4 задержки и на входы кодера 2, С выхода первого блока 4 задержки задержанные информационные символы поступают на первые входы корректора 5.

В кодере 2 из щ инятых информационных символов форьаг|1уются символы проверочной последовательности, которые поступают на первьй вход формирователя 3 жесткого синдрома, на второй вход которого поступают символы приянтой проверочной последовательности, Формщэуется жесткий синдром, структура которого зависит от типа ошибок как в информационных

так и в проверочных символах.

При использовании гибкого решения алгоритм порогового декодирования можно представить в виде

(1-2А;) W, + ) ,

(1)

где - система из ортогональных проверок

Wj - весовой коэффициент проверки А; ;

W - весовой коэффициент ин0

формационного символа, для которого осуществляется проверка.

При этом надежность каждой проверки (коэффициент W;) информационного символа (весовой коэффициент W) определяется надежностью наименее надежного символа, участвующего в формировании данной проверки.

Надежность символ а зависит от зоны квантования, в которую попал данный символ, Для Q 8 таблица коэф

фициентов надежности показана на фиг.З (первая и вторая колонки). Например, если символ 010(зона квантователя 2), то W; 01(3) и т.д.

Удобно преобразовать (1). Для этого умножим левую и правую часть (1) на -1 и прибавим число ( с +l),j где - максимальный весовой коэффициент:

(-t-D-W, -i:(l-2A;).W; -W

C,+i)-w,, ,

или

i:(,,-0 -2A,)-W;)

i i

причем для i О A; 0,

T+l X - у

2 max

„ ,- (1 - 2A;)-Wi S,-,

отсюда

30

5

0

5

Из таблицы следует: старший разряд взвешенного синдрома S; совпадает с жестким синдромом А; , остальные раз-, ряды совпадают с меткой надежности синдрома (колонка 5), если А,, и совпадают с инверсией меток надежное ти синдрома, если А; 1.

Одновременно с формированием - жесткого синдрома производится формирование коэффициентов надежности синдрома следуюп5им образом: принятая трехразрядная последовательность символов с канала связи поступает на вход шифратора 7, с выхода которого двухразрядный поток меток,указывающих зону, в которую попали длинные символы, поступает на распределитель 8 ветвер, с выхода которого k потоков меток поступает на формирователь 9 меток надежности провероч- ных символов, который производит свертку меток .в соответствии с порождающими многочленами сверточного кода, Сформированная последовательность меток надежности провероч:г1ых символов поступает на первьш вход формирователя 10 меток надежности

синдрома, на второй вход которого поступает последовательность меток попадания в зону канальных проверочных символов. Сформированная в соответствии с таблицей двухразрядная последовательность меток надежности синдрома поступает на второй вход формироватегЫ 11 взвешенного синдрома, на первый вход которого поступает жесткий синдром. Формируется взвешенная синдромная последовательность S; , структура которой зависит как от типа ошибок в информационных и проверочных символах, так и от надежности этих символов. При этом . метки попадания в зону L информационных символов поступают на второй блок 13 задержки, с выхода которого задержанные на m бит метки поступают в блок 14,

Необходимо отметить, что метки попадания в L зону на выходе блока задержки совпадают с Soi, так как в формировании Soi участвует лишь одна метка, указывающая в какуюi из симметричных зон надежности попал контролируемый j-м пороговым сумматором информационный бит.

Сформированный взвешенный синдром поступает на вход анализатора 12 синдрома. На каждом такте производится анализ пороговыми сумматорами структуры взвешенной синдромной последовательности S; и принятие решения о достоверности первого блока из k информационных символов. Решение о достоверности информационного бита: если

5-i-i.w

2max

il .7

2

17,5,

то принимается решение, что информа- 1ЩОННЫЙ символ принят с ошибкой, с выхода блока 14 на соответствующий вход корректора 5 ошибок, на первый вход которого поступает соответствующий информационный символ, и соответствующие сумматоры по модулю два анализатора 1 2 синдрома поступает импульс коррекции, соответствующие S; инвертируются. Например, S;

101; S; 010, Если 21S; Т, то

коррекция не происходит, С выхода корректора 5 откорректированные информационные символы поступают на мультиплексор 6, где объединяются в один информационный поток.

8

Формула изобрете.ния Декодер сверточного кода, содержащий кодер, выход которого подклю

0

5

0

5

0

5

0

5

чен к первому входу формирователя жесткого синдрома, блок формирования тактовых импульсов, первые выходы которого подключены к первым входам мультиплексора, анализатор синдрома, первый блок задержки, корректор ошибок, блок пороговьсх элементов, о тличающий ся тем, что, с целью повьштения помехоустойчивости декодера, в него введены второй блок задержки, блок сумматоров, формирователь взвешенного синдрома, формирователь меток надежности синдрома, формирователь меток надежности проверочных символов, первый и второй распределители и шифратор, вход которого объединен с первым входом первого распределителя и является входом декодера, выход шифратора соединен с первым входом второго распределителя, второй и третий входы которого объединены с одноименными входами первого распределителя и подключены к одноименным выходам блока формирования тактовых импульсов, первые выходы первого распределителя подключены к соответствующим входам кодера и первого блока задержки, выходы которого подключены к первым входам корректора ошибок, второй выход первого распределителя соединен с вторым входом формирователя жесткого синдрома, выход которого подключен к первому входу формирователя взвешенного синдрома, первые выходы второго распределителя подключены к соответствующем входам формирователя меток надежности проверочных символов и второго блока задержки, выходы которого подключены к первым входам соответствующих блоков сумматоров, второй выход второго распределителя цодключен к первому входу формирователя меток надежности синдрома, второй вход которого подключен к выходу формирователя меток надежности проверочных символов, а выход соединен с вторым входом формирователя взвешенного синдрома, выход которого подключен к первому входу анализатора синдрома, выходы которого подключены к вторым входам соответствующих блоков сумматоров, выходы которых через соответствуюш11е блоки пороговых элементов подключены к вторым входам

анализатора синдрома и корректора

:ошибок, выходы которого подключены

к вторым входам мультиплексора, выход которого является выходом декодера.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1992 |

|

RU2085035C1 |

| ПОРОГОВЫЙ ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1991 |

|

RU2023349C1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Пороговый декодер сверточного кода | 1991 |

|

SU1837385A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| СПОСОБ СИНДРОМНОГО ДЕКОДИРОВАНИЯ ДЛЯ СВЕРТОЧНЫХ КОДОВ | 2004 |

|

RU2282307C2 |

| Декодер сверточного кода (его варианты) | 1985 |

|

SU1320875A1 |

| Декодер сверточного кода | 1985 |

|

SU1320904A1 |

| Пороговый декодер сверточного кода | 1986 |

|

SU1443180A1 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

Изобретение относится к технике СВЯ2И и может использоваться для обеспечения помехоустойчивого кодирования при передаче дискретной ин- формации. Цель изобретения - повьше- ние помехоустойчивости устройства. Декодер сверточного кода содержит первый 1 и второй 8 распределители ветвей, кодер 2, формирователь 3 жесткого синдрома, первый 4 и второй 13 блоки задержки, корректор 5 ошибок, мультиплексор 6, шифратор 7, формирователь 9 меток надежности проверочных символов,формирователь 10 меток надежности синдрома, формирователь .11 взвешенного синдрома, анализатор 12 синдрома, блоки 14 сумматоров, блоки 15 пороговых элементов. Использование декодера сверточного кода с мягким алгоритмом решения позволяет повысить помехоустойчивость при фиксированном объеме оборудования и особенно эффективно для декодирования длинных (с большой длиной кодового ограничения) высокоскоростных кодов. 3 ил. i (Л

ts

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Декодер сверточного кода | 1985 |

|

SU1320904A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-04-15—Публикация

1986-04-18—Подача