Изобретение относится к радиотехнике и может быть использовано для приема данньпс, передаваемых последовательным частотным кодом от различных источников информации.

Цель изобретения - расширение функциональных возможностей путем декодирования тональных сигналов одновременно от нескольких источников информации.

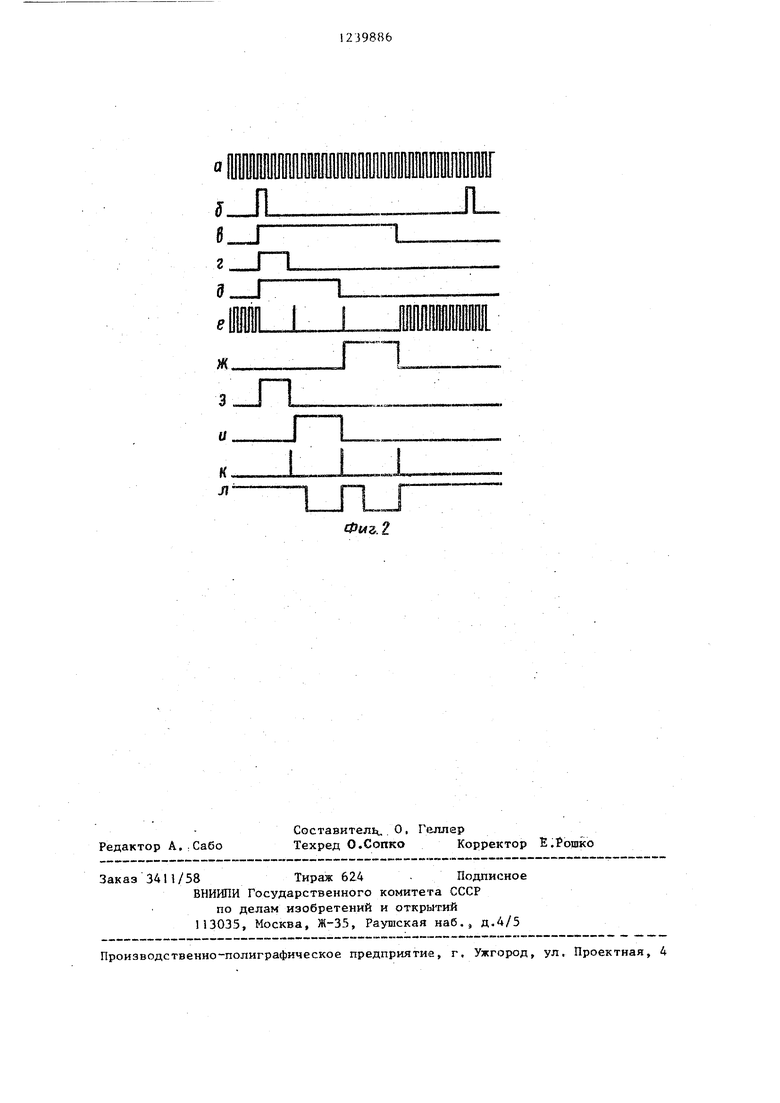

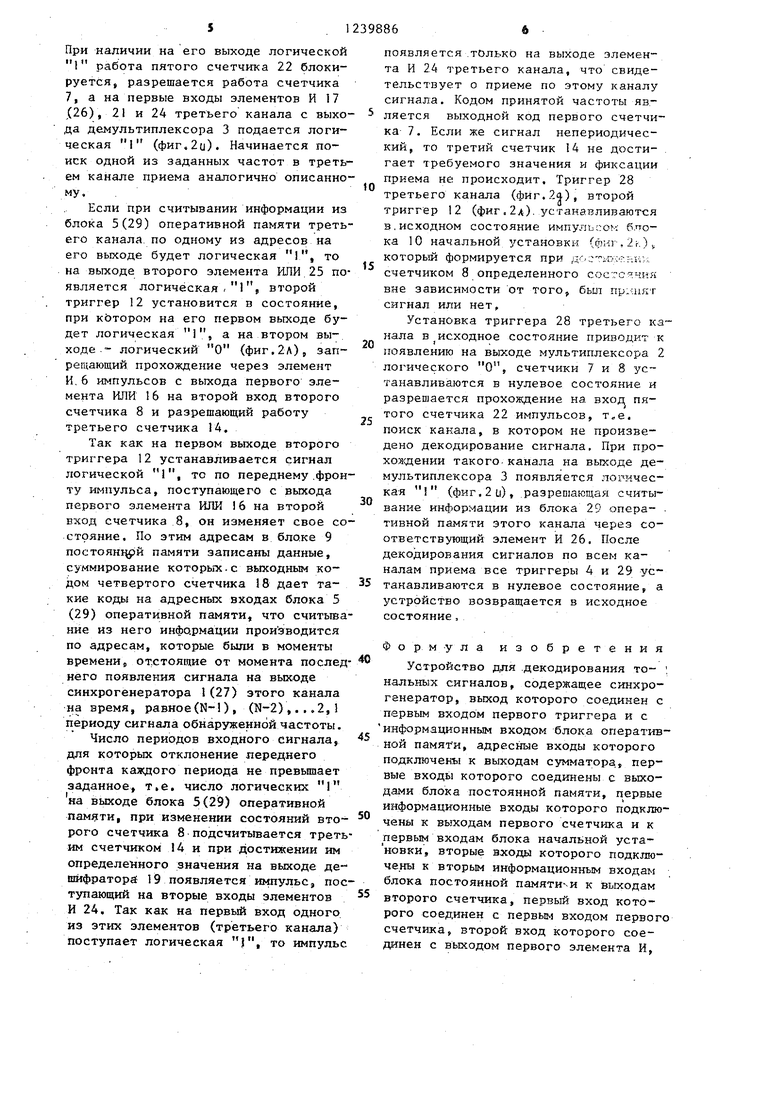

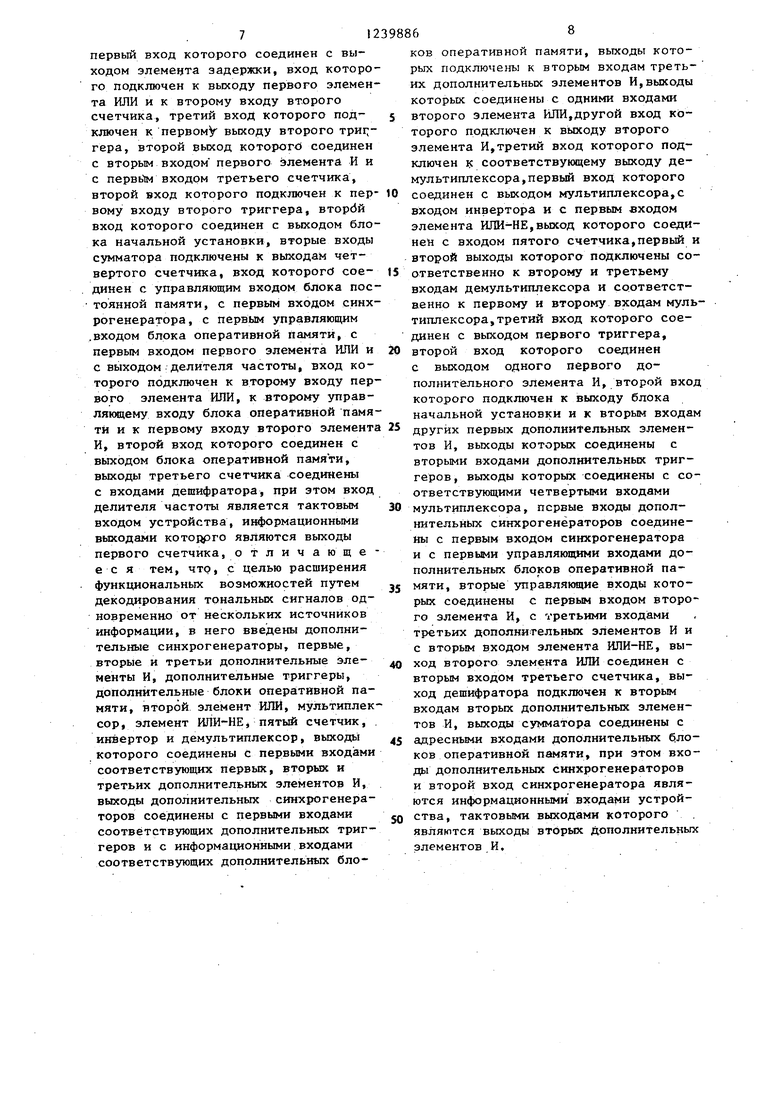

На фиг.1 изображена структурная электрическая схема предлагаемого устройства; на фиг. 2 - диаграммы, пояснякицие работу устройства.

Устройство для декодирования тональных сигналов содержит сйнхроге- нератор 1, мультиплексор 2., дамульти- плексор 3, первый триггер 4, блок 5 оперативной памяти, первый элемент И 6, первый и второй счетчики 7 и 8, блок 9 постоянной памяти, блок 10 начальной установки, элемент ИЛИ-НЕ II, второй триггер 12, сумматор 13, третий счетчик 1А, делитель 15 частоты, первый элемент ИЛИ 16, второй элемент И 17, четвертый счетчик 18, дешифратор 19, элемент 20 задержки,, первые дополнительные, элементы И 21, пятый счетчик 22, инвертор 23, вторые дополнительные элементы И 24, , второй элемент ИЛИ 25, третьи допол- нительные элементы И 26, дополнительные синхрогенераторы 27, дополнительные триггеры 28, дополнительные блоки 29 оперативной памяти.

Устройство работает следующим образом.

В исходном состоянии на выходках триггеров 4 и 28, а следовательно, на выходе мультиплексора 2 и выходах демультиплексора 3 будет логический О, на втором выходе второго тригII I и

гера 12 - логическая 1, счетчики 7, 8 и 14 установлены в нулевое состояние. Так как на выходах демуль- 5 типлексора 3 логический О, то на выходах элементов И 17 и 26 будет логический О. На третьем входе второго счетчика 8 (входе разрешения счета) будет логический О, поэтому работа этого счетчика блокируется даже при подаче логического О на его первый вход (R-вход). Выходным сигналом делителя 15 частоты

при логической j на выходе делителя 15 частоты блоки 5 и 29 оперативной памяти переводятся в режим записи, при логическом О - в режим счи

5 тывания информации, причем для осуществления записи и считывания необ- ходимо на вторые управляющие входы блоков 5 и 29 оперативной памяти подать логический О. Адреса записи

10 и считывания блоков 5 и 29 оперативной памяти задаются по их адресным входам выходным сигналом сумматора 13, На входы первого и второго счетчиков 7 и 9 сигнал от источника так15 тового сигнала (фиг.2а) поступает соответственно с выхода элемента И 6 и первого элемента ИЛИ 16, причем . при работе блоков 5 и 29 оперативной памяти в режиме записи информации

20 тактовые импульсы на счетные входы счетчиков 7 и 8 не поступают, так как в течение всего этого времени на первом входе элемента ИЛИ 16 будет логическая 1.

25 Изменение состояний первого и вто рого счетчиков 7 и 8 происходит по переднему фронту сигналов на их вто- рьк входах при подаче логического О на их первые входы (для перейо30 да счетчика 8 в режим счета импульсо необходимо подать еще на его третий вход логическую ). Так как на выходе мультиплексора 2 логический OV то через элемент ИЛИ-НЕ 11 на счетный вход счетчика 22 от источника тактового сигнала поступают импульсы Выходы счетчика 2 подключены к (адресным) входам мультиплексора 2 и де мультиплексора 3. Пятый счетчик 22 п

40 переднему фронту импульсов, поступа- кяцих на его вход (фиг.2е), изменяет свое состояние, в результате чего к выходу мультиплексора 2 последова- тельно подключаются выходы триггеров

4 и 28 всех каналов.приема.

Входные каналы от каждого из источников подаются на входы синхроге- нераторов 1 и 27 своих каналов. На выходах синхрогенераторов 1 и 27 по 50 переднему фронту входного сигнала формируется импульс, передний фронт которого совпадает с передним фронтом выходного сигнала делителя 15 частоты,, Выходные импульсы синхроге35

(фиг.2), частота которого значитель- 55 нераторов 1 и 27 каЗсдого из каналов но больше частот, принимаемых устрой- приема поступают на информационные ством сигналов, управляется работа блоков 5 и 29.оперативной памяти:

входы соответствующих оперативных блоков. 5 к 29 памяти, в результате

5

при логической j на выходе делителя 15 частоты блоки 5 и 29 оперативной памяти переводятся в режим записи, при логическом О - в режим счи5 тывания информации, причем для осуществления записи и считывания необ- ходимо на вторые управляющие входы блоков 5 и 29 оперативной памяти подать логический О. Адреса записи

0 и считывания блоков 5 и 29 оперативной памяти задаются по их адресным входам выходным сигналом сумматора 13, На входы первого и второго счетчиков 7 и 9 сигнал от источника так5 тового сигнала (фиг.2а) поступает соответственно с выхода элемента И 6 и первого элемента ИЛИ 16, причем . при работе блоков 5 и 29 оперативной памяти в режиме записи информации

20 тактовые импульсы на счетные входы счетчиков 7 и 8 не поступают, так как в течение всего этого времени на первом входе элемента ИЛИ 16 будет логическая 1.

25 Изменение состояний первого и второго счетчиков 7 и 8 происходит по переднему фронту сигналов на их вто- рьк входах при подаче логического О на их первые входы (для перейо30 да счетчика 8 в режим счета импульсов необходимо подать еще на его третий вход логическую ). Так как на выходе мультиплексора 2 логический OV то через элемент ИЛИ-НЕ 11 на счетный вход счетчика 22 от источника тактового сигнала поступают импульсы. Выходы счетчика 2 подключены к (адресным) входам мультиплексора 2 и демультиплексора 3. Пятый счетчик 22 по

40 переднему фронту импульсов, поступа- кяцих на его вход (фиг.2е), изменяет свое состояние, в результате чего к выходу мультиплексора 2 последова- . тельно подключаются выходы триггеров

4 и 28 всех каналов.приема.

,

Входные каналы от каждого из источников подаются на входы синхроге- нераторов 1 и 27 своих каналов. На выходах синхрогенераторов 1 и 27 по 50 переднему фронту входного сигнала формируется импульс, передний фронт которого совпадает с передним фронтом выходного сигнала делителя 15 частоты,, Выходные импульсы синхроге35

нераторов 1 и 27 каЗсдого из каналов приема поступают на информационные

входы соответствующих оперативных блоков. 5 к 29 памяти, в результате

чего в них записываются логические 1, Адрес ячейки оперативных блоков 5 и 29 памяти, в которую записьшает- ся информация, определяется суммой двух двоичных чисел: выходного кода четвертого счетчика 18 и выходного кода блока 9 постоянной памяти. Суммирование кодов осуществляется сумматором 13. При записи информации в блоки 5 .и 29 оперативной памяти на управляющем входе блока 9 постоянной памяти будет логическая , последний отключается и на его выходе будут сигналы, не зависящие от адресов на его информационных входах.

В случае одновременного появления сигналов на входах всех каналов приема на выходах синхрогенераторов 1 .и 27 формируются импульсы, устанавливающие триггеры 4 и 28 8 состояние, при котором на их выходах будут сигналы логической } (фиг. 26, Z ,а)

В зависимости от состояния в данный момент пятого счетчика 22 к выходу мультиплексора 2 подключается выход одного из триггеров 4 и 28. Предположим, что в момент установки первых триггеров 4 и 28 в состояние логической. I пятый счетчик 22 находится в состоянии, при котором к выходу мультиплексора 2 подключается выход триггера 28 второго канала приема. ,При этом на выходе мультиплексора 2 появляется логическая i, на выходе элемента РШИ-НЕ П. (фиг.2е) и инвер- тора 23 - логический О, что приводит к остановке пятого счетчика 22 и разрешению работы счетчика 7. Одновременно на втором выходе демульти- плексора 3 появляется логическая (фиг,2О, поступающая на первые входы элементов И 17(26), 21 и 24 второго канала приема. Таким образом, при обнаружении на выходе одного из триг геров 4 и 28 логической блокиру- ется пятый счетчик 22, т.е. происходит остано вка опроса каналов приема и начинается обработка сигнала одног из каналов.

При появлении логичеркого О на выходе делителя 15 частоты блок 5 оперативной памяти переводится в режим считывания, к входам сумматора 13 подключается блок 9 постоянной памяти, на выходе которого будет информация из ячеек памяти, адрес которых задается выходными кодами счетчиков 7 и 8. В блоке 9 постоянной памяти

398864

по этому адресу записана информация, суммирование которой с выходным кодом счетчика 18 дает адрес блока 5 (29) оперативной памяти, по которому 5 производилась запись информации ранее на время, равное N периодам первого из принимаемь1х устройством сигналов .заданной частоты. Если в тот момент сигнала на выходе синхрогенератора 27

10 второго канала не было, по этому адресу блока 5(29) оперативной- памяти этого канала будет записан логический О, на выходе элемента И 17(26) этого -канала и второго триггера 12

15 состояние не изменяется (на вьпсодах элементов И 6 и 29 остальных каналов логической 1 быть не может, так как на их первые входы с выходов демуль- типлексора 3 подается логический

20 О) и при появлении с выхода элемента И 6 на втором входе счетчика 7 логической 1 он переходит в состоякие 0001, изменяя адрес блока 9 постоянной памяти. По данному адресу в блоке 9 постоянной памяти хранятся длнные, суммирование которых с кодом четвертого счетчика 18 дает новый адрес с-читывания для блока 5,(29) оперативной памяти, т.е. устройство перестраивается на прием второй частоты. Если ни одна из частот, на прием которых настроено устройство, не будет обнаружена, что соответствует установке счетчика 7 в определенное состояние, то при этом на выходе блока 10 начальной установки формируется логическая 1 (фиг.2к). Этот сигнал поступает на вторые входы элементов И 21, на первых входах которых логический О (за исключением элемента И 21 второго канала). На вы- . ходе И 21 второго канала появляется логическая 1, триггер 28 этого канала устанавливается в состояние логического О (фиг. 2 2), на выходе мультиплексора 2 появляется логический О, на выходе инвертора 23 - логическая 1, устанавливающая счетчик 7 в нулевое состояние. Так как на первом входе элемента ИЛИ-НЕ I1 будет логический О, то при появлении на его втором входе логического О с тактового вхЬда устройства (фиг.2а) на входе пятого счетчика 22 будет логическая 1 (фиг.2й), состояние счетчика изменяется и к выходу мультиплексора 2 подключается выход триггера 28 третьего канала.

При наличии на его выходе логической 1 работа пятого счетчика 22 блокируется, разрешается работа счетчика 7, а на первые входы элементов И 17 .(26), 21 и 24 третьего канала с выхода демультиплексора 3 подается логическая 1 (фиг.2и). Начинается поиск одной из заданных частот в третьем канале приема аналогично описанному. ,

Если при считывании информации из блока 5(29) оперативной памяти третьего канала по одному из адресов на его выходе будет логическая 1, то на выходе второго элемента ИЛИ 25 появляется логическая (, второй триггер 12 установится в состояние, при котором на его первом выходе будет логическая I, а на втором выходе.- логический О (фиг,2л)5 запрещающий прохождение через элемент И,6 импульсов с выхода первого элемента ИЛИ 16 на второй вход второго счетчика 8 и разрешающий работу третьего счетчика 14,

Так как на первом выходе второго триггера 12 устанавливается сигнал логической 1, то по переднему .фронту импульса, поступающего с выхода первого элемента ИЛИ 6 на второй вход счетчика 8, он изменяет свое состояние. По этим адресам в блоке 9 постоянцрй памяти записаны данные, суммирование которых-с выходным кодом четвертого счетчика 18 дает такие коды на адресных входах блока 5 (29) оперативной памяти, что считьгеа ние из него инфармации прои зводится по адресам, которые были в моменты времениS от.стоящие от момента последнего появления сигнала на выходе синхрогенератора 1(27) этого канала на время, равное(N-i), (N-2),,.,2,l периоду сигнала обнаруженной частоты. Число периодов входного сигнала, для которых отклонение переднего фронта каждого периода не превышает заданное, т.е. число логических I на выходе блока 5(29) оперативной памяти, при изменении состояний второго счетчика 8 подсчитывается третьим счетчиком 14 и при достижении им определенного значения на выходе де- шйфраторй 19 появляется импульс, поступающий на вторые входы элементов И 24. Так как на первый вход одного из этих элементов (третьего канала) поступает логическая J, то импульс

o

5

0

5

0

появляется .только на выходе элемента И 24 третьего канала, что свидетельствует о приеме по этому каналу сигнала. Кодом принятой частоты яв.- ляется выходной код первого счетчика- 7. Если же сигнал непериодический, то третий счетчик 14 не дости- . гает требуемого значения и фиксации приема не происходит. Триггер 28 третьего канала (фиг,2а), второй триггер 12 (фиг,2л). устанавливаются в.исходном состояние импульсом блока 10 начальной установки (фиг, 2 к),; которьм формируется при дг .::.:-.тis-;:.;. счетчиком 8 определенного сосгс :чня вне зависимости от того, был .акт сигнал или нет,

Установка триггера 28 третьего канала в исходное состояние приводит к появлению на выходе мультиплексора 2 логического О, счетчики 7 и 8 устанавливаются в нулевое состояние и разрешается прохождение на вхо пятого счетчика 22 импульсов, т,е. поиск канала, в котором не произведено декодирование сигнала. При про- хо.ждении такого, канала на выходе демультиплексора 3 появляется лО1- ичес- кая (фиг,2 и), .разрешающая считывание информации из блока 29 опера- . тинной памяти этого канала через соответствующий элемент И 26, После декодирования сигналов по всем каналам приема все триггеры 4 и 29 ус- танавливаются в нулевое состояние, а устройство возвращается в исходное состояние,

Фор. мула изобретения

Устройство ДД1Я .декодирования то- ;

нальных сигналов, содержащее синхро- ггнератор, выход которого соединен с первым входом первого триггера и с информационным входом блока оперативной памяти, адресные входы которого подключены к выходам сумматора,, первые входь которого соединены с выходами блока постоянной памяти, первые информационные входы которого подключены к выходам первого счетчика и к первым входам блока начальной уста- новки, вторые входы которого подклю- че.ны к вторым информационным входам блока постоянной памятн -и к выходам 5 второго счетчика, первый вход которого соединен с первым входом первого счетчика, второй вход которого соединен с выходом первого элемента И,

5

0

10

ts

20

25

71239886

первый вход которого соединен с выходом элемента задержки, вход которого подключен к выходу первого элемента ИЛИ и к второму входу второго счетчика, третий вход которого подключен к первому выходу второго триг;- гера, второй вьгход которого соединен с вторым входом первого элемента И и с первьЧм входом третьего счетчика, второй вход которого подключен к первому входу второго триггера, вторбй вход которого соединен с выходом блока начальной установки, вторые входы сумматора подключены к выходам четвертого счетчика, вход KOTOpord соединен с управляющим входом блока постоянной памяти, с первым входом синх- рогенератора, с первым управляющим

входом блока оперативной памяти, с первым входом первого элемента ИЛИ и с выходом делителя частоты, вход которого подключен к второму входу первого элемента ИЛИ, к второму управляющему входу блока оперативной памяти и к первому входу второго элемента И, второй вход которого соединен с выходом блока оперативной памяти, выходы третьего счетчика соединены с входами дешифратора, при этом вход делителя частоты является тактовым входом устройства, информационными выходами которрго являются выходы первого счетчика, отличающееся тем, чтр, с целью расширения функциональных возможностей путем декодирования тональных сигналов одновременно от нескольких источников информации, в него введены дополнительные синхрогенераторы, первые, вторые и третьи дополнительные элементы И, дополнительные триггеры, дополнительные блоки оперативной памяти, второй элемент ИЛИ, мультиплексор, элемент ИЛИ-НЕ, пятый счетчик, инвертор и демультиплексор, выходы которого соединены с первыми входами соответствующих первых, вторых и третьих дополнительных элементов И, выходы дополнительных синхрогенера- торов соединены с первыми входами соответствующих дополнительных триггеров и с информационными входами соответствующих дополнительных бло30

35

40

45

50

ко ры их ко вт то эл кл му со вх эл не вт от вх ве ти ди вт с по ко на др то вт ге от му ни ны и по мя ры го тр с хо вт хо вх то ад ко ды и ют ст яв эл

0

s

0

5

9886

0

5

0

5

0

8

ков оперативной памяти, выходы которых подключены к вторым входам треть- их дополнительных элементов И,выходы которых: соединены с одними входами второго элемента ИЛИ,другой вход которого подключен к выходу второго элемента И,третий вход которого подключен If соответствующему выходу де- мультиплексора,первый вход которого соединен с выходом мультиплексора,с входом инвертора и с первым входом элемента ИЛИ-НЕ,выход которого соединен с входом пятого счетчика,первый и второй выходы которого подключены соответственно к второму и третьему входам демультиплексора и соответственно к первому и второму входам мультиплексора, третий вход которого соединен с выходом первого триггера, второй вход которого соединен с выходом одного первого дополнительного элемента И, второй вход которого подключен к выходу блока начальной установки и к вторым входам других первых дополнительных элементов И, выходы которых соединены с вторыми входами дополнительньк триггеров , выходы которых соединены с соответствующими четвертыми входами мультиплексора, первые входы дополнительньк синхрогенёраторов соединены с первым входом синхрогенератора и с первыми управляющими входами дополнительных блоков оперативной памяти, вторые управляющие входы которых соединены с первым входом второго элемента И, с третьими входами третьих дополнительных элементов И и с вторым входом элемента ИЛИ-НЕ, выход второго элемента ИЛИ соединен с вторым входом третьего счетчика, выход дешифратора подключен к вторым входам вторых дополнительных элементов И, выходы сумматора соединены с адресными входами дополнительиых блоков оперативной памяти, при этом входы дополнительных синхрогенёраторов и второй вход синхрогенератора являются информационными входами устройства, тактовыми выходами которого являются выходы вторых Дополнительных элементов И,

Л1

6.J

9

n

1

I I

I-I

.2

Редактор A,,Сабо

Составителг,. О, Пупшер

Техред О.Сопко Корректор Е.ощко

Заказ 34И/58Тираж 624 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

JL

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство декодирования тональных сигналов | 1986 |

|

SU1327327A2 |

| Устройство декодирования тональных сигналов | 1985 |

|

SU1277433A2 |

| Устройство декодирования тональных сигналов | 1988 |

|

SU1529473A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Устройство для выбора заданного числа повторений двоичных чисел | 1984 |

|

SU1267402A1 |

| Устройство для сигнализации | 1987 |

|

SU1429147A1 |

| Устройство для сигнализации | 1988 |

|

SU1693620A1 |

| Устройство для сигнализации | 1985 |

|

SU1278913A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1441452A1 |

| Устройство контроля качества датчиков времени | 1986 |

|

SU1422218A1 |

Изобретение относится к радиотехнике. Расширяются функциональные возможности путем декодирования тональных сигналов одновременно от нескольких источников информации. Уст-во содержит синхрог-р (СГ) 1, мультиплексор 2, триггер (Т) 4 12, блок оперативной памяти (БОП) 5,. эл-ты И 6 и 17, счетчики 7, 8, 14 и 18, блок постоянной памяти 9, блок начальной , сумматор 13, делитель частоты 15, эл-т ИЛИ 16, дешифратор 19, эл-т задержки 20. Цель достигается введением СГ 27, эл-тов И 21, 24 и 26, Т 28, БОП 29, эл-та ИЛИ 25, муль- типлексор 2, эл-та ИЛИ-НЕ 11, счетчика 22, инвертора 23, демультшшек- сора 3. 2 ил. с и

| Патент США № 4142177, кл | |||

| , опублик | |||

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Авторское свидетельство СССР № 1160614, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-06-23—Публикация

1984-10-24—Подача