выходе синхрогенератора 3, разделенных интервалом времени, равным N периодам принимаемой частоты. Окончательное решение о том, что принят

сигнал соответствующей частоты, принимается после проверки отклонения каждого периода сигнала от номинального значения. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования тональных сигналов | 1984 |

|

SU1239886A1 |

| Устройство декодирования тональных сигналов | 1986 |

|

SU1327327A2 |

| Устройство декодирования тональных сигналов | 1988 |

|

SU1529473A1 |

| Устройство декодирования тональных сигналов | 1988 |

|

SU1570034A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Стереотелевизионная камера с автоматической фокусировкой | 1989 |

|

SU1774518A1 |

| Устройство для выбора заданного числа повторений двоичных чисел | 1984 |

|

SU1267402A1 |

| Цифровой компандер | 1986 |

|

SU1427575A1 |

| Спироанализатор | 1986 |

|

SU1391621A1 |

| Устройство для отображения информации на экране цветного видеоконтрольного блока | 1988 |

|

SU1529280A1 |

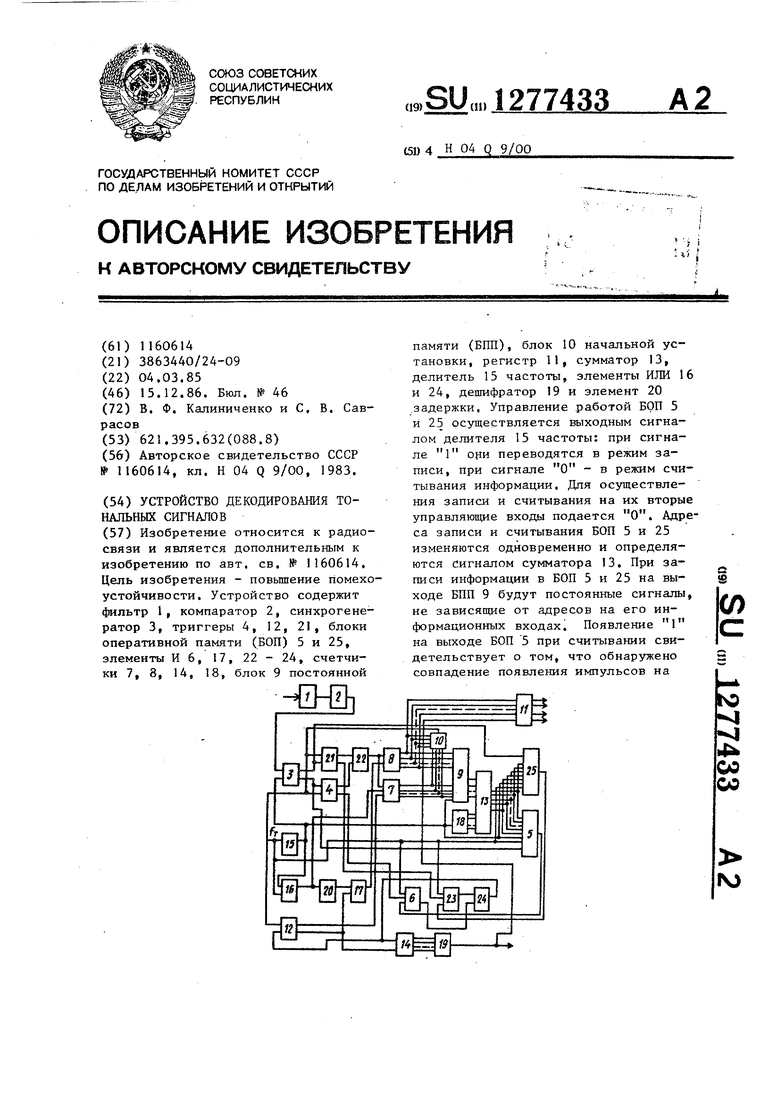

Изобретение относится к радиосвязи и является дополнительным к изобретению по авт. св. № 1160614. Цель изобретения - повьшение помехоустойчивости. Устройство содержит фильтр 1, компаратор 2, синхрогенератор 3, триггеры 4, 12, 21, блоки оперативной памяти (БОП) 5 и 25, элементы И 6, 17, 22 - 24, счетчики 7, 8, 14, 18, блок 9 постоянной памяти (БПП), блок 10 начальной установки, регистр 11, сумматор 13, делитель 15 частоты, элементы ИЛИ 16 и 24, дешифратор 19 и элемент 20 задержки. Управление работой БОП 5 и 25 осуществляется выходным сигналом делителя 15 частоты: при сигнале 1 они переводятся в режим записи, при сигнале О - в режим считывания информации. Для осуществления записи и считывания на их вторые управляющие входы подается О. Адреса записи и считывания БОП 5 и 25 изменяются одновременно и определяются сигналом сумматора 13. При записи информации в БОП 5 и 25 на вы(О ходе БПП 9 будут постоянные сигналы, (Л не зависящие от адресов на его информационных входах. Появление 1 на выходе БОП 5 при считывании свидетельствует о том, что обнаружено совпадение появления импульсов на ю со 00 14)

«

Изобретение относится к радиосвя аи и гложет быть использовано в устройствах для приема тональных сигналов нескольких заданных частот, в .частности, для приема данных, передаваемых последовательным частотным кодом.

Цель изобретения - повышение помехоустойчивости.

На чертеже представлена структурная схема устройства.

Устройство декодирования тональных сигналов содержит фильтр 1, компаратор 2, синхрогенератор 3, ,первый триггер 4, первый блок 5 оперативной памяти, первый элемент И 6, первый счетчик 7, второй счетчик 8, блок 9 постоянной памяти, блок 10 начальной установки, регистр 11, второй триггер 12, сумматор 13, третий счетчик 14, делитель 15 частоты, первый элемент ИЛИ 16, второй элемент И 17, четвертый счетчик 18, дешифратор 19, элемент 20 задержки, третий триггер 21, третий элемент И 22,четвертый элемент И 23, второй элемент ИЛИ 24 и второй блок 25 оперативной памяти.

Устройство декодирования тональных сигналов работает следующим образом.

В исходном состоянии на вторых выводах первого, второго и третьего триггеров 4, 12, 21 присутствует логическая 1, на вьпсоде третьего элемента И 22 - логическая 1. Первый, второй и третий счетчики 7, 8, 14 установлены в нулевое состояние. На выходах первого и четвертого элементов И 6 и 23 присутствует О. Выходным сигналом делителя 15 частоты управляется работа блоков 5 и 25 оперативной памяти,,При логической 1 на выходе делителя 15 первьй и второй блоки 5 и 25 оперативной памяти переводятся в режим записи, при О - в режим считывания информации, причем для осуществления записи и считывания необходимо на вторые управляющие входы блоков 5 и 25 оперативной памяти подать логический О. Адресу записи и считывания блоков 5 и 25 оперативной памяти изменяются одновременно и определяются выходным сигналом сумматора 13. При записи информации в блоки 5 и 25 оперативной памяти на выходе блока 9 постоянной памяти постоянные сигналы, не зависящие от

с адресов на его информационных входах.

На выходе сиихрогенератора 3 по переднему фронту входного сигнала формируется импульс, передний фронт

0 которого совпадает с передним фронтом выходного сигнала делителя 15 частоты. Выходной импульс синхрогенератора 3 поступает на информационный вход блока 5 оперативной памяти,

5 в результате чего в- него записывается 1. Адрес ячейки оперативного блока 5 памяти, в которую записывается информация, определяется суммой выходного кода четвертого счет0 чика 18 и выходного кода блока 9

постоянной памяти. По этому же адресу во второй блок 25 оперативной памяти записывается О, так как в это время на дополнительном выходе

5 синхрогенератора 3 будет О,

Одновременно выходным сигналом синхрогенератора 3 первый триггер 4 устанавливается в состояние, при 0 котором на его первом выходе 1, а .на втором - О, в результате чего на выходе третьего элемента И 22 появляется О, разрешающий работу второго счетчика 8 (для перевода первого счетчика 7 в режим счета

необходимо на его третий вход подать 1).

При появлении О на выходе делителя 15-частоты блоки 5 и 25 оперативной памяти переводятся в режим считывания, к входам сумматора 13 подключается блок 9 постоянной па. мяти, на выходе которого-будет информация из ячеек памяти, адрес которых задается выходными кодами первого и второго счетчиков 7 и 8.

На второй вход третьего счетчика 14 и первый вход второго триггера 12 информация через второй элемент ИЛИ 24 поступает только из блока 5 оперативной памяти. Это обусловлено тем, что на первом входе четвертого элемента И 23 - логический О, Независимо от выходной информации второго блока 25 оперативной памяти на выходе четвертого элемента И 23 будет О.

В блоке 9 постоянной памяти по адресу 00000, задаваемому в исходном состоянии выходными кодами первого и второго счетчиков 7 и 8, записана информация, суммирование которой с выходным кодом четвертого счетчика 18 дает адрес блока 5 оперативной памяти, по которому ранее производилась запись информации на время, равное N периодам первого из принимаемых устройством сигналов ладанной частоты. Если в тот момент /:игнала на выходе синхрогенератора 3 не бьшо, по этому адресу в блоке 5 оперативной памяти записан О, На выходе первого элемента И 6, второго элемента ИЛИ 24 и второго триггера 12 значение не изменяется. При появлении с выхода второго элемента И 17 на втором входе второго счетчика В логической 1 он перейдет в состояние 0001 , изменяя адрес блока 9 постоянной памяти. По данному адресу в блоке 9 постоянной памяти хранятся данные, суммирование которых с кодом четвертого счетчика 18 дает новый адрес считывания для блока 5 оперативной памяти, т.е. устройство декодирования перестраивается на прием второй частоты. Если и по этому адресу в блоке 5 оперативной памяти ранее был з аписан логический О, т.е. и эта частота не обнаружена, то второй счетчик б переходит в состояние 0010, что соответствует настройке устройства на

прием третьей частоты. Если ни одна из частот, на прием которых настроено устройство, не обнаружена, что соответствует установке второ5 го счетчика 8 в определенное состояние, то на выходе блока 10 начальной установки формируется логическая 1, устанавливающая второй счетчик 8 и первый триггер 4 в исходное со0стояние.

Если же при считывании информации из блока 5 оперативной памяти по одному из адресов на его выходе будет логическая 1, то на выходе первого элемента И 6, а следовательно, на выходе второго элемента ИЛИ 24, появляется логическая 1. Второй триггер 12 устанавливается в состояние, при котором на его первом выхо де - логическая 1, а на втором выходе - логический О, запрещающий прохождение через второй элемент И 17 импульсов с выхода элемента ИЛИ 16 на второй вход второго счетчика 8 и разрешающий работу третьего счетчика 14. В результате фиксируется выходной код второго счетчика 8, а так как на г1ервом выходе iвторого триггера 12 - логическая

0 то разрешается работа первого. счетчика 7.

Появление логической 1 на выходе блока 5 оперативной памяти

- свидетельствует о том, что обнаружено совпадение (с точностью до периода выходной частоты делителя 15) моментов появления импульсов на выходе синхрогенератора 3, разделенных интервалом времени, равным N периодам Ъднойиз принимаемых устройством час-, тот. Выходной код второго счетчтка 8 является при этом кодом обнаруженной частоты.

- Окончательное решение о том, что принят сигнал соответствующей частоты, принимается после проверки отклонения каждого периода сигнала от .номинального значения, что осуществляется следующим образом.

Так как на первом выходе второго триггера 2 устанавливается сигнал логической 1, то по переднему фронту импульса, поступающего с выхода первого элемента ИЛИ 16 на второй вход первого счетчика 7, он будет лзменять свое состояние, что вызывает изменение адресов блока 9 постоянной памяти. По этим адресам в

| Авторское свидетельство СССР № 1160614, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-12-15—Публикация

1985-03-04—Подача