Изобретение относится к электротехнике, а именно к электроприводам, и может быть использовано для повышения точности стабилизации скорости вращения электроприводов постоянного тока.

Цель изобретения - повьшение точ- нос;ти стабилизации скорости электро- при вода постоянного тока.

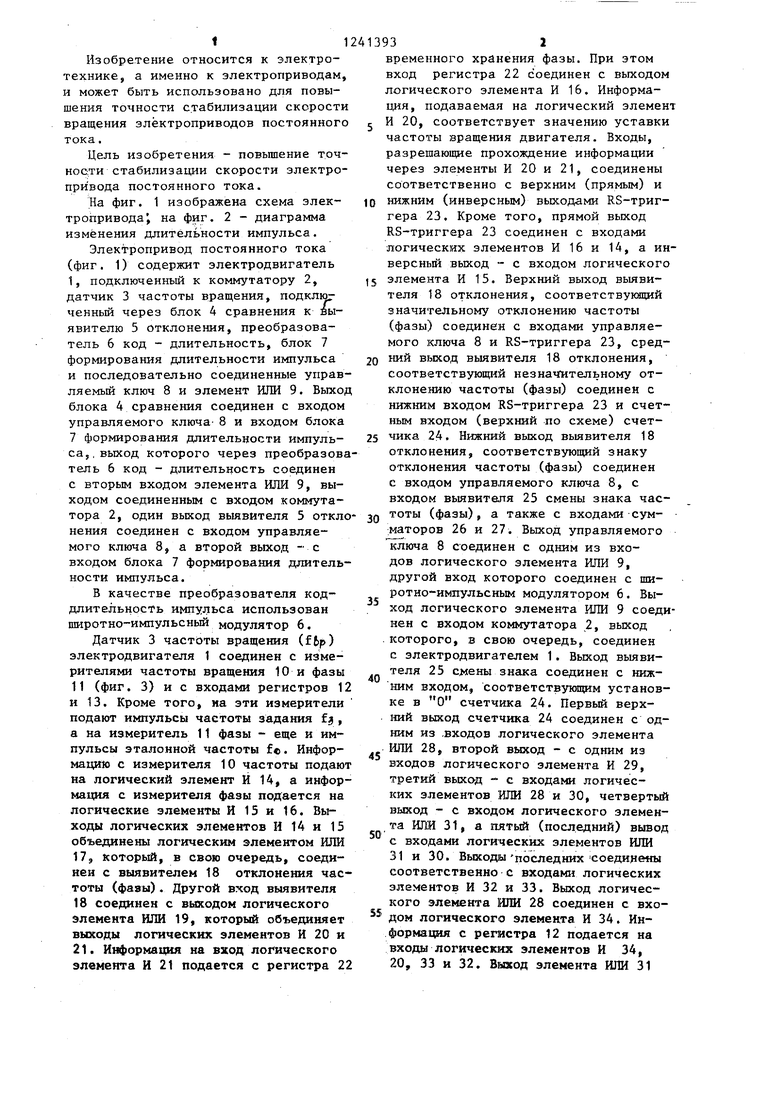

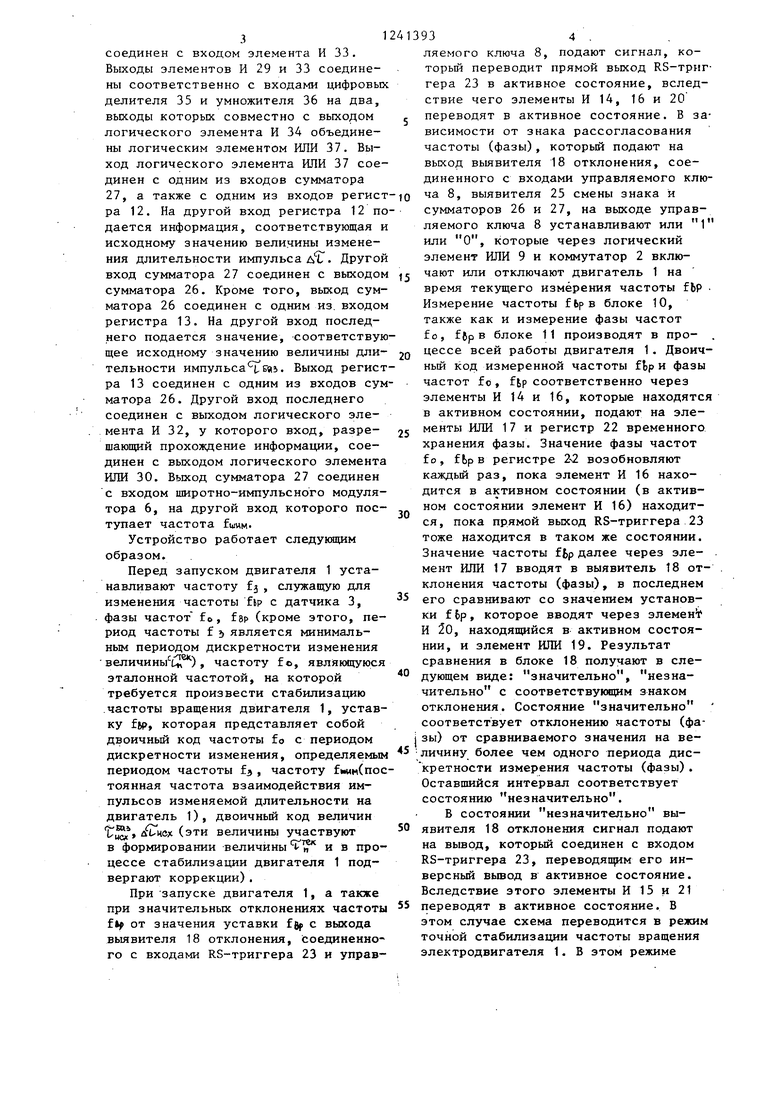

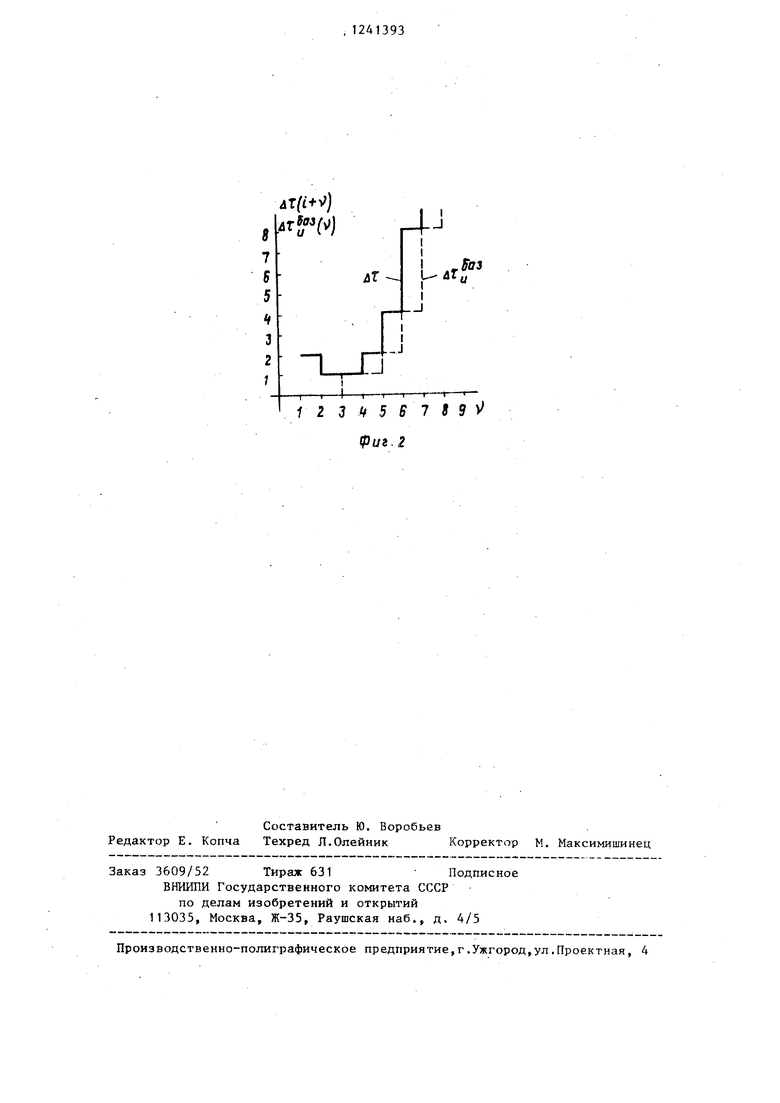

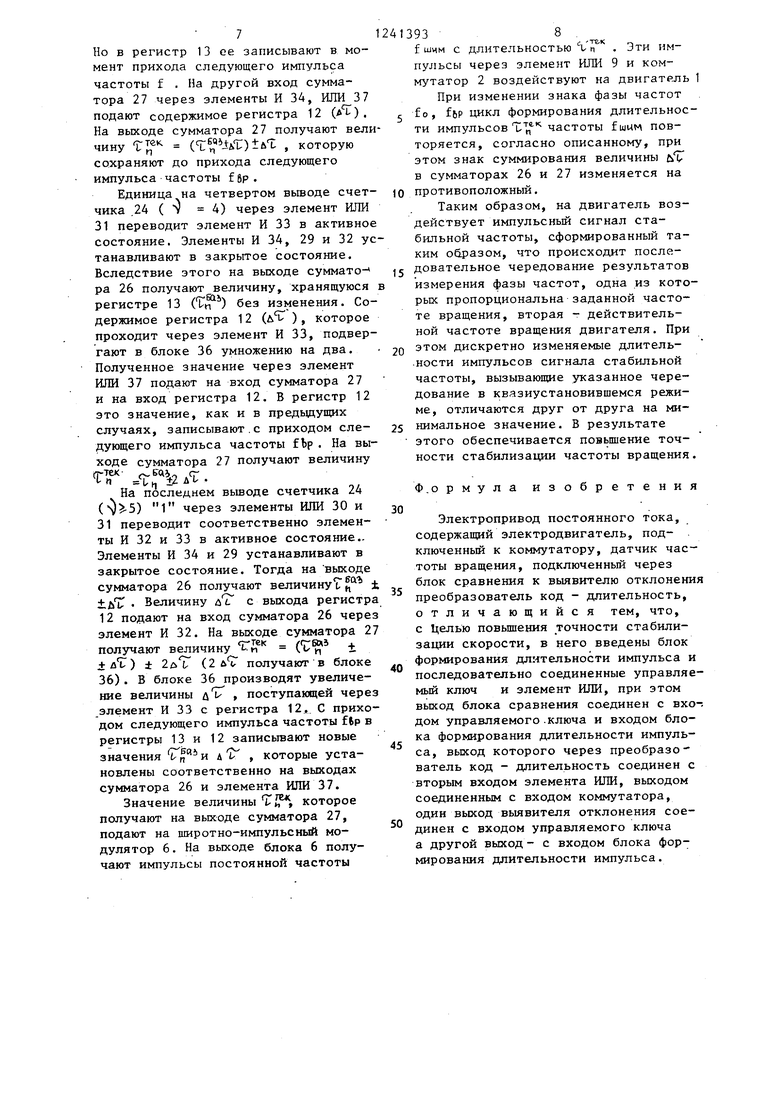

На фиг. 1 изображена схема электропривода , на фиг. 2 - диаграмма изменения длительности импульса.

Электропривод постоянного тока (фиг. 1) содержит электродвигатель 1, подключенньй к коммутатору 2, датчик 3 частоты вращения, подклюг ченный через блок 4 сравнения к выявителю 5 отклонения, преобразователь 6 код - длительность, блок 7 формирования длительности импульса и последовательно соединенные управляемый ключ 8 и элемент ИЛИ 9. Выход блока 4 сравнения соединен с входом управляемого ключа- 8 и входом блока 7 формирования длительности импульса,, выход которого через преобразователь 6 код - длительность соединен с вторым входом элемента ИЛИ 9, выходом соединенным с входом коммутатора 2, один выход выявителя 5 отклонения соединен с входом управляемого ключа 8, а второй выход - с входом блока 7 формирования длительности импульса.

В качестве преобразователя код- длительность импульса использован широтно-импульсный модулятор 6.

Датчик 3 частоты вращения (ftp) электродвигателя 1 соединен с измерителями частоты вращения 10 и фазы 11 (фиг. 3) и с входами регистров 12 и 13. Кроме того, на эти измерители подают импульсы частоты задания fj, а на измеритель 11 фазы - еще и импульсы эталонной частоты «. Информацию с измерителя 10 частоты подают на логический элемент И 14, а информация с измерителя фазы подается на логические элементы И 15 и 16. Выходы логических элементов И 14 и 15 объединены логическим элементом ИЛИ I, который, в свою очередь, соединен с выявителем 18 отклонения частоты (фазы). Другой вход выявителя 18 соединен с выходом логического элемента ШШ 19, который объединяет выходы логических элементов И 20 и 21. Информация на вход логического элемента И 21 подается с регистра 22

5

0

5

0

5

0

5

50

55

временного хранения фазы. При этом вход регистра 22 соединен с выходом логического элемента И 16. Информация, подаваемая на логический элемент И 20, соответствует значению уставки частоты вращения двигателя. Входы, разрешающие прохождение информации через элементы И 20 и 21, соединены соответственна с верхним (прямым) и нижним (инверсным) выходами RS-триг- гера 23. Кроме того, прямой выход RS-триггера 23 соединен с входами логических элементов И 16 и 14, а инверсный выход - с входом логического элемента И 15. Верхний выход выявителя 18 отклонения, соответствукш1 1й значительному отклонению частоты (фазы) соединен с входами управляемого ключа 8 и RS-триггера 23, средний выход выявителя 18 отклонения, соответствующий незначительному отклонению частоты (фазы) соединен с нижним входом RS-триггера 23 и счетным входом (верхний по схеме) счетчика 24. Нижний выход выявителя 18 отклонения, соответствующий знаку отклонения частоты (фазы) соединен с входом управляемого ключа 8, с входом выявителя 25 смены знака частоты (фазы), а также с входами сумматоров 26 и 27. Выход управляемого ключа 8 соединен с одним из входов логического элемента ШШ 9, другой вход которого соединен с щи- ротно-имлульсным модулятором 6. Выход логического элемента ИЛИ 9 соединен с входом коммутатора 2, выход которого, в свою очередь, соединен с электродвигателем 1. Выход выявителя 25 смены знака соединен с нижним входом, соответствующим установке в О счетчика 24. Первый верхний выход счетчика 24 соединен с одним из .входов логического элемента ШШ 28, второй выход - с одним из входов логического элемента И 29, третий выход - с входами логических элементов ИПИ 28 и 30, четвертый выход - с входом логического элемен- та ИЛИ 31, а пятый (последний) вывод с входами логических элементов ИЛИ 31 и 30. Выходы последних соединены соответственно с входами логических элементов И 32 и 33. Выход логического элемента 1ЯПИ 28 соединен с входом логического элемента И 34. Информация с регистра 12 подается на входы логических элементов И 34, 20, 33 и 32. элемента ИПИ 31

12413934 .

ляемого ключа 8, подают сигнал, который переводит прямой выход RS-триг- гера 23 в активное состояние, вследствие чего элементы И 14, 16 и 20 переводят в активное состояние. В зависимости от знака рассогласования частоты (фазы), который подают на выход выявителя 18 отклонения, соединенного с входами управляемого клю- 27, а также с одним из входов регист-ю выявителя 25 смены знака и ра 12. На другой вход регистра 12 по- сумматоров 26 и 27, на выходе управ- дается информация, соответствующая и ляемого ключа В устанавливают или 1 исходному значению величины изменения длительности импульса A tT. Другой вход сумматора 27 соединен с выходом чают или отключают двигатель 1 на сумматора 26. Кроме того, выход сум- время текущего измерения частоты fbP

3

соединен с входом элемента И 33. Выходы элементов И 29 и 33 соединены соответственно с входами цифровых делителя 35 и умножителя 36 на два, выходы которых совместно с выходом логического элемента И 34 объединены логическим элементом ИЛИ 37. Выход логического элемента ИЛИ 37 соединен с одним из входов сумматора

ляемого ключа В устанавливают или или О, которые через логический элемент ИЛИ 9 и коммутатор 2 вклю

матора 26 соединен с одним из. входом регистра 13. На другой вход последнего подается значение, соответствующее исходному значению величины дли- тельности импульса йи. Выход регистра 13 соединен с одним из входов сумматора 26. Другой вход последнего соединен с выходом логического элемента И 32, у которого вход, разрешающий прохождение информации, соединен с выходом логического элемента ИЛИ 30. Выход сумматора 27 соединен с входом широтно-импульсного модулятора 6, на другой вход которого поступает частота fwnM.

Устройство работает следующим образом.

Перед запуском двигателя 1 устанавливают частоту fj , служащую для изменения частоты fip с датчика 3, фазы частот f о , fep (кроме зтого, период частоты f 5 является минимальным периодом дискретности изменения величины и) , частоту fo, являющуюся эталонной частотой, на которой требуется произвести стабилизацию .частоты вращения двигателя 1, уставку fip, которая представляет собой двоичный код частоты fo с периодом

дискретности изменения, определяемым периодом частоты f , частоту (noc- тоянная частота взаимодействия импульсов изменяемой длительности на двигатель 1), двоичный код величин йС исх (эти величины участвуют

в формировании величины - « и в процессе стабилизации двигателя 1 подвергают коррекции).

При запуске двигателя 1, а также при значительных отклонениях частоты от значения уставки f5p с выхода выявителя 18 отклонения, соединенного с входами RS-триггера 23 и управляемого ключа 8, подают сигнал, который переводит прямой выход RS-три гера 23 в активное состояние, вслед ствие чего элементы И 14, 16 и 20 переводят в активное состояние. В з висимости от знака рассогласования частоты (фазы), который подают на выход выявителя 18 отклонения, соединенного с входами управляемого кл выявителя 25 смены знака и сумматоров 26 и 27, на выходе управ ляемого ключа В устанавливают или чают или отключают двигатель 1 на время текущего измерения частоты fb

ляемого ключа В устанавливают или или О, которые через логический элемент ИЛИ 9 и коммутатор 2 вклюляемого ключа 8, подают сигнал, который переводит прямой выход RS-триг- гера 23 в активное состояние, вследствие чего элементы И 14, 16 и 20 переводят в активное состояние. В зависимости от знака рассогласования частоты (фазы), который подают на выход выявителя 18 отклонения, соединенного с входами управляемого клю- выявителя 25 смены знака и сумматоров 26 и 27, на выходе управ- ляемого ключа В устанавливают или 1 чают или отключают двигатель 1 на время текущего измерения частоты fbP

0

о

Измерение частоты fbpB блоке 10, также как и измерение фазы частот fo, f6рв блоке 11 производят в процессе всей работы двигателя 1. Двоичный код измеренной частоты ftp и фазы частот fо, ftp соответственно через элементы И 14 и 16, которые находятся в активном состоянии, подают на эле- 5 менты ИЛИ 17 и регистр 22 временного хранения фазы. Значение фазы частот f о , f Ьр в регистре 2-2 возобновляют каждый раз, пока элемент И 16 находится в активном состоянии (в активном состоянии элемент И 16) находит5

0

ся, пока прямой выход RS-триггера 23 тоже находится в таком же состоянии. Значение частоты ffcp далее через элемент ИЛИ 17 вводят в выявитель 18 отклонения частоты (фазы)« в последнем его сравнивают со значением установки fbp, которое вводят через элемент И 20, находящийся в активном состоянии, и элемент ИЛИ 19. Результат сравнения в блоке 18 получают в следующем виде: значительно, незначительно с соответствующим знаком отклонения. Состояние значительно

соответствует отклонению частоты (фа- j зы) от сравниваемого значения на ве- 5 личину более чем одного периода дис- кретности измерения частоты (фазы). Оставшийся интервал соответствует

состоянию незначительно.

вы

явителя 18 отклонения сигнал подают на вьшод, который соединен с входом RS-триггера 23, переводящим его инверсный вывод в активное состояние. Вследствие этого элементы И 15 и 21 переводят в активное состояние. В этом случае схема переводится в режим точной стабилизации частоты вращения электродвигателя 1. В этом режиме

возобновление фазы частот f, fЬр в регистре 22 прекращают. Последнее значение фазы, которое записано в регистр 22, становится значением, с которым в дальнейшем сравнивают текущее значение фазы, поданное в выявитель 18 через элементы И 15, ИЛИ 17. Содержимое регистра 22 подают в выявитель 18 через элементы И 21, ИЛИ 19 до тех пор, пока RS-триггер 23 установлен в состояние 1 на

12413936

элемент ШШ 28 устанавливает элемент И 34 в активное состояние. Элементы И 29, 33 и 32 устанавливают в закрытое состояние, так как остальные J вьтоды счетчика 24 установлены в нулевое состояние. Вследствие этого величину, хранящуюся в регистре 12, через элементы. И, ИЛИ 34 и 37 подают в сумматор 27, а также обратно

10 в регистр 12. На другой вход сумматора 27 подают величину Г , хранящуюся в регистре -13 и прошедшую через сумматор 26 без изменения, так как элемент И 32 посредством элемен15 та ШШ 30 установлен в закрытое состояние. Содержимое регистра 19 также не изменяют. На выходе сумматора 27 получают величину .Знак суммирования .или вьиитания сумматоров 26 и 27 задают блоком 18 с вьто- да соответствующим состоянию знака фазы частот f о , ftp.

1 на втором выводе счетчика 24 . ( V 2) переводит в активное состояинверсном выводе. Сигнал, которым переводят RS-триггер в инверсное состояние (1 на инверсном выводе), кроме того, подают на счетный вход счетчика 24. Счетчик 24 представляет собой счетчик числа измерений частот fо, fБр с постоянным знаком. Всякое изменение знака рассматриваемой фазы, а также смену знака отклонения частоты ffep от значения уставки ffep фиксируют выявителем 25, который, в свою очередь, предустанавливает счетчик 24 в исходное состояние (нулевое) Определенное состояние счетчика 25 ние элемент И 29. Элементы И 34, 33 24 предопределяет соответствукяцие из- и 32 устанавливают в закрытое состоя20

менения величин и , хранящихся соответственно в регистрах 13 и 12 и участвую1дих в формировании вели- . После того, как произошло JQ изменение знака фазы частот fо, ffep, на верхнем вьшоде счетчика 24 устанавливают единичный сигнал. Остальные вьшоды устанавливают в нулевое - состояние. После второго, третьего и четвертого измерений фаз, если этот знак не меняется, единичный сигнал соответственно устанавливают на втором, третьем или четвер том выводе счетчика 24. После пятого измерения знака фазы, если он не изме.нился, единичный сигнал устанавливают на нижнем вьшоде счетчика 24. 1 на этом выводе сохраняется до fex пор.

35

40

ние, как и в предвдущем случае содержимое регистра 13 () не изменяют. Содержимое регистра 12 (ь) через элемент И 29 подают на вход делителя 35 на два. Значение йТ/2 через элемент ИЛИ 37 подают на другой вход сумматора 27, где оно совместно с величиной С дает величину tn v -At72. Величина л Р , поделенная на два, с выхода элемента ШШ 37 поступает на вход регистра 12, но запит сывают ее только в момент прихода следующего импульса частоты fip. Это означает, что информацию на выходах сумматоров 26 и 27 не изменяют в интервале между и «4пульсами частоты f6p

Единица на третьем выводе счетчика 24 (У 3) посредством элементов ШШ 28 и 30 переводит в активное состояние элементы И 34 и 32. Элементы И 29 и 33 устанавливают в закрытое состояние. Тогд.а, если ранее на вход сумматора 26 с выхода элемента И 32 никакой информа:ции не подавали, то теперь на него через элемент И 32 подают содержимое регистра 12 (л),: На другой вход сумматора 26 поступа- ет содержимое регистра 13 (Tj). Тогда на выходе сумматора 26 получаем величину б f . Эту величину подают одновременно на вход сумматора 27 и на вход регистра 13.

пока не произойдет смены знака фазы частот fo , ftp. Изменение величин ft v- в интервале постоянства знака фазы поясняет фиг. 2, на которой вместо изменения Т показано изменение величиныдЯГ относительно величины л С . ВеличинайТ тличается от ,величины при текущем знаке фазы iна величину г до изменения рассматриваемого знака Фазы. Параметр - номер измерения фазы в интервале .постоянства знака фазы.

Если 1 установлена на верхнем выводе счетчика 24 что соответствует J 1 (фиг. 2), то она через

ние, как и в предвдущем случае содержимое регистра 13 () не изменяют. Содержимое регистра 12 (ь) через элемент И 29 подают на вход делителя 35 на два. Значение йТ/2 через элемент ИЛИ 37 подают на другой вход сумматора 27, где оно совместно с величиной С дает величину tn v -At72. Величина л Р , поделенная на два, с выхода элемента ШШ 37 поступает на вход регистра 12, но запит сывают ее только в момент прихода следующего импульса частоты fip. Это означает, что информацию на выходах сумматоров 26 и 27 не изменяют в интервале между и «4пульсами частоты f6p

Единица на третьем выводе счетчика 24 (У 3) посредством элементов ШШ 28 и 30 переводит в активное состояние элементы И 34 и 32. Элементы И 29 и 33 устанавливают в закрытое состояние. Тогд.а, если ранее на вход сумматора 26 с выхода элемента И 32 никакой информа:ции не подавали, то теперь на него через элемент И 32 подают содержимое регистра 12 (л),: На другой вход сумматора 26 поступа- ет содержимое регистра 13 (Tj). Тогда на выходе сумматора 26 получаем величину б f . Эту величину подают одновременно на вход сумматора 27 и на вход регистра 13.

7

Но в регистр 13 ее записывают в момент прихода следующего импульса частоты f , На другой вход сумматора 27 через элементы И 34, ИЛИ 37 подают содержимое регистра 12 (Д1-). На выходе сумматора 27 получают величину () , которую сохраняют до прихода следующего импульса частоты fep.

Единица на четвертом вьшоде счет- чика ,24 ( Y 4) через элемент ИЛИ 31 переводит элемент И 33 в активное состояние. Элементы И 34, 29 и 32 устанавливают в закрытое состояние. Вследствие этого на выходе суммато- ра 26 получают величину, хранящуюся регистре 13 (Тп) без изменения. Содержимое регистра 12 (д ) , которое проходит через элемент И 33, подвергают в блоке 36 умножению на два. Полученное значение через элемент ИЛИ 37 подают на вход сумматора 27 и на вход регистра 12. В регистр 12 это значение, как и в предьщущих случаях, записывают.с приходом еле- дующего импульса частоты fЬр. На выходе сумматора 27 получают величину

ТТ ,k лТ .

На последнем вьшоде счетчика 24

() 1 через элементы ИЛИ 30 и 31 переводит соответственно элемен- ты И 32 и 33 в активное состояние.. Элементы И 34 и 29 устанавливают в закрытое состояние. Тогда на выходе сумматора 26 получают величину ± ±lft Величину д1 с выхода регистра 12 подают на вход сумматора 26 через элемент И 32. На выходе сумматора 27 получают величину tTjip ± i дТ) ± 2лТ (2 л получают в блоке 36). В блоке 36 производят увеличение величины йП , поступающей через элемент И 33 с регистра 12, С приходом следующего импульса частоты ffcp в регистры 13 и 12 записьгеают новые значения п и д , которые установлены соответственно на выходах сумматора 26 и элемента ИЛИ 37.

Значение величины Т/, которое получают на выходе сумматора 27, подают на широтно-импульсный модулятор 6. На выходе блока 6 получают импульсы постоянной частоты

ю 5 20 25

зо

0

5

3938 .

f шчм с длительностью Vn . Эти импульсы через элемент ИЛIi 9 и коммутатор 2 воздействуют на двигатрль 1

При изменении знака фазы частот fo, fbp цикл формирования длительности импульсов частоты fujWM повторяется, согласно описанному, при этом знак суммирования величины в сумматорах 26 и 27 изменяется на противоположный.

Таким образом, на двигатель воздействует импульсный сигнал стабильной частоты, сформированный таким ойразом, что происходит последовательное чередование результатов измерения фазы частот, одна из которых пропорциональна заданной частоте вращения, вторая - действительной частоте вращения двигателя. При этом дискретно изменяемые длитель- .кости импульсов сигнала стабильной частоты, вызывающие указанное чередование в квазиустановившемся режиме, отличаются друг от друга на минимальное значение. В результате этого обеспечивается повьшгение точности стабилизации частоты вращения.

Ф.о рмула изобретения

Электропривод постоянного тока, содержащий электродвигатель, под- . ключенный к коммутатору, датчик частоты вращения, подключенньш через блок сравнения к выявителю отклонения преобразователь код - длительность, отличающийся тем, что, с Целью повьщ1ения точности стабилизации скорости, в него введены блок формирования длительности импульса и последовательно соединенные управляемый ключ и элемент ИЛИ, при этом выход блока сравнения соединен с вхо-. дом управляемого.ключа и входом блока формирования длительности импульса, выход которого через преобразователь код - длительность соединен с вторым входом элемента ИЛИ, выходом соединенным с входом коммутатора, один выход выявителя отклонения соединен с входом управляемого ключа а другой выход- с входом блока формирования длительности импульса.

1 2 3 ff 5 6 7 8 9 ) «риг.г

| название | год | авторы | номер документа |

|---|---|---|---|

| ЧАСТОТНО-ФАЗОВОЕ РЕЛЕ | 2016 |

|

RU2641096C2 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| Устройство слежения за дорожкой дискового носителя информации | 1987 |

|

SU1614031A1 |

| Устройство для отображения информации | 1982 |

|

SU1152025A1 |

| Устройство для измерения параметров вращения ротора в переходных режимах | 1983 |

|

SU1352369A1 |

| СПОСОБ РЕГУЛИРОВАНИЯ ЖИДКОСТНОГО РАКЕТНОГО ДВИГАТЕЛЯ И УСТРОЙСТВА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2085755C1 |

| ЧАСТОТНО-ФАЗОВОЕ РЕЛЕ | 2003 |

|

RU2239904C1 |

| Электрогидравлический следящий привод | 1985 |

|

SU1269092A1 |

| Устройство для формирования аналогового сигнала рассогласования | 1983 |

|

SU1104462A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

Изобретение относится к олектро- технике, а именно к электроприводу. Цель изобретения - повьшение точности стабилизации скорости вращения электропривода. Устройство содержит электродвигатель 1, коммутатор 2, датчик 3 частоты вращения, блок сравнения 4 к выявителю отклонения 5, преобразователь код - длительность 6. Введение блока формирования 7 длительности импульсов, управляемого ключа 8 и элемента ИЛИ 9 позволяет таким образом воздействовать на двигатель, что происходит последовательное чередование результатов измере ния фазы частот. Одна из фаз пропорциональна заданной частоте вращения, а другая - действительной частоте. При этом дискретно изменяемые длительности импульсов сигнала стабильной частоты, вызывакщие указанное чередование в квазиустановившемся режиме, отличаются друг от друга на минимальное значение, что обеспечивает повьшение точности. 2 ил. i (Л ND 4: СО СО СА9

| УСТРОЙСТВО ДЛЯ СТАБИЛИЗАЦИИ СКОРОСТИ ЭЛЕКТРОДВИГАТЕЛЯ ПОСТОЯННОГО ТОКА | 0 |

|

SU372631A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ стабилизации скорости электродвигателя постоянного тока | 1978 |

|

SU725179A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1986-06-30—Публикация

1983-02-24—Подача