Изобретение относится к измерительной технике и может-быть использовано для автоматического измерения частоты вращения ротора, времени и скорости выбега и запоминания максимальных отклонений частоты вращения ротора в переходных режимах, например роторов паровых, газовых и гидравлических турбин

Целью изобретения является повьше- ние точности измерения.

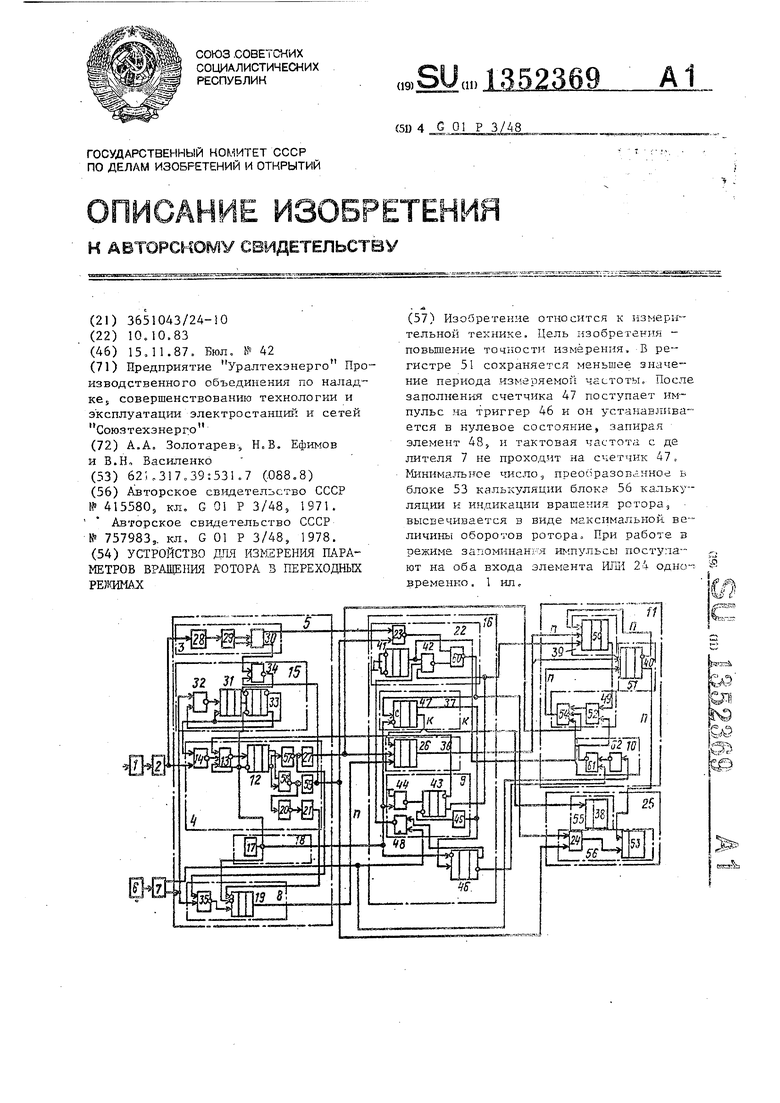

На чертеже изображена схема устройства .

Частотньй датчик 1 оборотов жестко соединен с ротором, скорость вращения которого контролируютS а выходом подключен к формирователю 2 стандар- тизировйнных импульсов5 который выходом одновременно соединен с входом блока 3 момента начала торможения и входом блока 4 задания тактовых сигналов, входящего в состав автомати-: ческого блока 5 измерения скорости.

РСварцевый генератор 6 опорной час- 25 од блока соединен с вторым входом тоты соединен через делитель 7 с бло- ключа 2И-НЕ 14 блока 4. Кроме того, ком 8 счета периодов, блоком 9 управ- первым ёходом триггер 33 блока 15

соединен через инвертор 34 с вторым выходом блока 4. Блок 15 формирует

30

ления памятью и блоком IО управления началом и окончанием сравнения блока 1 выделения минимума,

паузы большой длительности при выбеге (отрицательном ускорении) ротора

, Блок 5 автоматического измерения скорости состоит из пяти блоков. Основным яв ляется блок 4 задания тактовых сигналов 5 состоящий из счетчика 12, на вход которого через первьш вход элемента ЗИ-НЕ 13 поступают сигналы от частотного датчика I через формирователь 2 и первьш вход ключд 2И-НЕ 14; а также от блока 15 формирования пауз большой длительности через второй вход ключа 2И-НЕ 14, через вход элемента ЗИ-НЕ 13 от блока 9 управления памятью блока I6 памяти а также от устройства 17 Исходное состояние блока 18. Третьим выходом блок 4 соединен с вторым входом счетчика 19 блока 8 через инвертор 20 и. дифференциатор 21. Вторым выходом блок 4 соединен с вторым входом блока 22 управления счетчиком номера Ячеек через элемент 2И-НЕ 23 и с третьим входом блока 15f а также с элементом ИЛИ 24 блока 25 индикации, первьм выходом блок 4 подключен к второму входу оперативного запоминающего устройства (ОЗУ) 26 блока/ 16 памяти .через дифференциатор 27. Блок 4 сформирует сигналы, длительность которых обратно пропорциональна скорости (частоте) вращения ротора.

Блок 3 фиксации момента начала торможения состоит из преобразователя 28 частота - напряжение, который дополнен пороговым устройством 29 и формирователем 30 сигналов управления. Сигналы с первого выхода блока 3

подаются на второй вход блока 15 формирования пауз большой длительности. С второго выхода блока 3. сигнал подается на первый вход блока 22 управления счетчиком номера ячеек блока памяти через элемент 2И-НЕ 23. Блок 3 формирует сигналы в зависимости от знака ускорения.

Блок 15 формирования пауз большой длительности состоит из счетчика 31

циклов, на вход которого подключен через ключ 2И-НЕ 32 кварцевый генератор 6, второй выход блока 3, второй выход триггера 33 и выход элемента 17 Исходное состояние блока 18, а вы0

0

5

0

5

паузы большой длительности при выбеге (отрицательном ускорении) ротора.

Блок О счета периодов состоит из счетчика 19 и клю ча 2И-НЕ 35, на первый вход, которого подается сигнал от

блока 4 задания тактовых сигналов,на

I

второй вход - сигнал от кварцевого

генератора 6 через блок 7. Выход блока 8 соединен с входом ОЗУ 26 бло-- ка 16 памяти.. Блок 8 формирует сигнал Двоичньш код, которьш обратно пропорционален частоте вращения f ротора.

Блок 16 памяти состоит из -четырех блоков.- Основным является блок 36 ОЗУ, входы которого соединены с блоками 4 и 8 блока 5 автоматического измерения скорости и блоком 37 счета номера ячеек, с первым выходом которого соединен также индикатор 38 номера ячеек блока 25 индикации-. Выход блока 36 соединен с вторыми выходами блоков 39 сравнения (вычисления) и 40 регистра-минимума блока 11 деления минимума. Вход блока 37 счета номера ячеек соединен с вторым выходом блока 22 управления счетчиком номера . ячеек, который состоит и..з схемы 2И-НЕ 23, RS-триггера 41, схемы ЗИНЕ 42. На вход блока 22 подаются сиг3135 2369

налы от блоков 3 и 4 блока автомати-ка 56 калькуляции и индикации скоросческого измерения скорости. Блок 22ти вращения ротора. Блок 55 индикации

формирует сигналы на переключениеномера ячейки своим входом соединен с

ячеек.вторым выходом блока 37 счета номера

Блок 9 управления памятью- состоит ячеек блока 16 памяти, а блок 56 чеиз триггера 43 сброса памяти, на пер-рез элемент ИЛИ 24 - с третьим выхо- вый вход которого через схему 2И-НЕ 44 дом блока 37 и третьим выходом бловключены кнопка управления и выходка 4. Блок индикации обеспечивает пе- блока 18 установки в исходное состоя- , ревод числа периодов в величину сконие, а на второй вход подключен черезрости вращения,.считывание этих знадифференциатор 45 второй выход бло-.чений а также их маркировку. ка 37 счета номера ячеек, а также из Устройство, кроме того, содержит

триггера 46, первьш вход которого инвертор 57, элемент 2И-НЕ 58, диф- соединен с вторым выходом счетчика 47 g ференциатор 59, элемент 2И-НЕ 60, эле- номера ячеек блока 37, а второй вход- мент 2И 61, дифференциатор 62. с блоком 18 установки в исходное сое- Устройство работает следующим обтояние. Инверсным выходом через эле-разом.

мант 48 триггер 46 соединен с бло- В момент включения питания воздей- ,ком 22, а вторым выходом - с вторым у., ствием на кнопку Исходное состояние входом блока 10 управления началом иэлемента 17 триггеры 33 блока 15 и 43

окончанием сравнения блока If вьщеле-блока 9, а также счетчики 19 блока 8

ния минимума.и 47 блока 37 устанавливаются, в нулеБлок 11 выделения минимума состо-вое состояние. Счетчик 12 блока 4 ус- ит из четырех блоков: блока 39 срав- 25 танавливается в состояние двоичньй

нения (вычитания), блока 40 регистра-код которого соответствует 9, при .

минимума, блока 49 управления записьюэтом после снятия сигнала Исходное

в регистр и блока 10 управления нача-состояние импульсы на счетчик 19

лом и окончанием сравнения.блока 8 с делителя 7 не проходят, поЭлемент 50 сравнения блока 39 сво- о„ ка не поступит импульс от измеряемой им вторым входом соединен с выходомчастоты f и не переведет счетчик 12 ОЗУ 26 блока 36, третьим входом-- сблока 4 в состояние О. С этого мо- инверсным выходом регистра-минимума 51 мента начинается первый цикл измере- блока 40, а выходом - с первым входомния, В течение восьми периодов, кото- элемента 52 блока 49. Регистр-мини-рые отсчитывает счетчик 12 блока 4, мум 51 блока 40 первым входом соеди-счетчик 19 блока 8 заполняется стан- нен с выходом блока 49 управления за-дартизированнььми импульсами от дели- писью в регистр, вторым входом - стеля 7.

выходом ОЗУ 26, первым выходом - с По-окончании заполнения через це- третьим входом блока 39 и вторым вы-почку элементов 57, 27 блока 4 в ОЗУ ходом - с входом схемы 53 калькуляцииблока 36 поступает сигнал записи и и индикации скорости блока 25 инди-информация, содержащаяся в счетчи- (Кации.ке 19 блока 8, переносится в первую Блок 49 управления записью в ре-ячейку ОЗУ 26 и одновременно в регистр, состоит из логических элемен-гистр 51. По окончании переноса ин- тов 2И-НЕ 52 и ЗИ-НЕ 54; Выход бло-формации при сохранении положительно- ка 49 подсоединен к первому входу ре-го ускорения проходит импульс на , гистра-минимума 51. Входами блок 49счетчик 47 блока 37 и подготавливает соединен с выходом блока 10 управле-следующую ячейку ОЗУ для записи. Дания началом и окончанием сравнения илее идет сигнал сброса на счетчик 19 триггером 46.блока В через элементы 59, 20, 21

Блок 1 1 обеспечивает поочередноеблока 4, который устанавливает счет- сравнение значений числа периодов вчик 19 в нулевое состояние. Цикл сче- зафиксированных интервалах, информа-та и записи повторяется, В случае отция о которых хранится в ОЗУ, выбира-, df .ч

ее сутстБИя ускорения (-J-- - (J) счет- ет минимальное значение и передает , at

его калькулятору.чик 47 блока 37 сохраняет свое сосБлок 25 индикации состоит из бло-тояние, и при окончании очередного

ка 55 индикации номера ячейки и бло-цикла новая информация от счетчика 19

записывается опять в первую ячейку ОЗУ и регистр 51,

При появлении отрицательного ускорения от элемента 30 блока 3 поступает сигнал l, который разрешает прохождение импульса с дифференциатора 59 на триггер 33 блока 15. Этот импульс устанавливает триггер 33 в единичное состояние,. при этом на элемент 14 блока 4 поступает сигнал О, запрещающий прохождение импульсов измеряемой частоты, а на элемент 32 блока 15 поступает сигнал l, разрешающий счет импульсов с делителя 7 счетчиком 31. Таким образом, формируется длительная пауза i 30 с, Определяемая временем заполнения счетчика 31.

По окончании счета счетчик 31 блока 15 выдает импульс на триггер 33 и устанавливает его в состояние О,, при этом блок 4 включается в работу и осуществляет цикл замера длительности периода с записью в память, после чего вновь формируется пауза Т й 30 с. Такой режим работы производится до заполнения счетчика 47 блока 37, После его заполнения формируется сигнал от счетчика 47 на установку триггера 43 в состояние 1, при этом запись в ОЗУ прекращается за счет поступления сигнала О на элемент 13 блока 4 и остановки работы этого блока.

Одновременно на инверсном выходе триггера 43 блока 9-появляется сигнал l и элемент 44 разрешает прохождение сигнала ,с делителя 7 на счетчик 4 блока 37 через элементы 42.и 60 блока 22.

При этом на сумматоре 50 блока 39 при каждом импульсе происходит сравнение величин содержимого регистра 51 и соответствующей ячейки ОЗУ 26. Если в регистре 51 значение сравниваемой величины меньше, чем в ячейке памяти, то на выходе сумматора 50 имеется знак переноса тождественный логической единице, а на выходе элемента 52. - ло гический ноль. Элемент 54 при этом не пропускает сигнал на запись содержимого ячейки ОЗУ в регистр 51 и в регистре остается меньшее число. Если в ячейке ОЗУ число меньше, чем в регистре 51, то знак переноса на выходе сумматора 50 отсутствует, сигнал записи через эле- . менты 61 и 54 проходит в регистр 51

,

ы

7

1 352369 .

и при этом записывается меньшее число.

Таким образом, в регистре 51 сохраняется меньшее значение периода, измеряемой частоты. После заполнения счетчика 47 поступает импульс на триггер 46, который устанавливается в нулевое состояние, запирая при этом эле1Q мент 48, и тактовая частота с элемента 7 не проходит на счетчик 47. Минимальное число, преобразованное в схеме 53 калькуляции блока 56, высвечивается в виде максимальной величины

.|g заброса оборотов ротора.

Для ручного считывания записанного в ячейках ОЗУ предусмотрен элемент 41 Представляющий собой RS-триггер, у которого в исходном состоянии на выходе

2Q имеется 1. При замыкании контактов ключа на выходе элемента 41 появляется размыкании вновь 1. Через элементы 42 и 60 сигнал попадает на вход С счетчика 47.

25 Импульсы на запуск калькулятора 53 поступают через элемент ИЛИ 24 блока 56 либо с элемента 59 блока 4 при нормальном режиме (ускорение равно нулю), либо с элемента 60, при работе в режиме- вьщеления максимума или ручном съеме информации.

При работе в режиме запоминания (наличие ускорения, счетчик 47 не за полнен) импульсы поступают на оба входа элемента ИЛИ 24 одновременно.

30

45

35

Формула изобретения

Устройство для измерения парамет- .д ров вращения ротора в переходных режимах, содержащее частотньш датчик оборотов, подключенньй к формирователю стандартизированных импульсов,связанному с блоком автоматического измерения скорости вращения, к которому подключен через делитель частоты генератор опорной частоты-, блок момента начала торможения и блок индикации с регистром памяти, о т л и - чающее ся тем, что, с целью повьшения точности измерения, в него введен блок памяти, блок выделения минимума, в блок автоматического измерения скорости дополнительно введен задатчик тактовых сигналов и счетчик периодов, а в блок индикации дополнительно введен калькулятор, причем второй выход делителя частоты соединен с первым входом блока памя50

55

1352369

ти и с первым входом блока виделения;мерения скорости, первый вход Jcoropo- минимума., первый выход блока автома-го подключен к первому выходу блока тического измерения-скорости подклю-памяти, вторым выходом соединенного второму входу блока памяти,с первым входом блока 11ндикации, тре- третьим входом соединенного с вторымтьим выходом - с вторым входом блока выходом блока автоматического измере-индикации, четвертым выходом - с трения скорости, третий выход котороготьим входом блока выделения миниму- соединён с четвертым входом блока па-мау а пятым выходом - с четвертым мяти и с вторым входом блока йыделе- Q входом блока выделения минимума, трения минимума, четвертый выход блокатий вход блока индикации подключен к автоматического измерения скоростишестому выходу блока автоматического подключен к пятому входу блока памя-измерения скорости, а четвертым вхо- ти, шестым входом соединенного с пя- дом - к выходу блока выделения мини- тым выходом блока автоматического из-мума.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель несимметричности сигналов | 1990 |

|

SU1725179A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для вывода информации | 1985 |

|

SU1285460A1 |

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1358003A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Система для проведения испытаний турбины | 1989 |

|

SU1636706A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

Изобретение относится к измерительной технике. Цель изобретения - повышение ToqisocTH изь ёрения. В регистре 51 сохраняется меньшее значение периода измеряемой частоты. После заполнения счетчика 47 поступает импульс на триггер 46 и он устанавливается в нулевое состояние, запирая элемент 48, и тактовая частота с де .лителя 7 не проходит на счетчик 47 Минимальное число, преобразоБ нное в блоке 53 калькуляции блока 56 калькуляции и индикации вракения ротора, высвечивается в виде максимальной величины оборотов ротора. При работе в режиме запоминанр я и1-ту.пьсы поступа-- ют на оба входа элемента HTui 24 одновременно. 1 ил. Г/) ii i К5 SA5 ssp., ЧиГ с-

| Авторское свидетельство СССР № 4155805 кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| .Авторское свидетельство СССР № 757983, | |||

| кл, G 01 Р 3/48, 1978. | |||

Авторы

Даты

1987-11-15—Публикация

1983-10-10—Подача