Изобретение относится к электросвязи и может быть использовано в системах передачи данных управления и телесигнализации, работающих по радиоканалу.

Цель изобретения - повышение устойчивости синхронизации путем уменьшения вероятности сбоя при перерывах связи.

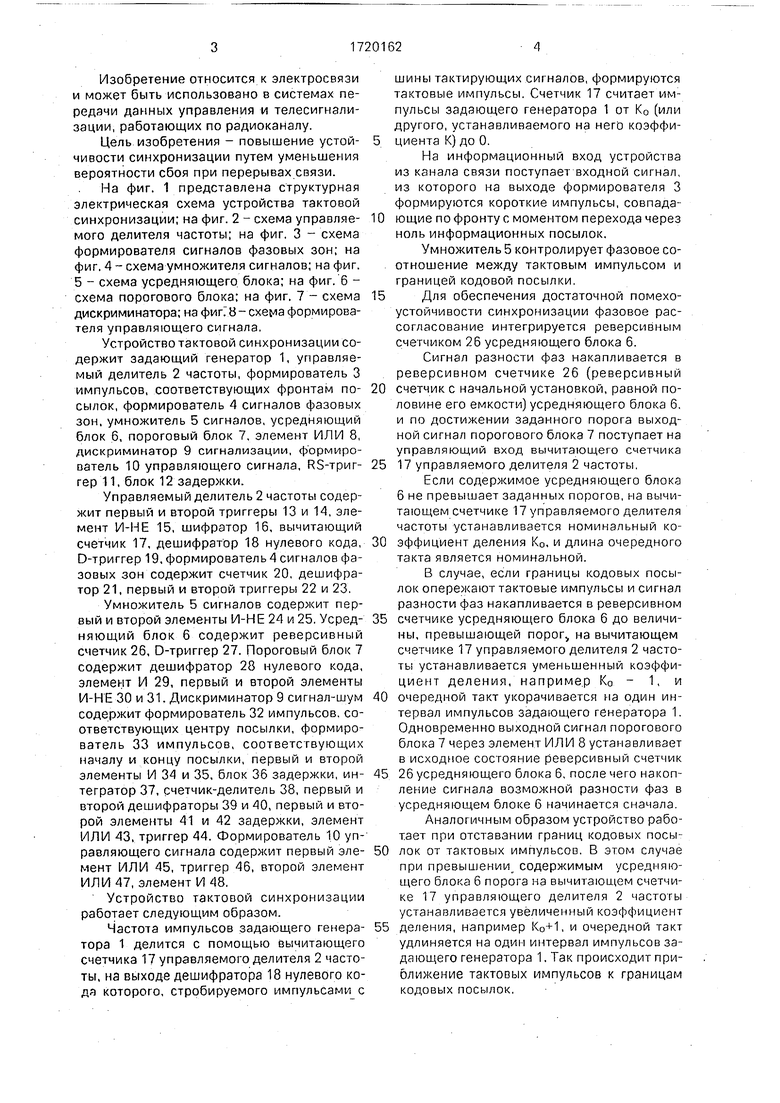

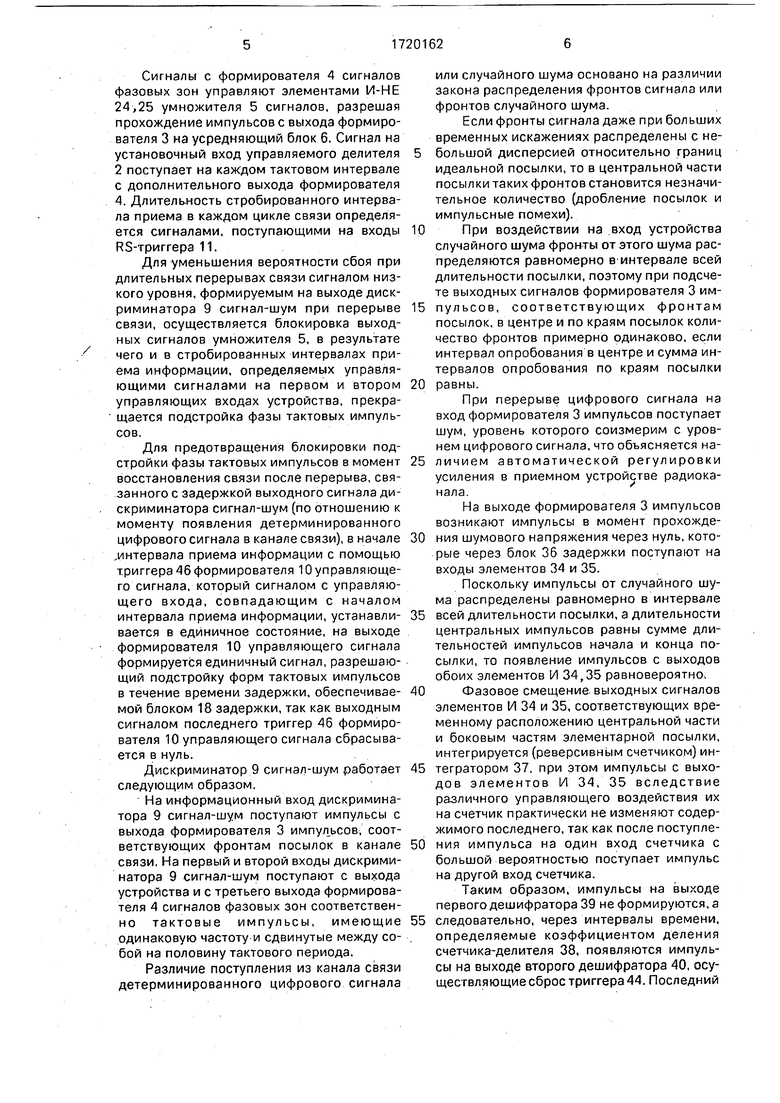

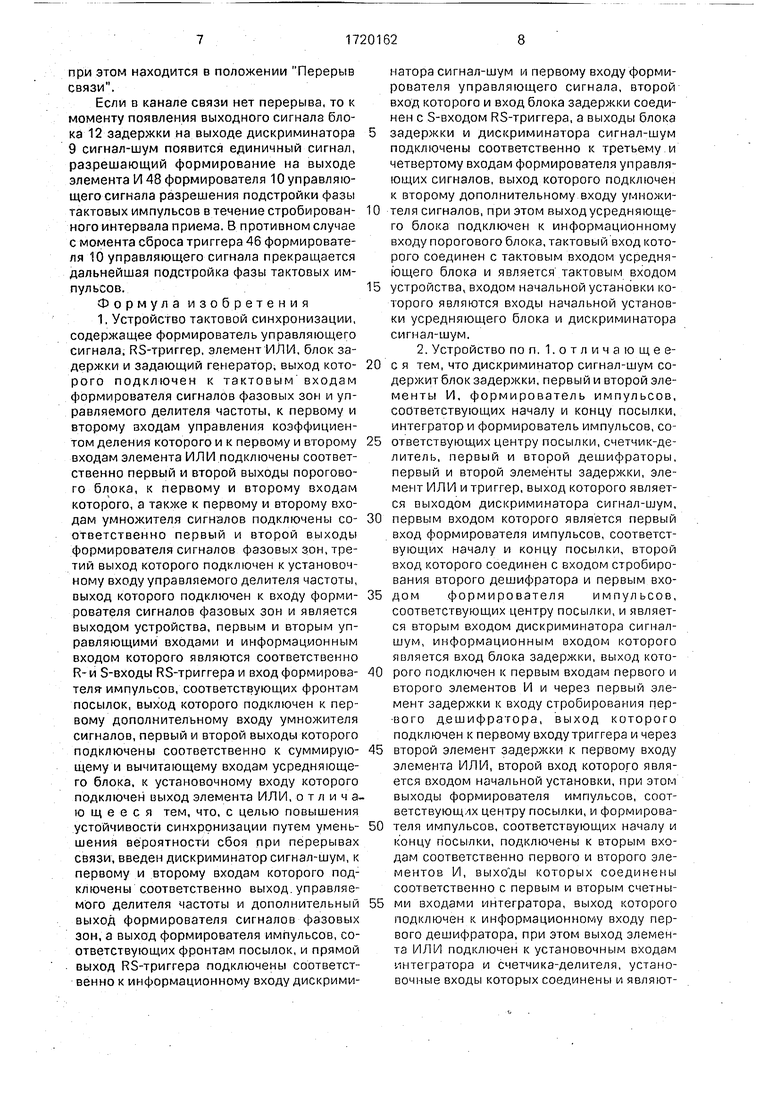

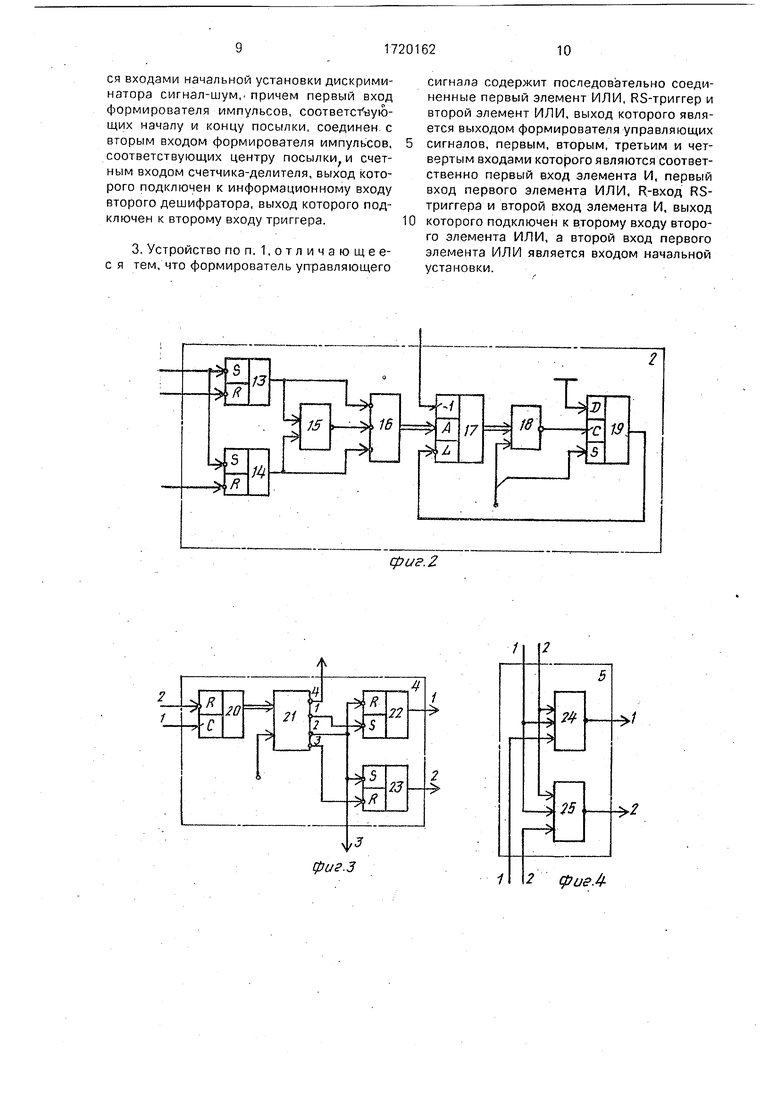

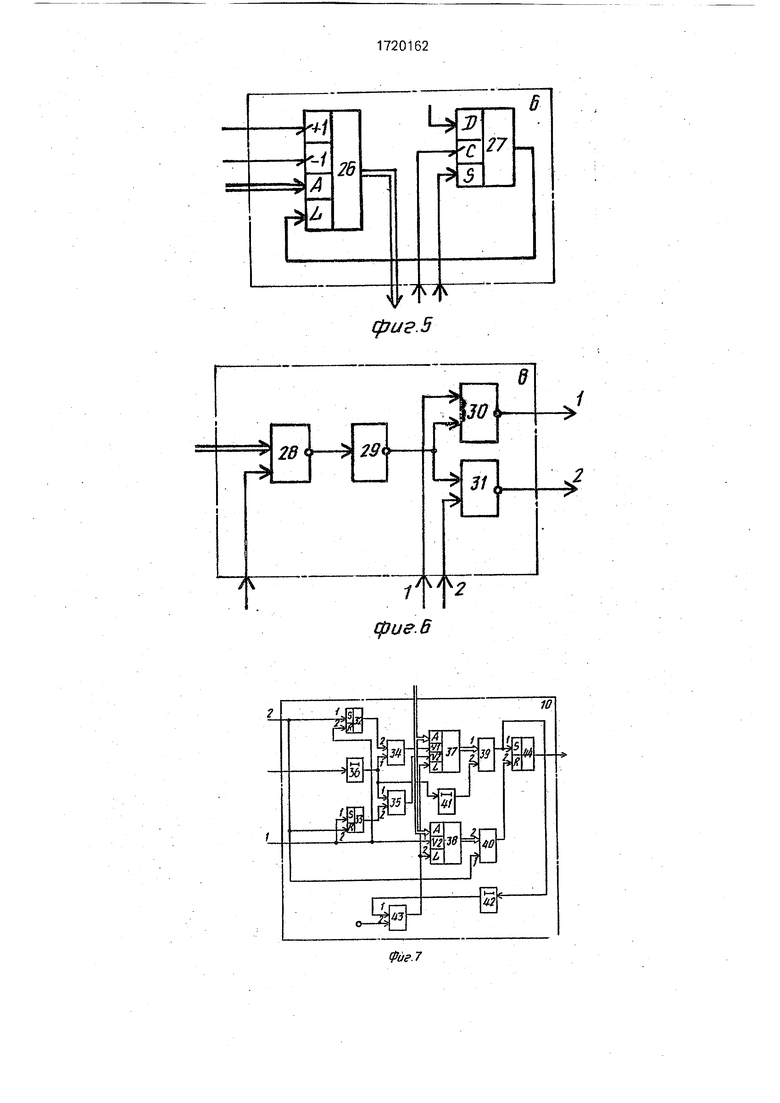

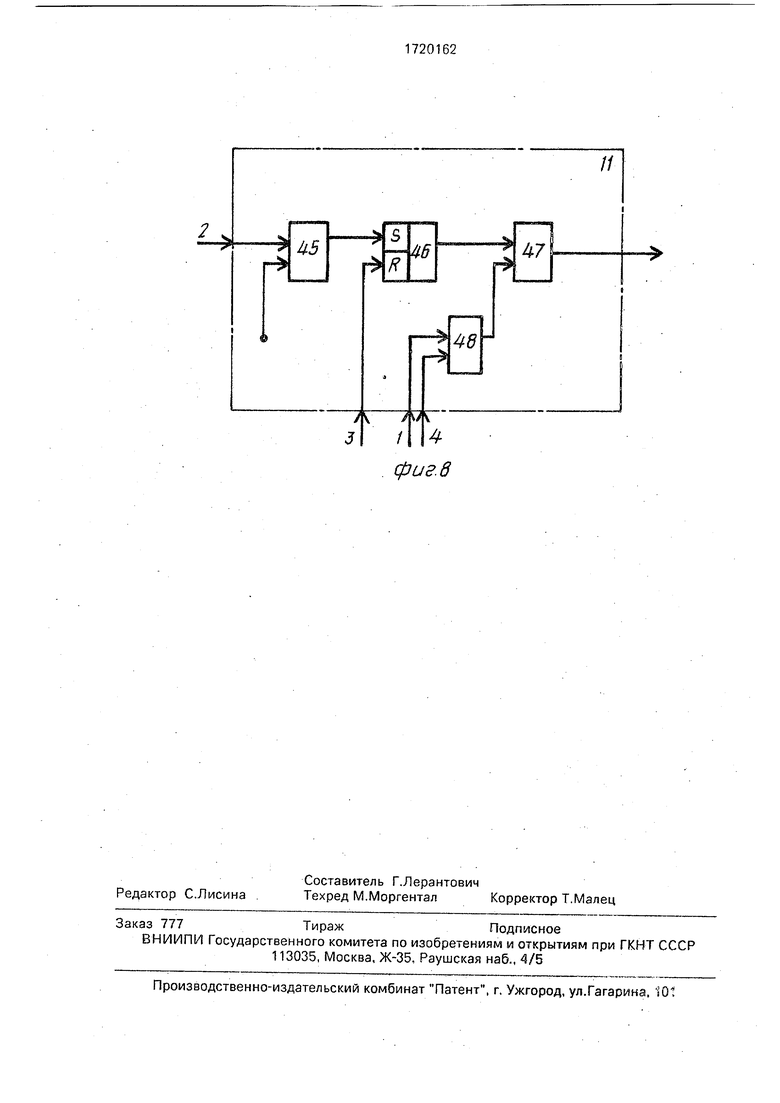

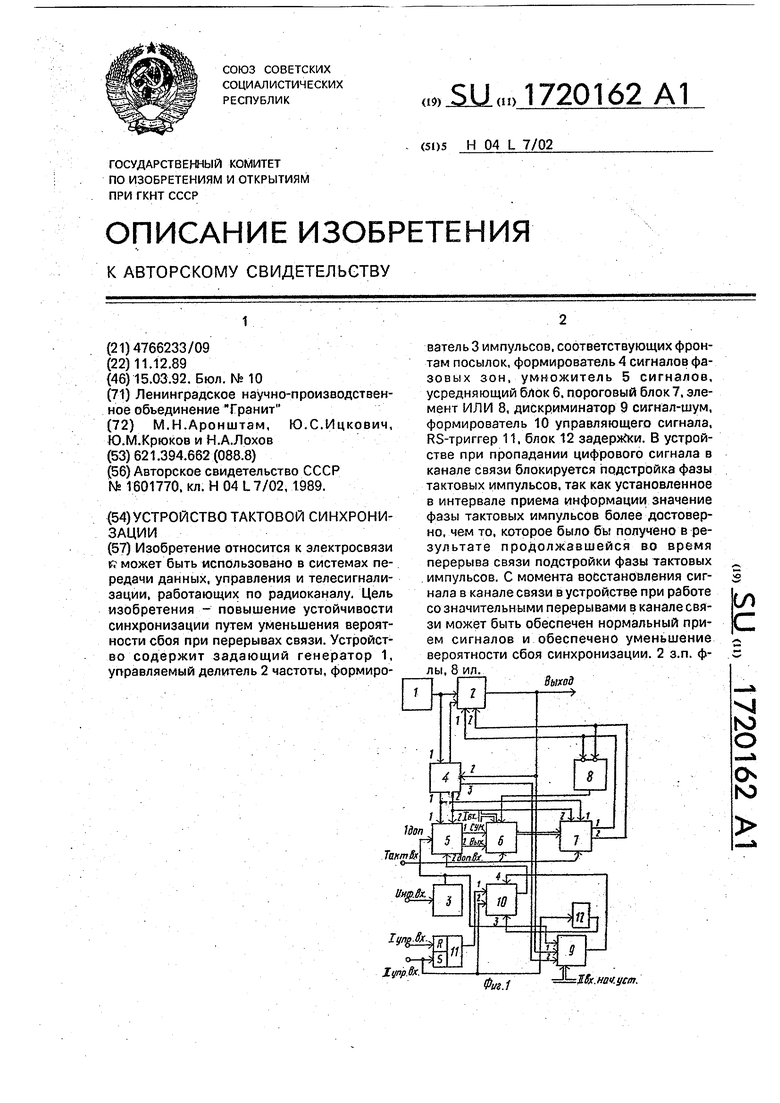

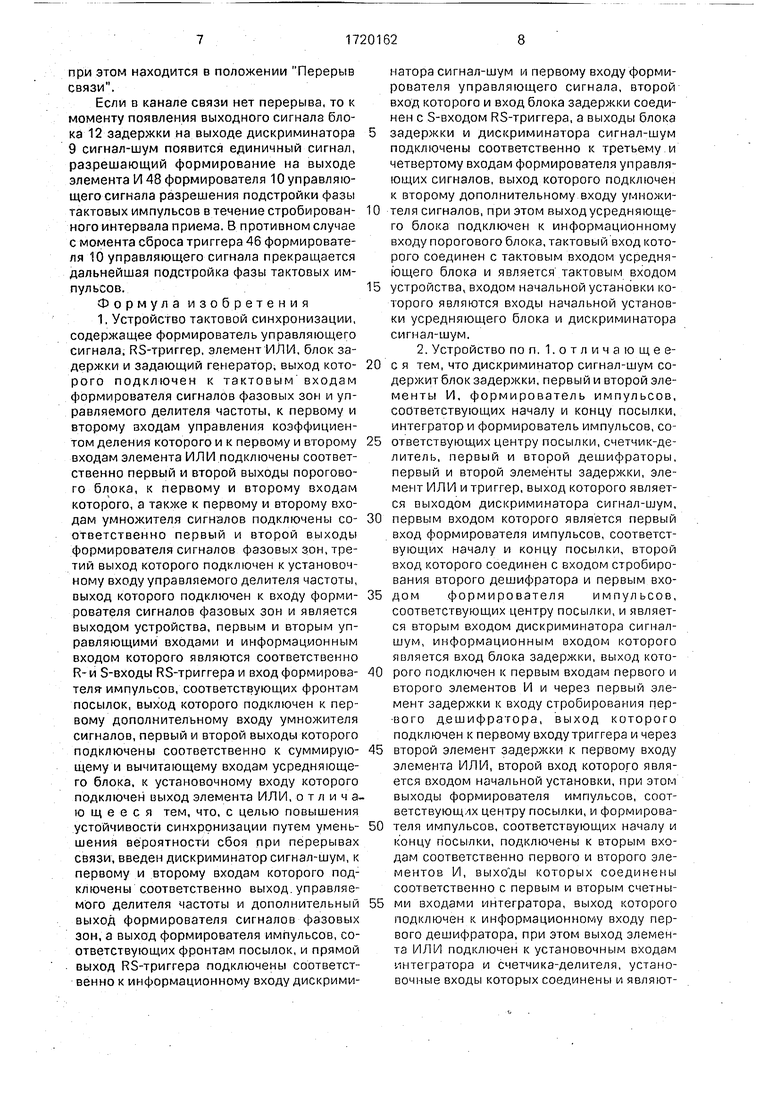

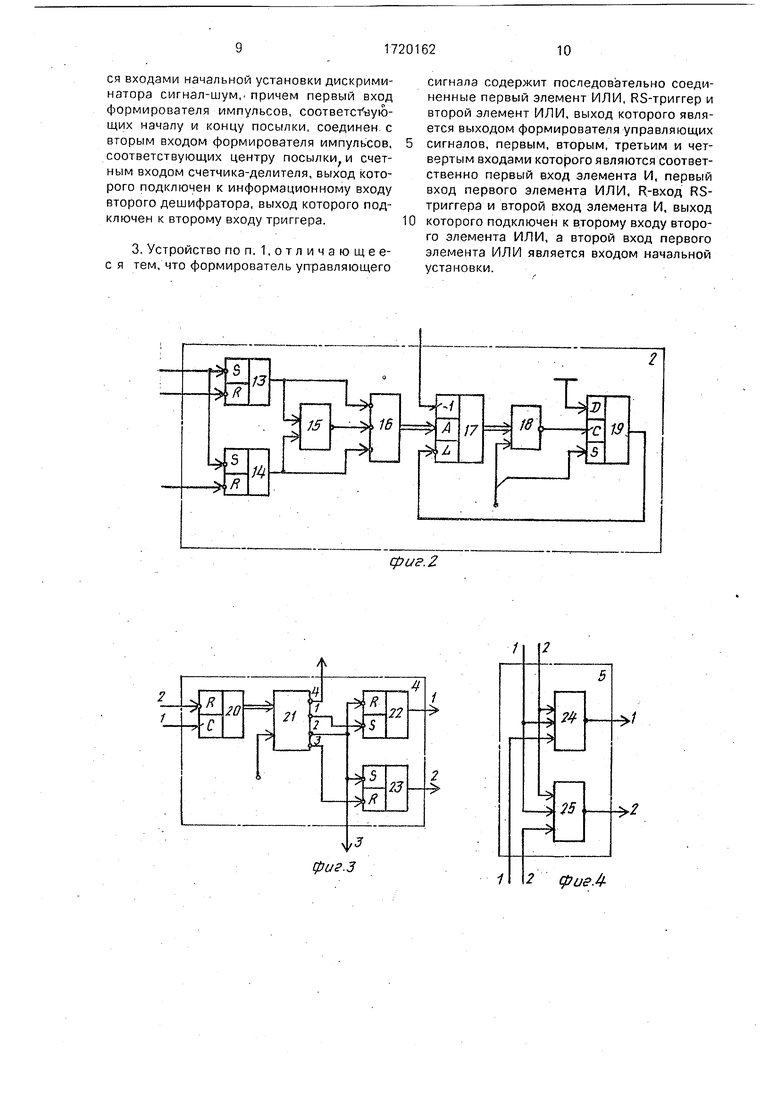

На фиг. 1 представлена структурная электрическая схема устройства тактовой синхронизации; на фиг. 2 - схема управляемого делителя частоты; на фиг. 3 - схема формирователя сигналов фазовых зон; на фиг. 4 - схема умножителя сигналов; на фиг. 5 - схема усредняющего, блока; на фиг. 6 - схема порогового блока; на фиг. 7 - схема дискриминатора; на фиг78- схема формирователя управляющего сигнала,

Устройство тактовой синхронизации содержит задающий генератор 1, управляемый делитель 2 частоты, формирователь 3 импульсов, соответствующих фронтам посылок, формирователь 4 сигналов фазовых зон, умножитель 5 сигналов, усредняющий блок 6, пороговый блок 7, элемент ИЛИ 8, дискриминатор 9 сигнализации, формирователь 10 управляющего сигнала, RS-триг- гер 11, блок 12 задержки.

Управляемый делитель 2 частоты содержит первый и второй триггеры 13 и 14, элемент И-НЕ 15, шифратор 16, вычитающий счетчик 17, дешифратор 18 нулевого кода, D-триггер 19, формирователь 4 сигналов фазовых зон содержит счетчик 20, дешифратор 21, первый и второй триггеры 22 и 23.

Умножитель 5 сигналов содержит первый и второй элементы И-НЕ 24 и 25. Усредняющий блок 6 содержит реверсивный счетчик 26, D-триггер 27. Пороговый блок 7 содержит дешифратор 28 нулевого кода, элемент И 29, первый и второй элементы И-НЕ 30 и 31. Дискриминатор 9 сигнал-шум содержит формирователь 32 импульсов, соответствующих центру посылки, формирователь 33 импульсов, соответствующих началу и концу посылки, первый и второй элементы И 34 и 35, блок 36 задержки, интегратор 37, счетчик-делитель 38, первый и второй дешифраторы 39 и 40, первый и второй элементы 41 и 42 задержки, элемент ИЛИ 43, триггер 44. Формирователь 1.0 управляющего сигнала содержит первый элемент ИЛИ 45, триггер 46, второй элемент ИЛИ 47, элемент И 48.

Устройство тактовой синхронизации работает следующим образом.

Частота импульсов задающего генератора 1 делится с помощью вычитающего счетчика 17 управляемого делителя 2 частоты, на выходе дешифратора 18 нулевого кода которого, стробируемого импульсами с

шины тактирующих сигналов, формируются тактовые импульсы. Счетчик 17 считает импульсы задающего генератора 1 от К0 (или другого, устанавливаемого на него коэффициента К) до 0.

На информационный вход устройства из канала связи поступает входной сигнал, из которого на выходе формирователя 3 формируются короткие импульсы, совпада0 ющие по фронту с моментом перехода через ноль информационных посылок.

Умножитель 5 контролирует фазовое соотношение между тактовым импульсом и границей кодовой посылки,

5 Для обеспечения достаточной помехоустойчивости синхронизации фазовое рассогласование интегрируется реверсивным счетчиком 26 усредняющего блока 6.

Сигнал разности фаз накапливается в реверсивном счетчике 26 (реверсивный

0 счетчик с начальной установкой, равной половине его емкости) усредняющего блока 6. и по достижении заданного порога выходной сигнал порогового блока 7 поступает на управляющий вход вычитающего счетчика

5 17 управляемого делителя 2 частоты.

Если содержимое усредняющего блока 6 не превышает заданных порогов, на вычитающем счетчике 17 управляемого делителя частоты устанавливается номинальный ко0 эффициент деления К0, и длина очередного такта является номинальной.

В случае, если границы кодовых посылок опережают тактовые импульсы и сигнал разности фаз накапливается в реверсивном

5 счетчике усредняющего блока 6 до величины, превышающей порог,, на вычитающем счетчике 17 управляемого делителя 2 частоты устанавливается уменьшенный коэффициент деления, например К0 - 1, и

0 очередной такт укорачивается на один интервал импульсов задающего генератора 1. Одновременно выходной сигнал порогового блока 7 через элемент ИЛИ 8 устанавливает в исходное состояние реверсивный счетчик

5 26 усредняющего блока 6, после чего накопление сигнала возможной разности фаз в усредняющем блоке 6 начинается сначала. Аналогичным образом устройство работает при отставании границ кодовых посы0 лок от тактовых импульсов. В этом случае при превышении содержимым усредняющего блока 6 порога на вычитающем счетчике 17 управляющего делителя 2 частоты устанавливается увеличенный коэффициент

5 деления, например К0+1, и очередной такт удлиняется на один интервал импульсов задающего генератора 1, Так происходит приближение тактовых импульсов к границам кодовых посылок.

Сигналы с формирователя 4 сигналов фазовых зон управляют элементами И-НЕ 24,25 умножителя 5 сигналов, разрешая прохождение импульсов с выхода формирователя 3 на усредняющий блок 6. Сигнал на установочный вход управляемого делителя 5 2 поступает на каждом тактовом интервале с дополнительного выхода формирователя 4. Длительность стробированного интервала приема в каждом цикле связи определяется сигналами, поступающими на входы 10 RS-триггера 11.

Для уменьшения вероятности сбоя при длительных перерывах связи сигналом низкого уровня, формируемым на выходе дискриминатора 9 сигнал-шум при перерыве 15 связи, осуществляется блокировка выходных сигналов умножителя 5, в результате чего и в стробированных интервалах приема информации, определяемых управляющими сигналами на первом и втором 20 управляющих входах устройства, прекра- щается подстройка фазы тактовых импульсов.

Для предотвращения блокировки подстройки фазы тактовых импульсов в момент 25 восстановления связи после перерыва, связанного с задержкой выходного сигнала дискриминатора сигнал-шум (по отношению к моменту появления детерминированного цифрового сигнала в канале связи), в начале 30 „интервала приема информации с помощью триггера 46 формирователя ТО управляющего сигнала, который сигналом с управляющего входа, совпадающим с началом интервала приема информации, устанавли- 35 вается в единичное состояние, на выходе формирователя 10 управляющего сигнала формируется единичный сигнал, разрешающий подстройку форм тактовых импульсов в течение времени задержки, обеспечивав- 40 мой блоком 18 задержки, так как выходным сигналом последнего триггер 46 формирователя 10 управляющего сигнала сбрасывается в нуль.

Дискриминатор 9 сигнал-шум работает 45 следующим образом.

На информационный вход дискриминатора 9 сигнал-шум поступают импульсы с выхода формирователя 3 импульсов, соответствующих фронтам посылок в канале 50 связи. На первый и второй входы дискриминатора 9 сигнал-шум поступают с выхода устройства и с третьего выхода формирователя 4 сигналов фазовых зон соответственно тактовые импульсы, имеющие 55 одинаковую частоту и сдвинутые между со- . бой на половину тактового периода.

Различие поступления из канала связи детерминированного цифрового сигнала

или случайного шума основано на различии закона распределения фронтов сигнала или фронтов случайного шума.

Если фронты сигнала даже при больших временных искажениях распределены с небольшой дисперсией относительно границ идеальной посылки, то в центральной части посылки таких фронтов становится незначительное количество (дробление посылок и импульсные помехи).

При воздействии на .вход устройства случайного шума фронты от этого шума распределяются равномерно в интервале всей длительности посылки, поэтому при подсчете выходных сигналов формирователя 3 им- пульсов, соответствующих фронтам посылок, в центре и по краям посылок количество фронтов примерно одинаково, если интервал опробования в центре и сумма интервалов опробования по краям посылки равны.

При перерыве цифрового сигнала на вход формирователя 3 импульсов поступает шум, уровень которого соизмерим с уровнем цифрового сигнала, что объясняется наличием автоматической регулировки усиления в приемном устройстве радиоканала.

На выходе формирователя 3 импульсов возникают импульсы в момент прохождения шумового напряжения через нуль, которые через блок 36 задержки поступают на входы элементов 34 и 35.

Поскольку импульсы от случайного шума распределены равномерно в интервале всей длительности посылки, а длительности центральных импульсов равны сумме длительностей импульсов начала и конца посылки, то появление импульсов с выходов обоих элементов И 34,35 равновероятно.

Фазовое смещение выходных сигналов элементов И 34 и 35, соответствующих временному расположению центральной части и боковым частям элементарной посылки, интегрируется (реверсивным счетчиком) интегратором 37, при этом импульсы с выходов элементов И 34, 35 вследствие различного управляющего воздействия их на счетчик практически не изменяют содержимого последнего, так как после поступления импульса на один вход счетчика с большой вероятностью поступает импульс на другой вход счетчика.

Таким образом, импульсы на выходе первого дешифратора 39 не формируются, а следовательно, через интервалы времени, определяемые коэффициентом деления счетчика-делителя 38, появляются импульсы на выходе второго дешифратора 40, осуществляющие сброс триггера 44. Последний

при этом находится в положении Перерыв связи.

Если в канале связи нет перерыва, то к моменту появления выходного сигнала блока 12 задержки на. выходе дискриминатора 9 сигнал-шум появится единичный сигнал, разрешающий формирование на выходе элемента И 48 формирователя 10 управляющего сигнала разрешения подстройки фазы тактовых импульсов в течение стробирован- ногоинтервала приема, В противном случае с момента сброса триггера 46 формирователя 10 управляющего сигнала прекращается дальнейшая подстройка фазы тактовых импульсов.

Формула изо б р е т е н и я 1. Устройство тактовой синхронизации, содержащее формирователь управляющего сигнала. RS-триггер, элемент ИЛИ, блок задержки и задающий генератор, выход которого подключен к тактовым входам формирователя сигналов фазовых зон и управляемого делителя частоты, к первому и второму входам управления коэффициентом деления которого и к первому и второму входам элемента ИЛИ подключены соответственно первый и второй выходы порогового блока, к первому и второму входам которого, а также к первому и второму входам умножителя сигналов подключены соответственно первый и второй выходы формирователя сигналов фазовых зон, третий выход которого подключен к установочному входу управляемого делителя частоты, выход которого подключен к входу формирователя сигналов фазовых зон и является выходом устройства, первым и вторым управляющими входами и информационным входом которого являются соответственно R-и 8-входы RS-триггера и вход формирователя- импульсов/соответствующих фронтам посылок, выход которого подключен к первому дополнительному входу умножителя сигналов, первый и второй выходы которого подключены соответственно к суммирующему и вычитающему входам усредняющего блока, к установочному входу которого подключен выход элемента ИЛИ, отличающееся тем, что, с целью повышения устойчивости синхронизации путем уменьшения вероятности сбоя при перерывах связи, введен дискриминатор сигнал-шум, к первому и второму входам которого подключены соответственно выход, управляемого делителя частоты и дополнительный выход формирователя сигналов фазовых зон, а выход формирователя импульсов, соответствующих фронтам посылок, и прямой выход RS-триггера подключены соответственно к информационному входу дискриминатора сигнал-шум и первому входу формирователя управляющего сигнала, второй вход которого и вход блока задержки соединен с S-входом RS-триггера, а выходы блока

задержки и дискриминатора сигнал-шум подключены соответственно к третьему и четвертому входам формирователя управляющих сигналов, выход которого подключен к второму дополнительному входу умножи0 теля сигналов, при этом выход усредняющего блока подключен к информационному входу порогового блока, тактовый вход которого соединен с тактовым входом усредняющего блока и является тактовым входом

5 устройства, входом начальной установки которого являются входы начальной установки усредняющего блока и дискриминатора сигнал-шум.

2. Устройство по п. 1. о т л и ч а ю щ е е0 с я тем, что дискриминатор сигнал-шум содержит блок задержки, первый и второй эле- менты И, формирователь импульсов, соответствующих началу и концу посылки, интегратор и формирователь импульсов, со5 ответствующих центру посылки, счетчик-делитель, первый и второй дешифраторы, первый и второй элементы задержки, элемент ИЛИ и триггер, выход которого является выходом дискриминатора сигнал-шум,

0 первым входом которого является первый вход формирователя импульсов, соответствующих началу и концу посылки, второй вход которого соединен с входом стробиро- вания второго дешифратора и первым вхо5 дом формирователя импульсов, соответствующих центру посылки, и является вторым входом дискриминатора сигнал- шум, информационным входом которого является вход блока задержки, выход кото0 рого подключен к первым входам первого и второго элементов И и через первый элемент задержки к входу стробирования пер- вого дешифратора, выход которого подключен к первому входу триггера и через

5 второй элемент задержки к первому входу элемента ИЛИ, второй вход которого является входом начальной установки, при этом выходы формирователя импульсов, соответствующих центру посылки, и формирова0 теля импульсов, соответствующих началу и концу посылки, подключены к вторым входам соответственно первого и второго элементов И, выходы которых соединены соответственно с первым и вторым счетны5 ми входами интегратора, выход которого подключен к информационному входу первого дешифратора, при этом выход элемента ИЛИ подключен к установочным входам интегратора и счетчика-делителя, установочные входы которых соединены и являются входами начальной установки дискриминатора сигнал-шум,, причем первый вход формирователя импульсов, соответствующих началу и концу посылки, соединен с вторым входом формирователя импульсов, соответствующих центру посылки,и счетным входом счетчика-делителя, выход которого подключен к информационному входу второго дешифратора, выход которого подключен к второму входу триггера.

3. Устройство поп. 1,отличающее- с я тем, что формирователь управляющего

0

сигнала содержит поспедовательно соединенные первый элемент ИЛИ, RS-триггер и второй элемент ИЛИ, выход которого является выходом формирователя управляющих сигналов, первым, вторым, третьим и четвертым входами которого являются соответственно первый вход элемента И, первый вход первого элемента ИЛИ. R-вход RS- триггера и второй вход элемента И. выход которого подключен к второму входу второго элемента ИЛИ, а второй вход первого элемента ИЛИ является входом начальной установки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство определения перерывов цифрового сигнала в радиоканале | 1988 |

|

SU1538262A1 |

| Устройство синхронизации | 1987 |

|

SU1525931A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1254589A1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство тактовой синхронизации псевдослучайных последовательностей | 1988 |

|

SU1596473A1 |

| Устройство для кодирования и декодирования сигналов в системах передачи цифровых данных | 1980 |

|

SU1046959A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

Изобретение относится к электросвязи к может быть использовано в системах передачи данных, управления и телесигнализации, работающих по радиоканалу. Цель изобретения - повышение устойчивости синхронизации путем уменьшения вероятности сбоя при перерывах связи. Устройство содержит задающий генератор 1, управляемый делитель 2 частоты, формирователь 3 импульсов, соответствующих фронтам посылок, формирователь 4 сигналов фа- зовых зон, умножитель 5 сигналов, усредняющий блок 6. пороговый блок 7, элемент ИЛИ 8, дискриминатор 9 сигнал-шум, формирователь 10 управляющего сигнала, RS-триггер 11, блок 12 задержки. В устройстве при пропадании цифрового сигнала в канале связи блокируется подстройка фазы тактовых импульсов, так как установленное в интервале приема информации значение фазы тактовых импульсов более достоверно, чем то, которое было бы получено в результате продолжавшейся во время перерыва связи подстройки фазы тактовых импульсов. С момента восстановления сигнала в канале связи в устройств© при работе со значительными перерывами в канале связи может быть обеспечен нормальный прием сигналов и обеспечено уменьшение вероятности сбоя синхронизации. 2 з.п. ф- лы, 8 ил. Выход - сл С xi ю о Ск ГО Ta/fmSrl flffifr.. «УТЛ-1 Itjnp.Bx. I Фиг.1 JSx.Hatf.ycm.

фиг.З

фиг. 2

г

$

м

Ч

15

2 фие.Ь

-вд

фиг.5

фие.6

w

5

г

м

Ui

«/

чг

фиг. 8

| Устройство тактовой синхронизации | 1988 |

|

SU1601770A1 |

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-03-15—Публикация

1989-12-11—Подача