и 8, формирователь 4 признака начала информации, счетчик 5, триггеры 9 и 10, генератор 11 импульсов, формирователь 12 признака конца информации, дешифратор 13 и формирователи 14 импульсов информации. Устройство содержит также триггеры 16 и 18, дешифратор 17, элементы ИЛИ 19-22, элементы И 23 и 28 и блоки 24 коррекции, каждый из которых выполнен

Изобретение относится к области накопления информации, а именно к устройствам для восстановления воспроизведенных тактовых импульсов.

Цель изобретения - повышение точности восстановления воспроизведенных тактовых импульсов.

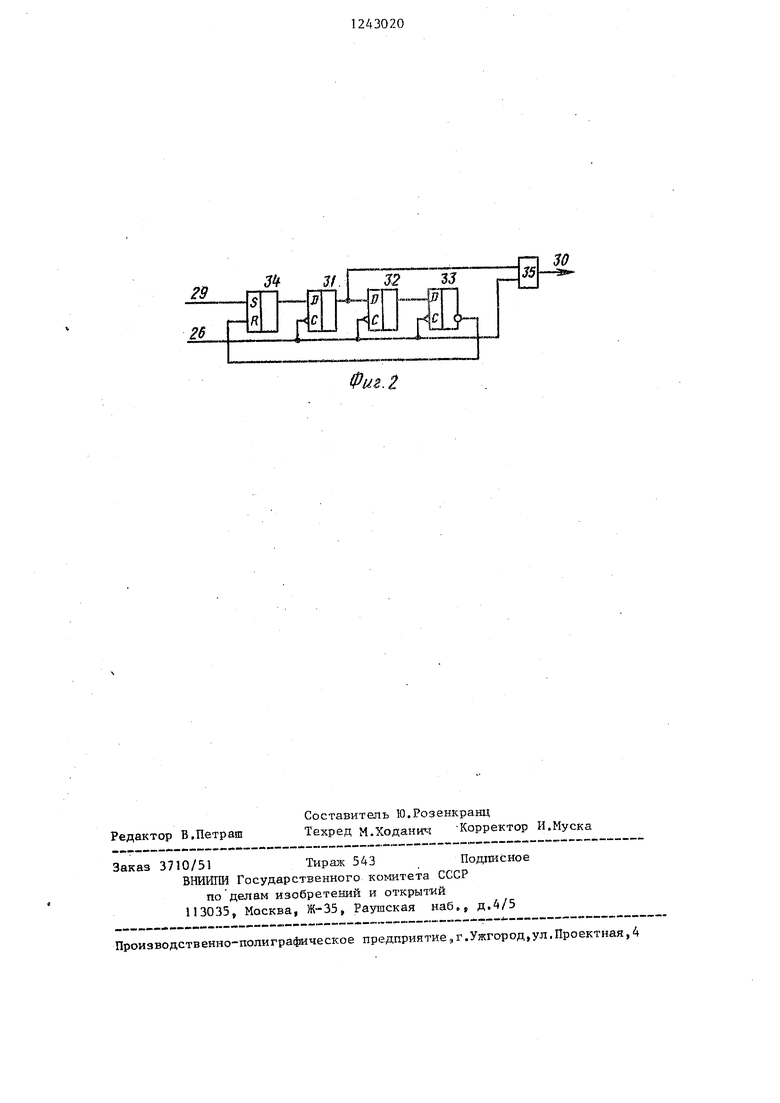

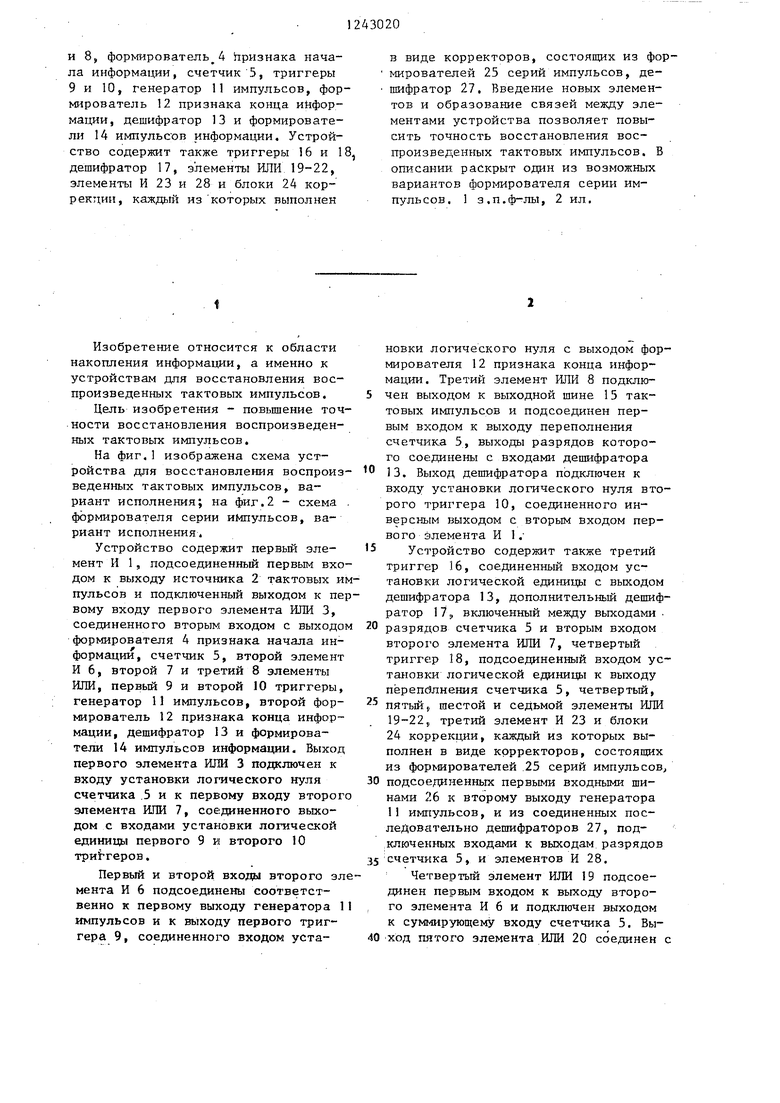

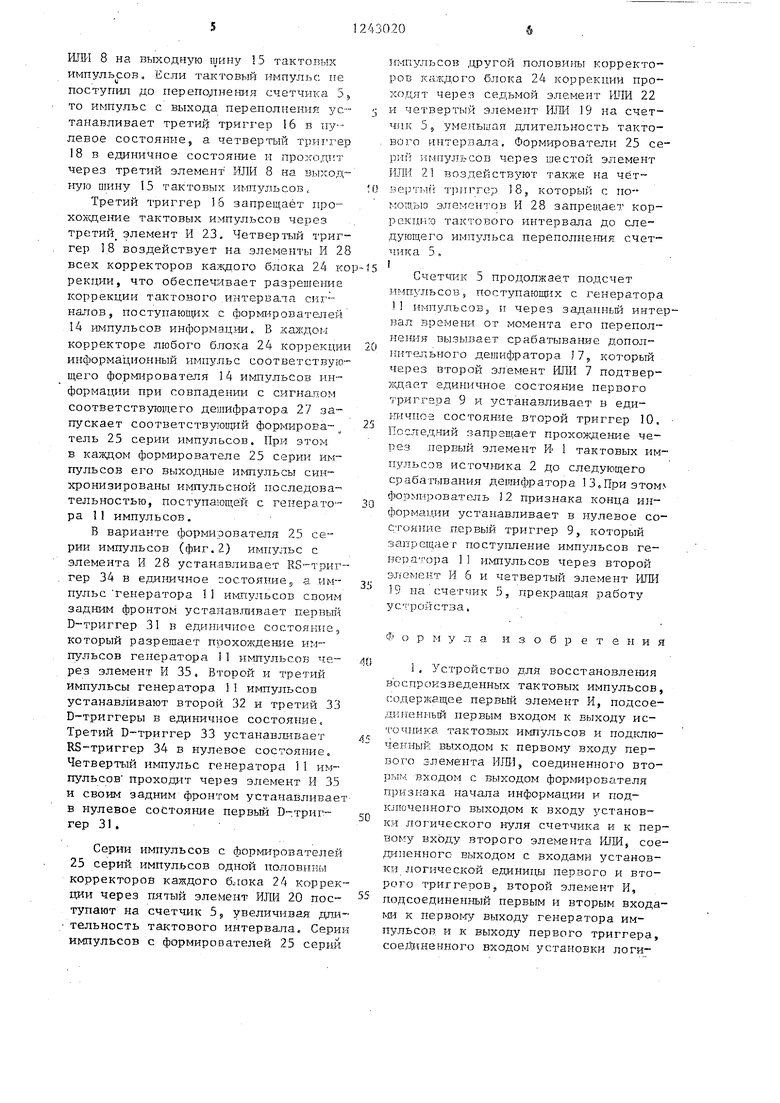

На фиг.1 изображена схема устройства для восстановления воспроизведенных тактовых импульсов, вариант исполнения; на фиг.2 - схема . формирователя серии импульсов, вариант исполнения.

Устройство содержит первый элемент И 1, подсоединенный первым входом к выходу источника 2 тактовых импульсов и подключенный выходом к первому входу первого элемента ИЛИ 3, соединенного вторым входом с выходом формирователя 4 признака начала информации, счетчик 5, второй элемент И 6, второй 7 и третий 8 элементы ИЛИ, первый 9 и второй 10 триггеры, генератор 11 импульсов, второй формирователь 12 признака конца информации, дешифратор 13 и формирователи 14 импульсов информации. Выход первого элемента ИЛИ 3 подключен к входу установки логического нуля счетчика .5 и к первому входу второго элемента ИЛИ 7, соединенного выходом с входами установки логической единицы первого 9 и второго 10 триггеров.

Первый и второй входы второго элемента И 6 подсоединены соответственно к первому ВЫ5СОДУ генератора 11 импульсов и к выходу первого триггера 9, соединенного входом устав виде корректоров, состояпщх из формирователей 25 серий импульсов, дешифратор 27, Введение новых элементов и образование связей между элементами устройства позволяет повысить точность восстановления вос- 1троизведенных тактовых импульсов. В описании раскрыт один из возможных вариантов формирователя серии импульсов. 1 з,п.ф-лы, 2 ил.

новки логического нуля с выходом формирователя 12 признака конца информации. Третий элемент ИЛИ 8 подключен выходом к выходной шине 15 тактовых импульсов и подсоединен первым входом к выходу переполнения счетчика 5, выходы разрядов которого соединены с входами дешифратора

13. Выход дешифратора подключен к

входу установки логического нуля второго триггера 10, соединенного инверсным выходом с вторым входом первого элемента И 1 .

Устройство содержит также третий триггер 16, соединенный входом установки логической единицы с выходом дешифратора 13, дополнительный дешифратор 17,, включенный между выходами .

разрядов счетчика 5 и вторым входом второго элемента ИЛИ 7, четвертый тригг€ф 18, подсоединенный входом установки логической единицы к выходу переполнения счетчика 5, четвертьй,

пятьй,, шестой и седьмой элементы ИЛИ 19-22, третий элемент И 23 и блоки 24 коррекции, каждый из которых выполнен в виде корректоров, состоящих из формирователей 25 серий импyльcoв

подсоединенных первыми входными шинами 26 к второму выходу генератора 11 импульсов, и из соединенных последовательно дешифраторов 27, под- ключенньп : входами к выходам разрядов

счетчика 5, и элементов И 28.

Четвертый элемент ИЛИ 19 подсоединен первым входом к выходу второго элемента И 6 и подключен выходом к сум1 ир:ующему входу счетчика 5. Выход пятого элемента ИЛИ 20 соединен с

вычитающим входом счетчика 5. Первый вход шестого элемента ИЛИ 21 подсоединен к выходу первого элемента И 1 Выход третьего элемента И 23 подключен к второму, входу третьего элемент ИЛИ 8, выход седьмог о элемента ИЛИ 22 - к второму входу шестого элемента ИЛИ 21 и к второму входу четвертого элемента ИЛИ 19, Шестой эле- |Мент ИЛИ 21 подсоединен третьим входом к выходу пятого элемента ИЛИ 20 и соединен выходом с входом установки логического нуля четвертого триггера 18, выход которого подключен к первым входам элементов И 28 коррек- торов блоков 24 коррекции. Выход пер вого элемента И 1 соединен с первым . входом третьего элемента И 23, подсоединенного вторым входом к выходу третьего триггера 16.

Вход установки логического нуля третьего триггера 16 соединен с выходом переполнения счетчика 5, Вторые входы элементов И 28 корректоров каждого блока 24 коррекции подсоеди- нены к выходу одного из формирователей 14 импульсов информации. Выход элемента И 28 каждого корректора . /. блоков 24 коррекции подключен к второй входной шине 29 одного из форми- рователей 25 серий импульсов. Входы пятого элемента ИЛИ 20 подсоединены к выходным шинам 30 формирователей 25 серий импульсов одной половины корректоров каждого блока 24 коррекции. Входы седьмого элемента ИЛИ 22 соединены с выходными шинами 30 формирователей 25 серий импульсов другой половины корректоров каждого бло ка 24 коррекции,

Каждый формирователь 25 серии импульсов корректора блока 24 коррекции содержит первый, второй и третий D-триггеры 31-33, подсоединенные синхронизирующими входами к пер- вой входной шине 26, RS-триггер 34, соединенный входом установки логической едини1д 1 с второй вх одной шиной 29, и элемент И 35, подключенный выходом к выходной шине 30, Вы- ход RS-триггера 34 подключен к информационному входу первого D-триг- гера 31, соединенного выходом с первым входом элемента И 35 и с информационным входом второго В-триг гера 32. Прямой выход второго D-триг гера 32 подсоединен к информационному входу третьего D-триггера 33, сое

5 Ю t5 , 20

25 ЗО ..

5 0 5

5

диненного инверсным выходом с входом установки логического нуля RS-триггера 34, При этом второй вход элемента И 35 подсоединен к первой входной шине 26.

Устройство работает следующим об- разом.

Сигнал признака начала информации с выхода формирователя 4 признака начала информации, пройдя через первый элемент ИЛИ 3, устанавливает счетчик 5 в нулевое состояние. Этот сигнал проходит также через второй элемент ИЛИ 7 и подтверждает единичное состояние первого триггера 9, а также устанавливает второй триггер 10 в единичное состояние. При этом импульсы генератора 11 импульсов проходят через второй элемент И 6 и четвертый элемент ИЛИ 19 на счетчик 5, Разрядность счетчика 5 устанавливает- ся из условия, что его заполнение : происходит за время, равное расчетному периоду следования тактовых импульсов. Счетчик 5 обеспечивает срабатывание дешифратора 13, который устанавливает второй триггер 10 в нулевое состояние, а третий триггер 16 в единичное состояние. При этом каждый тактовый импульс с выхода источника 2 тактовых импульсов прохог, дит через первый элемент И I и первый элемент ИЛИ 3 и устанавливает счетчик 5 в нулевое состояние. Этот же тактовый импульс проходит через шестой элемент ИЛИ 21 и переводит четвертый триггер 18 в нулевое состояние. Уровень логического нуля с четвертого триггера 18 воздействует на элементы-И 28 всех корректоров каждого блока 24 коррекции, что обеспечивает запрещение коррекции восстановленных тактовых импульсов. Каждый тактовый импульс, кроме того, проходит через второй элемент ИЛИ 7 и подтверждает единичное состояние первого триггера 9, а также переводит задним фронтом второй триггер 10 в единичное состояние. Второй триггер 10 запрещает поступление тактовых импульсов с источника 2 тактовых импульсов через первый элемент И 1 до следующего срабатывания дешифратора 13.

Если тактовый импульс поступил до переполнения счетчика 5, то он проходит через первый элемент И 1, третий элемент И 23 и третий элемент

ИЛИ 8 на выходную шину 15 тактовых импульсов. Если тактовый импульс не поступш до переполнения счетчика 5, то импульс с выхода переполнения устанавливает третий трип ер 16 в нулевое состояние, а четвертый триггер 18 в единичное состояние и проходтгг через третий элемент ИЛИ 8 на выход- ьгую шину 15 тактовых импульсов,

Третий триггер 16 запрещает про- xoxgqeiiHe тактовых импульсов через третий элемент И 23, Четвер1Ъ1й триггер 18 воздействует на элементы И 28 всех корректоров калщого блока 24 ко рекции, что обеспечивает разрешение коррекции тактового интервата сигналов, поступаюа11их с формирователей 14 импульсов информации. В каждо. корректоре любого блока 24 коррекции информационный импульс соответствующего формирователя 14 ишчульсов информации при совпадении с сигналом соответствзтащего дешифратора 27 запускает соответству ювщй формирова- тель 25 серии импульсов. При этом в каждом фop шpoвaтeлe 25 серии импульсов его выходные импульсы синхронизированы импульсной последова- тельностью, поступающей с генерато- ра 11 импульсов.

В варианте формирователя 25 серии импульсов (фиг.2} импульс с элемента И 28 устанавливает RS-триггер 34 в едд1Ничное : остояние5 а им- пульс генератора 1 I И1-1Гсульсов своим задним фронтом устанав.гмвает первьй В триггер 31 в един 1чное cocroHHiie, который разрешает прохождение импульсов генератора 1 и myльcoв че- рез элемент И 35. Второй и третий импульсы генератора 11 импульсов устанавливают второй 32 и третий 33 D-триггеры в единичное состояние. Третий D-триггер 33 устанавливает КЗ-триггер 34 в нулевое состояние. Четвертый импульс генератора 11 импульсов проходит через элемент И 35 и своим задним фронтом устанавливае в нулевое состояние первый 1)триг- гер 31.

Серии импульсов с формирователей 25 серий импульсов одной половины корректоров каждого блока 24 коррекции через пятый элемент ИЛИ 20 пос- тупают на счетчик 5, увеличивая для- тельность тактового интервала. Серии импульсов с формирователей 25 серий

импульсов другой полови гы корректоров каждого блока 24 корре сиии проходят через седьмой элемент 1-ШИ 22 и четвертый элемент ШШ 19 на счетчик 55 уменьшая длительность тактового интервала. Формирователи 25 се- p lii f нмпз льсов через шестой элемент ИЛИ 21 воздействуют также на четвертый т Л1Ггер 18, который с но- ,ыо элементов И 28 запрещает кор- рекцмю тактового интервала до следующего импульса переполнения счетчика 5.

Счетчик 5 продолжает подсчет инаульсов, поступающих с генератора 1 импул:ьсов, и через заданньй интервал времени от момента его переполнения вызывает срабатывание дополнительного дешифратора 17, который через второй элемент ШШ 7 подтвер- лсдар.т единичное состояние первого триггера 9 и устанавливает в еди- гшчпоз состояние второй триггер 10, Последний запрещает прохождение через первый элемент И 1 тактовых импульсов источ шка 2 до следующего срабатывания дешифратора 13.При этом формироват(1пь )2 признака конца информации устанавливает в нулевое состояние первый триггер 9, который запрещает поступление импульсов генератора 1 импульсов через второй элемент И б и четвертый элемент ИЛИ 19 на счетчик 5, прекращая работу устройства.

Ф о р м у л а изобретения

1. Устройство для восстановления в оспроизведенных тактовых импульсов с:одер5 ;ащее первый элемент И, подсоединенный первым входом к выходу ис- точлика тактовых иьшульсов и подключенный выходом к первому входу первого элемента ИШ, соединенного вторым вх:одом с выходом формирователя признака начала информации и подключенного выходом к входу установки логического нуля счетчика и к первому входу второго элемента ИЛИ, соединенного выходом с входами установ- килогической единш, первого и второго триггеров, второй элемент И, нодсоединенный первым и вторым входами к перво1-гу выходу генератора импульсов, и к выходу первого триггера, соединенного входом установки логического нуля с выходом формирователя признака конца информации, третий элемент ИЛИ, подключенный выходом к выходной шине тактовых импульсов и подсоединенный первым входом к выходу йереполнения счетчика,соединенного выходами разрядов с входами дешифратора, выход которого подключен к входу установки логического нуля второго триггера, соединенного инверсным выходом с вторым входом первого элемента И, и формирователи импульсов информации, отличающееся тем, что, с целью повышения точности восстановления воспроизведенных тактовых импульсов, в него введены третий .триггер, соединенный входом установки логической единицы с выходом дешифратора, дополнительный дешифратор, включенный между выходами разрядов счетчика и вторым входом второго элемента НЛИ, четвертый триггер, подсоединенный входом установки логической единицы к выходу переполнения счетчика, четвертый элемент ИЛИ, под25 седьмого элемента ИЛИ соединены выходными шинами формирователей серий импульсов другой половины ректоров каждого блока коррекции 2. Устройство поп,1,отли

соединенный первым входом к вых оду второго элемента И и подключенный выходом к суммирующему входу счетчика, пятый элемент ИЛИ, соединенный выхо- зо чающееся тем, что каждый дом с вычитающим входом счетчика, шестой элемент ИЛИ, подсоединенный первым входом к выходу первого элемента И, третий элемент И, подклюформирователь серии импульсов кор ректора блока коррекции содержит первый, второй и третий D-триггер подсоединенные синхронизирующими

ченный выходом к второму входу треть--, входами к первой входной шине, RSего элемента ИЛИ, седьмой элемент ИЛИ, подключенный выходом к второму входу шестого элемента ИЛИ и к второму входу четвертого элемента ИЛИ, и блоки коррекции, каждый из которых 0 выполнен в виде корректоров, состоящих из формирователей серий им- пулЬсов, подсоединенных первыми входными шинами к второму выходу гене- ратора импульсов,и из соединенных пос- 45 ледовательно дешифраторов, подключенных входами к выхода м разрядов счетчика,, и элементов И, причем шестой элемент ИЛИ подсоединен третьим входом к выходу пятого элемен- Q

триггер, соединенный входом установ ки логической единицы с второй вход ной шиной, и элемент И, подключенный выходом к выходной шине, причем выход RS-триггера подключен к инфор мационному входу первого D-триггера соединенного прямым выходом с первым входом элемента И и .с информационным входом второго D-триггера, прямой выход которого подсоединен к информационному входу третьего D- .триггера, соединенного инверсным вы

т Г-ходом с входом установки нуля RS-триг гера, а второй вход элемента И подсоед нен к первой входной шине.

та ИЛИ и соединен выходом с входом установки логического нуля четверто го триггера, подключенного выходом к первым входам элементов И корректоров блоков коррекции, выход первого элемента И соединен с первым входом третьего элемента И, подсоединенного вторым входом к выходу

третьего триггера, вход установки логического нуля которого соединен с выходом переполнения счетчика, вторые входы элементов И корректоров -,каждо го блока коррекции подсоединены к выходу одного из формирователей импульсов информации, выход элемента И каждого корректора блоков коррекции подключен к второй входной шине одного из формирователей серий импульсов, входы Пятого элемента ИЛИ подсоединены к выходным шинам формирователей серии импульсов одной половины корректоров каждого блока коррекции, а входы

седьмого элемента ИЛИ соединены с выходными шинами формирователей серий импульсов другой половины корректоров каждого блока коррекции. 2. Устройство поп,1,отличающееся тем, что каждый

чающееся тем, что каждый

формирователь серии импульсов корректора блока коррекции содержит первый, второй и третий D-триггеры, подсоединенные синхронизирующими

триггер, соединенный входом установки логической единицы с второй входной шиной, и элемент И, подключенный выходом к выходной шине, причем выход RS-триггера подключен к информационному входу первого D-триггера, соединенного прямым выходом с первым входом элемента И и .с информационным входом второго D-триггера, прямой выход которого подсоединен к информационному входу третьего D- .триггера, соединенного инверсным выт Г-ходом с входом установки нуля RS-триггера, а второй вход элемента И подсоединен к первой входной шине.

35

30

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для многоканальной записи-воспроизведения информации | 1985 |

|

SU1273992A1 |

| Устройство для магнитной записи-воспроизведения звуковых сигналов | 1986 |

|

SU1339637A1 |

| Устройство отсчета интервалов времени | 1982 |

|

SU1103228A1 |

| Устройство для многоканальной магнитной записи и воспроизведения последовательности импульсов | 1987 |

|

SU1483482A1 |

| Устройство для измерения мгновенного хода часов | 1985 |

|

SU1365044A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1986 |

|

SU1327174A1 |

| Устройство для ввода информации | 1989 |

|

SU1695314A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1247828A2 |

| Устройство для записи-воспроизведения многоканальной информации | 1984 |

|

SU1190410A1 |

| Устройство для защиты и автоматического отключения потребителя | 1985 |

|

SU1339722A1 |

Изобретение относится к области накопления информации, а именно к устройствам л,пя восстановления воспроизведенных тактовых импульсов. Цель изобретения - повьшение точности восстановления воспроизведенных тактовых импульсов. Устройство содержит элементы И 1 и 6, источник 2 тактовых импульсов, элементы ИЛИ 3, 7 (Л Is9 i СА9 фиг.1

Редактор В.Петраш

Составитель Ю.Розенкранц

Техред М.Ходанкч Корректор И.Муска

Заказ 3710/51Тираж 543Подписное

ВНИИГМ Государственного комитета СССР

по делам изобретений и открьпий 113035, Москва, Ж-35, Раушская наб,, д.4/5

Производственно-полиграфическое предприятие,, г .Ужгород ,ул. Проектная, 4

Фиг. 2

| Устройство для восстановления импульсов синхронизации при воспроизведении цифровой информации | 1977 |

|

SU678513A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для восстановления тактовых импульсов | 1984 |

|

SU1153348A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-07-07—Публикация

1984-11-06—Подача