мутатора констант дополнений, к информйционному входу которого подключен выход регистра констант дополнений, выход второго коммутатора текущих интервалов и коммутатора констант дополнений через блок элементов ИЛИ подсоединены к первому информационному входу блока памяти, выход первого элемента ИЛИ соединен с первым входом первого элемента И, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения вьщачи одиночных временных интервалов, в него введены триггер цикла, триггер запрета, два элемента И и второй элемент ИЛИ, причем первый вход второго

элемента И соединен с выходом разряда переполнения регистра суммы, второй вход второго элемента И подключен к выходу триггера запрета, информационный вход которого подключен к выходу блока памяти, выход второго элемента И соединен с управлякнцим входом коммутатора адреса, выход блока сравнения и выход третьего элемента И через второй элемент ИЛИ подключены к второму информационному входу блока памяти, первьй вход третьего элемента И подключен к выходу триггера цикла, информационный вход которого подключен к выходу блока памяти, второй вход третьего элемента И соединен с выходом первого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство отсчета интерваловВРЕМЕНи | 1979 |

|

SU807286A1 |

| Устройство для редактирования информации | 1981 |

|

SU980099A1 |

| Многоканальное устройство для формирования временных интервалов | 1980 |

|

SU932603A1 |

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1987 |

|

SU1540025A1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Устройство для определения интервалов стационарности дискретного случайного процесса | 1984 |

|

SU1198540A1 |

| Устройство для контроля блоков памяти | 1991 |

|

SU1833920A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для управления блоком памяти | 1982 |

|

SU1164718A1 |

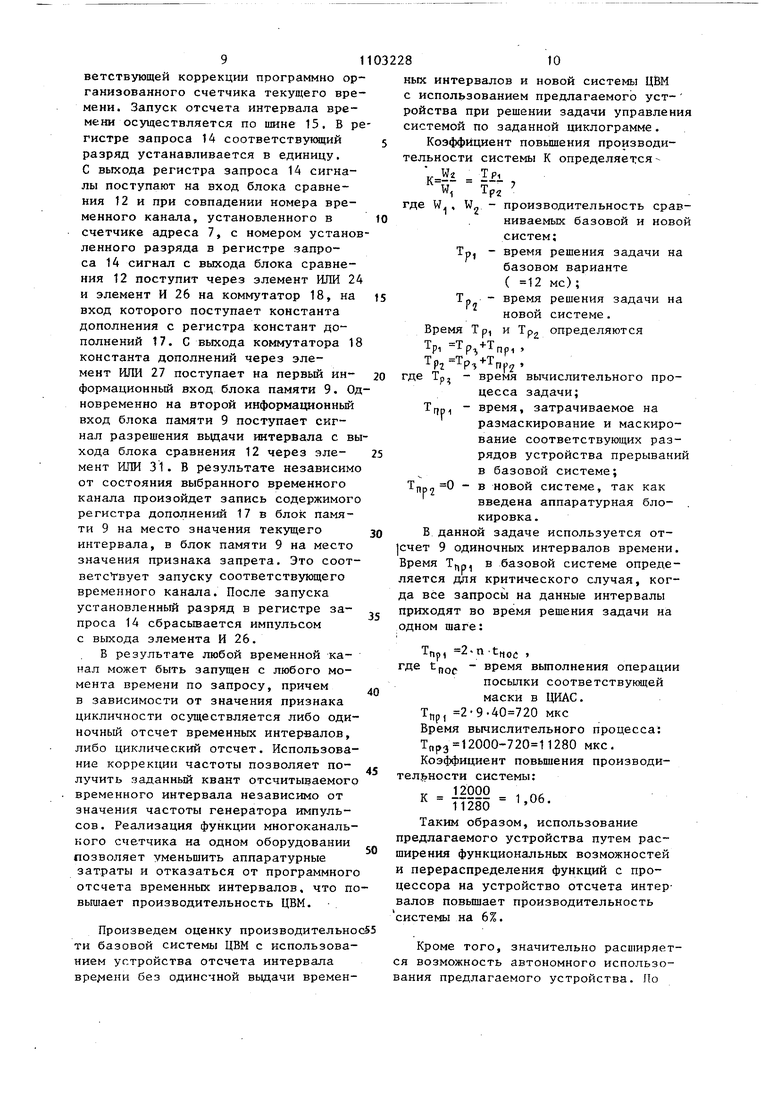

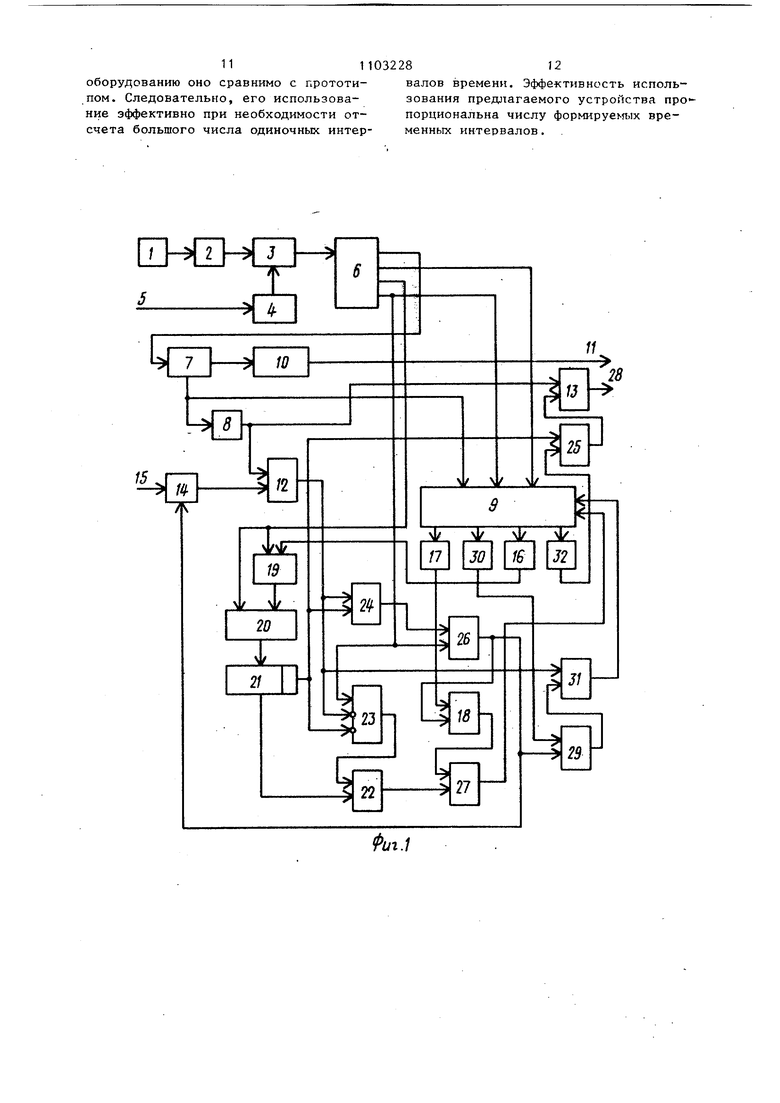

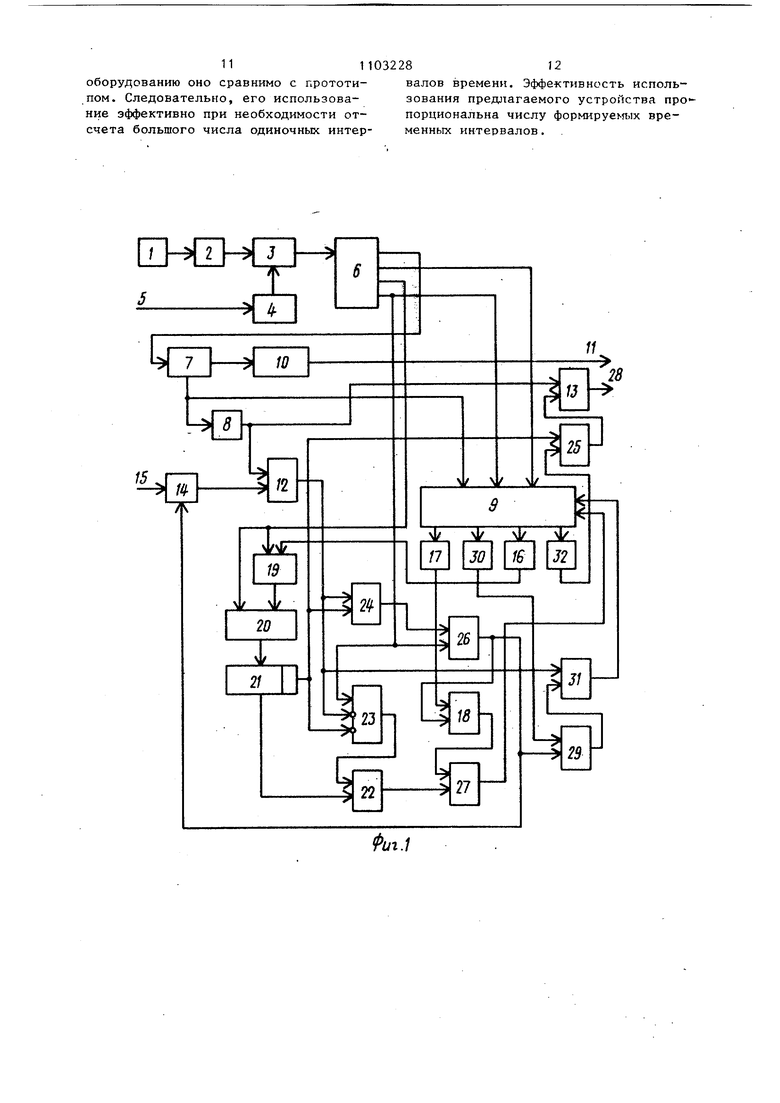

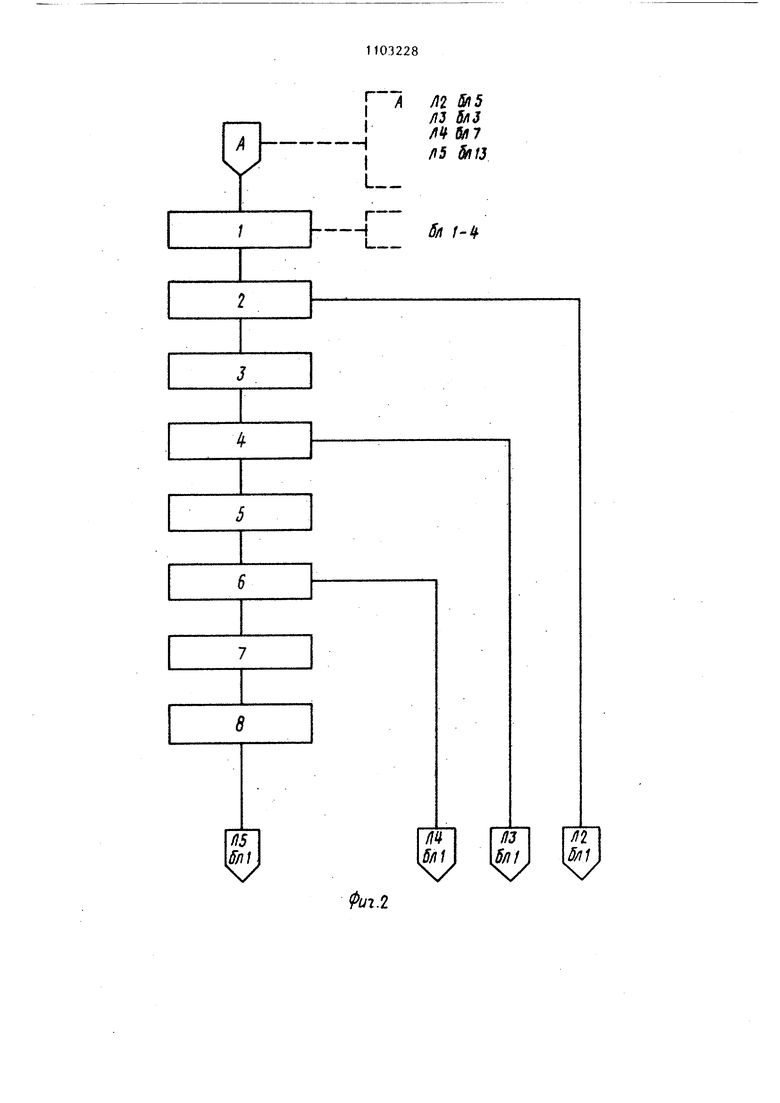

УСТРОЙСТВО ОТСЧЕТА ИНТЕРВАЛОВ ВРЕМЕНИ, содержащее генератор импульсов, делитель частоты, счетчик текущего времени, регистр коррекции, корректор частоты, формирователь серии импульсов, счетчик адреса, дешифратор, регистр запроса-, блок сравнс.ккя, блок памяти, коммутатор адреса, регистр текущих интервалов, регистр констант дополнений, первый коммутатор текущих интервалов, сумматор, регистр суммы, элемент И, элемент запрета, второй коммутатор текущих интервапов, блок элемента ИЛИ и элемент ИЛИ, причем выход делителя частоты соединен с входом занесения частоты корректора частоты, вход коррекции частоты которого подключен к выходу регистра коррекции, вькод корректора частоты соединен с входом формирователя серии импульсов, первый выход которого соединен со счетным входом счетчика адреса, выход переполнения которого соединен со счет. I БйЬЛИ01.к, ным входом счетчика текущего времени, выход счетчика адреса соединен с адресным входом блока памяти и с входом дешифратора, выход которого подключен к информационному входу коммутатора адреса и первому входу блока сравнения, второй вход которого соединен с выходом регистра запроса, второй выход формирователя серии импульсов подключен к входу чтения блоки памяти, выходы которого подключены к входам регистра констант дополнений и регистра текущих интервалов, выход которого подключен к первому входу первого коммутатора текущих интервалов, к второму входу которого и к первому входу сумматора подключен (Л третий выход формирователя серии импульсов, к второму входу сумматос ра подключен- выход первого коммутатора -текущих интервалов, выход сумматора соединен с информационным входом регистра суммы, выход которого соединен с информационным входом второго коммутатора текущих интервалов, выход э :/s разряда переполнения регистра суммы соединен с первым входом первого мента ИЛИ и первым инверсным входом ю эо элемента запрета, выход блока сравнения подключен к второму входу первого элемента ИЛИ и к второму инверсному входу элемента запрета, выход которого соединен с управлякщим входом второго коммутатора текущих интервалов, четвертый выход формирователя серии импульсов подключен к входу записи блока памяти, к третьему входу элемента запрета и к второму входу первого элемента И, выход которого соединен с входом сброса регистра запроса и с управляющим входом ком

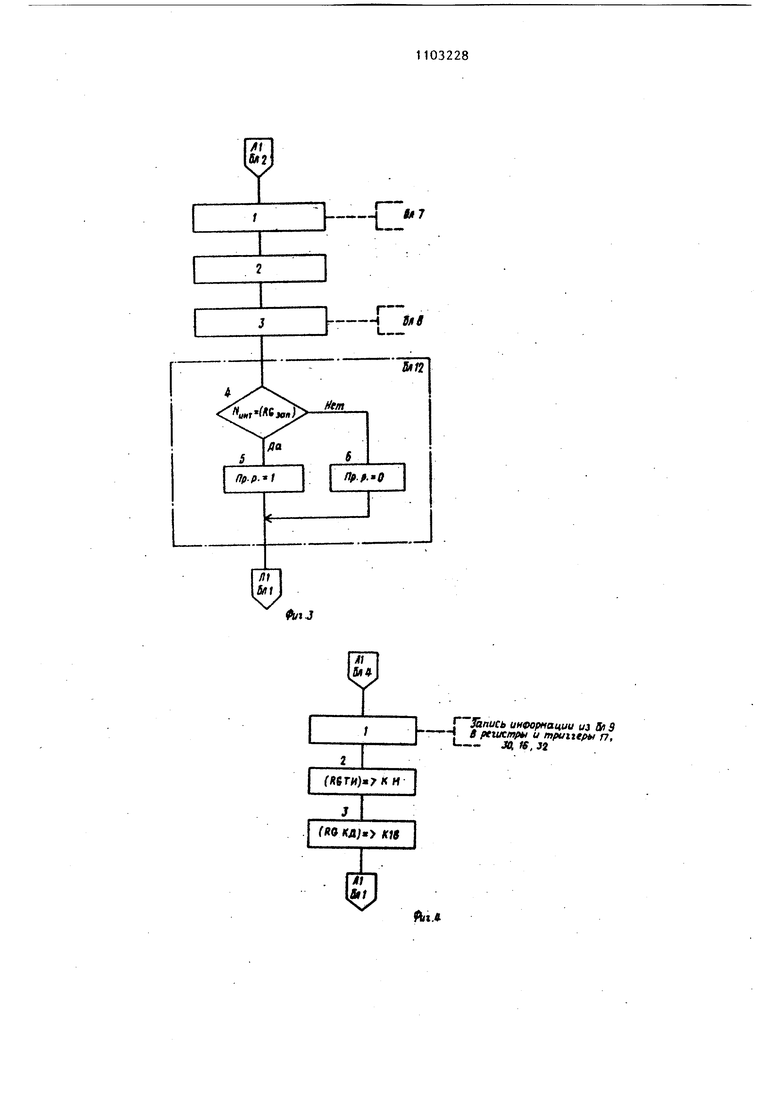

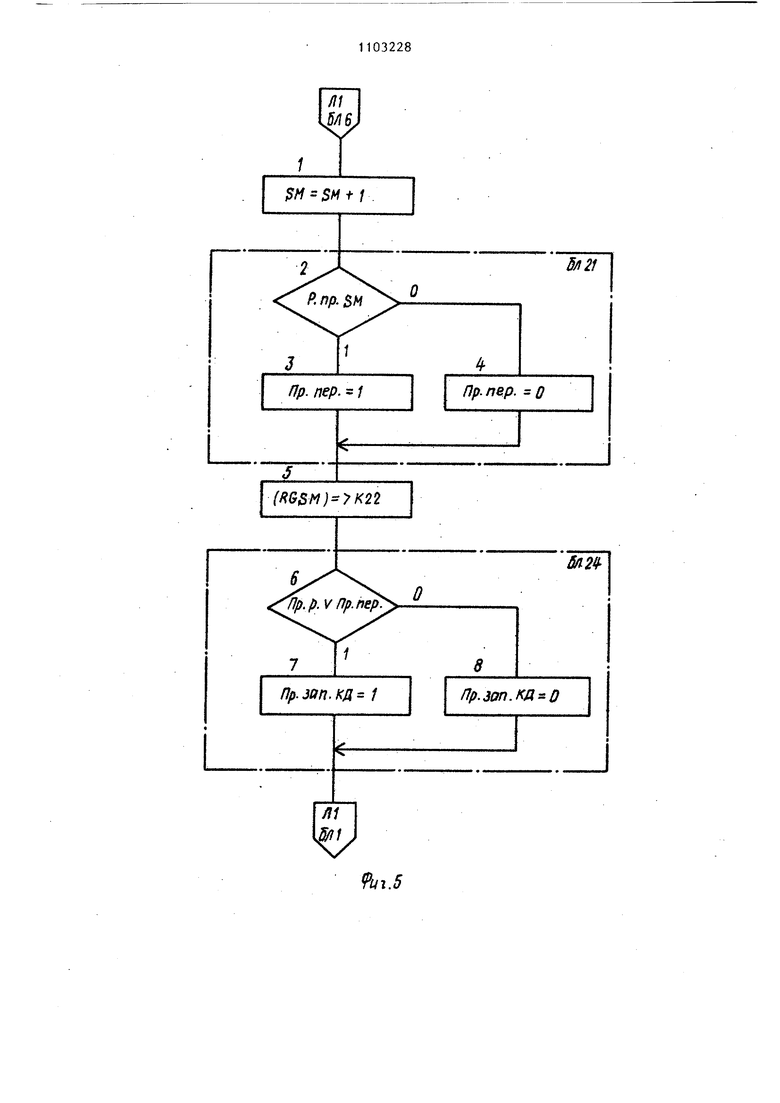

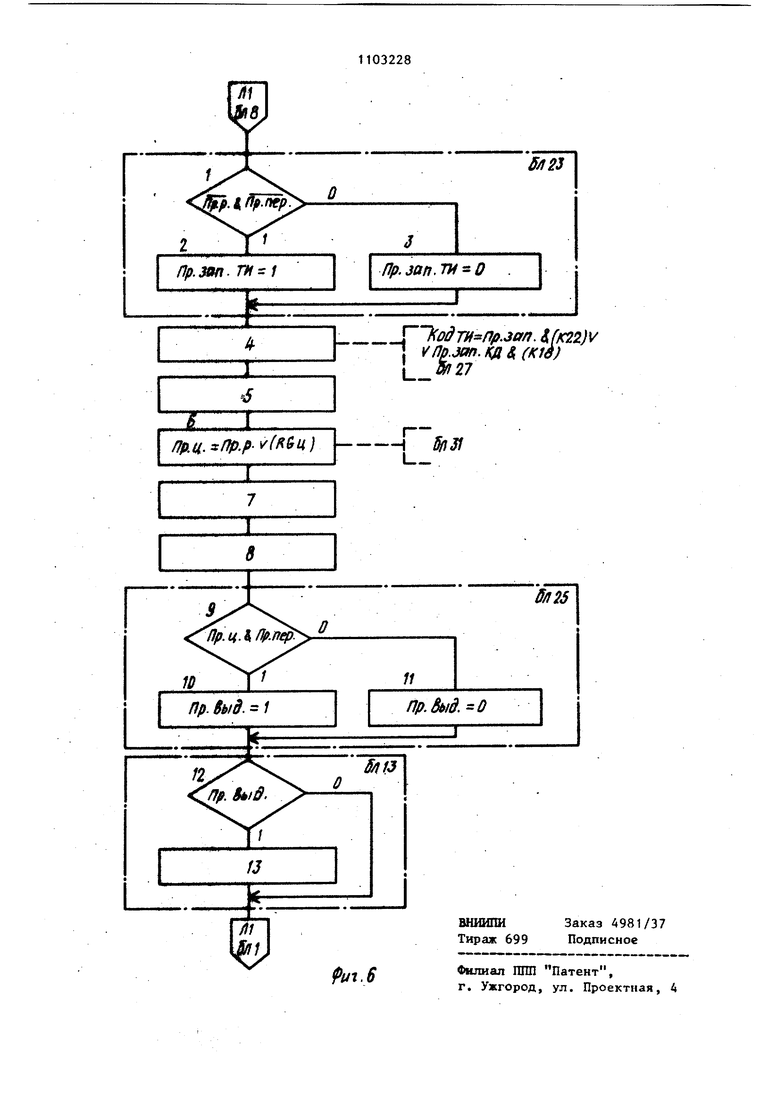

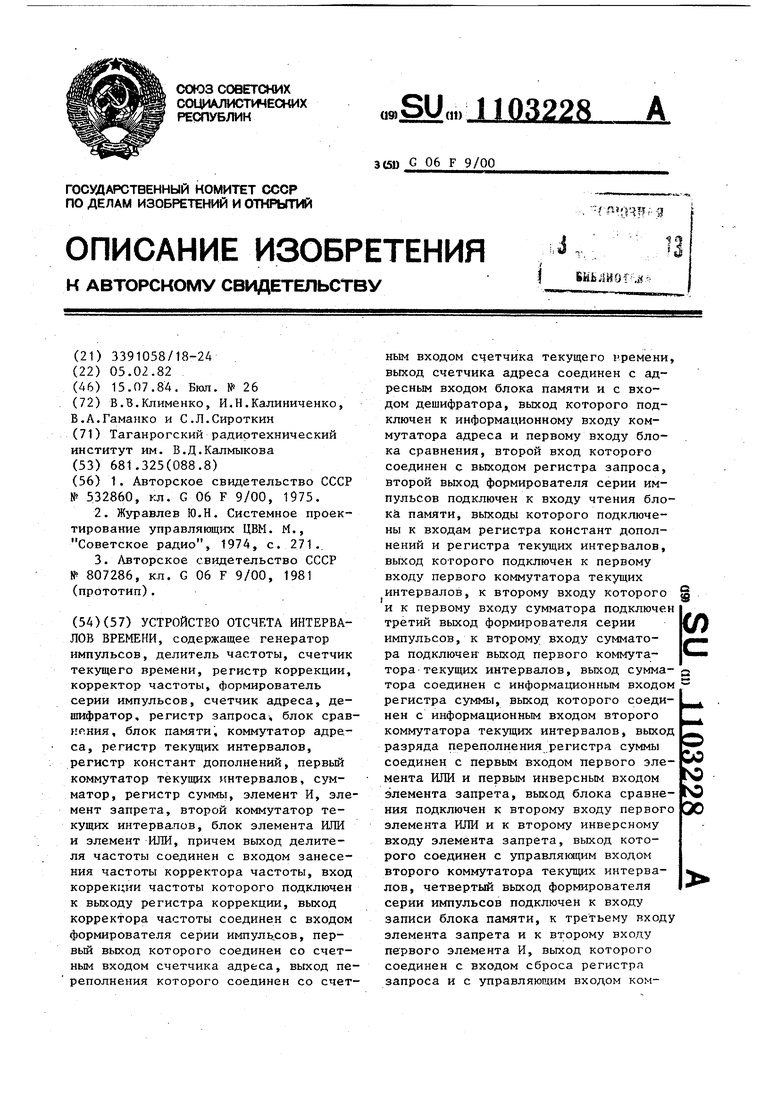

Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах -и системах для управления вычислительнь1М процессом в реальном масштабе времени.

Известно программное временное устройство, содержащее генератор импульсов и последовательно соединенные счетчик импульсов, блок набора программы, дешифратор, элементы И R исполнительные элементы, несимметричный триггер и инвертор Q .

Недостатком известного устройства является то, что интервалы времени, отсчитываемые устройством, синхронны так как используется один а ппаратурный счетчик, отсутствует коррекция частоты.

Известно временное устройство, содержащее генератор импульсов, счетчик времени, узлы связи, линию задержки, блоки прерывания, коррекции, обнуления, запроса текущего интервала, элемент Р1ПИ, элемент совпадения, программные сумматор и таймер 21.

Недостатком этого счетчика единог времени является то, что коррекция осуществляется с помощью импульсов единого времени, отсчет интервалов времени - программным путем в процессоре в результате снижается производительность вычислительной машины.

Наиболее близким к изобретению является устройство, содержащее гене ратор импульсов, делитель частоты, счетчик текущего времени, регистр коррекции, корректор частоты, формирователь серии импульсов, счетчик адреса, дешифратор, регистр запроса, блок сравнения, блок памяти, коммутатор адреса, регистр текущих интервалов, регистр констант дополнений, первый коммутатор текущих интервалов сумматор, регистр суммы, элемент И, элемент запрета, второй коммутатор текущих интервалов, коммутатор констант дополнений, блок ИЛИ и элемент ШШ, причем выход дел-ителя частоты соединен с входом занесения частоты корректора, частоты, вход коррекции частоты которого подключен к выходу регистра коррекции, выход корректора .частоты соединен с входом формирователя серии импульсов, первы выход которого соединен с входом счетчика адреса, выход переполнения которого соединен с входом счетчика текущего времени, выход счетчика адреса соединен с адресным входом блока памяти и с входом дешифратора, выход которого подключен к информационному входу коммутатора адреса и первому входу блока сравнения, второй вход которого соединен с выходом регистра запроса, второй выход формирователя серии импульсов подключен к входу чтения блока памяти, выходы которого подключены к входу регистра констант дополнений и регистра текущих интервалов, выход которого подключен к информационному входу перво го коммутатора регистра интервалов, к управляющему входу которого и к управляющему входу сумматора подключен третий выход формирователя серии импульсов, к информационному входу сумматора подключен выход первого коммутатора текущих интервалов, выхо сумматора соединен с входом регистра суммы, выход которого соедине с информационным входом второго коммутатора текущих интервалов, выход разряда переполнения регистра суммы соединен с управляющим входом коммутатора адреса, вторым входом элемента ИЛИ и вторым инверсным входом элемента запрета, выход блока сравнения подключен к первому входу элемента ИЛИ и к первому инверсному входу элемента запрета, выход которо го соединен с управлякяцим входом второго коммутатора текущих интервалов, четвертый выход формирователя серии импульсов подключен к входу записи блока памяти,, к третьему вхо ду элемента запрета и второму входу элемента И, выход которого соединен с входом сброса регистра запроса и с управляющим входом коммутатора констант дополнений, к информационному входу которого подключен выход регистра констант дополнений, выходы второго коммутатора текущих интервалов и коммутатора констант дополнений через блок РШИ подсоединены к информационному входу блока памяти, выход элемента ИЛИ соединен с первым входом элемента И з. Недостатком известного устройства является отсутствие возможности формирования одиночных интервалов време ни, что требует дополнительных затрат мащинного времени для организа ции блокировки формируемой устройст вом циклической последовательности временных интервалов. Цель изобретения - расширение 1функциональнь1х возможностей путем обеспечения выдачи одиночных времен ных интервалов по каналам наряду с циклической выдачей временных интервалов. Поставленная цель достигается тем, что в устройство отсчета интервалов времени, содержащее генератор импульсов, делитель частоты, счетчик текущего времени, регистр коррекции, корректор частоты, формирователь серии импульсов, счетчик адреса, дешифратор, регистр запроса, блок сравнения, блок памяти, коммутатор адреса, регистр текущих интервалов, регистр констант дополнений, первый коммутатор текущих интервалов, сумматор, регистр суммы, элемент И, элемент запрета, второй коммутатор текущих интервалов, блок элементов ИЛИ и элемент ИЛИ, причем выход делителя частоты соединен с входом занесения частоты корректора частоты, вход коррекции частоты которого подключен к выходу регистра коррекции, выход корректора частоты соединен с входом формирователя серии импульсов, первый выход которого соединен со счетным входом счетчика адреса, выход переполнения которого соединен со счетным входом счетчика текущего времени, выход счетчика адреса соединен с адресным входом блока Цамяти и с входом дешифратора, выход которого подключен к информационному входу коммутатора адреса и первому входу блока сравнения, второй вход которого соединен с выходом регистра запроса, второй выход формирователя серии импульсов подключен к входу чтения блока памяти, выходы которого подключены к входам регистра констант дополнений и регистра текущих интервалов, выход которого подключен к первому входу первого коммутатора текущих интервалов , к второму входу которого и к первому входу сумматора подкючен третий выход формирователя серии импульсов, к второму входу сумматора подключен выход первого коммутатора текущих интервалов, выход сумматора соединен с информационным входом регистра суммы, выход которого соединен с информационным входом второго коммутатора текущих интервалов, выход разряда переполнения регистра суммы соединен с первым входом первого элемента ИЛИ и первьич инверсным входом элемента запрета, выход блока сравнения подключен к второму входу первого элемента ИЛИ и к второму инверсному входу элемента запрета, выход которого соединен с управляющим входом второго коммутатора теку щих интервалов, четвертый выход фор мирователя серии ш-1пульсов подключе к входу записи блока памяти, к трет ему входу элемента запрета и к второму входу первого элемента И, вых которого соединен с входом сброса регистра запроса и с управляющим входом коммутатора констант дополнений, к информационному входу кото рого подключен выход регистра констант дополнений, вьпсоды второго коммутатора текущих интервалов и ко мутатора констант дополнений через блок элементов ИЛИ подсоединены к первому информационному входу бло ка памяти, выход первого элемента ИЛИ соединен с первым входом пер вого элемента И, введены триггер цикла, триггер запрета, два элемента И и второй элемент ИЛИ, причем первый вход второго элемента И соединен с выходом разряда переполнени регистра суммы, второй вход второго элемента И подключен к выходу триггера запрета, информационный вход которого подключен к выходу блока п мяти, выход второго элемента И соединен с управляющим входом коммутат ра адреса, выход блока сравнения и выход третьего элемента И через второй элемент ИЛИ подключены к вт рому информационному входу блока па мяти, первый вход третьего элемента И подключен к выходу триггера ци ла, информационный вход которого подключен к выходу блока памяти, второй вход третьего элемента И сое динен с выходом первого элемента И. На фиг. 1 представлена функциональная схема устройства отсчета интервалов времени; на фиг. 2-6 блок-схема алгоритма работы устройс ва. Устройство содержит генератор 1 импульсов, делитель 2 частоты, корректор 3 частоты, регистр 4 коррекции, вход 5 коррекции устройства, формирователь 6 серии импульсов, счетчик 7 адреса, дешифратор 8, блок 9 памяти, счетчик 10 текущего времени, выход 11, блок 12 сравнения, коммутатор 13 адреса, регистр запроса, вход 15, регистр 16 текуощк интервалов, регистр 17 констант дополнений, коммутатор 18 констант дополнений, коммутатор 19 текущих интервалов, сумматор 20, регистр 21 ы, коммутатор 22 текущих интеров, элемент 23 запрета, элеменЛИ 24, 25, элемент И 26, блок 27 ентов ИЛИ, адресный выход 28, ент И 29, триггер 30 цикла, элеШШ 31, триггер 32 запрета. асшифровка сокращений на блоке алгоритма следующая: ХС - хронирующая серия; инт номер интервала; RG,jg,f, - регистр запроса (бл 14); (ЕС-,дп) содержимое регистра запроса; Пр.р. - признак равенства номеров интервалов, формируемых бл 18, и запрашиваемого по шине 15; KSM - первый коммутатор текущин интервалов (бл 19); RG ТИ - регистр текущего интервала (бл. 16); RG КД - регистр кода дополнений (бл 17); К 18 - коммутатор 18; P.np.SM - разряд переполнения сумматора; Пр.пер. - признак переполнения сумматора (бл 21); К 22 - коммутатор 22; р.зап.КД - признак записи кода дополнения; р.зап.ТИ - признак записи кода текущего интервала; Код ТИ - код текущего интервала, поступающий в блок памяти 9; Пр. ц - признак цикличности; RG у - регистр цикла (бл 30); Пр.выд. - признак выдачи информации по шине 28 через коммутатор 13. стройство работает следующим зом. регистр коррекции 4 заносится танта коррекции по входу 5, кото определяется исходя из требовак частоте заполнения счетчиков ени. Генератор 1 вырабатывает ную частоту, которая через дели2 поступает на вход корректо. В корректоре 3 осуществляется ическое сложение константы кории, он позволяет изменять частоту ирования тактовых импульсов раммным путем. Сигналы переполнения с выхода кор ректора 3 вьщаются с частотой, которая требуется для работы счетчика адреса 7, В формирователе серии импульсов -6 по приходу каждого импульса с корректора 3 вырабатывается рас пределенная во времени серия импульсов для управления устройства. Импульс с первого выхода формирователя серии импульсов 6 поступает на вход счетчика адреса 7, где формируется адрес интервала, который поступает на адресньй вход блока памяти 9. При приходе импульсов с второго выхода формирователя серии импульсов 6 на вход чтения блока памяти 9 происходит считывание значения временного интервала в регистр,текущих,интервалов 16, признака запрета в триггер запрета 32, кода константы дополнения в регистр констант дополнений и признака цикличности в триггер цик ла 30. Код текущего интервала поступает на информационньй вход коммутатора текущих интервалов 19, с приходом импульса с третьего выхода формирователя серии импульсов 6 происхо дит суммирование значения текущего интервала с единицей в сумматоре 20 и образуется новое значение текущего интервала, которое записывается в ре гистр суммы 21. Если не закончен отсчет интервалов, то в разряде переполнения регистра суммы 21 будет ноль. Импульс с четвертого выхода формирователя серии импульсов 6 через элемент запрета 23, при отсутствии сигнала запроса с блока сравнения 12, откроет коммутатор 22 и через блок 27 код текущего интервала поступает на первый информационньй вход блока памяти 9. Одновременно импульс с четвертого выхода формирователя серии импульсов 6 поступает на вход записи блока памяти 9 и происходит запись нового значения текущего интервала. Если закончен отсчет интервалов, то сигнал с выхода разряда переполнений регистра суммы 21 запретит прохождение импульса через элемент запрета 2 и через элемент ИЛИ 24 откроет элемент И 26. На второй вход элемента И 26 приходит сигнал с четвертого выхода формирователя серии импульсов 6. Сигнал с выхода элемента И 26 открывает коммутатор 18 и через блок элементов ИЛИ 27 на первый информаци онный вход блока памяти 9 поступает значение кода константы дополнения с регистра дополнений 17. Сигнал с выхода элемента И 26 также открывает элемент И 29 и через элемент ИЛИ 31 на второй информационный вход блока памяти 9 поступает значение признака цикличности с триггера цикла 30. Нулевое состояние триггера цикла 30 соответствует вьщаче единичного интервала, а единичное состояние - циклической выдаче интервалов. Соответствующее состояние триггера цикла 30 записывается на место признака запрета в блоке памяти 9. Одновременно сигнал с четвертого вьгхода формирователя серии импульсов 6 поступит на вход записи блока памяти 9, где на место значения текущего интервала и признака запрета запишется константа дополнения и признак цикличности. Сигнал с разряда переполнения регистра суммы 21 при отсутствии запрета с триггера запрета 32 через элемент 25 поступит на управляющий вход коммутатора адреса 13, на информационный вход которого приходят сигналы, указывающие номер временного канала с выходов дешифратора 8. Сигнал с выхода коммутатора адреса 13 поступает на выход 28 для связи с устройством управления вычислительной машины и указывает номер временного канала, которые закончил отсчет интервала времени. Сигнал в триггер запрета 32 поступает из блока памяти 9. На этом работа первого временного канала устройства заканчивается. При приходе следующего импульса с корректора частоты 3 на вход формирователя серии импульсов 6 значение счетчика адреса 7 увеличивается на единицу. Работа второго временного канала происходит аналогично работе первого канала. Число временных каналов устройства где К - разрядность счетчика адреса 7. При переполнении счетчика адреса 7 с выхода .переполнения на вход счетчика текущего времени поступит импульс увеличивакщий его содержание на единицу. Информация о текущем времени может сниматься со счетчика текущего времени 10, а младшие разряды со счетчика адреса 7. При переполнении счетчика текущего времени 10 по шине 11 выдается сигнал, который поступает в устройство управления ЦВМ для соот91103228ветствующей коррекции программно организованного счетчика текущего времени. Запуск отсчета интервала времени осуществляется по шине 15, В регистре запроса 14 соответствующий разряд устанавливается в единицу. С выхода регистра запроса 14 сигналы поступают на вход блока сравнения 12 и при совпадении номера временного канала, установленного в счетчике адреса 7, с номером установленного разряда в регистре запроса 14 сигнал с выхода блока сравнения 12 поступит через элемент ИЛИ 24 и элемент И 26 на коммутатор 18, на вход которого поступает константа дополнения с регистра констант дополнений 17. С выхода коммутатора 18 константа дополнений через элемент ИЛИ 27 поступает на первый информационный вход блока памяти 9. Одновременно на второй информационный вход блока памяти 9 поступает сигнал разрешения вьщачи интервала с выхода блока сравнения 12 через эле- 25 мент ИЛИ 31. В результате независимо от состояния выбранного временного канала произойдет запись содержимого регистра дополнений 17 в блок памяти 9 на место значения текущего интервала, в блок памяти 9 на место значения признака запрета. Это соответствует запуску соответствукэдего временного канала. После запуска установленный разряд в регистре запроса 14 сбрасьшается импульсом с выхода элемента И 26. В результате любой временной канал может быть запущен с любого момента времени по запросу, причем в зависимости от значения признака цикличности осуществляется либо одиночньй отсчет временных интервалов, либо циклический отсчет. Использование коррекции частоты позволяет получить заданный квант отсчитываемого временного интервала независимо от значения частоты генератора импульсов . Реализация функции многоканального счетчика на одном оборудовании позволяет уменьшить аппаратурные затраты и отказаться от программного отсчета временных интервалов, что повьгаает производительность ЦВМ.

Произведем оценку производительнос§5 ти базовой системы ЦВМ с использованием устройства отсчета интервала без одиночной вьщачи временныс ро си те гд 20 гд |сч Бр ля да пр од те пр ши и це ва си

Кроме того, значительно расширяется возможность автономного использования предлагаемого устройства. Но интервалов и новой системы ЦВМ спользованием предлагаемого устства при рещении задачи управления темой по заданной циклограмме. Коэффициент повышения производиьности системы К определяется Ws: IP, , - 7 W , W,, - производительность сравниваемых базовой и новой систем; время решения задачи на базовом варианте ( 12 мс); время решения задачи на новой системе. Бремя Тр, и Т определяются Tpi Tp +Tnpi , - время вычислительного процесса задачи; время, затрачиваемое на размаскирование и маскирование соответствующих разрядов устройства прерываний в базовой системе; 0 - в новой системе, так как введена аппаратурная блокировка . В данной задаче используется отт 9 одиночных интервалов времени. мя , в базовой системе опредется для критического случая, когвсе запросы на данные интервалы ходят во время решения задачи на ом шаге: Tnpi -2- п пос - время вьтолнения операции посьшки соответствукнцей маски в ЦИАС. , 2-9-40 720 МКС Время вычислительного процесса: Тпрз 12000-720 11280 мкс. Коэффициент повьш1ения производи| ности системы: К 1,06. Таким образом, использование длагаемого устройства путем расения функциональных возможностей ерераспределения функций с просора на устройство отсчета интеров повышает производительность темы на 6%.

оборудованию оно сравнимо с гфототипом. Следовательно, его использование эффективно при необходимости отсчета большого числа одиночных интервалов времени. Эффективность использования предлагаемого устройства пропорциональна числу формируемых временных интервалов.

1

т

П5 Sfll

y

Л2S/15

/}36л S

/fifSfl7

/15S/H3

L

Sfl /I

y/j

l

h-i.

ft/iJ

l«7

I )«7KH I

fw кл;« /ifw

J Jant/гь информации из SaB 8 реиктры и тринеры n,

«- 30, IS, зг

A(i.«

Piii.5

S/I23

., .зап. fK22)V

I vnp.Jon. КД 4 (К1в)

I

/.U.ynp. Л

I

L 27

I

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Программное временное устройство | 1974 |

|

SU532860A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Системное проектирование управляющих ЦВМ | |||

| М., Советское радио, 1974, с | |||

| Искроудержатель для паровозов | 1920 |

|

SU271A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-15—Публикация

1982-02-05—Подача