ми к выходам блока элементов дифференцирования, подсоединенного входами к входам третьего элемента ИЛИ и к выходам дешифратора, выполненного с числом выходов, равным числу каналов, и соответствую1цими выходами соединенного с входами соответствующих элементов И, отдельные входы заданных элементов И подключены к одному из входов первого элемента ИЛИ, к первой управляющей шине, к первому входу второго триггера, к одному из входов блока элементов дифференцирования и третьего элемента ИЛИ, отдельными входами подсоединенных к соответствующему выходу дешифратора и к входу соответствующего из элементов И, при этом первый счетчик импульсов соединен установочным входом и выходом переполнения с выходом и с вторым входом второго триггера, тре тий элемент ИЛИ подключен выходом к вторым управляющим входам блока элементов И-ИЛИ, коммутатора и к управляющему входу второго блока элементов И.

2. Устройство по п. 1, отличающееся тем, что регистр контроля содержит последовательно соединенные первые блоки памяти, число которых на единицу меньше

90410

числа каналов, блок памяти и вторые блоки памяти, число которых на единицу меньше числа каналов, и элемент И, а каждьш из блоков памяти содержит последовательно соединенные элемент И и регистр сдвига, причем один вход элемента И первого из первых блоков памяти является входом регистра контроля, выход элемента И регистра контроля является выходом регистра контроля, а его один вход соединен с другим входом элемента И первого из первых блоков памяти и является одним из управляющих входов регистра контроля, другой из управляющих входов которого соединен с входами элементов И блока памяти и первого из вторых блоков памяти, а остальные управляющие входы регистра контроля соединены с объединенными входами элементов И соответствующих блоков памяти, при этом регистр сдвига каждого из блоков памяти подключен выходом к одному из входов элемента И последующего блока памяти, выход регистра сдвига последнего из вторьж блоков памяти подсоединен к другому входу элемента И регистра контроля, а выходы регистров сдвига блоков памяти явля- ются выходами регистра контроля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для многоканальной записи-воспроизведения информации | 1985 |

|

SU1273992A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для обнаружения и исправления ошибок | 1985 |

|

SU1368995A1 |

| Устройство для контроля синхронизма воспроизведенных сигналов | 1988 |

|

SU1585833A1 |

| Устройство для контроля ошибок аппаратуры многоканальной магнитной записи | 1988 |

|

SU1580438A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для контроля ошибок канала цифровой магнитной записи | 1988 |

|

SU1510007A1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| СПОСОБ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107334C1 |

1. УСТРОЙСТВО ДЛЯ ЗАПИСИ ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ИНФОРМАЦИИ, содержащее блок элементов И-Ш1И, число которых равно числу каналов, подключенный всеми выходами кроме первого, к входам регистров, кроме первого, вход которого подсоединен к первому выходу коммутатора, подключенного первым входом к первому выходу блока элементов И-ИЛИ, вторым входом к первому выходу коммутатора и третьим входом - к выходу сумматора по модулю два, подключенного первым входом к второму выходу коммутатора, а остальными входами к выходам соответствующих разрядов регистров, соединенных выходами последних разрядов с первыми входами сумматоров по модулю два, подсоединенных выходами к входам первого и второго блоков элементов И, соединенных выходами с входами магнитного накопителя и блока памяти, подключенных выходами к соответствующим входам блока элементов И-ИЛИ, а также содержащее регистр контроля, выполненный с числом пар выходов. равным числу каналов и соединенных с соответствующими входами элементов И, соединенных выходами с вторыми входами сумматоров по модулю два, первый счетчик импульсов, подключенный входом :к синхронизирующей шине и к соединенным между собой синхронизирующим входам регистров и регистра контроля, последний из которых соединен входом с третьим выходом коммутатора и с входом одного из элементов И, первую управляющую шину, вторую управляющую шину, подключенную к первым управляющим входам блока элементов И-ИЛИ и коммутатора и к (Л управляющим входам первого блока элементов И, отличающеес я тем, что, с целью повьш1ения верности воспроизведения информации путем повьш1ения исправляющей способности при групповых сбоях, в него введены второй счетчик имсо пульсов, первый и второй триггеры, о дешифратор, первый, второй и третий ifi элементы ИЛИ блок элементов дифференцирования, элемент задержки и инверторы, причем регистр контроля подключен управляющими входами через инверторы к выходам элементов И и выходом последнего разряда к входу второго счетчика импульсов, подсоединенного выходами через первый элемент ИЛИ к информационному входу первого триггера, соединенного синхронизирующим входом с установочным входом второго счетчика импульсов через элемент задержки и непосредственно с выходом второго элемента ИЛИ, подключенного входа

1

Изобретение относится к област

магнитной записи, а именно к устройствам для записи-воспроизведения многоканальной информации.

Цель изобретения - повьш ение верности воспроизведения информации путем повьш ения исправляющей способности при групповых сбоях.

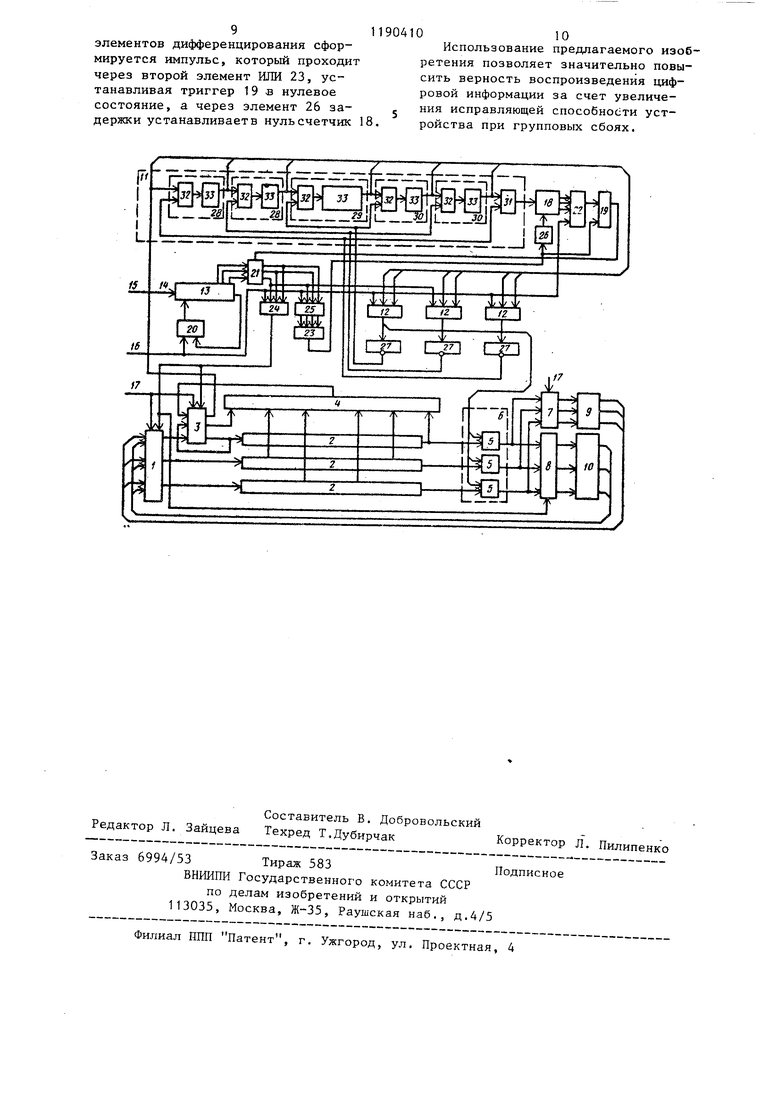

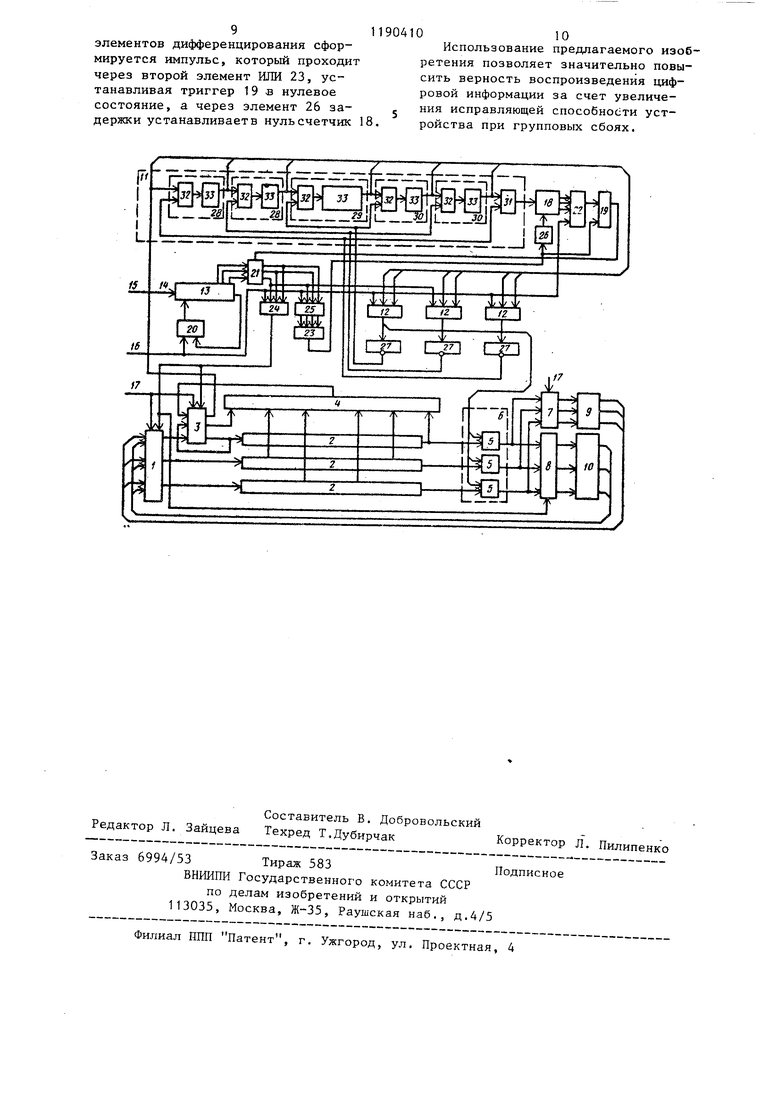

На чертеже приведен один из возможных вариантов устройства дл записи-воспроизведения многоканальной информации.

Устройство для записи-воспроизведения многоканальной информации содержит блок 1 элементов И-ИЛИ, число которых равно числу каналов подключенный всеми выходами кроме первого, к входам регистров 2, кроме первого, вход которого подсоединен к первому выходу коммутатора 3, подключенного первым входом к первому выходу блока 1 элементов И-1-Ш11, вторым входом - к

первому выходу коммутатора 3 и

третьим входом - к выходу сумматора 4 по модулю два, подключенного первым входом к второму выходу коммутатора 3, а остальными входами к выходам соответствующих разрядов регистров 2, соединенных выходами последних разрядов с первыми входами сумматоров 5 по модулю два, группы 6 сумматоров подсоединенных выходами к входам первого и второго блоков 7 и 8 элементов И, соединенных выходами с входами магнитного накопителя 9 и блока 10 памяти, подключенных выходами к соответствующим входам блока 1 элементов И-ИЛИ, а также содержащее регистр 11 контроля, выполненный с числом пар выходов, равным числу канйлов и соединенных с соответствующими входами элементов И 12, соединенных выходами с вторыми входами сумматоров 5 по модулю два первый счетчик 13 импульсов, подключенный входом 14 к синхронизирующей шине 15 и к соединенным между собой синхронизирующим входам регистров 2 и регистра 11 контроля (не показано), последний из которых соединен входом с третьим выходом коммутатора 3 и с входом одного из элементов И 12, первую управляющую шину 16, вторую управляющую шину 17, подключенную к первым управляющим входам блока 1 элементов И-ИЛИ и коммутатора 3 и к управляющим входам первого блока 7 элементов-И, кроме этого, содержит второй счетчик 18 импульсов, . первый и второй триггеры 19 и 20, дешифратор 21, первый, второй и тр тий элементы ИЛИ 22 - 24, блок 25, элементов дифференцирования, элемент 26 задержки и инверторы 27, причем регистр 11 контроля подключен управляющими входами через инверторы 27 к выходам элементов И 12 и выходам последнего разряда к входу второго счетчика 18 импульсов, подсоединенного выходами чере первый элемент ИЛИ 22 к информационному входу первого триггера 19, соединенного синхронизирующим входом с установочным входом второго счетчика 18 импульсов через элемент 26 задержки и непосредственно с выходом второго элемента ИЛИ 23, подключенного входами к выходам блока 25 элементов дифференцирования, подсоединенного входами к входам третьего элемента ИЛИ 24 и к выходм дешифратора 21, выполненного с числом выходов, равным числу каналов, и соответствующими выходами соединенного с входами соответствующих элементов И 12, отдельные входы заданных элементов И 12 подключены к одному из входов первого элемента ИЛИ 22, к первой управляющей шине 16j к первому входу второго триггера 20, к одному из входов блока 25 элементов дифференцирования и третьего элемента ИЛИ 24, отдельными вхо- дами подсоединенных к соответствующему выходу дешифратора 21 и к входу соответствующего из элементов И 12, при этом первый счетчик 13 импульсов соединен установочным входом и выходом переполнения с выходом и с вторым входом второго триггера 20, Третий элемент ИЛИ 24 подключен выходом к вторым управляющим входам блока 1 элементов И-ИЛИ, коммутатора 3 и к управляющему входу второго блока 8 элементов И. В устройстве для записи-воспроизведения многоканальной информации регистр 11 контроля содержит последовательно соединенные первые блоки 28 памяти, число которых на единицу меньше числа каналов, блок 29 памяти и вторые блоки 30 памяти, число которых на единицу меньше числа каналов, и элемент И 31, а каждый из блоков 28 - 30 памяти содержит последовательно соединенные элемент И 32 и регистр 33 сдвига, причем один вход элемента И 32 первого из первых блоков 28 памяти является входом регистра 11 контроля , выход элемента И 31 регистра 11 контроля является выходом регистра 11 контроля, а его один вход соединен с другим входом элемента И 32 первого из первых блоков 28 памяти и является одним из управляющих входов регистра 11 контроля

другой из управляющих входов которого соединен с входами элементов И 32 блока 29 памяти и первого из вторых блоков 30 памяти, а остальные управляющие входы регистра 11 контроля соединены с объединенными входами элементов И 32 соответствующих блоков памяти, при этом регистр 33 сдвига каждого из блоков 28 - 30 памяти подключен выходом к одному и из входов элемента И 32 последующего блока 28, 29 или 30 памяти, выход регистра 33 сдвига последнего из вторых блоков 30 памяти подсоединен к другому входу элемента И 31 регистра 11 контроля, а выходы регистров 33 сдвига блоков 28 - 30 памяти являются выходами регистра 11 контроля.

Устройство работает следующим образом.

Информация, подлежащая записи в накопитель 9, поступает по двум каналам из блока 10 в блок 1. По сигналу записи с шины 17 третий вход коммутатора 3 подключается к его первому выходу, а второй и третий i выходы коммутатора 3 подсоединяются внутри него к общей шине. В регистрах 2 по внешним тактам с пшны 15 (не показаны) производится последовательный сдвиг информации, поступа ющий на их вход, параллельно по все каналам. Сумматор 4 по модулю два в каждом такте суммирует по модулю два сигналы с вторых выходов регист ра 2. Выходные сигналы сумматора 4 по модулю два через коммутатор 3 в каждом такте поступают на первый из регистров 2 одновременно с инфор мацией, соответствующей строки с вы хода блока 1, Выходная информация регистров 2, содержащая в каждой строке два информационных и один контрольный разряда, через блок 7, открытый сигналом с шины 17, поступает на вход накопителя 9. Таким образом, в процессе записи устройст во работает как шифратор, формируя в каждой строке контрольные разряды При воспроизведении информации с шины 16 подается команда воспроизведения. В коммутаторе 3 соединяются между собой одноименные входы и выходы (первый вход с первым выходо и т.д.). Выходная информация накопи теля 9 через блок 1 и коммутатор 3 построчно параллельно-последователь ным кодом поступает на входы регистров 2, где происходит последова тельный построчный сдвиг этой инфор мации по тактам с шины 15. Одновременно по тактам сдвигается информация и в регистре 11. В сумматоре 4 по модулю два в каяодом такте суммируются по модулю 2 выходные сигналы регистров 2. Отклонение от четности суммы сигналов, поступающих на входы сумматора 4, воспринимается как признак ошибки в виде единичного сигнала, который с выхода сумматора 4 по модулю два через коммутатор 3 поступает на вход регистра 11 и продвигается к его выходу параллельно с продвижением информации в регистрах 2. Каждая одиночная ошибка входной информации будет представлена в регистре 11 двумя признаками. Один признак формируется при прохождении сбойным битом информации последнего разряда первого из сдвигающих регистров 2 соответствующего канала, а второй признак формируется при прохождении этим же битом соответствующих разрядов сдвигающего регистра 2 того же канала. В зависимости от сбойного канала признаки ошибок располагаются в регистре 1 1 в определенном сочетании. Аналогичным образом будут записаны в регистре 11 и пакеты ошибок в разных каналах. В процессе воспроизведения информации с накопителя 9 происходит в каналах 1 и 3 коррекция ошибок, представленных в регистре 11 двумя признаками. При наличии ошибок в третьем канале происходит совпадение единичных сигналов с выходов сдвигающего регистра 33 последнего из блоков 28 и сдвигающего регистра 33 блока 29 памяти. Это совпадение воспринимается в определенных тактах одним из элементов И 12, который открытым сигналом воспроизведения и передает-г ся в третий из сумматоров 5 по модулю 2, где инвертируются ошибочные биты информации, поскольку именно в этих тактах строки с ошибочными битами будут поступать с выходов регистров 2 на входы сумматоров 5 по модулю два. При наличии ошибок в третьем канапе происходит совпадение единичных сигналов с третьего выхода коммутатора 3 и сдвигающего регистра 33 последнего блока 30 памяти. Это совпадение воспринимается соответствующим элементов И 12 и передается в соответствующий сумматор по модулю два, где инвертируются ошибочные биты информации первого канала. Корректирующие сигналы с выходов элементов И 12, кроме того, через инверторы 27 поступаютна вторые входы соответствующих элементов И 32 регистра 11 и второй вход элемента И 31, запрещая прохождение признаков ошибок на выход этих элементов. В результате в регистре 11 будут исключены признаки скорректированных ошибочных битов. Oшибo ные биты во втором канале в процессе воспроизведения информации не корректируются, поскольку соответствующий элемент И 12 закрыт выходным сигналом дешифратора 21.

711

Скорректированный по первому и третьему каналам выходной код сумматоров 5 по модулю два через открытьш блок 8 элементов И переписывается в блок 10 памяти. Наличие нескорректированных ошибок и их количество фиксируется во втоJ)OM счетчике 18 импульсов. Сигналом с шины 16 второй триггер 20 устанавливается в 1 и разрешает подсчет первым счетчиком 13 им-, Пульсов. В счетчике 13 фиксируется код числа строк в воспроизведенном массиве информации. В конце воспроизведения в старших разрядах счетчика 13 будет записан код, соответствующий 1.

При наличии нескорректированных ошибок во втором счетчике 18 импульсов в конце воспроизведения появляются единичные сигналы на выходе дешифратора 21 и на выходе третьего элемента ИЛИ 24. Информация с выхода блока 10 памяти передается через блок 1 и коммутатор 3 на вход регистров 2 и продвигается вдоль них построчно так же, как и в режиме воспроизведения. В сумматоре 4 формируются единичные сигналы отклонения от четности, которые записываются в регистре 11 и продвигаются по тактам вдоль него параллельно с продвижением информации в регистрах 2. Каждая ошибка во втором канале будет представлена в регистре 11 двумя признаками. При наличии нескорректированных ошибок в счетчике 18 в конце воспроизведения на информационный вход триггера 19 через элемент ИЛИ 22 поступит единичный сигнал. По окончании команды воспроизведения на выходе блока 25 элементов дифференцирования сформируется импульс;, который проходит через второй элемент ИЛИ 23 и устанавливает триг.гер 19 в единичное состояние, а через элемент 26 задержки устанавливает в О счетчик 18. На выходе дешифратора 21 и на выходе третьего элемента ИЛИ 24 формируются единичные сигналы. Информация с выода блока 10 памяти передается через блок 1 и коммутатор 3 на вход регистров 2 и продвигается вдоль

них построчно также, как и в режиме воспроизведения. В сумматоре 4

формируются сигналы отклонения от | четности, которые записываются в ре-;

04108

гистре 11 и продвигаются по тактам вдоль регистра 11 параллельно с продвижением информации в регистрах 2. Каждая ошибка во втором 5 канале будет представлена двумя .. признаками. При совпадении единичных сигналов с выходов сдвигающего регистра 33 первого из первых блоков 28 и сдвигающего регистра 38

fO первого из вторых блоков 30 на выходе соответствующего элемента И 12, который открыт сигналом коррекции-с выхода дешифратора 21, формируются единичные сигналы, которые

JS поступают в соответствующий сумматор 5 по модулю два, инвертируя ошибочные биты информации во втором канале. Одновременно выходные сигналы открытого элемента И 12 второ20 го канала через инвертор 27 второго канала поступают на вторые входы элементов И 32 вторых из первых и вторых блоков 28 и 30, исключая . признаки скорректированных ошибоч25 ных битов.

Если накопитель 9 содержит К каналов (не считая тактового), то (К-1) канал используется для записи входной информации, а К-канал

3Q для записи контрольных разрядов. При этом регистры 2 содержат Кканалов.

При воспроизведении производится коррекция информации в первом и К-каналах. При коррекции информации в К-ом канале производится контроль совпадений единичных сигналов на первых входах блока 29 памяти первого из вторых блока 30 памяти регистра 11,а при коррекции информации в первом канале производится контроль совпадений сигналов на первых входах первого из первых блока 28 и элемента И 31.

В первом цикле коррекции исправляются ошибки во втором и (К-1) каналах.

После коррекции информации в последнем канале первый счетчик

/J 13 импульсов переполняется и устанавливает второй триггер 20 в О.

Процесс коррекции может прерываться в конце любого цикла или после воспроизведения, когда в счетчике 5 18 после окончания цикла коррекции

или после воспроизведения будет нуiлевой код. По сигналу окончания : цикла коррекции на выходе блока 25

911

элементов дифференцирования сформируется импульс, которьй проходит через второй элемент ИЛИ 23, устанавливая триггер 19 в нулевое состояние, а через элемент 26 задержки устанавливает в нуль счетчик 18.

9041010

Использование предлагаемого изобретения позволяет значительно повысить верность воспроизведения цифровой информации за счет увеличе, ния исправляющей способности устройства при групповых сбоях. сжз с: OD №UJ:©PbL H

| Способ записи и воспроизведения цифровой информации | 1981 |

|

SU1001166A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Скотт Эд | |||

| и др | |||

| Исправление многобитовых ошибок при помощи одного контрольного бита на слово | |||

| - Электроника | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| с | |||

| Приспособление с иглой для прочистки кухонь типа "Примус" | 1923 |

|

SU40A1 |

Авторы

Даты

1985-11-07—Публикация

1984-07-31—Подача