ся в нем в соответствии с сигналами сумматора 4 по модулю два. В режиме воспроизведения производится коррекция ошибок в первом контрольном и последнем информационном каналах. По окончании воспроизведения единичное состояние триггера 46 по сигналу блока 15 дифференцирующих элементов переписывается в триггер 13,открывающий дешифратор 14. После этого триггер 46 через элемент 18 задержки устанавливается в О. В конце воспроизведения в старшие разряды счетчика 11 записывается единица, а дешифратор 14 воздействует на блок 6 элементов И 7, формирующих сигнал ошибок во втором и предпоследнем кайалах. Дешифратор 14 воздействует на формирователь 32 управляющих сигналов и через элементы ИЛИ 16 и 43 на коммутатор 1, в котором сохраняется коммутация, соответствующая режиму воспроизведения, 1 з.п. ф-лы, 2ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для записи-воспроизведения многоканальной информации | 1984 |

|

SU1190410A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для воспроизведения с носителя магнитной записи | 1984 |

|

SU1216788A1 |

| Селектор импульсов по длительности | 1990 |

|

SU1758866A2 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

| Устройство для воспроизведения цифровой магнитной записи | 1987 |

|

SU1458885A1 |

| Устройство для обнаружения и исправления ошибок | 1985 |

|

SU1368995A1 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2013 |

|

RU2534955C1 |

Изобретение относится к накоплению информации и позволяет повысить пропускную способность за счет уменьшения задержки. Каждая ошибка информации магнитного накопителя 21 представляется регистре 5 контроля двумя признаками, которые формируютts3 ОЭ СО to

Изобретение относится к накоплению информации, а именно к устройствам для многоканальной магнитной записи-воспроизведения информации.

Цель изобретения - повышение пропускной способности за счет уменьшения задержки.

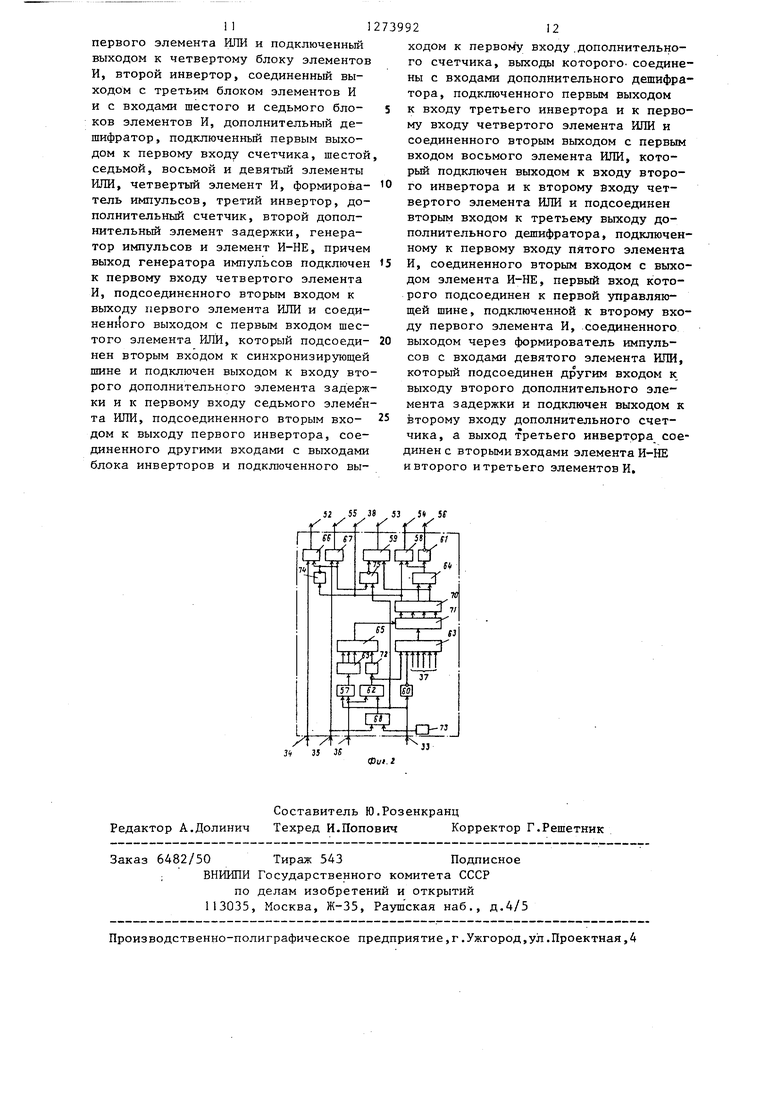

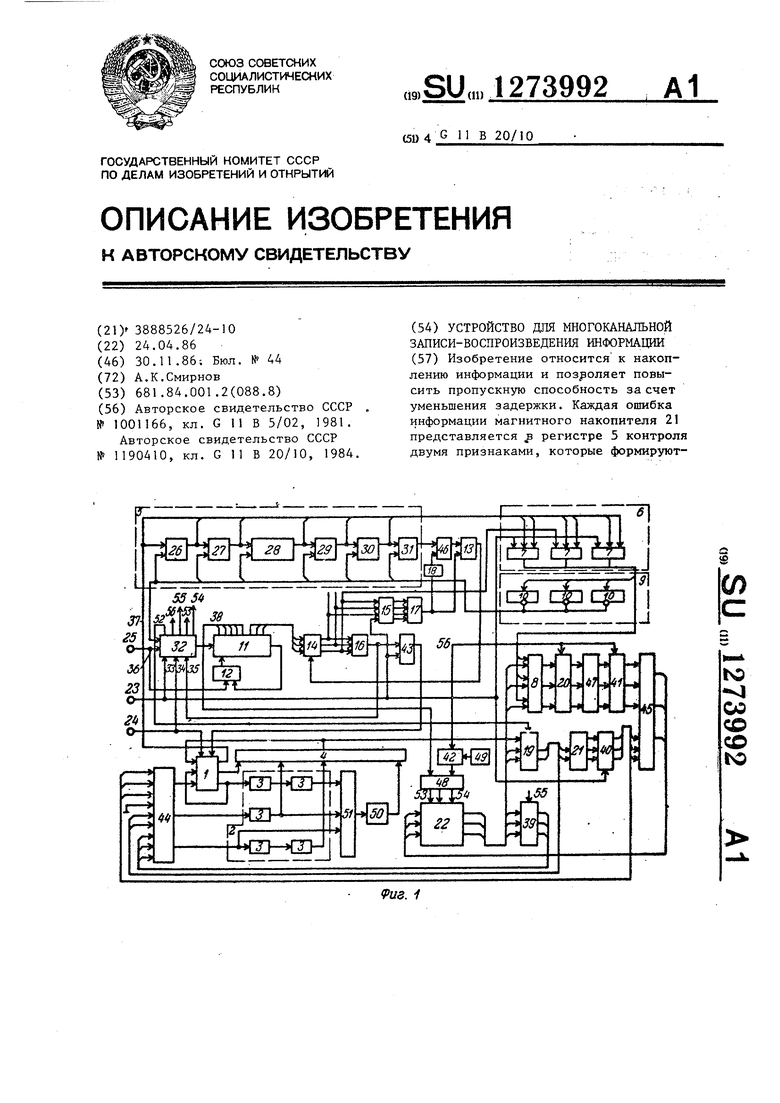

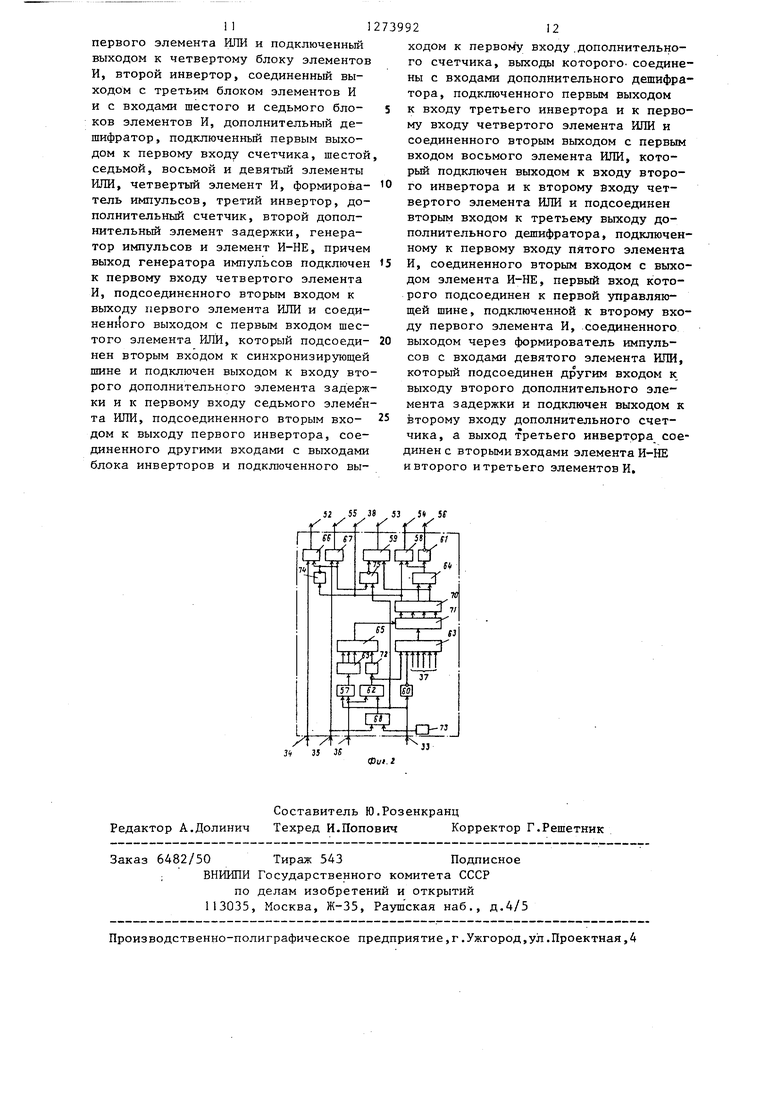

На фиг. 1 ..изображено устройство для многоканальной Записи-воспроизведения информации; на фиг.2 - формирователь управляющих сигналов.

Устройство содержит коммутатор 1, подключенный первым выходом к его первому входу и к первому входу блока 2 регистров 3 и соединенный вторым выходом с первым входом сумматора 4 по модулк) два, регистр 5 контроля, первьй блок 6 элементов И 7, блок 8 сумматоров по модулю два,блок 9 инверторов 10, счетчик 11, первый и второй триггеры 12 и 13, дешифратор 14, блок 15 дифференцирующих элементов, первый и второй элементы ИЛИ 16 и 17, элемент 18 задержки, второй и третий блоки 19 и 20 элементов И, магнитный накопитель 21, блок 22 памяти, первую и вторую управляющие шины 23 и 24 и синхронизирующую шину 25. Cj MaTop 4 по модул р два подсоединен другими входами к выходам блока 2 регистров 3 и соецинен выходом со вторым входом ком 1утатора 1 . Третий выход коммутатора 1 подключен к регистру 5 контроля, соединенного выходами с первым блоком 6 элементов И 7; выходы которого подключены ко вхрдам блока 8 сумматоров по модулю два и ко входам

блока 9 инверторов 10. Выходы блока 9 инверторов 10 соединены со входами регистра 5 контроля. Счетчик 11 подключен выходом переполнения к первому входу первого триггера 12 и соединен выходами старших разрядов с информационными входами дешифратора 14, подсоединенного выходами к входам первого элемента ИЖ 16, к входу первого блока 6 элементов И 7 и к входам блока 15 дифференцирующих элементов. Выходы блока 15 дифференцирующих элементов соединены через второй элемент ИЛИ 17 с входом элемента 19 задержки и с первым входом второго триггера 13, подключенного выходом к управляющему входу дешифратора 14. Первая управляющая шина 23 соединена с другим входом блока 15 дифференцирующих элементов и с другими входами первого блока 6 элементов И 7.Вторая управляющая шина 24 подключена к третьему входу коммутатора 1. Выходы второго блока 19 элементов И подсоединены к входам магнитного накопителя 21. Входы третьего блока 20 элементов И соединены с выходами блока 8 сумматоров по модулю два. При этом регистр 5 контроля выполнен в виде соединенных последовательно блоков 26-30 памяти и элемента И 31.

Устройство содержит также формирователь 32 управляющих сигналов, подсоединенный первым, вторым, третьим и четвертым входами 33-36 соответственно к первой и второй управляющим шинам 23 и 24, к выходу первого элемента ИЛИ 16 и к синхронизирующей шине 25, подключенной к первому входу первого триггера 12, соединенный другими входами 37 с выходами блока 9 инверторов 10 и подключенный первым выходом 38 к первому входу счет чика 11, четвертый, пятьш, шестой н седьмой блоки 39-42 элементов И, тре тий элемент ИЛИ 43, первый и второй блоки 44 и 45 элементов ИЛИ, третий триггер 46, регистр 47, сумматор 48, формирователь 49 сигнала установки, дополнительный элемент 50 задержки и дополнительньш сумматор 51 по модулю два. Счетчик 11 соединен вторьм входом с выходом первого триггера 12 Формирователь 32 управляющих сигналов подсоединен вторым выходом 52 к второму блоку 19 элементов И, соединенному с выходом сумматора 4 по модулю два. Входы четвертого блока 39 элементов И подсоединены к выходам блока 22 памяти, соединенным с другими входами блока 8 сумматоров по модулю два. Первый блок 44 элементов ИЛИ подключен первым выходом к четвертому входу коммутатора 1, соединен другими выходами с другими входа ми блока 2 регистров 3 и подсоединенный к выходам второго блока 19 элементов И. Выходы второго блока 45 элементов ИЛИ подключены ко входам блока 22 памяти. Третий элемент ИЛИ 43 включен между выходом первого эле мента ИЛИ 16 и пятым входом коммутатора 1. Входы пятого блока 40 элементов И подсоединены к выходам магнитного накопителя 21. Третий триггер 46 подсоединен первым входом к регистру 5 контроля, соединен вторым входом с выходом элемента 18 задержки и подключен выходом к второму вхо ду второго триггера 13. Регистр 47 подсоединен входами к выходам третьего блока 20-элементов, И. Сумматор 48 соединен.входами с выходами младших разрядов счетчика 11 и подключен выходом к другому входу блока 22 памяти. Дополнительный сумматор 51 по модулю два подсоединен входами к бло ку 2 регистров 3 и соединен выходом через дополнительньм элемент 50 задержки с сумматором 4 по модулю два. Блок 22 памяти подсоединен к третьему и четвертому выходам 53 и 54 формирователя 32 управляющих сигналов, который подключен пятым выходом 55 к четвертому блоку 39 элементов И. Чет вертый блок 39 элементов И соединен 924 выходами со входами первого блока 44 элементов ИЛИ. Шестой выход-56 формирователя 32 управляющих сигналов подсоединен к входу седьмого блока 42 элементов И, к третьему блоку 20 элементов И и к входу шестого блока 41 элементов И, включенного между выходами регистра 47 и входами второго блока 45 элементов ИЛИ, который соединен другими входами е выходами пятого блока 40 элементов И, подключенными к другим входам первого блока 44 элементов ИЛИ. Другой вход сумматора 48 подсоединен к выходу седьмого блока 42 элементов И, соединенного другим входом с выходом формирователя 49 сигнала установки. При этом вход третьего элемента ИЛИ 43 подсоединен к первой управляющей 23.Формирователь 32 управляющих сигналов содержит первый элемент И 57, подсоединенный первым входом к синхронизирующей шине 25, четвертый и пятьй элементы ИЛИ 58 и 59, подключенные выходами к блоку 22 памяти, первый инвертор 60, соединенный входом с первой управляющей шиной 23, второй инвертор 61, шестой, седьмой, восьмой и девятый элементы ИЛИ 62-65, второй, третий и четвертый элементы И 66, 67 и 68, формирователь 69 импульсов, дополнительный дешифратор 70, дополнительньш счетчик 71, второй дополнительный элемент 72 задержки, генератор 73 импульсов, третий инвертор 74 и элемент И-НЕ 75. Второй элемент И 66 подсоединен первым входом к второй управляющей шине 24 и подключен выходом к второму блоку 19 элементов И. Третий элемент И 67 подсоединен первым входом к выходу первого элемента ИЛИ 12 и подключен выходом к четвертому блоку 39 элементов И. Дополнительный дешифратор 70 подключе первым выходом к первому входу счетчика 11. Второй инвертор 61 соединен выходом с третьим блоком 20 элементов И и с входами шестого и седьмого блоков 41 и 42 элементов И. Выход генератора 73 иипульсов подключен к первому входу четвертого элемента И 68, подсоединенного вторым входом к вьпсоду первого элемента ИЛИ 12 и соединенного выходом с первым входом шестого элемента ИЛИ 62. Шестой элемент ИЛИ 62 подсоединен вторым входом к синхронизирующей шине 25 и подключен

выходом ко входу второго дополнительного элемента 72 задержки и к первому входу седьмого элемента ИЛИ 63, Седьмой элемент ИЛИ 63 подсоединен вторым входом к выходу первого инвер тора 60, соединен другими входами с выходами блока 9 инверторов 10 и подключен выходом к первому входу дополнительного счетчика 71. Дополнительный счетчик 71 подключен .выходами к входам дополнительного дешифратора 70, подключенного первым выходом ко входу третьего инвертора 74 и к первому входу четвертого элемента ИЛИ 58 и соединенного вторым выходом с первым входом восьмого элемента ИЛИ 64. Восьмой элемент ИЛИ 64 подключен выходом к входу второго инвертора 61 и к второму входу четвертого элемента ИЛИ 58 и подсоединен вторым входом к третьему выходу дополнительного дешифратора 70, соединенному с первым входом пжгого элемента ИЛИ 59. Второй вход пятого элемента ИЛИ 59 соединен с выходом элемента И-НЕ 75, подсоединенного первым входом к первой управляющей шине 23, подключенной к второму входу первого элемента И 57. Выход первого элемента И 57 соединен через формирователь 69 импульсов с входами девятого элемента ИЛИ 65, подсоединенного другим входом к выходу второго дополнительного элемента 72 задержки и подключенного выходом к второму входу дополнительного счетчика 71. Выход третьего инвертора 74 соединен с вторыми входами элемента И-НЕ 75 и второго и третьего элементов И 66 и 67.

Многоканальная запись-воспроизведепие информадии посредством предложенного устройства происходит следующим образом.

В режиме записи информация из блока 22 памяти построчно поступает через второй блок 19 элементов И на магнитный накопитель 21. При этом для каждой строки информации в сумматоре 4 по модулю два формируется контрольный разряд, который через второй блок 19 элементов И также поступает в магнитный накопитель 21. Кроме того, по второй управляющей шине 24 на коммутатор 1 и на формирователь 32 управляющих сигналов поступает высокий потенциал, а по синхронизирующей шине 25 на формирователь 32 управляющих сигналов и на первый

триггер. 12 подаются синхронизирующие .импульсы, имеющие частоту записи строк информации в магнитный накопитель 21. При этом первый триггер 12 разрешает подсчет входных импульсов счетчиком 11, а импульсы отрицательной полярности с синхронизирующей шины 25, проходя в формирователе 32 управляющих сигналов через шестой и седьмой элементы ИЛИ 62 и 63, разрешают на время действия каждого из них работу дополнительного счетчика 71. С выхода шестого элемента ИЛИ 62 импульсы проходят после задержки во втором дополнительном элементе 72 задержки через девятый элемент ИЛИ 65 на дополнительный счетчик 71. По переднему фронту каждого из этих импулсов дополнительньй счетчик 71 устанавливается в состояние, при котором дополнительньш дешифратор.70 формирует разрешающий иьшульс, проходящий через четвертый элемент ИЛИ 58 на блок 22 памяти, а через третий инвертор 74 и второй элемента И 66 на второй блок 19 элементов И. На элемент И-НЕ 75 с первой управляющей шины 23 поступает нулевой потенциал, что обеспечивает поступление высокого потенциала с четвертого элемента ИЛИ 59 на блок 22 памяти, соответствующего операции считывания.

Счетчик 11 подсчитывает число строк информации, записываемой в магнитньш накопитель 21. Код с выходов младших разрядов счетчика 11 поступает через сумматор 48 на блок 22 памяти. При этом информация номера адреса подается на блок 22 памяти, который производит считывание информации, подлежащей записи в магнитном накопителе 21, на которьш она поступает через второй блок 19 элементов И. Эта информация поступает также через первый блок 44 элементов ИЛИ на блок 2 регистров 3, где производится ее последовательный сдвиг параллельно по всем каналам. При этом блок 2 регистров 3 воздействует на сумматор 4 по модулю два непосредственно и через дополнительный сумматор 51 ПС модулю два и дополнительньй элемент 50 задержки.

В режиме воспроизведения информация с магнитного накопителя 21 поступает через пятый блок 40 элементов И и второй блок 45 элементов ИЛИ на блок 22 памяти. При этом на первый блок 6 элементов И 7, на пятый блок 40 элементов И и на формирователь 32 управляющих сигналов с первой управляющей шины 23 поступает высокий потенциал, который проходит также через третий элемент ИЛИ 43 на коммутатор 1, а по синхронизирующей шине 25 подаются синхронизирующие импульсы, вырабатываемые синхронно со строками информации, воспроизвоДИМОЙ в магнитном накопителе 21.Последнее обеспечивает установку первого триггера 12 в единичное состояние разрешающее подсчет входных импульсов счетчиком 11 , Высокий потенциал первой управляющей шины 23 через первый инвертор 60 и седьмой элемент ИЛИ 63 в формирователе 32 управляющих сигналов открывает дополнительный счетчик 71 для импульсов, постулающих на него через шестой элемент ИЛИ 62, второй дополнительный элемент 72 задержки и девятый элемент ИЛИ 65. Кроме того, эти импульсы поступают на формирователь 69 импульсов, формирующий тройки импульсов сдвинутых один относительно другого и относительно входного импульса.Дополнительный счетчик 71 работает в режиме непрерывного счёта пачек по четыре импульса, поступающих с девятого элемента ИЛИ 65. По первому импульсу пачки дополнительный дешифратор 70 формирует управляющий импульс поступающий на счетчик 11. Выходные импульсы дополнительного дешифратора 70 подаются на блок 22 памяти через третий инвертор 74, элемент И-НЕ 75 и пятый элемент ИЛИ 59, а также через четвертый элемент ИЛИ 58. Информация с магнитного накопителя 21 поступает на блок 22 памяти, на который с выходов младших разрядов счетчика 11 через сумматор 48 подается код адреса. В результате этого в-блок 22 производится построчная запись информации.

Информация с магнитного накопителя 21 через пятый блок 40 элементов И, первый блок 44 элементов ИЛИ и коммутатор 1 поступает на блок 2 регистров 3, в котором продвигается синхронно со входными импульсами счетчика 11. При отклонении от четности суммы разрядов, поступающих в каждой строке на сумматор 4 по модулю два, происходит формирование сигнала признака ошибки, подаваемого

на регистр 5 контроля. Каждая ошибка информации магнитного накопителя 21 представляется в регистре 5 контроля двумя признаками, которые формируются в нем в соответствии с сигналами сумматора 4 по модулю два. В режиме воспроизведения производится коррекция ошибок в первом контрольном и последнем информационном ка- налах, если эти ошибки представлены в регистре 5 контроля двумя признаками.

При окончании воспроизведения единичное состояние третьеготриггера 46 по сигналу блока 15 дифференцирующих элементов переписывается во второй триггер 13, который открьшает дешифратор 14. После этого третий триггер 46 через элемент 18 задержки устанавливается в нулевое состояние. В конце воспроизведения в старшие разряды счетчика записывается единица, а дешифратор 14 воздействует на первый блок 6 элементов И 7, формирующий сигнал о наличии ощибок во втором и предпоследнем каналах. Кроме того, дешифратор 14 воздействует на формирователь 32 управляющих сигналов непосредственно, а через первый элемент ИЛИ 16 и второй элемент ИЛИ 43 - на коммутатор f, в котором сохраняется коммутация, соответствующая режиму воспроизведения. Далее аналогично воспроизведению производится коррекция информации в остальных каналах.

Формула и з-о бретения

| Способ записи и воспроизведения цифровой информации | 1981 |

|

SU1001166A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для записи-воспроизведения многоканальной информации | 1984 |

|

SU1190410A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-11-30—Публикация

1985-04-24—Подача