Изобретение относится к радиосвязи и может использоваться в приемниках высокоскоростных систем передачи дискретной информации и амплитудной модуляции сигналов.

Цель изобретения - повьшение помехоустойчивости от межсимвольных помех при приеме сигналов амплитудной телеграфии.

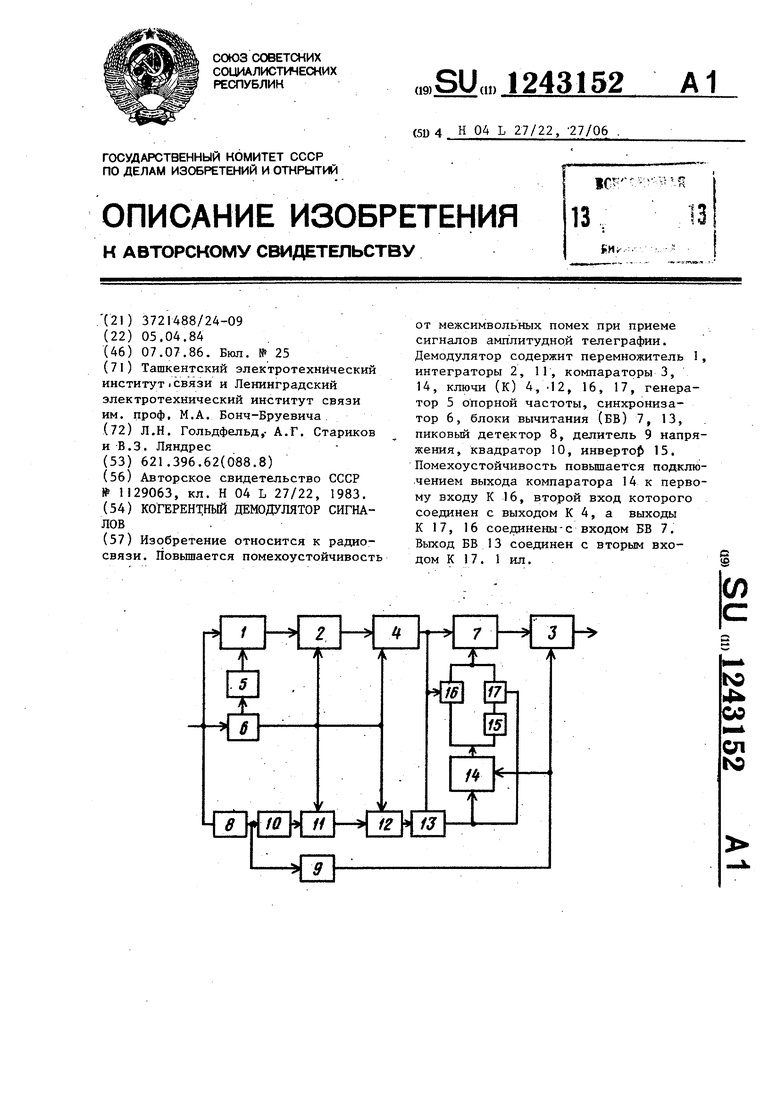

На чертеже изобрадена структурная электрическая схема предложенного когерентного демодулятора.

Когерентный демодулятор сигналов содержит перемножитель 1., первый интегратор 2, первый компаратор 3, первый ключ 4, генератор 5 опорной частоты, Синхронизатор 6, первый блок 7 вычитания, пиковьш детектор 8, делитель 9 напряжения, квадратор 10, второй интегратор П, второй ключ 12, второй блок 13 вычитания, второй компаратор 14, инвертор 15, четвертый ключ 16, третий ключ 17.

Когерентный демодулятор сигналов работает следующим образом.

Входной сигнал и„ (t), представ- собой аддитивную смесь полезного сигнала Uj,(t) флуктуационной помехи U(t) и межсимвольной помехи U,(t), описываемой выра;кеннем

Uftv (t)-U(t)+U(t)+U(t),

U sinu)t - при передаче сигнала ло.ги- ческой единицы;

О - при передаче сигнала логического нуля, IP - длительность одной посылки сигнала амплитудной телеграфии (АТ) поступает на вход перемножителя 1 , синхронизатора 6 и пикового детектора 8. Синхронизатор 6 формирует из входного сигнала синхроимпульсы, подаваемые на генератор 5 для синхронизации его работы и тактовые импульсы, интервал следования которых равен tp . Тактовые импульсы с второго- выхода синхронизатора 6 поступают на управляющие входы интеграторов 2, 11 к ключей 4, 12, Причем передним фронтом тактовые импульсы отпирают ключи 4, 12, задавая тем самым момент отсчета выходного сигнала интеграторов 2 и 11, а задним фронтом осуществляют сброс напряжения на выходах интеграторов 2и 11,подготавливаяих коб- работкеследующей посылки сигналаАТ.

10

2431522

Генератор 5, синхронизируемый импульсами, поступающими с первого выхода си:нхронизатора 6 , вырабатывает опорный сигнал Ucs(t), определяемый выражением

( Ь) ,

поступающий на управляющий вход пере- м:ножитепя 1 . На выходе перемножителя 1 при этом формируется напряжение и (t), определяемое выражением

и, (t)-u(t)-u(.t),

которое поступает на информационный вход интегратора 2, где осуществляется линейное интегрирование напряже- 15 НИН U(t) в течение длительности одной посыпки сигнала AT. Выходное напряжение интегратора 2 определяется выражением J.

, и,(t) i и (t)dt.

о 1 20 В конце каждой посьшки сигнала AT на

интегратор 2 и ключ 4 поступает так- .товьш импульс, передним фронтом отпи- раюЕЦИй ключ 4, а задним фронтом осуществляющий сброс напряжения на выхо- 25 де интегратора 2. При отпирании ключа 4 на его выход поступает напряжение и (t), представляющее .собой от30

35

счет выходного напряжения интегратора 2 в момент Т, где ,2,.,. Напряжение, поступающее на выход ключа 4 в конце каждой посылки сигнала AT, описывается выражением

uJt)u,(T)u,(C,)u,(V. .

(1)

I ) - напряжение флуктуационгде и.

7

40

г.п (

V

.

45

и. ( )

}с

.ной помехи на выходе интегратора 2 в момент отсчета;

напряжение межсимвольной помехи на выходе интегратора 2 в момент отсчета;

, - при передаче сигнала логической единицы ; О - при передаче сигнала логического нуля;

- напряжение сигнала AT на выходе интегратора 2 в .момент отсчета. С выхода ключа 4 напряжение U4(t) подается на информационный вход блока 7 вычитания. Пиковьм детектор 8 55 представляет собой инерционный амплитудный детектор с большой постоянной времени Т цепи нагрузки, выбираемой из условия

50

L .

0

5

счет выходного напряжения интегратора 2 в момент Т, где ,2,.,. Напряжение, поступающее на выход ключа 4 в конце каждой посылки сигнала AT, описывается выражением

uJt)u,(T)u,(C,)u,(V. .

(1)

I ) - напряжение флуктуационгде и.

7

0

г.п (

V

.

и. ( )

}с

.ной помехи на выходе интегратора 2 в момент отсчета;

напряжение межсимвольной помехи на выходе интегратора 2 в момент отсчета;

, - при передаче сигнала логической единицы ; О - при передаче сигнала логического нуля;

- напряжение сигнала AT на выходе интегратора 2 в .момент отсчета. С выхода ключа 4 напряжение U4(t) подается на информационный вход блока 7 вычитания. Пиковьм детектор 8 5 представляет собой инерционный амплитудный детектор с большой постоянной времени Т цепи нагрузки, выбираемой из условия

L .

U -()Т-;,

где t, - квазипериод замираний сигн аи

ла в радиоканале. В -высокоскоростных системах передачи дискретной информации, где длительность элементарной посылки в сотни раз меньше квазипериода замираний, составляющего О,1-0,05, такое условие легко реализуемо.

При выборе постоянной времени нагрузки пикового детектора 8 из условия (2) напряжение межсимвольных помех на его выходе будет усредняться, приближаясь к нулю, так как интервал их действия не превышает (4-5)Тр и будет тем ближе к нулю,

чем больше i . Напряжение на выходе н

пикового детектора 8 не будет также

содержать составляющих с частотой

манипуляции f - или ее гармоник

так как гораздо больше.

Уровень флуктуационных помех на Выходе пикового детектора 8 меньше, чем на входе в П раз, где П - полоса пропускания радиотракта приемника, за счет сужения ширины их спектра. Таким образом, напряжение Ug(t) ,на выходе пикового детектора 8 При подаче на него входного сигнала и (t) практически определяется только амплитудой несущей принимаемого сигнала AT, медленно меняющейся по закону замираний в радиоканале, т,е.

где К,

Ue(t)

- коэффициент передачи пикового детектора 8, практически равный единице. Напряжение Ug(t) с выхода пикового детектора 8 подается на делитель 9 напряжения, с коэффициентом деле1

ния Ко, определяемым выражением

1

2Кл

Делитель 9 напряжения служит для формирования оптимального порогового напряжения Uj,(t), подаваемого на управляющие входы компараторов 3 и 14, определяемого вьфажением

Ug (t)U,(t) ,

При подаче на управляющий вход компаратора оптимального порогового напряжения, равного половине амплитуды сигнала, обеспечивается минимальная вероятность ошибочного срабатывания компаратора.

На интервале одной посылки напряжение на выходе пикового детектора 8

243I524

практически не меняется и равно 11 - амплитуде несущей сигнала AT на входе демодулятора. Это напряжение подается на квадратор 10, на выходе которо- 5 го выделяется напряжение U(t)AU, .

подаваемое н,а информационный вход интегратора 11, В конце каждой посылки сигнала AT на управляющие, входы ин- tO тегратора 11 и ключа 12 с второго . входа синхронизатора 6 поступает тактовый импульс, который передним фронтом отпирает- ключ 12, а задним стира- .ет напряжение на выходе интегратора 15 11.При этомв концекаждой посылкина выходе ключа 12 вьщеляется напряжение

и.

uL

0

5

0

5

;,j ( ) J -ri m 0

0

подаваемое на управляющий вход блока 13 вычитания, на информационный вход которого с выхода ключа 4 в тот же момент подается отсчет выходного напряжения интегратора 2, определяемый выражением (1) ,При этом на выходе блока 13 вычитания выделяется сигнал компенсации U(t), Как видно из (1), на пряжение U (t), следовательно, и сигнал компенсации U (t) зависят от

12

ТОГО, какой полезный сигнал содержится в напряжении U. (t), поступающем на вход демодулятора.

При передаче сигнала логической единицы н апряжения U(t) на выходе ключа 4 в момент отсчета равно

u ; (t) +и„ (.)

0

-4 ---m о -Qm ; /07lr

а сигнал компенсации U (tj представляет собой сумму отсчетов межсимвольной и флуктуационной помехи.

U J (t)Vt)-U,2(t),,(.) +

5

0

+4s.()с выхода блока 13 вычитания этот сигнал компенсации подается на информационные входы ключа 17 и компаратора 14, Напряжение U (t), как правило, существенно меньше амплитуды полезного сигнала U, так как практически в любой реальной системе передачи дискретной информации отношение сигнала к помехе h удовлетворяет условию h,

В связи с этим порог компаратора U(t)

14, равный

, не превьшгается

,и

напряжением U (t), на выходе компаратора 14 появляется сигнал логического нуля, который запирает ключ 16, а на выходе инвертора 15 - сигнал логической единицы, который отпирает

ключ 1 7 . При отпирании- ключа 1 7 , сигнал компенсации ), поступающий На его информационный вход проходит через него на управляющий вход блока 7 вычитания, на информационный вход которого в тот же момент подается напряжение u (t).

В блоке 7 вычитания происходит компенсация межсимвольной помехи и на его выход поступает напряжение и (t), определяемое выражением:

u;(t)uV {t)-u,)v tj,

где ,(TO) остаточное напряжение флуктуационной помехи, обусловленное различием спектра флуктуационных помех, поступающих на управляющий и информационный вход блока 13 вычитания .

Напряжение ) подается на информационный вход компаратора 3. Если условие

u,(t)u,(t)

(3)

выполняется, на выходе демодулятора появляется сигнал логической единицы

При передаче сигнала логического нуля .напряжение на выходе ключа 4 не содержит составляющей сигнала AT и в соответствии с (1) определяется выражением

u,(t)unt)-u,7(bu,,(,)+ u,(t)-u:-.;.

При этом на выходе блока 13 вычитания сформируется напряжение

U.(t)(t)-ulf(t)U () +

и

4 12 Ои,

-uL(o)-u

о которое подается на информационные

входы компаратора 14 и ключа 17.

Как уже указывалось, уровень сигнала существенно превышает уровень помех, поэтому при подаче на информационный вход компаратора 14 напряжения Uj (t) порог срабатьшания компаратора 14 будет превЕЛпен, на выходе его сформируется сигнал логической единицы, который отпирает ключ 16, а на выходе инвертора 15 - сигнал логического нуля, который запирает ключ 17. При этом на управляю

5

5

о

5

0

5

щий вход блока 7 вычитания подается напряжение ) такое же, как и на его информационный вход, Напря- жение на выходе блока 7 вычитания, подаваемое на информационный вход компаратора 3, при этом близко к нулю, условие (3) не-выполняется, на выходе демодулятора появляется сигнал логического нуля.

Формула изобретения

Когерентный демодулятор сигналов, содержащий объединенные по входу перемножитель, синхронизатор и пико- вьй детектор, первый выход синхрони- затора через генератор -опорной частоты соединен с другим входом пере- множитёля, выход которого через последовательно соединенные первьй интегратор, первый ключ и первый блок вычитания соединен с первым входом первого компаратора, выход пикового детектора через последовательно соединенные квадратор, второй интегратор, Е;торой ключ, второй блок вычитания, второй компаратор и инвертор соединен с первым входом третьего ключа,, выход пикового детектора через Делитель напряжения соединен с объединенными вторыми входами первого и второго компараторов, выход синхронизатора соединен с объединенными вторыми входами первого и второго интеграторов, первого и второго ключей, выход первого ключа соединен с вторым входо.м второго блока вычитания, отличающи йся тем , что, с целью повышения помехоустойчивости от межсимвольных помех при приеме сигналов амплитудной телеграфии, выход второго компаратора соединен с первым входом четвертого ключа, второй вход которого соединен с выходом первого ключа, а выходы третьего и четвертого ключей соединены с входом перЕЮГо блока вычитания, выход второго блока вычитания соединен с вторым входом третьего ключа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Корреляционный демодулятор сигналов с угловой модуляцией | 1983 |

|

SU1166338A1 |

| Устройство передачи и приема шумоподобных сигналов | 1987 |

|

SU1631737A1 |

| Устройство тактовой синхронизации | 1988 |

|

SU1614122A2 |

| Устройство для оценки параметров многолучевого канала связи | 1991 |

|

SU1781828A1 |

| Адаптивный фильтр | 1984 |

|

SU1224983A2 |

| Демодулятор фазоманипулированных сигналов с компенсацией помех | 1987 |

|

SU1545332A1 |

| Устройство тактовой синхронизации | 1979 |

|

SU932642A1 |

| Частотный дискриминатор | 1978 |

|

SU790252A1 |

| Регенератор цифрового сигнала | 1986 |

|

SU1381728A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1989 |

|

SU1672575A2 |

Изобретение относится к радиосвязи. Повышается помехоустойчивость от межсимвольных помех при приеме сигналов амплитудной телеграфии. Демодулятор содержит перемножитель I, интеграторы 2, П, компараторы 3, 14, ключи (к) 4, -12, 16, 17, генератор 5 опорной частоты, синхронизатор 6, блоки вычитания (БВ) 7, 13, пиковый детектор 8, делитель 9 напряжения, квадратор 10, инверто{ 15. Помехоустойчивость повьшается подключением выхода компаратора 14 к первому входу К 16, второй вход которого соединен с выходом К 4, а выходы К 17, 16 соединены- с входом БВ 7. Выход БВ 13 соединен с вторым входом К 1 7. 1 ил. 4 00 СП to

| Устройство для шлифования | 1983 |

|

SU1129063A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-07-07—Публикация

1984-04-05—Подача