1

Изобретение относится к вычислительной технике и может быть исполь- ювано в устройствах отображения информации на ЭЛТ.

Цель изобретения - расширение области применения устройства за счет увеличения формата матрицы изо ра- жения и упрощение устройства .

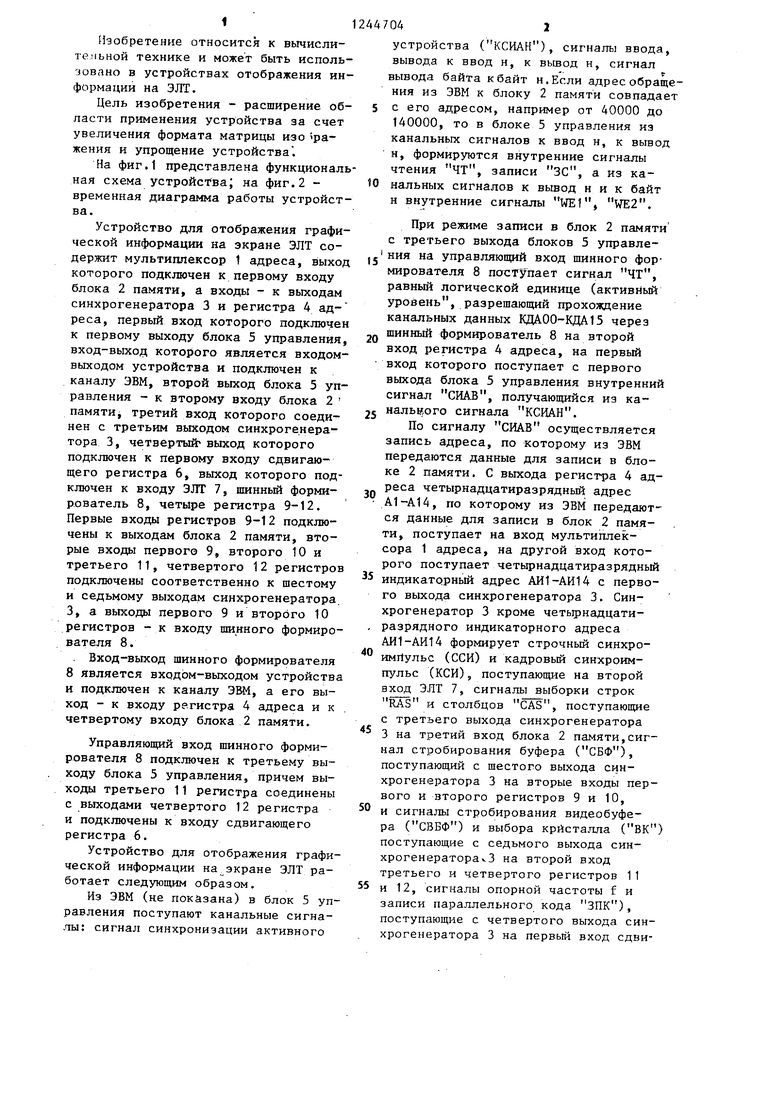

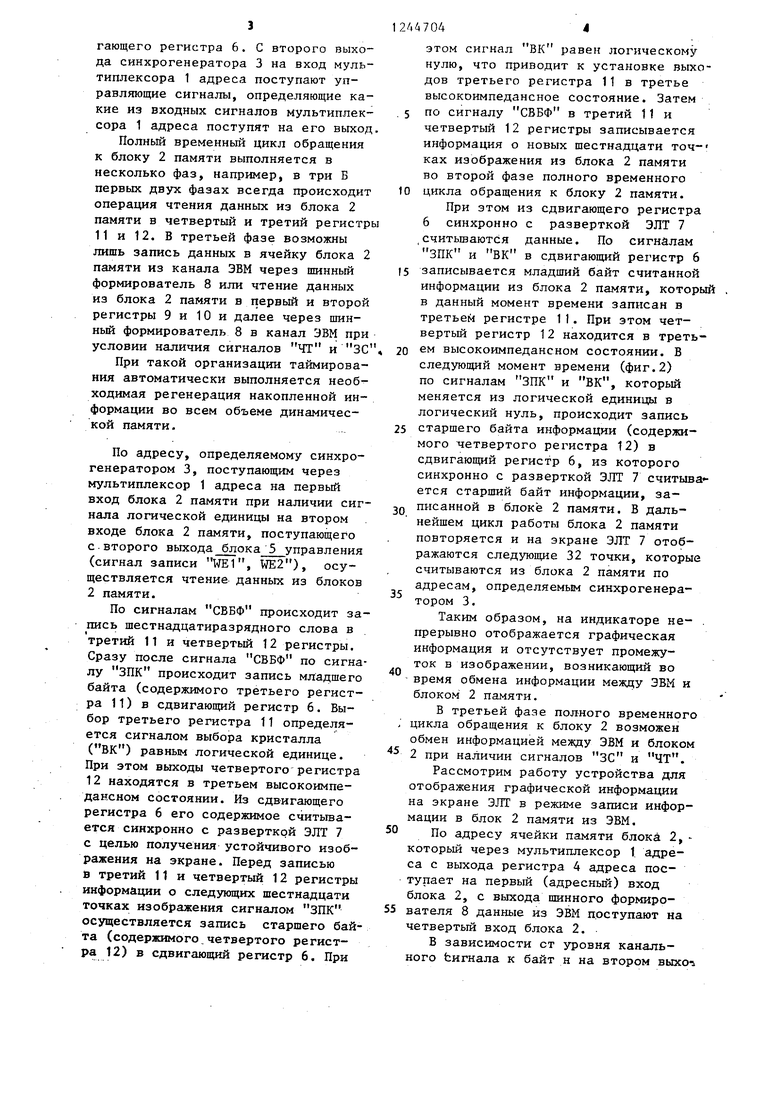

На фиг.1 представлена функциональная схема устройстваJ на фиг.2 - временная диаграмма работы устройства.

Устройство для отображения графической информации на экране ЭЛТ содержит мультиплексор 1 адреса, выход которого подключен к первому входу блока 2 памяти, а входы - к выходам синхрогенератора 3 и регистра 4 адреса, первый вход которого подключен к первому выходу блока 5 управления, вход-выход которого является входом- выходом устройства и подключен к каналу ЭВМ, второй выход блока 5 управления - к второму входу блока 2 пaмятиj третий вход которого соединен с третьим выходом синхрогенератора 3, четвертый выход которого подключен к первому входу сдвигающего регистра 6, выход которого подключен к входу ЭЛТ 7, шинный формирователь 8, четыре регистра 9-12. Первые входы регистров 9-12 подключены к выходам блока 2 памяти, вторые входы первого 9, второго 10 и третьего 11, четвертого 12 регистров подключены соответственно к шестому и седьмому выходам синхрогенератора. 3, а выходы первого 9 и второго 10 регистров - к входу шинного формирователя 8.

. Вход-выход шинного формирователя 8 является входом-выходом устройства и подключен к каналу ЭВМ, а его выход - к входу регистра 4 адреса и к четвертому входу блока 2 памяти.

Управляющий вход шинного формирователя 8 подключен к третьему выходу блока 5 управления, причем выходы третьего 11 регистра соединены с выходами четвертого 12 регистра и подключены к входу сдвигающего регистра 6.

Устройство для отображения графической информации на экране ЭЛТ работает следующим образом.

Из ЭВМ (не показана) в блок 5 управления поступают канальные сигналы: сигнал синхронизации активного

2447042

устройства (КСИАН), сигналы ввода, вывода к ввод н, к вьшод и, сигнал вывода байта к байт н.Если адрес обращения из ЭВМ к блоку 2 памяти совпадает 5 с его адресом, например от 40000 до 140000, то в блоке 5 управления из канальных сигналов к ввод н, к вывод

н, формируются внутренние сигналы чтения ЧТ, записи ЗС, а из ка- нальных сигналов к вывод ник байт н внутренние сигналы WE1, WE2.

При режиме записи в блок 2 памяти с третьего выхода блоков 5 управления на управляющий вход шинного формирователя 8 поступает сигнал ЧТ, равные логической единице (активный уровень, разрешающий прохождение канальных данных КДАОО-КДА15 через

шинньй формирователь 8 на второй

вход регистра 4 адреса, на первый вход которого поступает с первого выхода блока 5 управления внутренний сигнал СИАВ, получающийся из канальвого сигнала КСИАН.

По сигналу СИАВ осуществляется запись адреса, по которому из ЭВМ передаются данные для записи в блоке 2 памяти. С выхода регистра 4 адреса четырнадцатиразрядный адрес А1-А14, по которому из ЭВМ передаются данные для записи в блок 2 памяти, поступает на вход мультиплексора 1 адреса, на другой вход которого поступает четырнадцатиразрядный

индикаторный адрес АИ1-АИ14 с первого выхода синхрогенератора 3. Син- хрогенератор 3 кроме четырнадцати- разрядного индикаторного адреса АИ1-АИ14 формирует строчный синхро- имИульс (ССИ) и кадровьй синхроимпульс (КСИ)5 поступающие на второй вход ЭЛТ 7, сигналы выборки строк RAS и столбцов CAS, поступающие с третьего выхода синхрогенератора

3 на третий вход блока 2 памяти,сигнал стробирования буфера (СБФ), поступающий с шестого выхода синхрогенератора 3 на вторые входы первого и второго регистров 9 и 10,

и сигналы стробирования видеобуфера (СВБФ) и выбора кристалла (ВК) поступающие с седьмого выхода син- хрогенараторакЗ на второй вход третьего и четвертого регистров 11 и 12, сигналы опорной частоты f и записи параллельного кода ЗПК), поступающие с четвертого выхода синхрогенератора 3 на первый вход сдви

тающего регистра 6. С второго выхода синхрогенератора 3 на вход мультиплексора 1 адреса поступают управляющие сигналы, определяющие какие из входных сигналов мультиплексора 1 адреса поступят на его выход

Полный временный цикл обращения к блоку 2 памяти выполняется в несколько фаз, например, в три Б первых двух фазах всегда происходит операция чтения данных из блока 2 памяти в четвертый и третий регистр

11и 12. В третьей фазе возможны лишь запись данных в ячейку блока 2 памяти из канала ЭВМ через шинный формирователь 8 или чтение данных из блока 2 памяти в первьШ и второй регистры 9 и 10 и далее через шин- ньй формирователь 8 в канал ЭВМ при условии наличия сигналов ЧТ и ЗС

При такой организации таймирова- ния автоматически выполняется необходимая регенерация накопленной информации во всем объеме динамической памяти.

По адресу, определяемому синхро- генератором 3, поступающим через мультиплексор 1 адреса на первый вход блока 2 памяти при наличии сигнала логической единицы на втором входе блока 2 памяти, поступающего с второго выхода блока 5 управления (сигнал записи WEI, WE2), осуществляется чтение данных из блоков 2 памяти.

По сигналам СВБФ происходит запись шестнадцатиразрядного слова в третий 11 и четвертый 12 регистры. Сразу после сигнала СВБФ по сигналу ЗПК происходит запись младшего байта (содержимого третьего регистра 11) в сдвигающий регистр 6. Выбор третьего регистра 11 определяется сигналом выбора кристалла (ВК) равным логической единице. При этом выходы четвертого регистра

12находятся в третьем высокоимпе- дансном состоянии. Из сдвигающего регистра 6 его содержимое считьша- ется синхронно с разверткой ЭЛТ 7

с целью получения устойчивого изображения на экране. Перед записью в третий 11 и четвертый 12 регистры информации о следующих шестнадцати точках изображения сигналом ЗПК осуществляется запись старшего байта (содержимого.четвертого регистра 12) в сдвигающий регистр 6. При

этом сигнал ВК равен логическому нулю, что приводит к установке выходов третьего регистра 11 в третье Бысокоимпедансное состояние. Затем 5 по сигналу СВБФ в третий 11 и четвертый 12 регистры записывается информация о новых шестнадцати точ- ках изображения из блока 2 памяти во второй фазе полного временного 0 цикла обращения к блоку 2 памяти.

При этом из сдвигающего регистра 6 синхронно с разверткой ЭЛТ 7 ,считьшаются данные. По сигналам ЗПК и ВК в сдвигающий регистр 6 5 записывается младший байт считанной информации из блока 2 памяти, который в данный момент времени записан в третьей регистре 11. При этом четвертый регистр 12 находится в треть- 0 ем высокоимпедансном состоянии. Б следующий момент времени (фиг.2) по сигналам ЗПК и ВК, который меняется из логической единицы в логический нуль, происходит запись 5 старшего байта информации (содержимого четвертого регистра 12) в сдвигающий регистр 6, из которого синхронно с разверткой ЭЛТ 7 считыва - ется старший байт информации, за- Q писанной в блоке 2 памяти. В дальнейшем цикл работы блока 2 памяти повторяется и на экране ЭЛТ 7 отображаются следующие 32 точки, которые считываются из блока 2 памяти по адресам, определяемым синхрогенера- тором 3.

Таким образом, на индикаторе не- . прерывно отображается графическая информация и отсутствует промежуток в изображении, возникающий во время обмена информации между ЭВМ и блоком 2 памяти,

В третьей фазе полного временного , цикла обращения к блоку 2 возможен

обмен информацией между ЭВМ и блоком 2 при наличии сигналов ЗС и ЧТ. Рассмотрим работу устройства для отображения графической информации на экране ЭЛТ в режиме записи информации в блок 2 памяти из ЭВМ. 0 По адресу ячейки памяти блока 2, - который через мультиплексор t адреса с выхода регистра 4 адреса поступает на первый (адресный) вход блока 2, с выхода шинного формиро- вателя 8 данные из ЭВМ поступают на четвертый вход блока 2.

В зависимости от уровня канального Ьигнала к байт н на втором выхо1

5

0

де блока 5 управления формируются сигналы записи WE1, WE2,. определяющие режим записи: всего шестнадцатиразрядного слова; младшего или старшего байта. По сигналам с третьего выхода синхрогенератора 3 RAS, CAS в ячейке памяти блока 2 осуществляется запись информации из ЭВМ

При считывании информации из блока 2 памяти в ЭВМ по адресу, записанному в регистре 4 адреса через мультиплексор 1 адреса, из блока 2 памяти считывается содержимое его ячейки памяти.

. По сигналу СВБФ (см. временную диаграмму, на фиг.2) происходит запись содержимого ячейки блока 2 в первый 9 и второй 10 регистры, из которых через шинный формирователь 8 по сигналу ЧТ, равному логическому нулю, с третьего выхода блока 5 управления содержимое данной ячейки памяти блока 2 поступает в канал ЭВМ. Наличие сигналов RAS и CAS в третьей фазе полного временного цикла обращения к блоку 2 определяется сигналом с четвертого выхода блока 5 управления, зависящим от наличия сигналов ЧТ и ЗС. С выхода блока 5 управления в канал ЭВМ в ответ на сигнал КСИАН вырабатывается сигнал синхронизации пассивного устройства КСИПН.

Устройство позволяет ЭВМ вести работу с блоком 2 памяти как с внутренней памятью ЭВМ, что сокращает аппаратурные затраты, а также время выполнения операций обмена и модификации информации за счет сокращения числа необходимых для обмена команд процессора.

Сокращение адресного поля процессора ЭВМ несущественно в связи с наличием возможности расширения адресного поля у современных микропроцессоров до 1-4 м байт.

Обеспечение возможности у блока включения на одну фазу работы с процессоров ЭВМ нескольких фаз (например, двух) вывода информации на экран ЭЛТ позволяет увеличить скорость вывода данных из блока 2 на индикацию без увеличения временного цикла памяти блока 2.

0

5

0

5

0

5

0

5

0

Увеличение скорости вывода данных из блока 2 на индикацию позволяет получить большую матрицу изображения (например, 560400 элементов) без существенного снижения быстро- . дейстЕ Ия ЭВМ.

Формула изобретения

Устройство для отображения графической информации на экране электронно-лучевой трубки (ЭЛТ), содержащее мультиплексор адреса, выход которого подключен к первому входу блока памяти, а входы к первому и второму выходам синхрогенератора и к выходу регистра адреса, первьй вход которого подключен к первому выходу блока управления, вход-выход которого является входом-выходом устройства, второй выход блока управления - к второму входу блока памяти, третий вход которого соединен с третьим выходом синхрогенератора, четвертый выход которого подключен к первому входу сдвигающего регистра, выход которого подключен к первому )зходу 2ШТ„ второй вход которой подключен к пятому выходу синхрогенератора, отличающееся тем, что, с целью расширения области при- менения устройства за счет увеличения формата матрицы изображения и .упрощения устройства, оно содержит шинный формирователь и четыре регистра, первые входы которых подключены к выходам блока памяти, вторые входы первого, второго, третьего и четвертого регистров соответственно - к шестому и седьмому выходам синхрогенератора, а выходы первого и второго регистров подключены к входу шинного формирователя, вход- выход которого является входом-выходом устройства, выход шинного формирователя подключен к второму входу регистра адреса и к четвертому входу блока памяти, а управляющий вход его подключен к третьему выходу блока угфавления, выходы третьего и четвертого регистров подключены к второму входу сдвигающего регистра, четвертый выход блока управления подключен к входу синхрогенератора.

-NX) -v

Л/

rv

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для редактирования и контроля управляющих программ для станков с числовым программным управлением на экране электронно-лучевой трубки | 1986 |

|

SU1451676A1 |

| Устройство для отображения многоугольников на экране растрового графического видеоконтрольного блока | 1987 |

|

SU1534454A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1990 |

|

SU1795510A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1983 |

|

SU1141418A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1401470A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1984 |

|

SU1254498A2 |

| Устройство для обмена информацией между персональной ЭВМ и управляющим вычислительным комплексом | 1991 |

|

SU1838819A3 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1352477A1 |

| Устройство обработки и отображения цветных полутоновых и графических изображений | 1988 |

|

SU1658419A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах отображения информации на ЭЛТ. Цель изобретения - расширение области применения устройства за счет увеличения формата матрицы изображения.и упрощение устройства, которая достигается введением шинного формирователя,четырех регистров и соответствующих функциональных связей, что позволяет увеличить скорость вывода данных из блока памяти на индикацию и получить большую матрицу изображения (например, 560400 элементов) без существенного снижения быстродействия ЭВМ, 2 ил. W о

к,

a

памяти

СВдФ

СбФ

Редактор И. Касарда

Фие 2

Составитель С. Гришин

Техред Н.Бонкало Корректор Е. Сирохман

Заказ 3922/54Тираж 455 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

L

| Авторское свидетельство СССР | |||

| Устройство для отображения информации | 1980 |

|

SU951379A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Волкова Л.А., Гасанбеков P.M., Екимов А.В., Карпеков Ю | |||

| Д., , | |||

| Макаров Г.П., Овгоров С.Я., Симонов Ю.Н | |||

| Отображение графической информации на индикаторах с те- .левизионным растром | |||

| Ин-т физики высоких энергий | |||

| Серпухой, 1980. | |||

Авторы

Даты

1986-07-15—Публикация

1983-07-28—Подача