Изобретение относится к вычислительной технике и автоматике и может быть использовано в качестве терминала ЭВМ для контроля и редактирова- НИН управляющих программ для станков с числовым программным управлением.

Цель изобретения г упрощение и повышение быстродействия устройства.

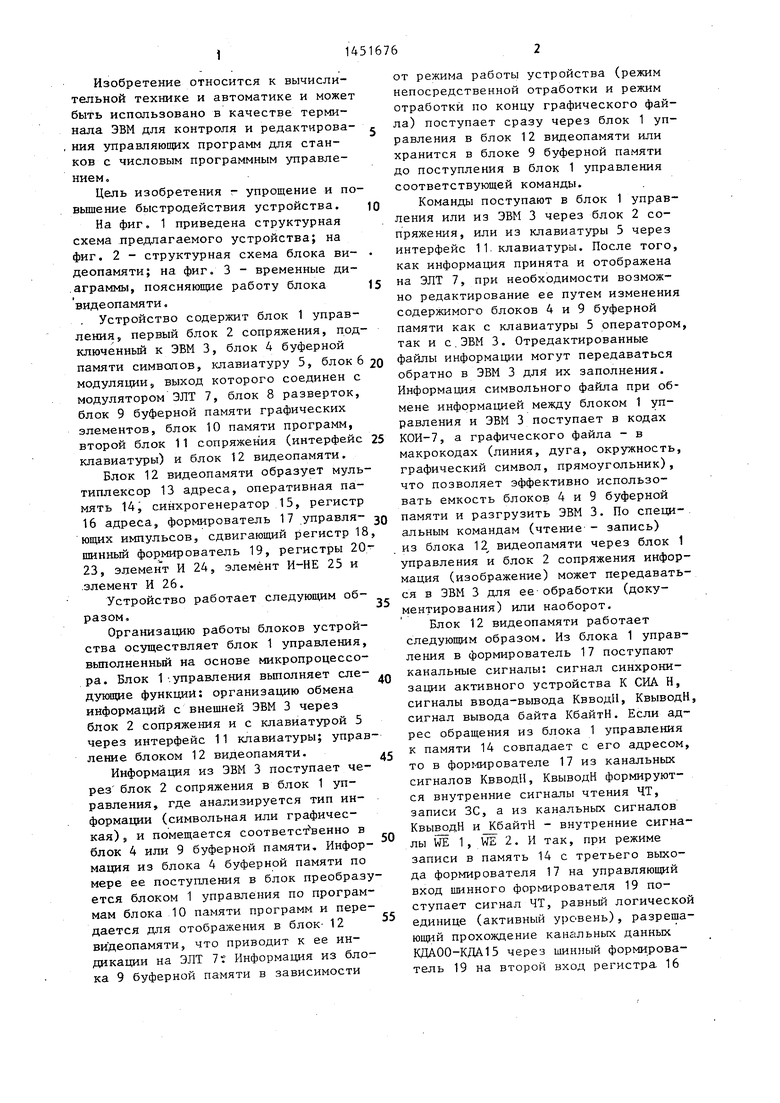

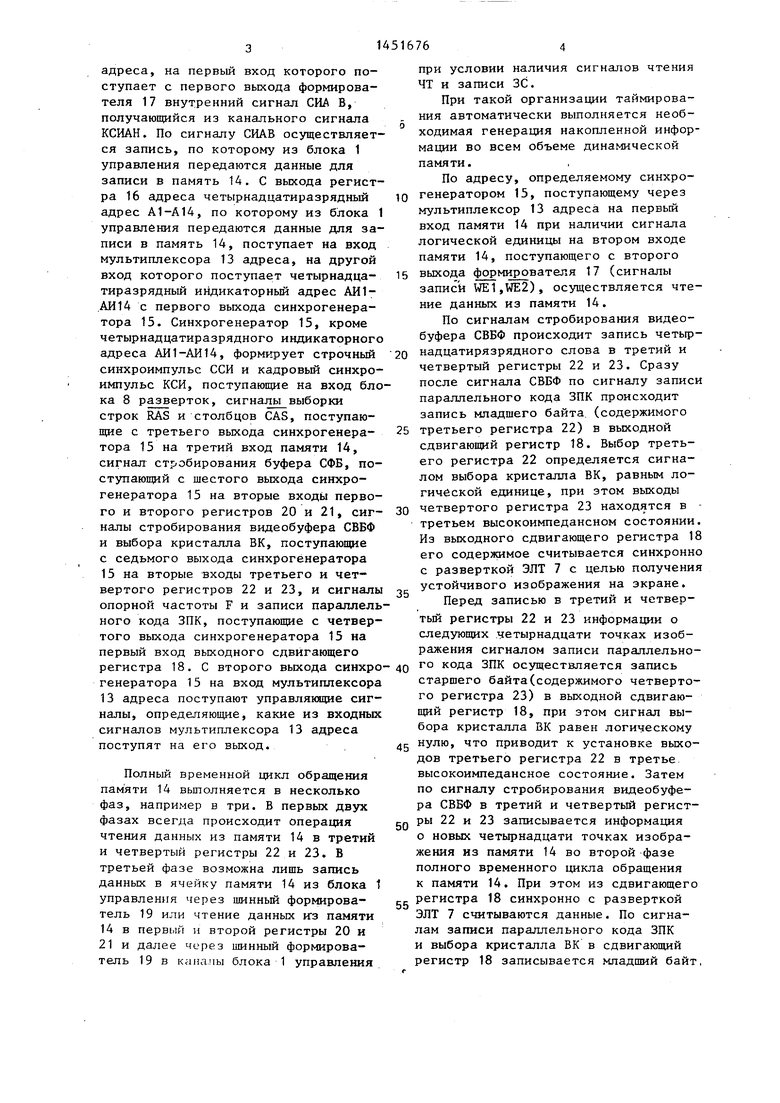

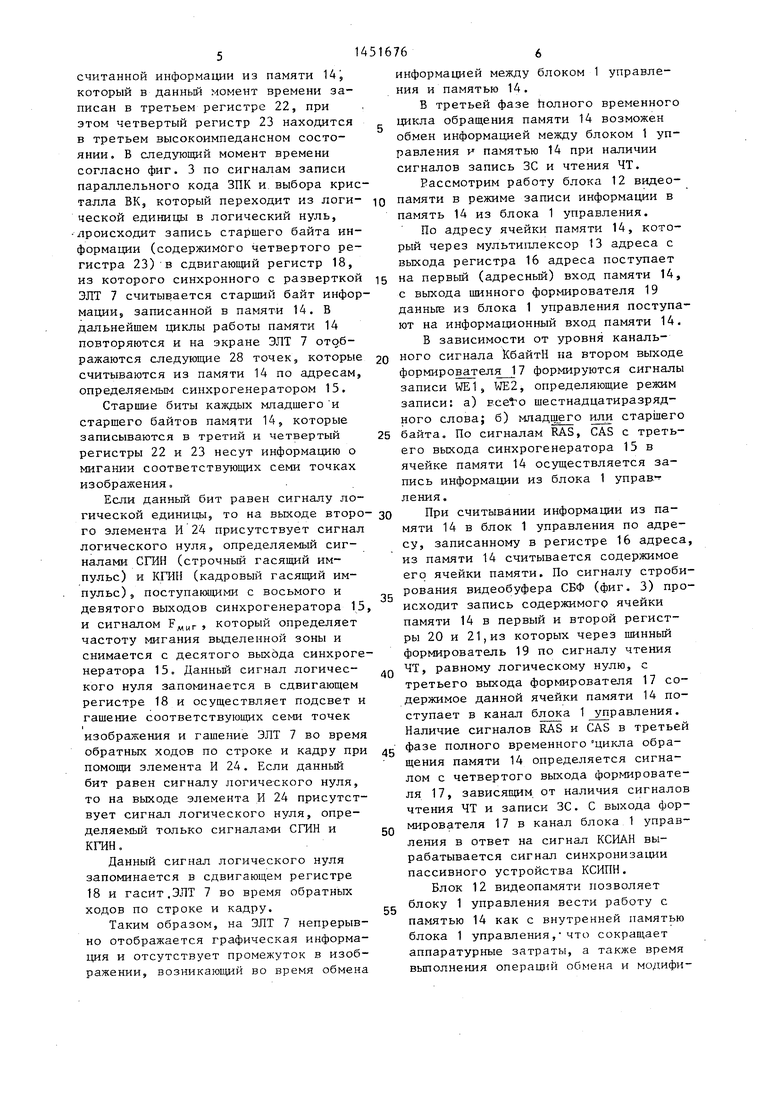

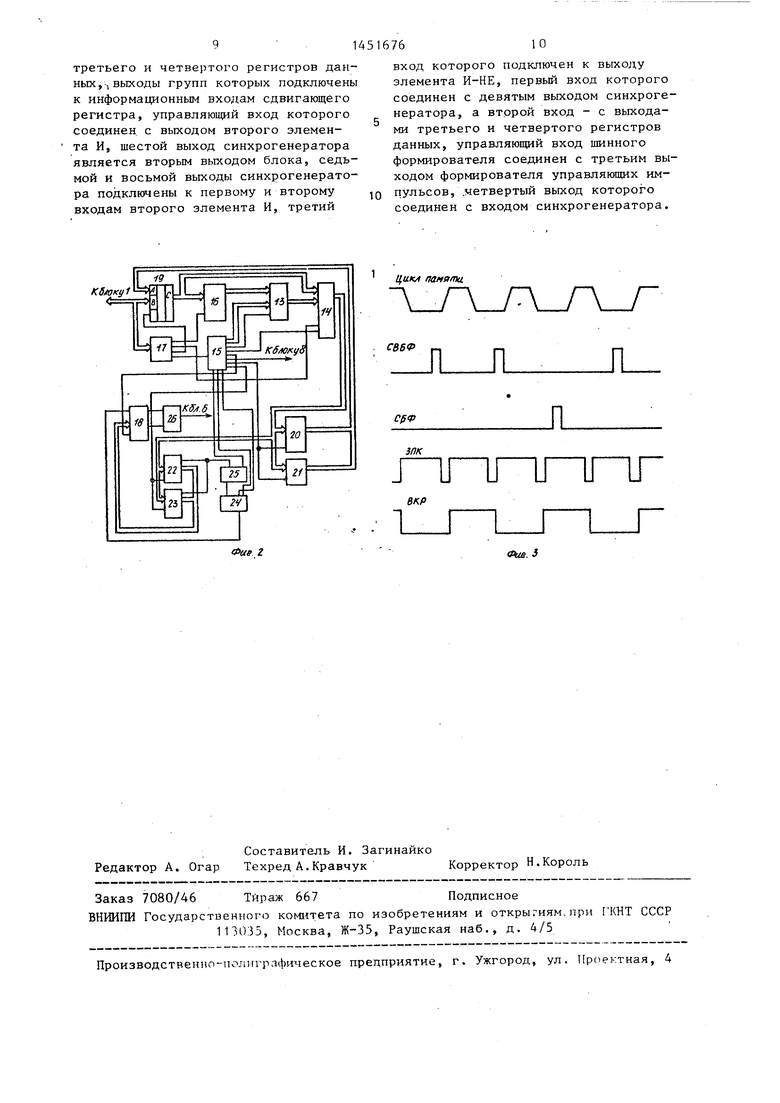

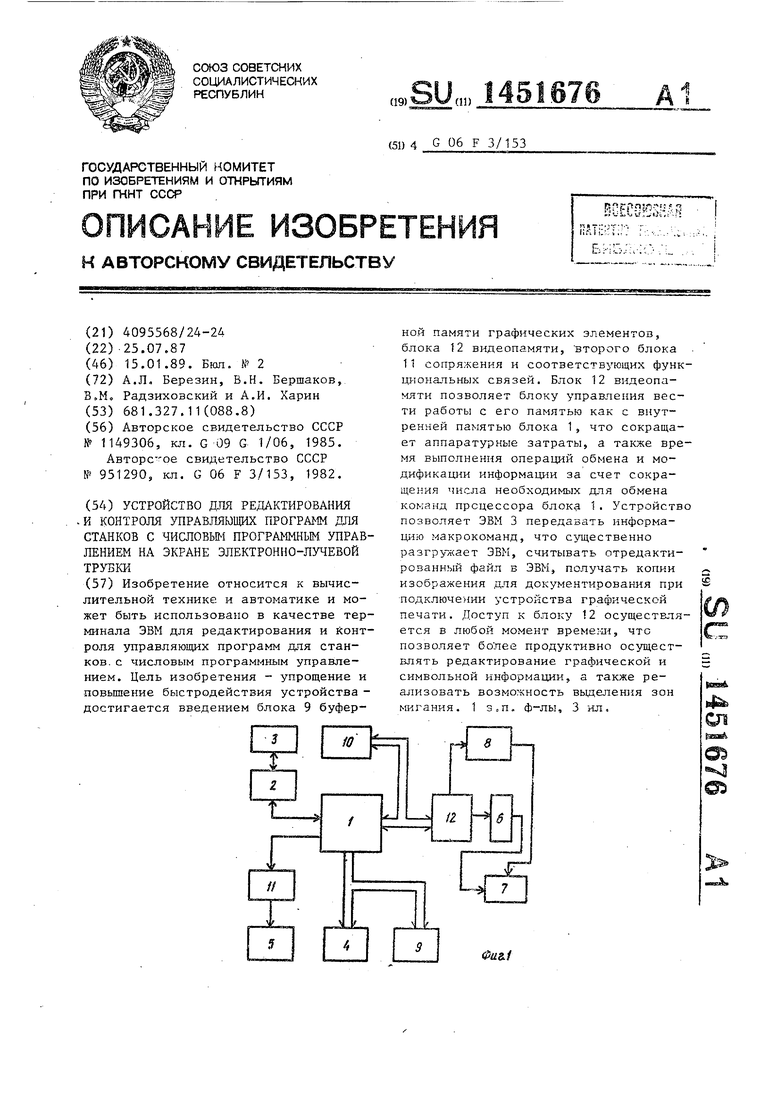

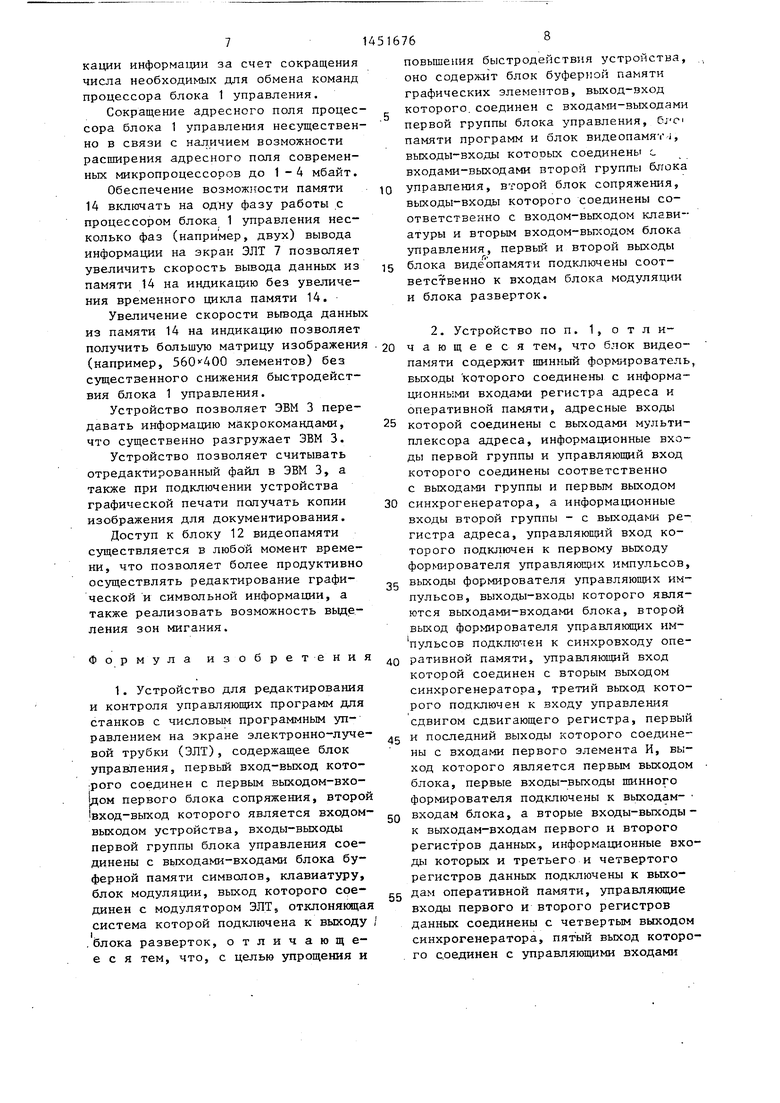

На фиг, 1 приведена структурная схема предлагаемого устройства; на фиг, 2 - структурная схема блока ви- деопамяти; на фиг, 3 - временные ди- .аграммы, поясняющие работу блока видеопамяти.

Устройство содержит блок 1 управления, первый блок 2 сопряжения, подключенный к ЭВМ 3, блок 4 буферной памяти символов, клавиатуру 5, блок 6 модуляции, выход которого соединен с модулятором ЭЛТ 7, блок 8 разверток, блок 9 буферной памяти графических элементов, блок 10 памяти программ, второй блок 11 сопряжения (интерфейс клавиатуры) и блок 12 видеопамяти.

Блок 12 видеопамяти образует мультиплексор 13 адреса, оперативная память 14, синхрогенератор 15, регистр 16 адреса, формирователь 17 управля- ющих импульсов, сдвигающий регистр 18 шинный формирователь 19, регистры 20 23, элемен т И 24, элемент И-НЕ 25 и

.элемент И 26.

Устройство работает следующим об-

разом.

Организацию работы блоков устройства осуществляет блок 1 управления, вьтолненный на основе микропроцессора. Блок 1 -.управления выполняет еле- дующие функций: организацию обмена информации с внешней ЭВМ 3 через блок 2 сопряжения и с клавиатурой 5 через интерфейс 11 клавиатуры; управление блоком 12 видеопамяти,

Информация из ЭВМ 3 поступает через блок 2 сопряжения в блок 1 управления, где анализируется тип информации (символьная или графическая) , и помещается соответст венно в блок 4 или 9 буферной памяти. Информация из блока 4 буферной памяти по мере ее поступления в блок преобраз ется блоком 1 управления по программам блока 10 памяти программ и пере дается для отображения в блок- 12 видеопамяти, что приводит к ее ин дикации на ЭЛТ 7 Информация из блока 9 буферной памяти в зависимости

.

от режима работы устройства (режим непосредственной отработки и режим отработки по концу графического файла) поступает сразу через блок 1 управления в блок 12 видеопамяти или хранится в блоке 9 буферной памяти до поступления в блок 1 управления соответствующей команды.

Команды поступают в блок 1 управления или из ЭВМ 3 через блок 2 сопряжения, или из клавиатуры 5 через интерфейс 11. клавиатуры. После того, как информация принята и отображена на ЭЛТ 7, при необходимости возможно редактирование ее путем изменения содержимого блоков 4 и 9 буферной памяти как с клавиатуры 5 оператором так и с.ЭВМ 3. Отредактированные файлы информации могут передаваться обратно в ЭВМ 3 длЯ их заполнения. Информация символьного файла при обмене информацией между блоком 1 управления и ЭВМ 3 поступает в кодах КОИ-7, а графического файла - в макрокодах (линия, дуга, окружность, графический символ, прямоугольник), что позволяет эффективно использовать емкость блоков 4 и 9 буферной памяти и разгрузить ЭВМ 3, По специальным командам (чтение - запись) из блока 12, видеопамяти через блок 1 управления и блок 2 сопряжения информация (изображение) может передаваться в ЭВМ 3 для ее обработки (документирования) или наоборот.

Блок 12 видеопамяти работает следующим образом. Из блока 1 управления в формирователь 17 поступают канальные сигналы: сигнал синхронизации активного устройства К СИЛ Н, сигналы ввода-вывода КвводН, Квывод сигнал вывода байта КбайтН, Если адрес обращения из блока 1 управления к памяти 14 совпадает с его адресом то в форг-шрователе 17 из канальных сигналов КвводИ, КвыводН формируются внутренние сигналы чтения ЧТ, записи ЗС, а из канальных сигналов КвыводН и КбайтН - внутренние сигналы WE 1, WE 2, И так, при режиме записи в память 14 с третьего выхода формирователя 17 на управляющий вход шинного формирователя 19 поступает сигнал ЧТ, равный логическо единице (активный уровень), разрешающий прохождение канальных данных КДАОО-КДА15 через шинный формирователь 19 на второй вход регистра 16

адреса, на первый вход которого поступает с первого выхода формирователя 17 внутренний сигнал СИА В, получающийся из канального сигнала КСИАН. По сигналу СИАВ осуществляется запись, по которому из блока 1 управления передаются данные для записи в память 14. С выхода регистра 16 адреса четырнадцатиразрядный адрес А1-А14, по которому из блока 1 управления передаются данные для записи в память 14, поступает на вход мультиплексора 13 адреса, на другой вход которого поступает четырнадцатиразрядный индикаторньй адрес АИ1- .АШ4 с первого выхода синхрогенера- тора 15. Синхрогенератор 15, кроме четырнадцатиразрядного индикаторного адреса АИ1-АИ14, формирует строчный синхроимпульс ССИ и кадровый синхроимпульс КСИ, поступающие на вход блока 8 разверток, сигналы выборки строк RAS и столбцов CAS, поступающие с третьего выхода синхрогенера- тора 15 на третий вход памяти 14, сигнал стробирования буфера СФБ, поступающий с шестого выхода синхро- генератора 15 на вторые входы первого и второго регистров 20 и 21, сигналы стробирования видеобуфера СВБФ и выбора кристалла ВК, поступающие с седьмого выхода синхрогёнератора 15 на вторые входы третьего и четвертого регистров 22 и 23, и сигналы опорной частоты F и записи параллельного кода ЗПК, поступающие с четвертого выхода синхрогёнератора 15 на первый вход выходного сдвигающего

10

при условии наличия сигналов чтени ЧТ и записи ЗС.

При такой организации таймирова ния автоматически выполняется необ ходимая генерация накопленной инфо мации во всем объеме динамической памяти.

По адресу, определяемому синхро генератором 15, поступающему через мультиплексор 13 адреса на первьм вход памяти 14 при наличии сигнала логической единицы на втором входе памяти 14, поступающего с второго 15 выхода формирователя 17 (сигналы

записи WE1,WE2), осуществляется чт ние данных из памяти 14.

По сигналам стробирования видео буфера СВБФ происходит запись четь надцатирязрядного слова в третий и четвертый регистры 22 и 23. Сразу после сигнала СВБФ по сигналу запи параллельного кода ЗПК происходит запись младшего байта, (содержимого 25 третьего регистра 22) в выходной сдвигающий регистр 18. Выбор треть его регистра 22 определяется сигна лом выбора кристалла ВК, равным ло гической единице, при этом выходы четвертого регистра 23 находятся в третьем высокоимпедансном состояни Из выходного сдвигающего регистра его содержимое считывается синхрон с разверткой ЭЛТ 7 с целью получен устойчивого изображения на экране

Перед записью в третий и четвер

тьш регистры 22 и 23 информации о следующих .четырнадцати точках изоб ражения сигналом записи параллельн

20

30

35

регистра 18. С второго выхода синхро- 40 ° ° осуществляется запись

старшего байта(содержимого четверт го регистра 23) в выходной сдвигаю пщй регистр 18, при этом сигнал вы бора кристалла ВК равен логическом 4g нулю, что приводит к установке вых дов третьего регистра 22 в третье высокоимпедансное состояние. Затем по сигналу стробирования видеобуфе ра СВБФ в третий и четвертый регис ры 22 и 23 записывается информация о новых четырнадцати точках изобра жения из памяти 14 во второй фазе полного временного цикла обращения к памяти 14. При этом из сдвигающе регистра 18 синхронно с разверткой ЭЛТ 7 считываются данные. По сигна лам записи параллельного кода ЗПК и выбора кристалла ВК в сдвигающий регистр 18 записывается младший ба

генератора 15 на вход мультиплексора

13адреса поступают управлянлцие сигналы, определяющие, какие из входных сигналов мультиплексора 13 адреса поступят на его выход.

Полный временной цикл обращения памяти 14 выполняется в несколько фаз, например в три. В первых двух фазах всегда происходит операция чтения данных из памяти 14 в третий и четвертый регистры 22 и 23. В третьей фазе возможна лишь запись данных в ячейку памяти 14 из блока 1 управления через шинньй формирователь 19 или чтение данных и з памяти

14в первый и второй регистры 20 и 21 и далее через шинный формирователь 19 в каналы блока 1 управления

0

при условии наличия сигналов чтения ЧТ и записи ЗС.

При такой организации таймирова- ния автоматически выполняется необходимая генерация накопленной информации во всем объеме динамической памяти.

По адресу, определяемому синхро- генератором 15, поступающему через мультиплексор 13 адреса на первьм вход памяти 14 при наличии сигнала логической единицы на втором входе памяти 14, поступающего с второго 5 выхода формирователя 17 (сигналы

записи WE1,WE2), осуществляется чтение данных из памяти 14.

По сигналам стробирования видеобуфера СВБФ происходит запись четьф- надцатирязрядного слова в третий и четвертый регистры 22 и 23. Сразу после сигнала СВБФ по сигналу записи параллельного кода ЗПК происходит запись младшего байта, (содержимого 5 третьего регистра 22) в выходной сдвигающий регистр 18. Выбор третьего регистра 22 определяется сигналом выбора кристалла ВК, равным логической единице, при этом выходы четвертого регистра 23 находятся в - третьем высокоимпедансном состоянии. Из выходного сдвигающего регистра 18 его содержимое считывается синхронно с разверткой ЭЛТ 7 с целью получения устойчивого изображения на экране.

Перед записью в третий и четвертьш регистры 22 и 23 информации о следующих .четырнадцати точках изображения сигналом записи параллельно

0

5

40 ° ° осуществляется запись

старшего байта(содержимого четвертого регистра 23) в выходной сдвигаю- пщй регистр 18, при этом сигнал выбора кристалла ВК равен логическому 4g нулю, что приводит к установке выходов третьего регистра 22 в третье высокоимпедансное состояние. Затем по сигналу стробирования видеобуфера СВБФ в третий и четвертый регистры 22 и 23 записывается информация о новых четырнадцати точках изображения из памяти 14 во второй фазе полного временного цикла обращения к памяти 14. При этом из сдвигающего регистра 18 синхронно с разверткой ЭЛТ 7 считываются данные. По сигналам записи параллельного кода ЗПК и выбора кристалла ВК в сдвигающий регистр 18 записывается младший байт

50

55

считанной информации из памяти 14, который в данный момент времени записан в третьем регистре 22, при этом четвертый регистр 23 находится в третьем высокоимпедансном состоянии, В следующий момент времени согласно фиг. 3 по сигналам записи параллельного кода ЗПК и выбора крис

талла ВК, который переходит из логической единицы в логический нуль, лроисходит запись старшего байта информации (содержимого четвертого регистра 23) В сдвигающий регистр 18, из которого синхронного с разверткой ЭЛТ 7 считывается старший байт информации, записанной в памяти 14. В дальнейшем циклы работы памяти 14 повторяются и на экране ЭЛТ 7 отображаются следующие 28 точек, которые считываются из памяти 14 по адресам, определяемым синхрогенератором 15.

Старшие биты каждых младшего и старшего байтов памяти 14, которые записываются в третий и четвертый регистры 22 и 23 несут информацию о мигании соответствующих семи точках изображения

Если данный бит равен сигналу логической единицы, то на выходе второ го элемента И 24 присутствует сигнал логического нуля, определяемый сигналами СГИН (строчный гасящий импульс) и КГИН (кадровый гасящий импульс) 9 пocтyпaюш ми с восьмого и

девятого выходов синхрогенератора 15

и сигналом F.

который определяет

частоту мигания выделенной зоны и снимается с десятого выхйда синхрогенератора 15. Данньм сигнал логического нуля запоминается в сдвигающем регистре 18 и осуществляет подсвет и гашение соответствуюш 1х семи точек изображения и гашение ЭЛТ 7 во время обратных ходов по строке и кадру при помош элемента И 24. Если данный бит равен сигналу логического нуля, то на выходе элемента И 24 присутствует сигнал логического нуля, определяемый только сигналами СГИН и КГИН.

Данный сигнал логического нуля запоминается в сдвигающем регистре 18 и гасит.ЭЛТ 7 во время обратных ходов по строке и кадру.

Таким образом, на ЭЛТ 7 непрерывно отображается графическая информация и отсутствует промежуток в изображении, возникающий во время обмена

0

0

зо

информацией между блоком 1 управления и памятью 14.

В третьей фазе Ьолного временного цикла обращения памяти 14 возможен обмен информацией между блоком 1 управления и памятью 14 при наличии сигналов запись ЗС и чтения ЧТ.

Рассмотрим работу блока 12 видеопамяти в режиме записи информации в память 14 из блока 1 управления.

По адресу ячейки памяти 14, который через мультиплексор 13 адреса с выхода регистра 16 адреса поступает 5 на первый (адресный) вход памяти 14, с выхода шинного формирователя 19 данные из блока 1 управления поступают на информационный вход памяти 14.

В зависимости от уровня канального сигнала КбайтН на втором выходе формирователя 17 формируются сигналы записи WE1, WE2, определяющие режим записи: а) шестнадцатиразрядного слова; б) младщ его или старшего 25 байта. По сигналам RAS, CAS с третьего выхода синхрогенератора 15 в ячейке памяти 14 осуществляется запись информации из блока 1 управ.т ления.

При считывании информации из памяти 14 в блок 1 управления по адресу, записанно1угу в регистре 16 адреса, из памяти 14 считывается содержимое его ячейки памяти. По сигналу строби- рования видеобуфера СБФ (фиг. 3) происходит запись содержимого ячейки памяти 14 в первый и второй регистры 20 и 21, из которых через шинньй формирователь 19 по сигналу чтения ЧТ, равному логическому нулю, с третьего выхода формирователя 17 содержимое данной ячейки памяти 14 поступает в канал блока 1 управления. Наличие сигналов RAS и CAS в третьей фазе полного временного цикла обращения памяти 14 определяется сигналом с четвертого выхода формирователя 17, зависящей от наличия сигналов чтения ЧТ и записи ЗС. С выхода формирователя 17 в канал блока 1 управления в ответ на сигнал КСИАН вырабатывается сигнал синхронизации пассивного устройства КСИПН.

Блок 12 видеопамяти позволяет блоку 1 управления вести работу с памятью 14 как с внутренней памятью блока 1 управления,-что сокращает аппаратурные затраты, а также время выполнения операций обмена и модифи35

40

45

50

55

кации информации за счет сокращения числа необходимых для обмена команд процессора блока 1 управления.

Сокращение адресного поля процессора блока 1 управления несущественно в связи с наличием возможности расширения адресного поля современных микропроцессоров до 1 - 4 мбайт.

Обеспечение возможности памяти 14 включать на одну фазу работы с процессором блока 1 управления несколько фаз (например, двух) вывода информации на экран ЭЛТ 7 позволяет увеличить скорость вывода данных из памяти 14 на индикацию без увеличения временного цикла памяти 14.

Увеличение скорости вьгоода данных из памяти 14 на индикацию позволяет получить большую матрицу изображения (например, 560400 элементов) без существенного снижения быстродействия блока 1 управления.

Устройство позволяет ЭВМ 3 передавать информацию макрокомандами, что существенно разгружает ЭВМ 3.

Устройство позволяет считывать отредактированный файл в ЭВМ 3, а также при подключении устройства графической печати получать копии изображения для документирования.

Доступ к блоку 12 видеопамяти существляется в любой момент времени, что позволяет более продуктивно осуществлять редактирование графической и символьной информации, а также реализовать возможность вьще- ления зон мигания.

Формула изобретени

1. Устройство для редактирования и контроля управляющих программ для станков с числовым программным управлением на экране электронно-лучевой трубки (ЭЛТ), содержащее блок управления, первый вход-выход кото- :рого соединен с первым выходом-входом первого блока сопряжения, второ (вход-выход которого является входом выходом устройства, входы-выходы первой группы блока управления соединены с выходами-входами блока буферной памяти символов, клавиатуру, блок модуляции, выход которого соединен с модулятором ЭЛТ, отклоняюща система которой подключена к выходу .блока разверток, отличающееся тем, что, с целью упрощения и

повышения быстродействия устройства, оно содержиЧ блок буферной памяти графических элементов, выход-вход которого.соединен с входаьш-выходами первой группы блока управления, бт памяти программ и блок видеопамяти, выходы-входы которых соединены с входами-выходами второй группы 6j-roKa управления, второй блок сопряжения, выходы-входы которого соединены соответственно с входом-выходом клавиатуры и вторым входом-выходом блока управления, первый и второй выходы блока виде опамяти подключены соответственно к входам блока модуляции и блока разверток.

2, Устройство по п. 1, о т л и- 0 чающееся тем, что блок видеопамяти содержит шинный формирователь, выходы которого соединены с информационными входами регистра адреса и оперативной памяти, адресные входы 5 которой соединены с выходами мультиплексора адреса, информационные входы первой группы и управляющий вход которого соединены соответственно с выходами группы и первым выходом 0 синхрогенератора, а информационные входы второй группы - с выходами регистра адреса, управляющий вход которого подключен к первому выходу формирователя управляющих импульсов, с выходы формирователя управляющих импульсов, выходы-входы которого являются выходами-входами блока, второй выход формирователя управлякяцих им- пульсов подключен к синхровходу опе- 0 ративной памяти, управляющий вход которой соединен с вторым выходом синхрогенератора, третий выход которого подключен к входу управления сдвигом сдвигающего регистра, первый 5 и последний выходы которого соединены с входами первого элемента И, выход которого является первым выходом блока, первые входы-выходы шинного формирователя подключены к выходам- Q входам блока, а вторые входы-выходы- к выходам-входам первого и второго регистров данных, информационные входы которых и третьего и четвертого регистров данных подключены к выхо- сс дам оперативной памяти, управляющие входы первого и второго регистров данных соединены с четвертым выходом синхрогенератора, пятый выход которого соединен с управляющими входами

третьего и четвертого регистров данных,- выходы групп которых подключены к информационным входам сдвигающего регистра, управляющий вход которого соединен с выходом второго элемента И, шестой выход синхрогенератора является вторым выходом блока, седьмой и восьмой выходы синхрогенератора подключены к первому и второму входам второго элемента И, третий

вход которого подключен к выходу элемента И-НЕ, первый вход которого соединен с девятым выходом синхрогенератора, а второй вход - с выходами третьего и четвертого регистров данных, управляющий вход шинного формирователя соединен с третьим выходом формирователя управляющих импульсов, .четвертый выход которого соединен с входом синхрогенератора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1983 |

|

SU1244704A1 |

| Устройство для отображения многоугольников на экране растрового графического видеоконтрольного блока | 1987 |

|

SU1534454A1 |

| Устройство для обработки и отображения видеоинформации | 1988 |

|

SU1748284A1 |

| Устройство для формирования видеосигнала | 1990 |

|

SU1741124A1 |

| ЭВМ | 1990 |

|

RU2024928C1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1990 |

|

SU1795510A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1991 |

|

SU1807516A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство для обмена информацией между персональной ЭВМ и управляющим вычислительным комплексом | 1991 |

|

SU1838819A3 |

Изобретение относится к вычислительной технике и автоматике и может быть использовано в качестве терминала ЭВМ для редактирования и контроля управляющих программ для станков, с числовым программным управлением. Цель изобретения - упрощение и повышение быстродействия устройства - достигается введением блока 9 буферной памяти графических элементов, блока 12 видеопамяти, второго блока 11 сопряжения и соответствующих функциональных связей. Блок 12 видеопамяти позволяет блоку управления вести работы с его памятью как с внутренней памятью блока 1, что сокращает аппаратурные затраты, а также время выполнения операций обмена и модификации информации за счет сокращения числа необходимых для обмена команд процессора блока 1 . стройство позволяет ЭВМ 3 передавать информа- макрокоманд, что существенно разгружает ЭВМ, считывать отредактированный файл в ЭВМ, получать копии изображения для документирования при подключении устройства графической печати. Доступ к блоку 12 осуществляется в любой момент времеми, что позволяет бо лее продуктивно осуществлять редактирование графической и символьной информации, а также реализовать возможность вьщелешгя зон мигания. 1 з.п, ф-лы, 3 ил. «5

Кдюку 1

Z

Цикл тняти.

СВВФ

п п

л

зпк

1ППГ

1

ВКР

Фив. i

| Устройство для индикации | 1983 |

|

SU1149306A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Устройство для контроля и редактирования управляющих программ для станков с числовым программным управлением на экране электронно-лучевой трубки | 1977 |

|

SU951290A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-01-15—Публикация

1986-07-25—Подача