тельности - положительного полупериода, а другой - отрицательного. Импульсы БС 3 поступают сразу на коммутатор 5 и через элемент И и одновре- менно на входы формировате-гтя импульсов сброса 6 и распределит гля импульсов (РИ) 8, Импульс с выхода. УДЧ 4 поступает.на информационный вход триггера 7 и переводит его в другое состояние, Появленив логического нуля на выходе РИ 8 прекращает прохождение тактовых импульс.ов через комму1

Изобретение относится к преобразовательной технике и может быть использовано для управления многофазными статическими преобразователями.

Целью изобретения является повышение быстродействия и точности регулирования.

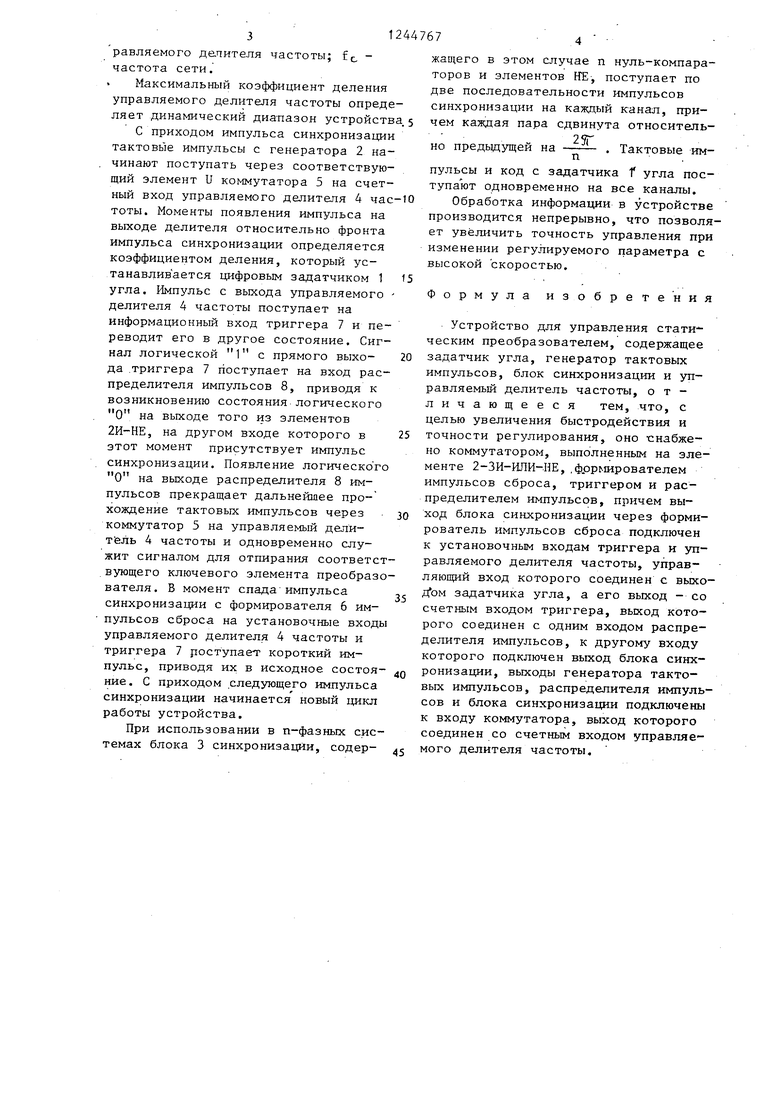

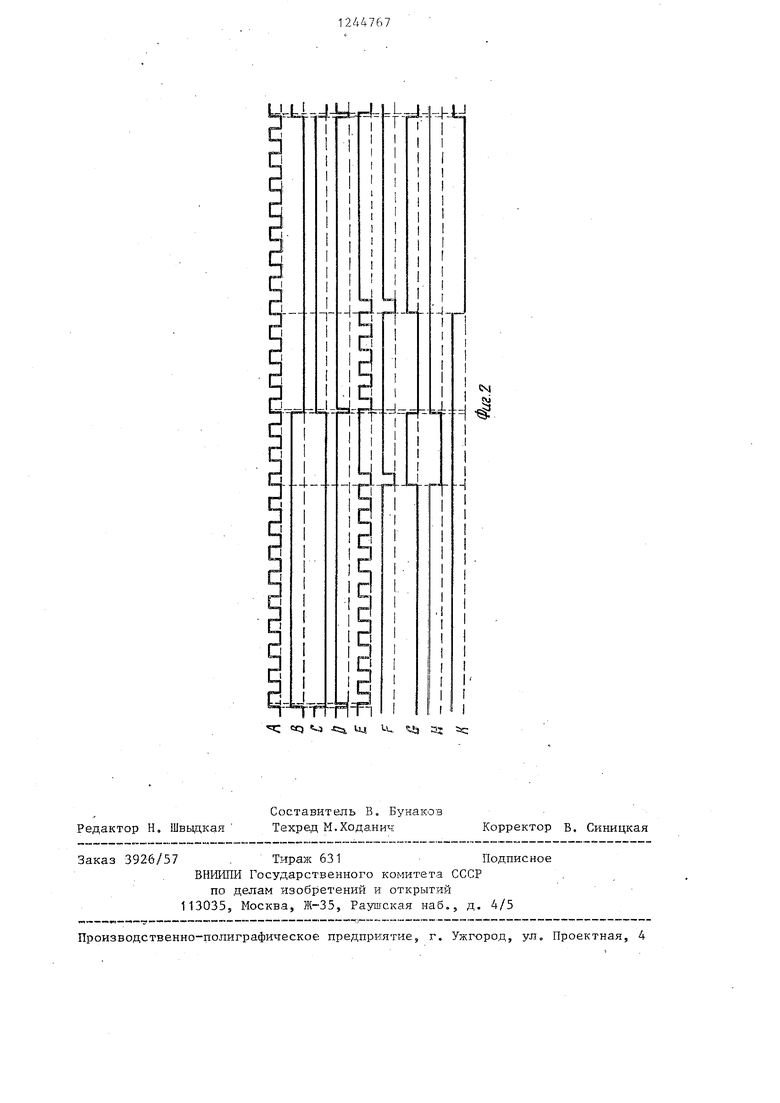

На фиг, 1 приведена функциональна схема устройства; на фиг, 2 - временные диаграммы, поясняющие работу устройства при управлении трехфазным мостовым преобразователем.

Функцио.нальная схема устройства содержит задатчик 1 угла, генератор тактовых импульсов, блок 3 синхронизации, управляемый делитель 4 частоты, коммутатор 5, формирователь 6 импульсов сброса, триггер 7 и распределитель 8 импульсов,

Управляемьш делитель 4 частоты имеет управляющий счетный и установочный входы, соединенные соответственно с выходами задатчика 1 угла, коммутатора 5 и формирователя 6 им- нульсов сброса. Входы коммутатора 5 соединены соответственно с выходами -генератора 2 тактовых импульсов, блока 3 синхронизации и распределителя В импульсовJ выход блока 3 синхронизации подключен, помимо коммутатора, к входам формирователя 6 импульсов сброса и распределителя 8 Импульсов; счетный вход триггера 7 Подключен к выходу управляемого делителя 4 частоты, а его установочный вход - к выходу формирователя 6 импульсов сброса, причем выход триггетатор 5 на УЦЧ 4 и служит сигналом для отпирания соответствующего ключа преобразователя. При использовании в п-фазных системах БС 3, содержащего п нуль-компараторов и элементов НЕ, поступает по две последовательности импульсов синхронизации на каждый канал, причем каждая пара сдвинута относительно предьщущей на 25Г/П,. Обработка информации производится непрерывно, что позволяет увеличить точность управления. 2 ил.

ра 7 подключен к входу распределителя 8 импульсов.

Блок 3 синхронизации представляет собой нуль-компаратор и элемент НЕ, а коммутатор - элемент 2-ЗИ-ИЛИ-НЕ. Формирователь 6 импульсов сброса представляет собой обычную схему формирователя коротких импульсов по фронту и спаду входного сигнала, . Распределитель импульсов представляет собой схему, состоящую из двух элементов 2И-НЕ,

Устройство работает следующим образом,

Блок 3 синхронизации вырабатывает две последовательностр} прямоугольных импульсов, сформированных из на- пряжения сети, причем фронт и спад импульсов соответствуют моментам пе- рехода сетевого напряжения через

нуль, вершины импульсов одной последовательности - положительным полупериодам сетевого напряжения, а вершины импульсов другой - отрицательным.

С выхода блока 3 синхрониза1дии импульсы одной последовательности поступают на первый элемент И коммутатора, а импульсы другой последова- тельности - на второй элемент И, Одновременно импульсы синхронизации поступают на входы формирователя 6 импульсов сброса и распределителя 8 м тульсов,

Частоту тактовых импульсов выбирают из расчета (, где га - максим11льный коэффициент деления уп

равляемого депителя частоты; f, - частота сети.

Максимальный коэффициент деления управляемого делителя частоты определяет динамический диапазон устройств

С приходом импульса синхронизации тактовые импульсы с генератора 2 начинают поступать через соответствующий элемент U коммутатора 5 на счетный вход управляемого делителя 4 час тоты. Моменты появления импульса на выходе делителя относительно фронта импульса синхронизации определяется коэффициентом деления, который устанавливается цифровым задатчиком 1 угла. Импульс с выхода управляемого делителя 4 частоты поступает на информационный вход триггера 7 и переводит его в другое состояние. Сигнал логической 1 с прямого выхода .триггера 7 поступает на вход распределителя импульсов 8, приводя к возникновению состояния логического О на выходе того из элементов 2И-НЕ, на другом входе которого в этот момент присутствует импульс синхронизации. Появление логического О на выходе распределителя 8 импульсов прекращает дальнейшее прохождение тактовых импульсов через коммутатор 5 на управляемый делитель 4 частоты и одновременно служит сигналом для отпирания соответствующего ключевого элемента преобразователя. В момент спада импульса синхронизации с формирователя 6 импульсов сброса на установочные входы управляемого делителя 4 частоты и триггера 7 роступает короткий импульс, приводя их в исходное состояние. С приходом следующего импульса синхронизации начинается новый цикл работы устройства.

При использовании в п-фазных системах блока 3 синхронизации, содер-

5

0

5

5

0

5

0

жащего в этом случае п нуль-компараторов и элементов НЕ, поступает по две последовательности импульсов синхронизации на каждый канал, причем каждая пара сдвинута относитель2Г

но предыдущей на

Тактовые имп

пульсы и код с задатчика f угла поступают одновременно на все каналы.

Обработка информации в устройстве производится непрерывно, что позволяет увеличить точность управления при изменении регулируемого параметра с высокой скоростью.

Формула изобретения

Устройство для управления стати- ческим преобразователем, содержащее задатчик угла, генератор тактовых импульсов, блок синхронизации и управляемый делитель частоты, отличающееся тем, что, с целью увеличения быстродействия и точности регулирования, оно -снабжено коммутатором, выполненным на элементе 2-ЗИ-ИЛИ-НЕ,.фррмирователем импульсов сброса, триггером и распределителем импульсов, причем выход блока синхронизации через формирователь импульсов сброса подключен к установочным входам триггера и управляемого делителя частоты, управляющий вход которого соединен с выхо- ffoM задатчика угла, а его выход - со счетным входом триггера, выход которого соединен с одним входом распределителя импульсов, к другому входу которого подключен выход блока синхронизации, выходы генератора тактовых импульсов, распределителя импульсов и блока синхронизации подключены к входу коммутатора, выход которого соединен со счетным входом управляемого делителя частоты.

.-J.:KM

ecj «-Л -е U4 l-u Чэ

Редактор Н, Швьщкая

Составитель В, Бунакоз Техред М.Ходанич

Заказ 3926/57 . Тираж 631Подписное

ВНЖШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Рауш:ская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

Корректор Б. Синицкая

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 2002 |

|

RU2252450C2 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Устройство для испытаний датчиков давления | 1983 |

|

SU1129624A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Устройство для отображения информации на экране телевизионного приемника | 1987 |

|

SU1425770A2 |

| Делитель частоты периодических сигналов сложной формы | 1986 |

|

SU1356179A1 |

| Устройство для управления двухтактным преобразователем напряжения | 1987 |

|

SU1624635A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Цифровое устройство одноканального фазового управления вентильным преобразователем | 1974 |

|

SU674182A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

Изобретение относится к электронике и может быть использовано для управления многофазными вторичными источниками электропитания. Цель изобретения - повышение быстродействия и точности регулирования. .Устройство содержит генератор тактовых импульсов, задатчик угла 1, управляемый делитель частоты (УДЧ) 4 и блок синхронизации (БС) 3, вырабатывающий две последовательности прямоугольных импульсов, причем фронт и спад импульсов соответствуют переходу через нуль сетевого напряжения, вершины импульсов одной последова(О 4 4 Ч О5 Ч

| Христов П.И., Тодоров П.С | |||

| Системы цифрового управления силовыми тиристорными преобразователями | |||

| М.: ВЭЛК, секция 6, докл | |||

| Способ сужения чугунных изделий | 1922 |

|

SU38A1 |

| Устройство для управления статическим преобразователем | 1980 |

|

SU902200A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1986-07-15—Публикация

1983-02-21—Подача