щим входом - с вторым импульсным выходом распределителя импульсов, третий преобразователь аналог - длительность импульса соединен информационным входом с третьим входом устройства,выходом - через элемент i НЕ с первым входом четвертого элемента HS а управляющим входом - с третьим импульсным выходом распределителя импульсов, диа выхода уровня которого соединены соответственно через второй элемент ИЛИ и четвертый элемент И с входами блока сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для допускового контроля объекта | 1984 |

|

SU1246060A1 |

| Многоканальное устройство для до-пуСКОВОгО КОНТРОля пАРАМЕТРОВ | 1979 |

|

SU840819A1 |

| Устройство для допускового контроля | 1978 |

|

SU771619A1 |

| Устройство для допускового контроляОб'ЕКТА | 1979 |

|

SU834678A1 |

| Устройство для допускового контроля | 1980 |

|

SU898390A2 |

| Устройство для контроля экспоненциальных процессов | 1990 |

|

SU1732331A1 |

| Устройство для контроля переходных режимов объекта | 1989 |

|

SU1817062A1 |

| Устройство для контроля экспоненциальных процессов | 1986 |

|

SU1310781A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| Устройство для контроля экспоненциальных процессов | 1987 |

|

SU1500997A1 |

УСТРОЙСТВО ДЛЯ ДОПУСКОВОГО. КОНТРОЛЯ ПАРАМЕТРОВ ОБЪЕКТА, содержащее первый преобразователь аналогдлительность импульса, информационный вход которого соединен с первым входом устройства, выход через блок сравнения - с блоком индикации, а управляющий вход - с первым импульсным выходом распределителя импуль- ; сов, подключенного входом через первый злемен,- И к выходу переноса последовательного сумматора, выход суммы которого подсоединен к информационному входу регистра сдвига, а йервый вход - к выходу первого злемента ИЛИ, соединенного первым входом с выходом регистра сдвига, вторЫм и третьим входами - с выходами второго и третьего злементов И соответственно, блок синхронизации, группа выходов котЬрого соединена через блок уставок с первыми входами второго и третьего элементов И, вторые входы которых подключены к выходам первого и второго триггеров соответственно, управляющий выход (Л блока синхронизации соединен с управляющим входом регистра сдвига, с второй вход последовательного сумматора подключен к первому выходу группы выходов блока синхронизации, последний выход из которых о соединен с вторым входом первого СП элемента И и с. нулевыми входами перо вого и ВТ9РОГО триггеров, единичные входы которых подключены к первому 00 4 и второму импульсным выходам распредехштеля импульсов соответственно, отличающееся тем, что, с целью повьшения достоверности кон троля переходных процессов, в него введены второй и третий преобразова тели аналог - длительность импульса, второй элемент ИЛИ, четвертый глемент И и элемент НЕ, причем второй преобразователь аналог - длительность импульса соединен информа ционным входом с вторым входом устройства, выходом - с первым входом второго элемента ИЛИ, а управляю

Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано для контроля как установившихся, таки переходных процессов в различных технологических объектах, например энергобло1 ов электростанций.

Извеётйо устройство дпя допускового контроля параметров объекта, содержащее последовательно соединенные управляемый многоканальный масштабный преобразователь, аналоговые сумматоры, прямые преобразователи аналог - код, блок вывода измеряемой информации, а также общий для всех каналов блок обратного преобразователя код - аналог и вычислительный блок С1 J.

Недостатками такого устройства для допускового контроля являются его сложность, обусловленная наличие м большого числа преобразователей аналог - код и аналоговых сумматоров, и низкая точность контроля параметров объекта, вызванная использованием аналогового сумматора.

Известно также устройство для доцускового контроля параметров объекта, содержащее N преобразователей аналог - длительность импульсов, где N - количество входных каналов устройства, блок синхронизации, блок уставок, N блоков сравнения, N блоков индикации блок регистрации, два регистра,сдвига, последовательный сумматор, N+1 распределителей импульсов, два триггера, элемент задержки, три элемента ИЛИ и три элемента иС2)

Недостатками атого устройства для допускового контроля являются его относительная сложность и низкая достоверность контроля переходных процессов.

Наиболее близким техническим решением к изобретению является устройство для допускового контроля параметров объекта, содержащее преС) образователь аналог - длительность импульса, блок синхронизации, блок уставок, блок сравнения, блок индикации, блок регистрации, регистр сдвига, последовательный сумматор, распределитель импульсов,, два триггвра элемент задержки, элемент ИЛИ и три элемента И E3J.

Недостатком устройства.является 1шзкая достоверность контроля переходных процессов объекта.

Цель изобретения - Повышение достоверности контроля переходного npoltecca объекта.

Поставленная цель достигается тем, что в устройство дпя допускового контроля параметров объекта, содержащее первый преобразователь ана лог - длительность импульса, информационш 1Й вход которого соединен с

5 первым входом устройства, выход через блок сравнения - с блоком индикации, а управлякяций вход - с первым импульсным выходом распределите,ля импульсов, подключенного входом

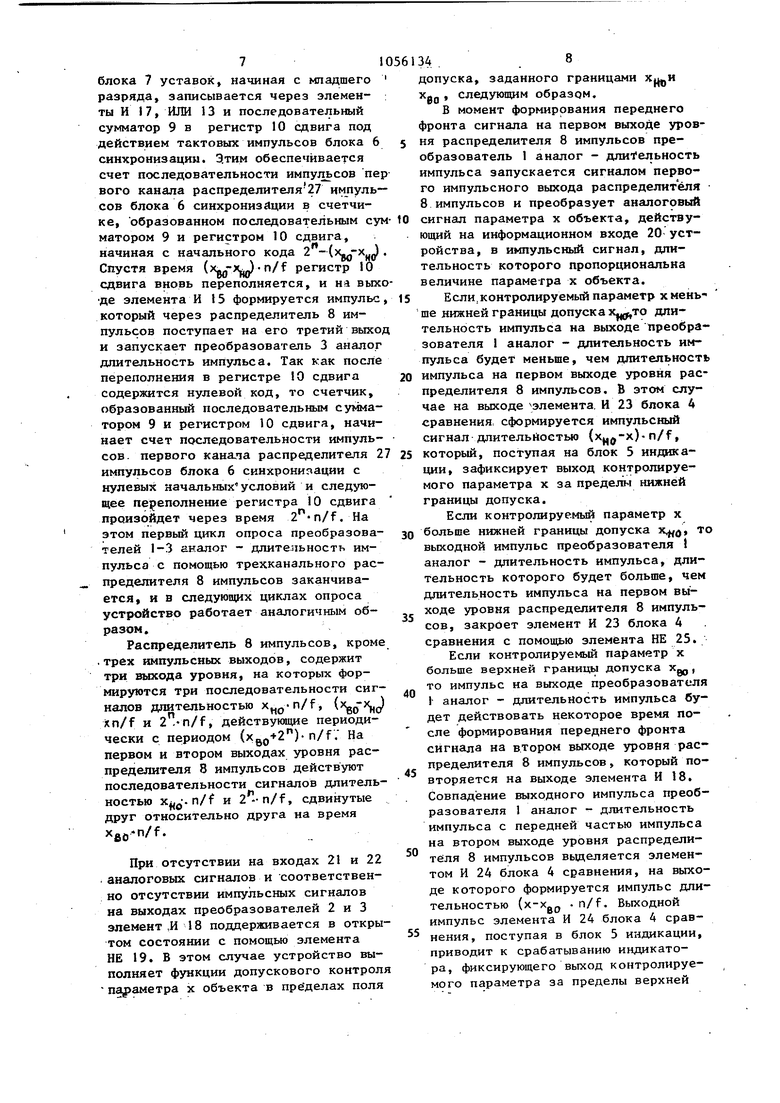

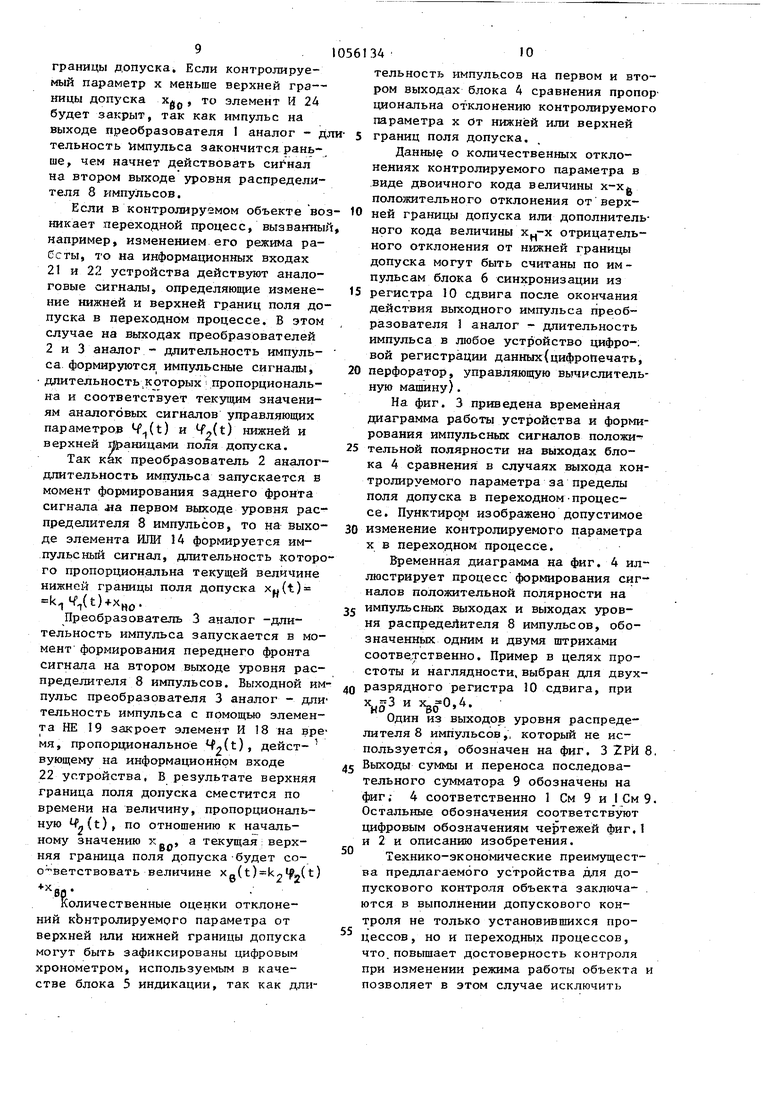

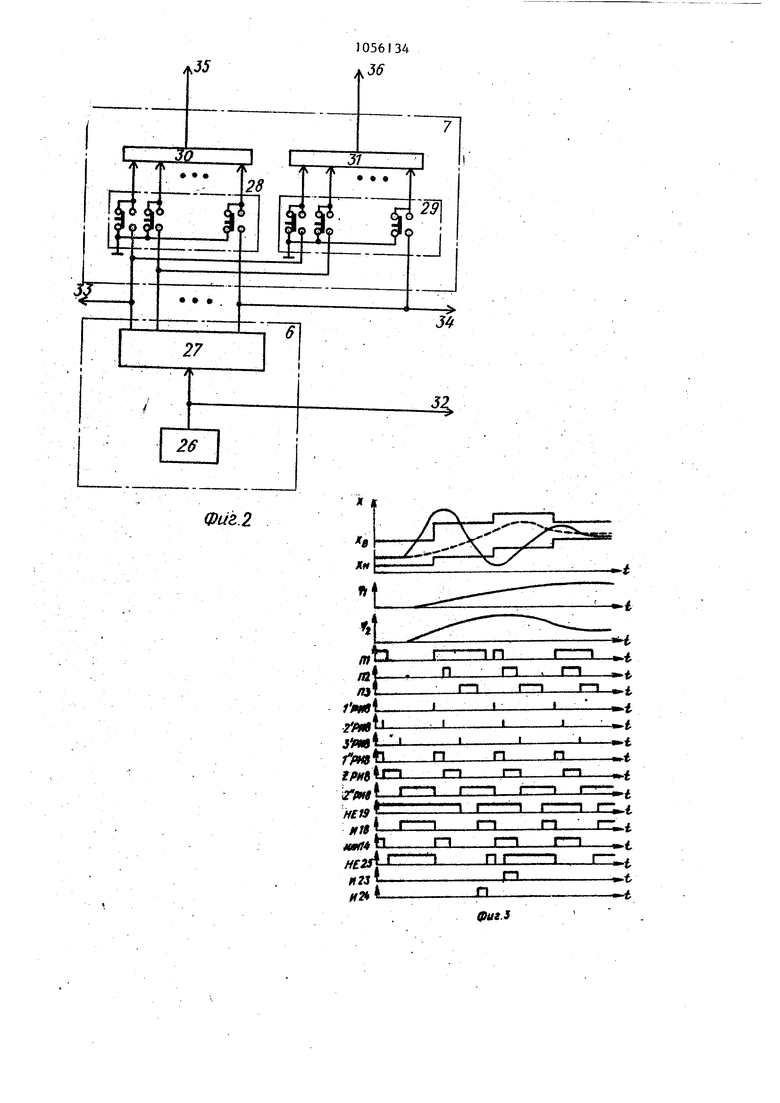

0 через первый элемент И к выходу переноса последовательного сумматора, выход суммы которого подсоединен к информационному входу регистра сдвига, а первый вход - к выходу первоC го элемента ШШ, соединенного пер: вым входом с выходом регистра сдвига, вторым и третьим входами - с выходами в торого и третьего элементов И соответственно, блок синхронизахщи, группа выходов которого соединена через блок уставок с первыми входами второго и третьего элементов И, вторые входы которых подключены к выходам первого и второ3го триггеров соответственно, управляющий выход блока синхронизации со динен с управляющим входом регистра сдвига, второй вход последовательного сумматора подключен к первому .выходу группы выходов блока синхро низации, последний выход из которых соединен с вторым входом первого элемента И и с нулевыми входами , первого и второго триггеров, -единич ные входы которых подключены к первому и второму импульсным выходам распределителя импульсов соответственно, введены второй и третий преобразователи аналог - длительность, импульса, второй элемент ИЛИ, четве тый элемент И и элемент НЕ, причем второй преобразователь аналог - дли тельность импульса соединен информа ционным входом с вторым входом устройства, вьпсодом - с первым входом второго элемента ИЛИ, а управляющий входом - с вторым импульсным вы ходом распределителя импульсов, тре тий преобразователь аналог - длител . ность импульса соединен информацион ным входом с третьим входом устройства,, выходом - через элемент НЕ с первым входом четвертого элемента И а управляющим аходом - с третьим им пульсным выходом распределителя импульсов, два выхода уровня которого соединены соответственно через второй элемент ИЛИ и четвертый элемент И с входами блока сравнения. На фаг изображена функционалЬ ная схема устройства; на фиг. 2 , функциональная схема блока синхронизации и блока.уставок; на фиг.Звременная диаграмма работы устройства; на фиг. 4 - временная диаграм ма работы отдельных блоков устройства. Устройство содержит преобразователи 1-3 аналог - длительность импульса, блок 4 сравнения, блок 5 ин дикации, блок 6 синхронизации, блок 7 уставок, распределитель 8 импульсов, последовательный сумматор 9, регистр 10 сдвига, триггеры 11 и 12 элементы ИЛИ 13, и 14, элементы И 15-18, элемент НЕ 19 и информационнные входы 20-22 устройства. Блок 4 сравнения содержит элементы И 23 и 24 и элемент НЕ 25. Блок 6 синхронизации (фиг. 2) содержит генератор 26 тактовых импульсов и распределитель 27 импуль сов. Блок 7 уставок содержит комму44таторы 28 и 29 и элементы ИЛИ 30 и 31 . Выход 32 генератора 26 тактовых импульсов соединен с управляющим входом регистра 10 сдвига. Первый 33 и последний 34 выходы распределителя 27 импульсов соединены соответственно с вторым входом последовательного сумматора 9 и с вторым входом элемента И 15. Выходы 35 и 36 элементов ИЛИ 30 и 31 соединены с первыми входами элементов И 16 и 17 соответственно. Примеры реализации преобразователей 1-3 аналог - длительность импульса содержатся в 4. Блок 5 индикации может быть реализован по любой схеме динамической индикации С5 J. Блок 6 синхронизации, содержащий генератор 26 тактовых импульсов и распределитель импульсов, может быть реализован. например, на микросхеме К 536 ГГ Гб J. Примеры реализации распределителя 8 импульсов, последовательного сумматора 9 и регистра 10 сдвига содержатся, например, в С 7 }. Коммутаторы 28 и 29 могут быть реализованы в виде клавишных переключателей на М направлений, где п количество разрядов регистра 10 сдвигов , либо в виде блока п параллельных ключей, yпpaвляe ыx по сигналам от цифровой вычислительной машины централизованного управления. Устройство для допускового контроля параметров объекта выполняет функции допускового контроля как установившихся значений параметра объекта, так и переходных процессов, когда параметры; о. гя изменяются от одного до другого установившегося значения. Это обеспечивается функциональным изменением в переходном процессе верхней и нижней границ поля допуска Б зависимости от двух других параметров объекта или про- граммных сигналов, формируемых, например, функциональными генераторами. Верхняя и нижняя границы поля допуска изменяются во времени согласно соотношениям Xn(t)k.,if.,(t)4X x,,(t) (t)-ex 5 , где,Ч(1) и ) - нижний и верхни управляющие параметры соответ венно; начальные значе XHO eo ния нижней и верхней границ поля допуска со ответственно; k и k2 - постоянные коэф фициенты. В переходном процессе параметры 41,(t) и (t) объекта изменяют гра ницы поля допуска для контролируемого параметра объекта X. Устройство работает следующим об разом. Начальные значения поля допуска задаются блоком 7 уставок, на ко мутаторах 28 и 29 которого набирают cooTBCTCTBeHHOjдополнительный двоичный код начальной нижней границы поля допуска 2 -х,где И количество разрядов регистра 10 сдвига, и дополнительный двоичный код начального поля допуска 2 /-(xg-r -Xj . В единичных разрядах дополнительных кодов коммутаторы 28 и 29 подключают соответствующий выход ,п-канального распределителя 27 импульсов блока 6 синхронизации к соответствующему входу элементов ИЛИ 30 и 31,В.нулевых разрядах набираемых дополнительных кодов на соответствующих выходах коммутаторов 28 и 29 присутствует сигнал логического нуля. Йосле запуска устройства на п-вы ходах распределителя 27 импульсов формируется п последовательность импульсов частоты f/n, где f - тактовая частота генератора 26, сдвину тых друг относительно друга на время 1/f. Из последовательностей имПульоов распределителя 27 импульсов блока 6- синхронизации на выходах элементов ШШ 30 и 31 блока 7 уставок формируются две последовательности импульсов, периодически повто ряющие последовательные двоичные коды 2 -х„дИ (Хдо-х„). Последовательность -импульсов на аьрсоде первого канала распределител 27 импульсов блока 6 синхронизации, поступает на вход последовательного сумматора 9, который совместно с регистром 10 сдвига образует счет чик импульсов. Первый импульс перво го канала распределителя 27 импуль 4сов записывается через последователь ный сумматор 9 в регистр 10 сдвига под действием тактовых импульсов ге нератора 2Б тактовых импульсов блока 6 синхронизации. При,поступлении второго импульса из первого канала распределителя 27 импульсов состояние регистра 10 сдвига увеличивается на единицу и т.д. до тех пор, пока на выходе переноса последовательного сумматора 9 не сформируется сигнал переполнения регистра 10 сдвига, который совпадает с импульсом послед него п-го канала распределителя 27 импульсов блока 6 синхронизации на входах элемента И 15. Импульс с выхода элемента И 15 поступает через распределитель 8 импульсов на его первый импульсный выход, запускает преобразователь 1 аналог - длительность импульса и устанавливает триггер 11 в единичное состояние. Триггер 11 в единичном состоянии находится п тактов и подключает с помощью элемента И 16 первый выход блока 7 уставок через элемент ИЛИ 13 к первому входу последовательного сумматора 9.. Последовательный двоичшлй код , действунщий на первом выходе блока 7 уставок, начиная с младшего разряда, записывается через элементы И 16, ИЛИ 13 и последовательный сумматор 9в регистр 10 сдвига под действием тактовых импульсов блока 6 синхрони задии. Следовательно, после переполнения регистра 10 сдвига счетчик, образованный последовательным сумматором 9 и регистром 10 сдвига, начинает счет последовательности импульсов первого канала распределителя 27 импульсов блока 6 синхронизации, начиная с начального кода . Спустя время регистр 10сдвига вновь переполняется и, на выходе элемента И 15 формируется импульс,- который поступает через распределитель 8 импульсов на его второй импульсный выход, запускает преобразователь 2 аналог - длительность импульсов и устанавливает триггер I2 в оданочное состояние на время п тактов. Триггер 12 в одиночном состоянии подключает с помощью элемента И 17 второй выход блока 7 уставок через элемент ШШ 13 к первому входу .последовательного сумматора 9. Последовательный двоичньпй код 2 -(x jXHO действуЕр й на втором выходе 7 блока 7 уставок, начиная с младшего разряда, записывается через элементы И 17, ИЛИ 13 и последовательный сумматор 9 в регистр 10 сдвига под действием тактовых импульсов блока 6 синхронизации. Э.тим обеспечивается счет последовательности импульсов пе вого канала распределителя27 имJlyль сов блока 6 синхронизации в счетчике, образованном последовательным су матором 9 и регистром 10 сдвига, начиная с начального кода 2-( Спустя время ( регистр 10 сдвига вновь переполняется, и на вых де элемента И 15 формируется импульс который через распределитель 8 импульсов поступает иа его третий выхо и запускает преобразователь 3 аналог длительность импульса. Так как после переполнения в регистре 10 сдвига содержится нулевой код, то счетчик, образованный последовательным сумматором 9 и регистром 10 сдвига, начинает счет последовательности импульсов, первого канала распределителя 2 импульсов блока 6 синхронизации с нулевых начальных условий и следующее переполнение регистра 10 сдвига произойдет через время . На этом первый цикл опроса преобразовагелей 1-3 аналог - длительность импульса с помощью трехканального распределителя 8 импульсов заканчивается, и в следующих циклах опроса устройство работает аналогичным образом. Распределитель 8 импульсов, кроме .трех импульсных выходов, содержит три выхода уровня, на которых формируются три последовательности сигналов длительностью , ( Xn/f и 2 .-n/f, действунлцие периодически с периодом (xgQ+2)n/f. На первом и втором выходах уровня распределителя 8 импульсов действуют последовательности сигналов длительностью . n/f и , сдвинутые друг относительно друга на время При отсутствии на входах 21 и 22 аналоговых сигналов и соответственно отсутствии импульсных сигналов иа выходах преобразователей 2 и 3 элемент,И 18 поддерживается в открытом состоянии с помощью элемента НЕ 19. В этом случае устройство выполняет функции допускового контроля па аметра х объекта в пределах поля допуска, заданного границами Xgg, следующим образом. В момент формирования переднего фронта сигнала на первом выходе уровня распределителя 8 импульсов преобразователь 1 аналог - длительность импульса запускается сигналом первого импульсного выхода распределителя 8 импульсов и преобразует аналоговый сигнал параметра х объекта, действующий на информационном входе 20 устройства, в импульсный сигнал, длительность которого пропорциональна величине параметра х объекта. Если,контролируемый параметр х меньше нижней границы допуск а длительность импульса на выходе преобразователя I аналог - длительность импульса будет меньше, чем длительность импульса на первом выходе уровня распределителя 8 импульсов. В этом случае на выходе - элемента, И 23 блока 4 сравнения, сформируется импульсный сигнал длительностью ()-n/f, который, поступая на блок 5 индикации, зафиксирует выход контролируемого параметра х за пределы нижней границы допуска. Если контролируемый параметр х больше нижней границы допуска то выходной импульс преобразователя аналог - длительность импульса, длительность которого будет больше, чем длительность импульса на первом выходе уровня распределителя 8 импульсов, закроет элемент И 23 блока 4 сравнения с помоиуью элемента НЕ 25. Если контролируемый параметр х больше верхней границь допуска , то импульс на выходе преобразователя 1 аналог - длительность импульса будет действовать некоторое время после формирования переднего фронта сигнала на втором выходе уровня распределителя 8 импульсов, который повторяется на выходе элемента И 18. Совпадение выходного импульса преобразователя 1 аналог - длительность импульса с передней частью импульса на втором выходе уровня распределителя 8 импульсов выделяется элементом И 24 блока 4 сравнения, на выходе которого формируется импульс длительностью (х-Хцр . n/f. Выходной импульс элемента И 24 блока 4 сравнения, поступая в блок 5 индикации, приводит к срабатыванию индикатора, фиксирующего выход контролируемого параметра за пределы верхней 9 границы допуска. Если контролируемый параметр х меньше верхней гра- ницы допуска ХА. , то элемент И 24 будет закрыт, так как импульс на выходе преобразователя 1 аналог - Д тельность 1мпульса закончится раньше, чем начнет действовать сигнал на втором выходеуровня распределителя 8 импульсов. Если в контролируемом объекте во никает переходной процесс, вызванны например, изменением его режима раСсты, то на информационных входах 21и 22 устройства действуют аналоговые сигналы, определяющие изменение нижней и верхней границ поля до пуска в переходном процессе. В этом случае на выходах преобразователей 2 и 3 аналог - длительность импульса формирзпотся импульсные сигналы, длительность .которых пропорциональна и соответствует текзщим значениям аналоговых сигналов управляющих параметров 4(t) и «(t) нижней и верхней фаницами поля допуска. Так как преобразователь 2 аналог длительность импульса запускается в момент формирования заднего фронта сигнала зла первом выходе уровня рас пределителя 8 импульсов, то на выхо де элемента ИЛИ 14 формируется импульсный сигнал, длительность котор го пропорциональна текущей величине нижней границы поля допуска x(t) 4%(t)XHOПреобразователь 3 аналог -длительность импульса запускается в мо мент формирования переднего фронта сигнала на втором выходе уровня распределителя 8 импульсов. Выходной им пульс преобразователя 3 аналог - дли тельность импульса с помощью элемен та НЕ 19 закроет элемент И 18 на вр мя, пропорциональное ), деиствующему на информационном входе 22устройства, В результате верхняя граница поля допуска сместится по времени на величину, пропорциональную Ч, (t), по отношению к начальа текущая;верхному значению х няя граница поля допуска-будет соо ветствовать величине x(t)k2f2( Количественные оценки отклонений кЬнтролируемрго параметра от верхней или нижней границы допуска могут быть зафиксированы цифровым хронометром, используемым в качестве блока 5 индикации, так как длительность импульсов на первом и втором выходах блока 4 сравнения пропорциональна отклонению контролируемого параметра х От нижней или верхней границ поля допуска. Данные о количественных отклонениях контролируемого параметра в .виде двоичного кода величины х-х поло7кительного отклонения от верхней границы допуска или дополнительного кода величины отрицательного отклонения от нижней границы допуска могут быть считаны по импульсам блока 6 синхронизации из регистра 10 сдвига после окончания действия выходного импульса преобразователя 1 аналог - длительность импульса в любое устройство цифро-; вой регистрации данных(цифропечать, перфоратор, управляющую вычислительную машину). На фиг. 3 приведена временная диаграмма работы устройства и формирования импульсных сигналов положительной полярности на выходах блока 4 сравнения в случаях выхода контролируемого параметра за пределы поля допуска в переходном-процессе. Пунктиром изображено допустимое изменение контролируемого параметра X в переходном процессе. Временная диаграмма на фиг. 4 иллюстрирует процесс формирования сигналов положительной полярности на импульсных выходах и выходах зфовня распределителя 8 импульсов, обозначенньк одним и двумя штрихами соотве..тственно. Пример в целях простоты и наглядности, выбран для двухразрядного регистра 10 сдвига, при V « Один из выходов уровня распределителя 8 импульсов,, который не используется, обозначен на фиг. 3 ZPH 8, Выходы суммы и переноса последовательного сумматора 9 обозначены на фиг; 4 соответственно 1 См 9 и I См 9. Остальные обозначения соответствуют цифровым обозначениям чертежей фиг. и 2 и описанию изобретения. Технико-экономические преимущества предлагаемого устройства д.пя допускового контроля объекта заключаются в выполнении допускового контроля не только установившихся процессов , но и переходных процессов, что. повышает достоверность контроля при изменении режима работы объекта и позволяет в этом случае исключить П1 ложную индикацию выхода параметра за допустимые пределы. Повьппение достоверности контроля переходных процессов в свою очередь позволяет оператору, например, энергоблока АЭС своевременно выявить тенденцию изменения его состояния и своевременно предпринять действия, направленные на устранение .неблагоприятного изменения состояния контролируемого объ акта. Бели в качестве базового устройства выбрать прибор Щ1531 на. микропроцессоре, программа которого преду .сматривает выполнение функций допуснового контроля, то предлагаемое устройство повышает достоверность ко троля как за счет снижения времени цикла опроса, так и за счет возмож412ности учета переходных процессов. Действительно время одного цикла измерения в предлагаемом устройстве значительно меньше, чем в базовом, а , функции базового устройства ограничены, поскольку ОНО позвол1 ет контролировать параметр объекта тольХо при постоянно заданных уставках поля допуска. Максимальное время одного цикла контроля в предлагаемом устройстве составляет , где f - тактовая частота, П - разрядность регистра 10 сдвига. Например, при «3 МГц и время одного цикла контроля в предлагаемом устройстве составляет Ш мс, в то время как прибор Ц1531 имеет время измерения 200 мс 8.

фиг.2

J«fiв27-П-J л JlJ JГlл JlJ

3j/%7--Л-JT-JT-JT-Jl-Jl-Jl

яy/ л --Л-JlJIЛlJlJгJгJl лJ J -Ллпягцшллппплшшлллшии

гг//-Г Т-..

///tf-Л П- :/г/2T-L гп

И17 -ПЛ.ПЛи.

реюПЛП-- Г1 ЛЛЛПЛП TL-ПЛЛ

НЛИ13 -ЛГ1лллл т л1ита ллллл гша

1С„9 -ЛЯП. ПППП ППП

2смз - пялл „ П ППП

и 15 TLJTrU-FLJlП/ //5J П1L-г

I-IL

..

2PH6- -- -SPf S-П -П-

Фиг.

Авторы

Даты

1983-11-23—Публикация

1982-08-25—Подача