(54) ГЕНЕРАТОР ЦИКЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор циклов | 1979 |

|

SU877511A1 |

| Счетчик для вычитания | 1984 |

|

SU1228276A1 |

| Генератор циклов | 1981 |

|

SU995289A1 |

| Генератор циклов | 1978 |

|

SU744531A1 |

| Устройство для контроля экспоненциальных процессов | 1984 |

|

SU1282087A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Устройство для допускового контроля объекта | 1984 |

|

SU1246060A1 |

| Преобразователь двоичного кода в двоично-десятичный масштабированный код | 1978 |

|

SU767750A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

1

Изобретение относится к автоматике и вычиспитепьной технике и предназначе но Для генерирования импульсных сигналов с заданными периодами следования.

Известен генератор циклов, содержащий динамический регистр, соединенный с сумматором, кварцевый генератор, соединенный с блоком синхронизации, блок ввода начальных условий и триггер, подкшоченнь1й через элемент И и сумматор к динамическому регистру 1.

Недостатком этого генератора циклов является сложность его перестройки на . заданный период следования, что яъпяется следствием двоичной обработки сумматором содержимого регистра.

Наиболее близким к данному изобретению техническим решением является генератор циклов, содержащий генератор эталонной частоты, блок синхронизации, блок перестройки, сумматор, регистр сдвига, четыре элемента И, два элемента ИЛИ, два элемента задержки и триггер 2.

Недостатком известного генератора циклов является относительная сложность перестройки, что снижает его эксплуатационные характеристики;

Цепью изобретения является улучшение эксплуатационных характеристик генератора циклов.

Указанная цепь достигается тем, что в генератор циклов, содержащий генератор эталонной частоты, блок синхронизации,

10 состоящий из п -разрядного распределителя импульсов (п-4т- число разрядов в двоично-десятичном коДе длительности цикла, m -число тетрад), и m -входового элемента ИЛИ, блок перестройки, состояtsщий из коммутатора и п -входового элемента ИЛИ, (п -2)-разрядный регистр сдвига, четыре элемента И, два элемента ИЛИ, два элемента задержки и первый триггер, причем выход генератора

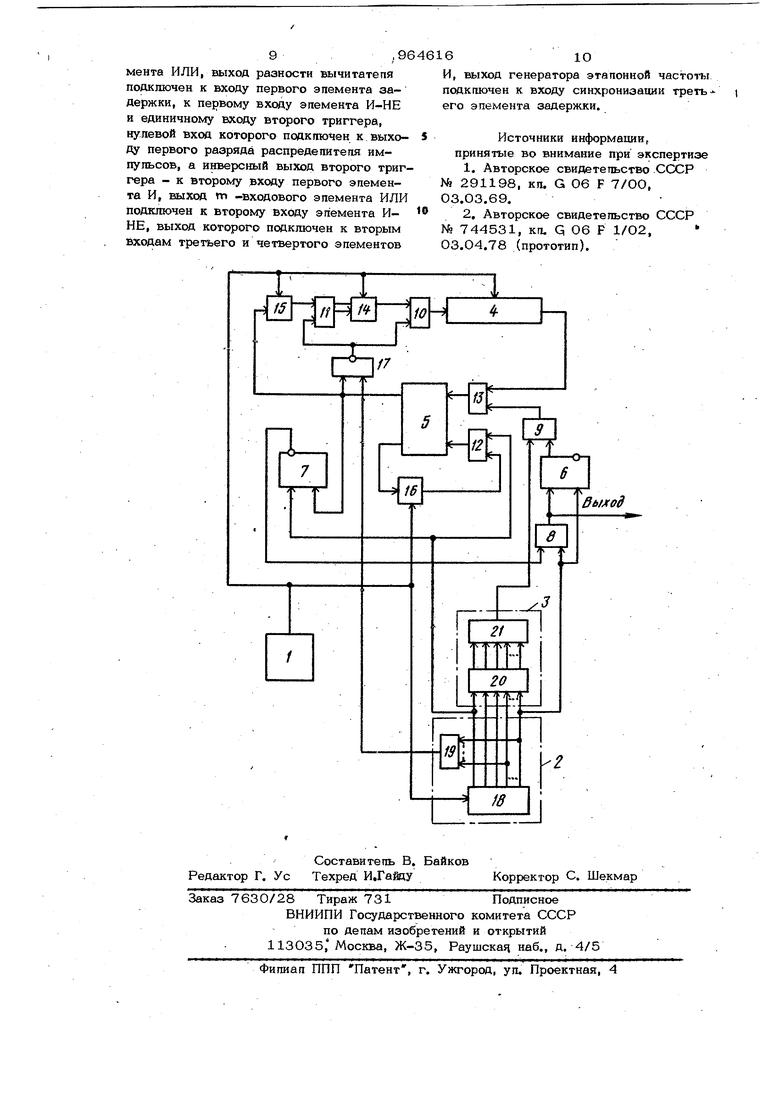

20 эталонной частоты подключен к переключающему входу распредепителя импульсов, к входу синхронизации (п -2)-разрядного регистра сдвига и ко входам синхронизаIjTu пгфкого и второго эпе ентоБ задержки, выход первого разряда распредепите;ш импульсов подключен к первому входу первого эпемента ИЛИ, выход п -го разряда распредепитепя импупьсов подкшючен к нулевому входу первого триггера и к nepBONiy входу первого эпемента И, выход которого, являющийся выходом генератора циклов, подключен к единичному входу первого . триггера, выходы разрядов с померг ми 1 (i -t-rfri) распределителя импупьсов подключены ко входам твходового элемента ИЛИ, выходы разрядов с первого по- п -ft распределитель кмпупьсов подключены к входам коммутатора, выходы которого через п-входовой элемент ИЛИ подключен к первому входу второго эпемента И, второй вход которого подключен к выходу первого триггера, а выход второго элемента И - к первому входу второго эпемента ИЛИ, выход nej вого элемента задержки подключен к первому входу третьего элемента И, выход которого через второй элемент задержки подключен к первому входу четвертого элемента И, выход последнего подключен к входу (п-2)-разрядного регистра сдвига, а выход (ti-2)-разрядного регистра сдвига подключен к второму входу второго элемента ИЛИ, содержит вычитатель, второй триггер, третий элемент задержки и элемент И-НЕ, причем выход первого эпемента ИЛИ - подключен к входу вычитаемого, а выход второга элемента ИЛИ ко входу уменьшаемого вычитателя, выход займа в старшие разряды вычитате- пя через третий элемент задержки подключен к второму входу первого эпемента ИЛИ, выход разности вычитатепя подключен к входу первого элемента задержки, к первому входу эпемента И-НЕ и единичному входу второго триггера, нулевой вход которого подключен к выходу первого разряда распределитепя импупьсов, а. инверсный выход второго триггера - к второму входу первого эпемента И, выход тп -входового эпемента ИЛИ подключен к второму входу элемента И-НЕ, выход которого подключен к вторым входам третьего и четвертого элементов И, выход генератора эталонной частоты подключен к входу синхронизации третьего элемента задержки. На чертеже представлена функциональная схема генератора циклов. Устройство содержит генератор 1 эталонной частоты, блок 2 синхронизации, блок 3 перестройки, (п -2)-разрядньтй регистр сдвига 4, вычитатель 5, триггеры 6 И 7, элементы И 8-11, ИЛИ 12 и 13, элементы задержки 14-16, элемент И-НЕ 17, распределитель 18 импупьсов, (тг -входовой ИЛИ 19, коммутатор 20, п -вхоДовой элемент ИЛИ 21. Генератор циклов работает следующим образом. Генератор 1 эталонной частоты вырабатывает импульсные сигналы с частотой f , которые поступают на вход распределителя 18 импульсов блока 2 синхронизации. На п выходах распределителя 18 импульсов формируются п последовательностей импульсов, сдвинутые друг относительно друга на один период эталонной частоты -f. Регистр 4 сдвига- содержит (ri-2) двоичных разрядов. Эпементы 14 и 15. задержки на один период этапонной частоты Дополняют регистр 4 сдвига до п двоичных разрядов, где n 4m , количество тетрад полного, п - разрядного регистра. На выходе элемента ИЛИ из выходных поспедовательностей распределителя 18 импульсов формируется последовательность импугоьсов частоты f 4, которая синхронизирует каждый четвертый разряд тетрад полного п -разрядного регистра. Каждый выход с первого по п -и рас предепителя 18 импупьсов блока 2 синхронизации синхронизирует считывание с выхода регистра 4 сдвига соответствующего разряда двоично-десятичного кода. Коммутатор 20 блока 3 перестройки состоит, например, из m перекшочателей, каждый из которых имеет десять положений от О до 9 к содержит четыре выхода, либо из 4т управляемых ключей. На п 4 m выходах коммутатора 20 формируется двоично-десятичный код 8-42-1, который эпементомИЛИ 21 преобразуется в последовательный 4т -разрядный двоично-десятичный код заданного периода следования выходных сигналов генератора циклов. В исходном.состоянии триггеры 6 и 7, выполняющие функцию S -триггеров, обнулены, что обеспечивается подачей импульсов с соответствующих выходов распределителя 18 импупьсов блока 2 синхронизации. Во,время формирования им пульса на последнем п -м выходе распределителя 18 импульсов элемент И 8 от крывается и триггер 6 устанавливается в единичное состояние. В это время выходной импульс эпемента И 8 проходит на

596

выходную шину генератора цикпов. Сигнап с прямого выхода триггера 6 открывает элемент И 9, через который проходит, начиная с мпадших разрядов, п.оспедоватепьный двоично-десятичный, код 8-4-2-1 блока 3 перестройки. Во время поступления через элемент ИЛИ 13 мпадшего разряда двоично-десятичного кода перестройки на второй вход двоичного вычитате-ля 5, на его первый вход через элемент ИЛИ 12 поступает синхронизирующий им- пупьс с первого выхода распредели те он 18 импульсов. Двоичный одноразрядный вычитатепь 5 выполняет последовательно во времени вычитание из двоично-десятичного кода перестройки одного импульса младшего разряда с первого выхода распределителя 18 импульсов. На первом выЬсоде двоичного вычитателя 5 формируются сигналы двоично-десятичного кода разности, а на втором выходе - сигналы займа в старшие разряды, которые через элемент задержки 16 на период эталонной частоты и элемент ИЛИ 12 поступают на первый вход двоичного вычита теля 5.

Если в младшей тетраде двоично-десятичного кода перестройки содержится хоть одна единица, то двоичное вычитание дает правильный результат, который с первого выхода двоичного вычитателя 5 через элементь 14 и 15 задержки на один период эталонной частоты и элементы И 10 и 1.1 записывается в регистр 4 сдвига.

Если в младшей тетраде двоично-десятичного кода перестройки содержатся нули ОООО, то двоичное вычитание дает код разности 1111 и сигнал займа во вторую тетрару, В этом случае, во время действия на первом выходе двоичного вычитателя 5 единичного сигнала четвертого разряда на вькоде элемента ИЛИ 19 блока 2 синхронизации действует импульсный сигнал, который сформирует на выхоДе элемента И-НЕ 17 нулевой сигнал, закрывающий элементы И 1О и 11 во время передачи сигнала второго разряда младшей тетрады с выхода элемента 14 задержки на вход регистра 4 сдвига и сигнала третьего разряда младшей тетрады с выхода элемента 15 задержки на вход элемента 14 задержки соответственно. В результате в регистр 4 сдвига в младшей тетраде запишется код 1001 (девять), а сигнал займа со второго выхода двоичного вычитателя 5 поступит на его второй вход через элемент 16 задержки и элемент ИЛИ 12.

166

Вычисления во второй тетраде осуществляются аналогично вычислениям в младшей тетраде.

Таким образом, за один цикл циркуляции кода перестройки в полном кольцевом регистре, образованном последовательным соединением выхода регистра 4 сдвига с его входом через элемент ИЛИ 13, двоичный вычитатель 5, элементы 1-4 и 15 задержки, элементы И 10 и 11, начальный двоично-десятичный код заданного периода следования выходных импульсов генератора циклов уменьшится на единицу.

До тех пор, пока в результате вычисления на первом выходе двоичного вы- читателя 5 формируется хотя бы один единичньгй сигнал в любом разряде любой тетрады, триггер 7 блокирует элемент И 8 сигналом с инверсного выхода, так как единичный сигнал первого выхода двоичного вычитателя 5 устанавл1тает триггер 7 в единичное состояние к моменту действия на последнем выходе распределителя 18 импульса синхронизации, поступающего на первый вход элемента И 8. В результате блокировки элемента И 8 на выходной шине генератора циклов импульсы отсутствуют, а i триггер 6 устанавливается в нулевое состояние импульсом последнего выхода распределителя 18.

Спустя время

Т.., ,

где Т-, - заданный период следования выходных сигналов генератора циклов;

Кр- десятичное число, задаваемое коммутатором 20 блока перестройки;

- эталонная частота генератора 1 двоично-десятичный код перестройки обнулится, на первом выходе двоичного вычитателя 5 в течение времени n/f будет отсутствовать единичный сигнал и триггер 7, который Устанавливается в нулево состояние сигналом первого выхода распределителя 18, останется в нулевом состоянии к Моменту формирования импульсного сигнала на последнем п -м выходе распределителя 18 импульсов. В этом случае срабатывает элемент И 8, на выход которого проходит импульсный сигнал последнего выхода распределителя 18 импульсов.

Выходной сигнал элемента И- 8 проходит на выходную шину генератора циклов и вновь устанавливает триггер 6 в единичное состояние. Цикл работы устройства повторяется аналогичным образом. . Технико-экономические преимущества заявляемого генератора цикпов закшочаю ся в упрощении перестройки устройства на заданный период следования выходных сйгнапов. В известном генераторе циклов процесс перестройки закшочается в вь1чисг1ении десятичного кода перестройки , где Tj - заданный период; - этапонная частота; m - количество десятичных разрядов кода перестройки. Вычисление десятичного кода перестро ки требует Дополнительного арифметического бпока, В предлагаемом генераторе циклов де сятичный код перестройки соответствует заданному периоду следования выходных сигналов генератора циклов, что позвбляет непосредственно осуществлять процесс перестройки. Действительно, Т,, ,, где - эталонная частота; Tj - заданный период; К - Десятичный код перестройки; m - количество Десятичных разрядов кода перестройки, Если выбрать эталонную частоту из условия f 4mioru, , где Р - целое число, то получим прямое соответствие между десятичным. кодом перестройки и заданным периодом . .оР с, где р - определяет вес единицы десятич ного кода перестройки. Максимальный заданный период, , так как Ю Например, при р 5 и m 10 десятиразрядный десятичный код перестройки, старшие пять разрядов которого задают период следования выходных сигналов генератора циклов в диапазоне 10 с /Тз / 1 ,. а младшие пять разрядов десятичного кода перестройки задают период следования в диапазоне It . . Таким образом, с помощью коммутатора 20 тока 3 перестройки непосредственно задается период следования выходных сигналов генератора циклов в диа пазоне lOc -xTj / lOc, что Дает для рассматриваемого примера диапазон Юс 7, Т 5/ 10%. Формула изобретения Генератор циклов, содержащий генератор эталонной частоты, блок синхронизации, состоящий из п -разрядного распределителя импульсов (п :4т- число разрядов в двоично-Десятичном коде длительности цикла, m -число тетрад), и гп-входового элемента ИЛИ, блок пере- . стройки, состоящий из коммутатора и п входового элементаИЛИ, (п -2)-разрядный регистр сдвига, четыре элемента И, два элемента ИЛИ, два элемента задержки и первый триггер, причем выход генератора эталонной частоты подключен к переключающему входу распределителя импульсов, к входу синхронизации (п -2)разрядного регистра сдвига и к входам синхронизации первого и второго элементов задержки, выход первого разряда, распределителя импульсов подключен к первому входу первого элемента ИЛИ, выход п -го разряда распредепитепя импупьсов подключен к нулевому входу первого триггера и к перЬому входу первого элемента И, выход которого, являющийся выходом генератора циклов, подключен к единичному входу первого триггера, выходы разрядов с номерами 4 i ( i 1т m) распределителя импульсов подключены к входам ГТ1 - входового элемента ИЛ И, выходы . разрядов с первого по п -и распредели- , те ль импульсов подключены к входам коммутатора, выходы которого через tl-входовой элемент ИЛИ подключены к первому входу второго элемента И, второй вход которого подключен к выходу первого триггера, а выход второго элемента И - к первому входу второго элемента ИЛИ, выход первого элемента задержки подключен к первому входу третьего элемента И, выход которого через второй элемент задержки подключен к первому входу четвертого элемента И, выход последнего подключен к входу (п -2)-разрядного регистра сдвига, а выход (п -2)разрядного регистра сдвига - к второму входу второго элемента ИЛИ, отличающийся тем, что, с целью улучшения эксплуатационных характеристик генератора циклов, он содержит вычитатель второй триггер, третий элемент задержки и элемент И-НЕ, причем выход первого элемента ИЛИ подключен к входу вычитаемого, а выход второго элемента ИЛИ - к входу уменьшаемого вычитателя, выход займа в старшие разряды вычи тате ля через третий элемент задержки подключен к второму входу первого элемента ИЛИ, выход разности вычитатепя подключен к входу первого элемента задержки, к первому входу элемента И-НЕ и единичному входу второго триггера, нулевой вход которого подкгпочен к выходу первого разряда распределитепя импульсов, а инверсный выход второго триггера - к второму входу первого эпемента И, выход m -входового элемента ИЛИ подключен к второму входу элемента ИНЕ, выход которого подключен к вторым Ёходам третьего и четвертого элементов

И, выход генератора эталонной частоты подкпючен к входу синхронизации треть его эпемента задержки.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-10-07—Публикация

1981-03-18—Подача