1 1

Изобретение относится к области цифровой вычислительной техники.

Цель изобретения - сокращение оборудования .

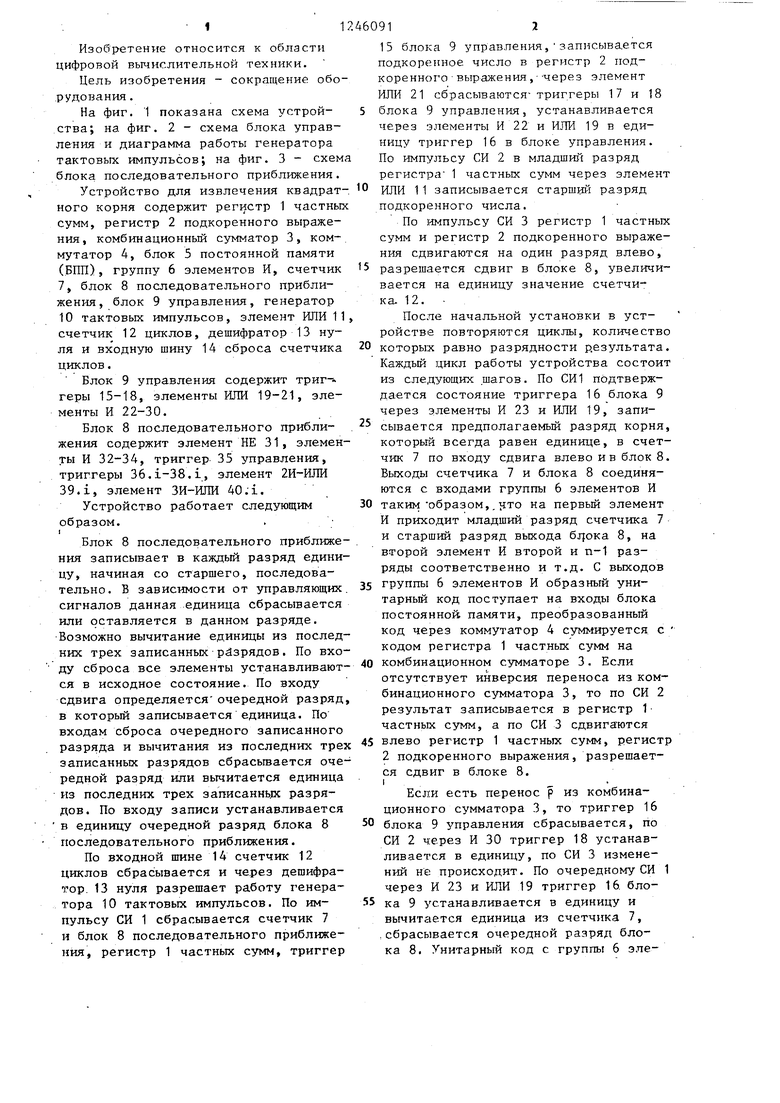

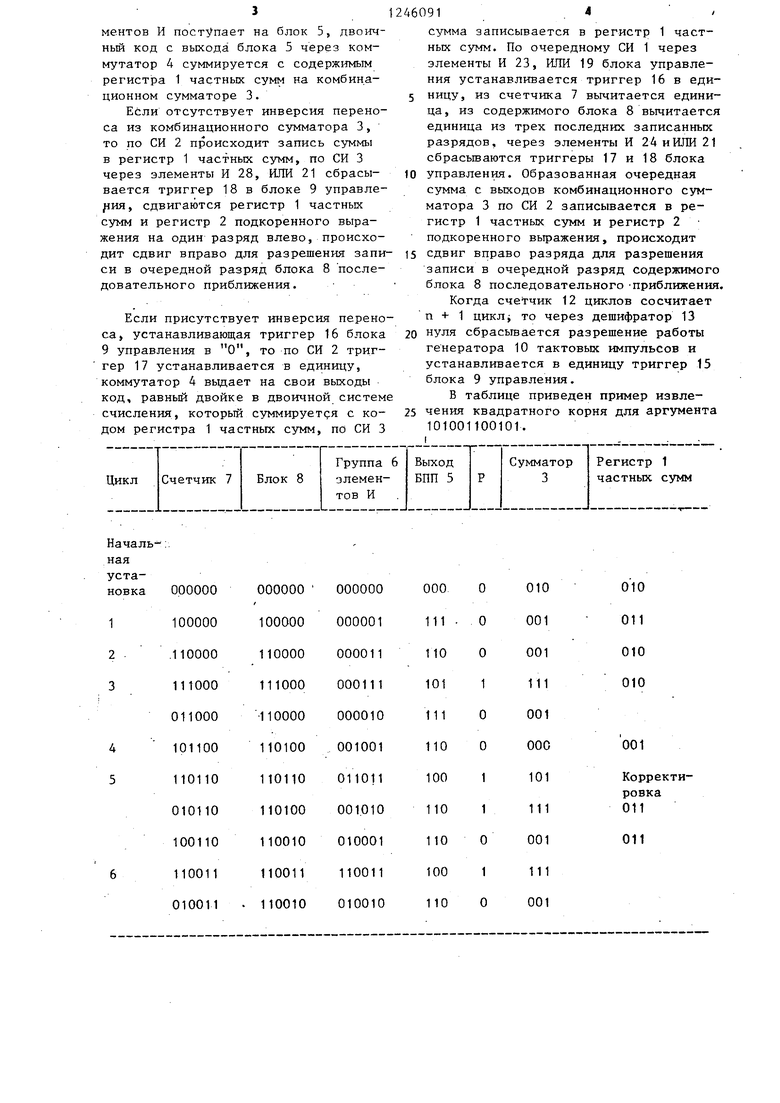

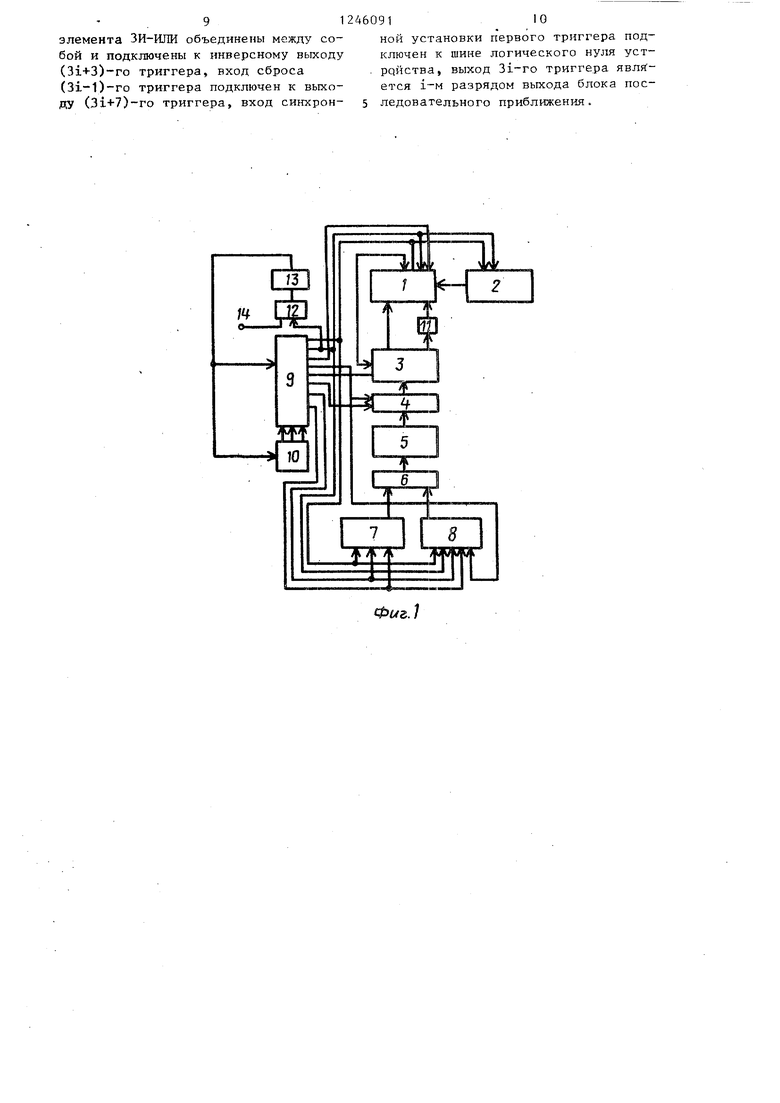

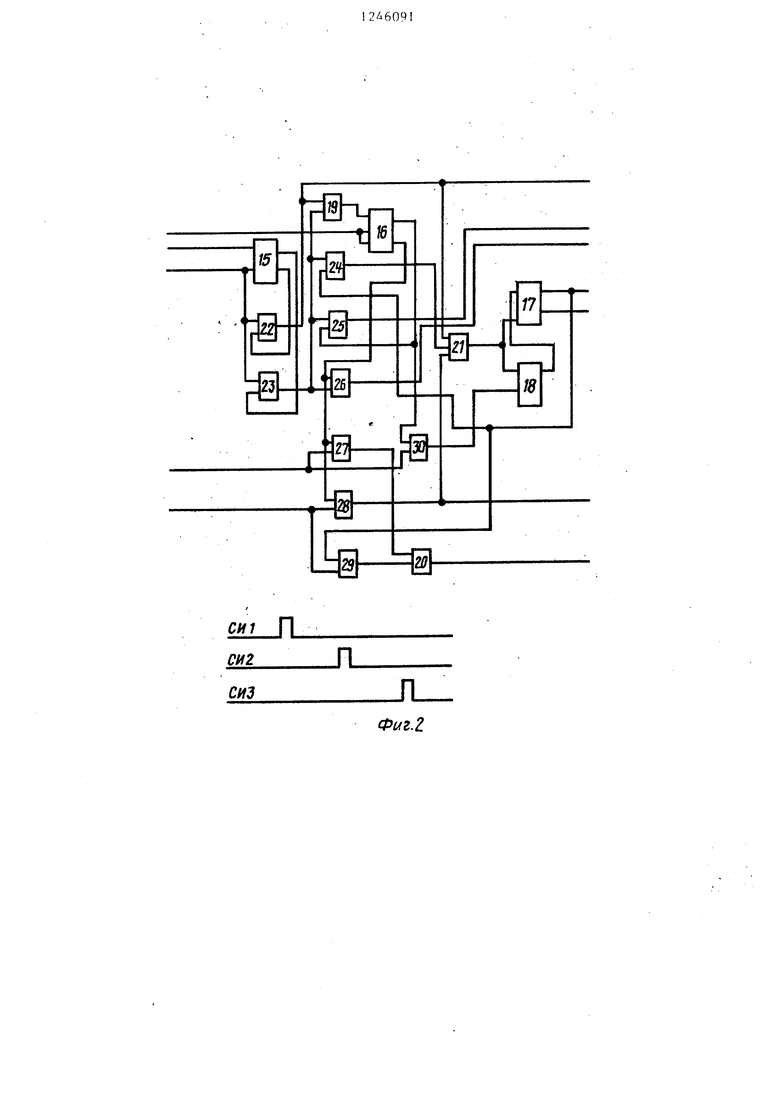

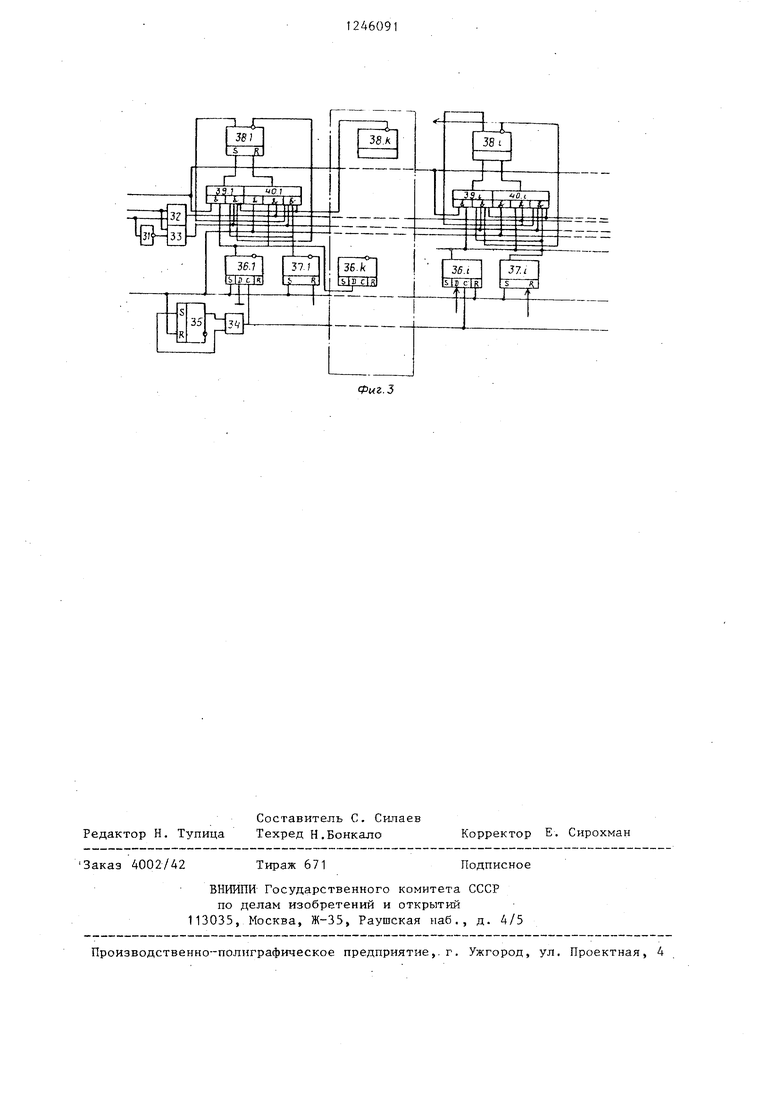

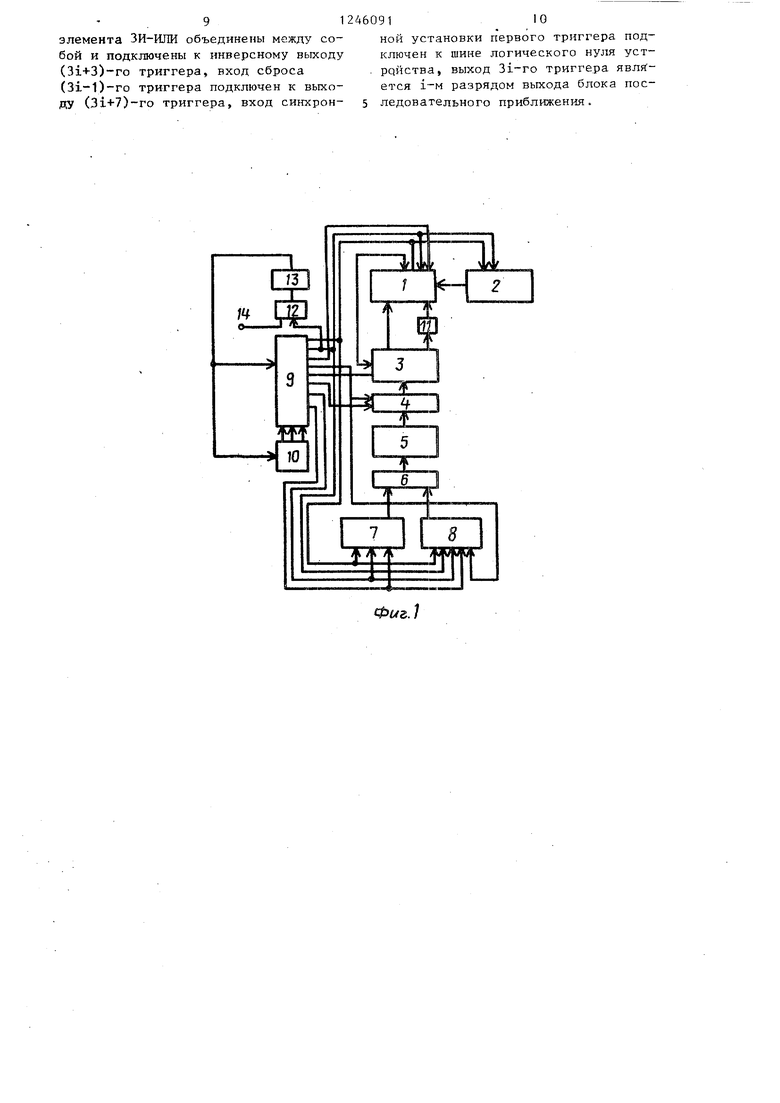

На фиг. 1 показана схема з строй- ства; на фиг. 2 - схема блока управления и диаграмма работы генератора тактовых импульсов; на фиг. 3 - схем блока последовательного приближения.

Устройство для извлечения квадратного корня содержит регистр 1 частных сумм, регистр 2 подкоренного выражения, комбинационный сумматор 3, коммутатор 4, блок 5 постоянной памяти (БПП), группу 6 элементов И, счетчик 7, блок 8 последовательного приближения, блок 9 управления, генератор 10 тактовых импульсов, элемент ИЛИ 11 счетчик 12 циклов, дешифратор 13 нуля и входную шину 14 сброса счетчика циклов.

Блок 9 управления содержит триг-« геры 15-18, элементы ИЛИ 19-21, элементы И 22-30.

Блок 8 последовательного приближения содержит элемент НЕ 31, элементы И 32-34, триггер 35 управления, триггеры 36.1-38.1, элемент 2И-ИЛИ 39.1, элемент ЗИ-ИЛИ 40.1.

Устройство работает следующим

образом.,

I

Блок 8 последовательного приближения записывает в каждый разряд единицу, начиная со старшего, последовательно. В зависимости от управляющих сигналов данная единица сбрасывается или оставляется в данном разряде. Возможно вычитание единицы из последних трех записанных разрядов. По входу сброса все элементы устанавливаются в исходное состояние. По входу сдвига определяется очередной разряд в который записывается единица. По входам сброса очередного записанного разряда и вычитания из последних трех записанных разрядов сбрасьгеается очередной разряд или вычитается единица из последних трех записанных разрядов. По входу записи устанавливается в единицу очередной разряд блока 8 последовательного приближения.

По входной шине 14 счетчик 12 циклов сбрасывается и через дешифра- гор. 13 нуля разрешает работу генератора 10 тактовых импульсов. По импульсу СИ 1 сбрасывается счетчик 7 и блок 8 последовательного приближения, регистр 1 частных сумм, триггер

913

15 блока 9 управления, записывается подкоренное число в регистр 2 подкоренного выражения , -через элемент ИЛИ 21 сбрасываются- триггеры 17 и 18

блока 9 управления, устанавливается через элементы И 22 и ИЛИ 19 в единицу триггер 16 в блоке управления. По импульсу СИ 2 в младший разряд регистра 1 частных сумм через элемент

ИЛИ 11 записывается старший разряд подкоренного числа.

По )ямпульсу СИ 3 регистр 1 частных сумм и регистр 2 подкоренного выражения сдвигаются на один разряд влево,

разрешается сдвиг в блоке 8, увеличивается на единицу значение счетчика. 12.

После начальной установки в устройстве повторяются циклы, количество

которых равно разрядности результата.

Каждый цикл работы устройства состоит из следующих шагов. По СИ1 подтверждается состояние триггера 16 блока 9 через элементы И 23 и ИЛИ 19, записывается предполагаемый разряд корня, который всегда равен единице, в счетчик 7 по входу сдвига влево и в блок 8. Выходы счетчика 7 и блока 8 соединяются с входами группы 6 элементов И

таким образом,. JJTO на первый элемент И приходит младший разряд счетчика 7 и старший разряд выхода 6j|OKa 8, на второй элемент И второй и п-1 разряды соответственно и т.д. С выходов

группы 6 элементов И образный уни- тарньй код поступает на входы блока постоянной памяти, преобразованный код через коммутатор 4 суммируется с кодом регистра 1 частных сумм на

комбинационном сумматоре 3. Если

отсутствует инверсия переноса из комбинационного сумматора 3, то по СИ 2 результат записывается в регистр 1 - частных сумм, а по СИ 3 сдвигаются

влево регистр 1 частных сумм, регистр 2 подкоренного выражения, разрешается Сдвиг в блоке 8. I.

Если есть перенос р из комбинационного сумматора 3, то триггер 16

блока 9 управления сбрасывается, по СИ 2 через И 30 триггер 18 устанавливается в единицу, по СИ 3 изменений не происходит. По очередному СИ 1 через И 23 и ИЛИ 19 триггер 16. блока 9 устанавливается в единицу и вьтитается единица из счетчика 7, сбрасывается очередной разряд блока 8. Унитарный код с группы 6 эле5 .

ментов И поступает на блок 5, двоичный код с выхода блока 5 через ком- fyтaтop 4 суммируется с содержимым perHCTjpa 1 частных сумм на комбинационном сумматоре 3.

Если отсутствует инверсия переноса из комбинационного сумматора 3, то по СИ 2 происходит запись суммы в регистр 1 частных сумм, по СИ 3 через элементы И 28, ИЛИ 21 сбрасывается триггер 18 в блоке 9 управле- ия, сдвигаются регистр 1 частных сумм и регистр 2 подкоренного выражения на один разряд влево, происходит сдвиг вправо для разрешения записи в очередной разряд блока В последовательного приближения.

Если присутствует инверсия переноса, устанавливающая триггер 16 блока 9 управления в О, то по СИ 2 триггер 17 устанавливается в единицу, коммутатор 4 вьщает на свои выходы код, равный двойке в двоичной систем счисления, который суммируется с кодом регистра 1 частных сумм, по СИ 3

20

46091.4 у

сумма записывается в регистр 1 частных сумм. По очередному СИ 1 через элементы И 23, ИЛИ 19 блока управления устанавливается триггер 16 в еди- 5 ницу, из счетчика 7 вьтитается единица, из содержимого блока 8 вычитается единица из трех последних записанных разрядов, через элементы И 24 и ИЛИ 21 сбрасываются триггеры 17 и 18 блока

10 управления. Образованная очередная сумма с выходов комбинационного сумматора 3 по СИ 2 записывается в регистр 1 частных сумм и регистр 2 подкоренного выражения, происходит

15 сдвиг вправо разряда для разрешения записи в очередной разряд содержимого блока 8 последовательного приближения.

Когда счетчик 12 циклов сосчитает п + 1 цикл то через дешифратор 13 нуля сбрасывается разрешение работы генератора 10 тактовых импульсов и устанавливается в единицу триггер 15 блока 9 управления.

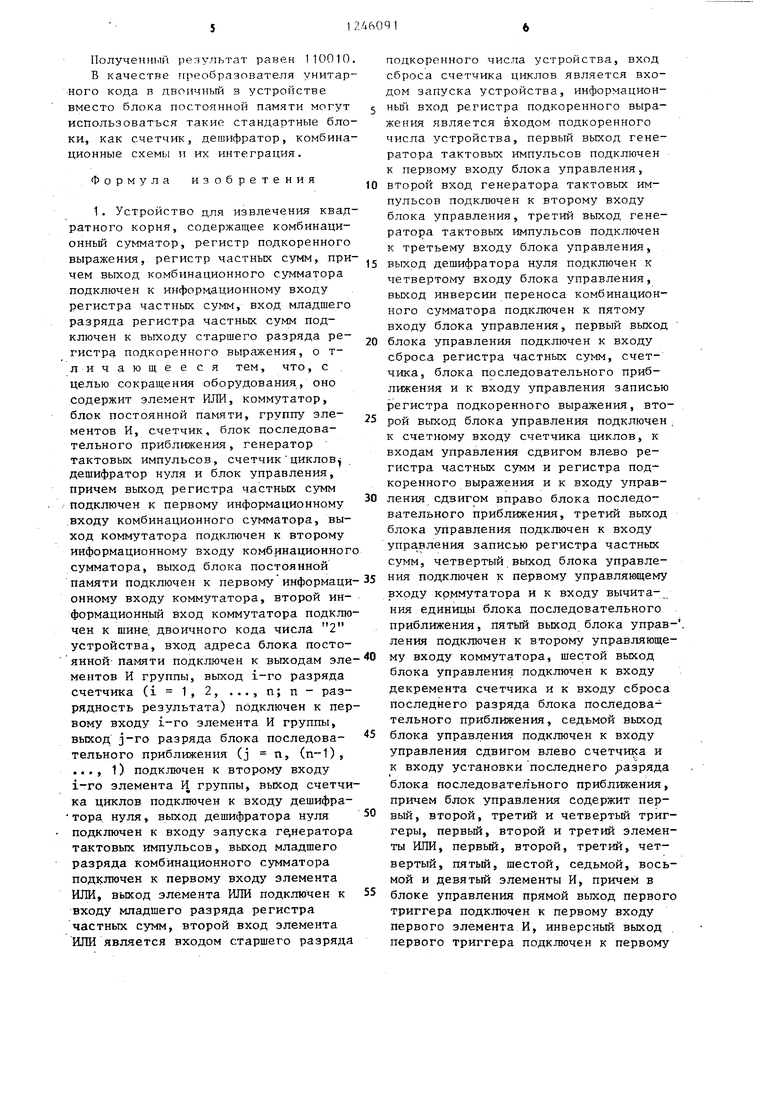

В таблице приведен пример извле-

25 чения квадратного корня для аргумента

101001100101.

I

Полученный результат равен 110010.

В качестве преобразователя унитарного кода в дг оичный в устройстве вместо блока постоянной памяти могут использоваться такие стандартные блоки, как счетчик, дешифратор, комбинационные схемы и их интеграция.

Формула изобретения

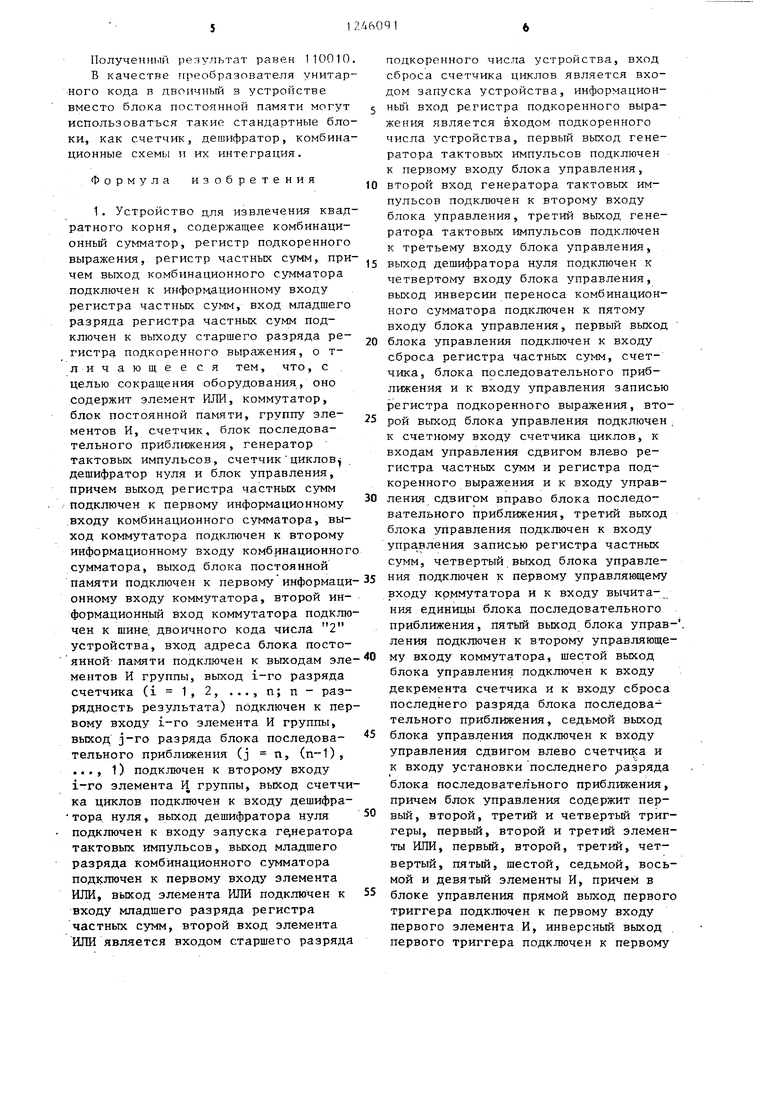

1. Устройство для извлечения квадратного корня, содержащее комбинационный сумматор, регистр подкоренного выражения, регистр частных сумм, при- чем выход комбинационного сумматора подключен к информационному входу регистра частных сумм, вход младшего разряда регистра частных сумм подключен к выходу старшего разряда ре

гистра подкоренного выражения, о т- личающееся тем, что, с целью сокращения оборудования, оно содержит элемент ИЛИ, коммутатор, блок постоянной памяти, группу эле- ментов И, счетчик, блок последовательного приближения, генератор тактовых импульсов, счетчик циклов дешифратор нуля и блок управления, причем выход регистра частных сумм подключен к первому информационному входу комбинационного сумматора, выход коммутатора подключен к второму информационному входу комбинационног сумматора, выход блока постоянной памяти подключен к первому информаци онному входу коммутатора, второй информационный вход коммутатора подключен к шине, двоичного кода числа 2 устройства, вход адреса блока посто явной памяти подключен к выходам эле ментов И группы, выход i-ro разряда счетчика (i 1, 2, ..., п; п - разрядность результата) подключен к первому входу i-ro элемента И группы, выход j-ro разряда блока последова- тельного приближения (j п, (п-1), ..., 1) подключен к второму входу i-ro элемента И группы, выход счетчика циклов подключен к входу дешифра тора нуля, выход дешифратора нуля подключен к входу запуска ге,нератора тактовых импульсов, выход младшего разряда комбинационного сумматора подключен к первому входу элемента ИЛИ, выход элемента ИЛИ подключен к входу младшего разряда регистра частных сумм, второй вход элемента ИЛИ является входом старшего разряда

0

,

0

0

5 5

О

0 5

подкоренного числа устройства, вход сброса счетчика циклов является входом запуска устройства, информацион- Hbrii вход регистра подкоренного выражения является входом подкоренного числа устройства, первый выход генератора тактовых импульсов подключен к первому входу блока управления, второй вход генератора тактовых импульсов подключен к второму входу блока управления, третий выход генератора тактовых импульсов подключен к третьему входу блока управления, выход дешифратора нуля подключен к четвертому входу блока управления, выход инверсии переноса комбинационного сумматора подключен к пятому входу блока управления, первый выход блока управления подключен к входу сброса регистра частных сумм, счетчика, блока последовательного приближения и к входу управления записью регистра подкоренного выражения, второй выход блока управления подключен . к счетному входу счетчика циклов, к входам управления сдвигом влево регистра частных сумм и регистра под- коренного выражения и к входу управления сдвигом вправо блока последовательного приближения, третий выход блока управления подключен к входу управления записью регистра частных сумм, четвертый выход блока управления подключен к первому управляющему входу кр,ммутатора и к входу вычитания единицы блока последовательного приближения, пятый выход блока управ- , ления подключен к второму управляющему входу коммутатора, шестой выход блока управления подключен к входу декремента счетчика и к входу сброса последнего разряда блока последовательного приближения, седьмой выход блока управления подключен к входу управления сдвигом влево счетчика и к входу установки последнего разряда блока последовательного приближения, причем блок управления содержит первый, второй, третий и четвертый триггеры, первый, второй и третий элементы ИЛИ, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый элементы И, причем в блоке управления прямой выход первого триггера подключен к первому входу первого элемента И, инверсный выход первого триггера подключен к первому

входу второго элемента И, выход первого элемента И подключен к первым входам первого и второго элементов Ш1И, выход второго элемента И подктш- чен к второму входу первого элемента 5 ШЖ и к первым входам третьего, четвертого и пятого элементов И, выход первого элемента РШИ подключен к входу асинхронной установки второго триггера, выход третьего элемента И 10 подключен к второму входу второго элемента ИЛИ, выход второго элемента ИЛИ .подключен к входам асинхронного сброса третьего и четвертого триггеров, прямой выход четвертого тригге- 15 ра подключен к счетному входу третьего триггера, прямой выход второго триггера подключен к nepBjjiH входам пятого, шестого и седьмого элементов И, инверсный выход второго триггера 20 подключен к второму входу четвертого и к первому входу девятого элементов И, выход шестого элемента И подключен к первому входу третьего элемента ИЛИ, выход седьмого элемента И подключен 25 к третьему входу второго элемента ИЛИ,-выход восьмого элемента И подключен к второму входу третьего элемента ИЛИ, выход девятого элемента И подключен к счетному входу четвертого 30 триггера, прямой выход третьего триггера подключен к второму входу третьего и к первому входу восьмого элементов И, причем вход сброса первого триггера соединен с вторыми входами 35 первого и второго элементов И и является первым входой блока.управления, вторые входы шестого и девятого элементов И соединены между собой и являются вторым входом блока управ- 40 ления, вторые входы седьмого и восьмого элементов И соединены между собой и являются третьим входом блока управления, вход установки первого триггера является четвертым входом 45 блока управления, вход синхронной установки в О и вход синхронизации второго триггера соединены между собой и являются пятым входом блока правления, выход первого элемента И 50 вляется первым выходом блока управления , выход седьмого элемента И вляется вторым выходом блока управения,, выход третьего элемента ИЛИ вляется третьим выходом блока управ- 55 ения, прямой выход третьего триггеа является четвертым выходом блока правления, инверсный выход третьего

триггера является пятым выходом блок управления, выход четвертого элемента И является шестым выходом блока управления, выход пятого элемента И является седьмым выходом блока управления .

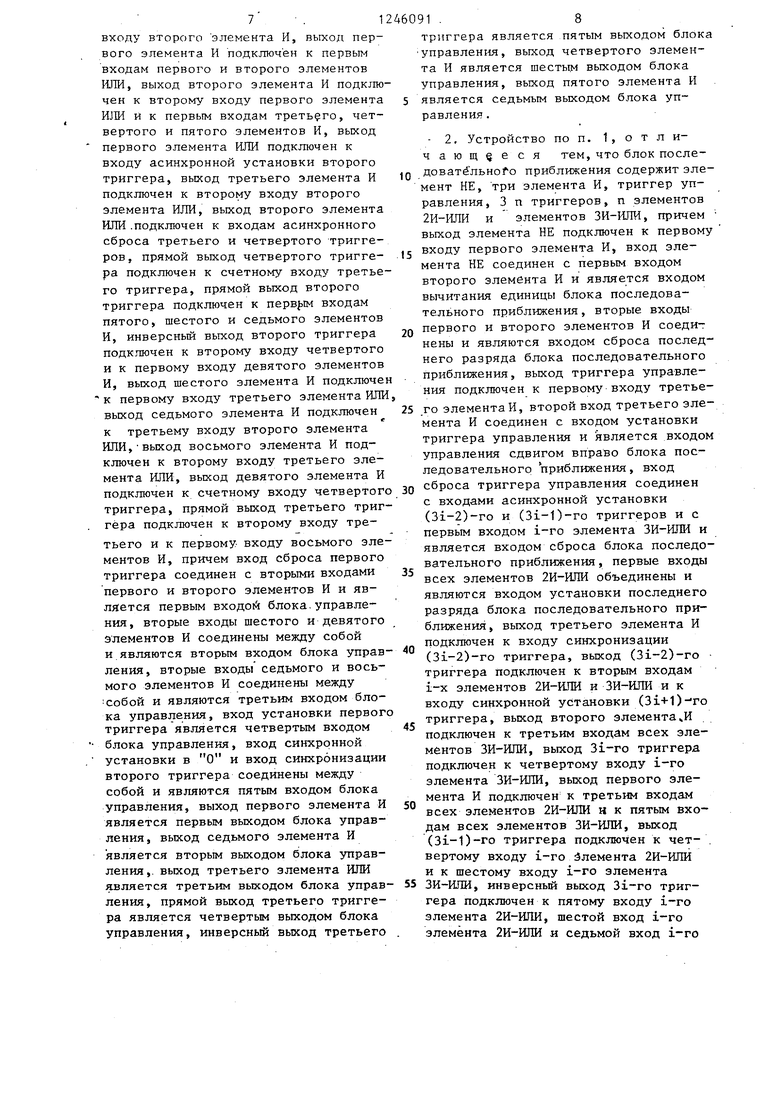

- 2, Устройство по п, 1, о т л и- чающ§еся тем, что блок после- доватё льно о приближения содержит элемент НЕ, три элемента И, триггер управления, 3 п триггеров, п элементов 2И-ИЛИ и элементов ЗИ-ИЛИ, причем выход элемента НЕ подключен к первом входу первого элемента И, вход элемента НЕ соединен с первым входом второго элемента И и является входом вычитания единицы блока последовательного приближения, вторые входы первого и второго элементов И соедит нены и являются входом сброса последнего разряда блока последовательного приближения, выход триггера управления подключен к первому входу третьего элемента И, второй вход третьего элемента И соединен с входом установки триггера управления и является входо управления сдвигом вправо блока последовательного приближения, вход сброса триггера управления соединен с входами асинхронной установки (3i-2)-ro и (3i-1)-ro триггеров и с первым входом i-ro элемента ЗИ-ИЛИ и является входом сброса блока последовательного приближения, первые входы всех элементов 2И-ИЛИ объединены и являются входом установки последнего разряда блока последовательного приближения, выход третьего элемента И подключен к входу синхронизации (3i-2)-ro триггера, выход (31-2)-го триггера подключен к вторым входам i-x элементов 2И-ИЛИ и ЗИ-ИЛИ и к входу синхронной установки (31+1)-то триггера, выход второго элементами подключен к третьим входам всех элементов ЗИ-ШШ, выход 3i-ro триггера подключен к четвертому входу i-ro элемента ЗИ-ИЛИ, выход первого элемента И подключен к третьим входам всех элементов 2И-ИЛИ н к пятым входам всех элементов ЗИ-ШШ, выход (3i-1)-ro триггера подключен к чет- вертому входу i-ro Элемента 2И-И1Ш и к шестому входу i-ro элемента ЗИ-ИЛИ, инверсный выход 3i-ro триггера подключен к пятому входу i-ro элемента 2И-Ш1И, шестой вход i-ro элемента 2И-Ш1И и седьмой вход i-ro

элемента ЗИ-ИЛИ объединены между собой и подключены к инверсному выходу (3i+3)-ro триггера, вход сброса (3i-1)-ro триггера подключен к выходу (3i+7)-ro триггера, вход синхронной установки первого триггера подключен к шине логического нуля уст- ррйства, выход 3i-ro триггера ется i-M разрядом выхода блока пос- ледовательного приближения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметико-логическое устройство | 1983 |

|

SU1176321A1 |

| Арифметико-логическое устройство | 1988 |

|

SU1599853A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1003078A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU924703A1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Арифметическое устройство | 1976 |

|

SU703804A1 |

| Арифметическое устройство | 1979 |

|

SU849206A2 |

| Многофункциональное вычислительное устройство | 1985 |

|

SU1293727A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для деления нормализованных чисел | 1985 |

|

SU1290302A1 |

Изобретение предназначено для вычисления квадратных корней из двоичных чисел и может быть ислользовано для построения цифровых вычислительных машин. Целью изобретения является сокращение оборудования. Устройство содержит регистр, подкоренного выражения, регистр частных сумм, комбинационный сумматор, коммутатор, элемент ИЛИ, счетчик циклов, дешифратор, генератор тактовых импульсов, блок управления, преобразователь кода унитарного в двоичный, группу элементов И, счетчик, регистр последовательного приближения, причем выходы счетчика соединены с первыми входами группы элементов И, выходы регистра последовательного приближения соединены с вторыми входами группы элементов И, выходы которых соединены с входами преобразователя кода унитарного в двоичный, выходы которого соединены с первыми входами коммутатора, выходы которого соединены с вторыми входами комбинационного сумматора, выходы которого соединены с входами регистра частных сумм, выходы генератора .тактовых импульсов соединены с входами блока управления, выходы которого соединены с управляющими входами счетчика, регистра последовательного приближения, коммутатора, регистра частных сумм, регистра подкоренного вьгражения, счетчика циклов, выходы счетчика циклов соединены с входами дешифратора, выход которого соединен с входом генератора тактовых импульсов, выход младшего разряда комбинационного сумматора соединен с первым входом элемента ИЛИ, второй вход которого является входом устройства, и выход которого .соединен с входом младшего разряда регистра частных сумм, выходы комбинационного суммат о- ра соединены с входом блока управде- ния, выходы регистра частных сумм соединены с первыми входами комбинационного сумматора, старший разряд регистра подкоренного выражения соединен по схеме сдвига влево с входом регистра частных суйм. 1 з.п. ф-лы, 3 ил., 1 табл. (О (Л ND 4 О) О ;о

х1ж

Н

Фиг.1

r&Vn

ш

17

СИ1 П

СИ2 СНд

Я

л

Фиг.2

Составитель С. Силаев Редактор Н. Тупица Техред Н.Бонкало

Заказ 40027А2

Тираж 671

ВНИИПЙ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие,, г. Ужгород, ул. Проектная, 4

Корректор Е. Сирохман

Подписное

| Устройство для извлечения квадратного корня и возведения в квадрат | 1974 |

|

SU571807A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Карцев Н.А | |||

| Арифметика цифровых машин | |||

| М.: Наука, 1969, с | |||

| Кухонный очаг | 1922 |

|

SU537A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-07-23—Публикация

1984-07-23—Подача