. .- ..Изобретение относится к области вычислительной техники и может бытБ использовано для выполнения операций сложения, вычитания, умножения, деления и извлечения квадратного корня при обработке больших массивов многоразрядных чисел.

Известно арифметическое устройство СЦВМ, в котором использован спбсоб ум- .ножения с промежуточным суммирсшанием частных производных и анализом четырех старших разрядов и метод асинхронного деления, а извлечение корня провЭводйтся методом итераций l.

В указанном устройстве каждаай щкл умножения характеризуется операцией сложения и сдвига.Время умножения одной пары разрядных чисел равно (Тсдож- Тсдв), а время извлечения квадратного корня в четыре раза больше. При обработке Hi чйсвп, рремя увеличивается как минимум еще в и раз. Таким образом, большой производительностью и быстродействием это устройство не обладает.

Извес-гно матричное ари4метнческое устройство, обладающее достаточно высоким быстродействием 2}.

Однако, это устройство не имеет большой производительности при обработке массивачисел. Обработку очередной пары чксеа моящб производить лишь тогда, когда будет получен предыдущий результат.. - - .

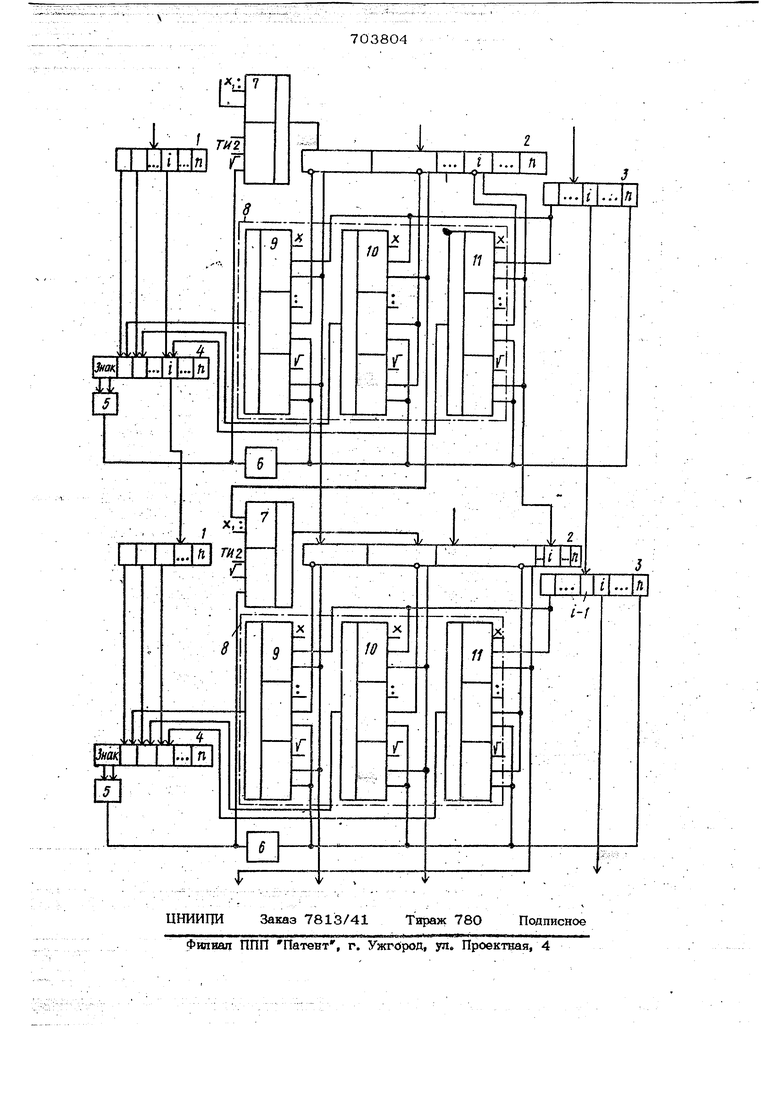

Наиболее близким по технической сущности к предложенному является арифметическое устройство, содержащее И последовательно соединенных однотипных блоков, причем каждый блок содержат два регистра, комбинационный сумматор и триггер, выходы первого регистра каждого блока соединены с первой группой входов комбинационного сумматора того же блока, выход i -,ро ( i О,.., , h -1) комбинацнонно1Х) сумматора ( К -1 )го блока (Н-2, ...,П ) соединен со входсяй ( + 1)что разряда первого регистра блока, выход ..го разряда второго регистра ( К- 1)г4О блока подключен ко входу 1 -го разряда второго регистра К -го блока, входы первого и второго регистров первого блока -соединены с первой и второй группами входов устройства 3. Данное устройство не предназначено для вычисления результатов операций дел ния и извлечения квадратного корня. Целью изобретения является расширение функциональных возможностей, заключающееся в возможиости выпошзения операций деления и извлечения квадратного корня. Для достижения поставленной цели каж дый блок устройства содержит третий регистр, узел айаййза переполнения комбинационного сумматора, первый и второй коммутаторы, ходы узла анализа перепол нения комбинационного су дматора каждого блока соединень с выходами знакового разряда комбинационного сумматора, а выход подключен ко входу триггера и первому входу первого коммутатора, вы ход триггера подключен ко входу VI-го разряда третьего регистра ипервому вхо ду каждого разряда второго коммутатора, второй вход которого соединен с выходсал первого разряда третьего регистра, третий и четвертый входа т соединены с прямым и инверсным выходами соответствукяцёго разряда второго регистраз выходы второго коммутатора соединены со второй группой входов комбинайЁонйого сумматсора, второй вход первого коммутатора блока соединен с BbccOinoM ) разрыда второго регистра (К-1)-го блока, вторЪй вход первого коммутатора nepiBord блока соединен со входом устрой ства, первый, второй и третий управляющие входы первого коммутатора соединены соотватственно с управляющей шиной умнрЖйсия и деления, управляющей шиной извлечения корйя и тактовой шиной устройства, выход i-го разряда третьего регистра ( i - 2, ..., П ) ( К- 1)-го блока соединен со входом (-i - 1 )чго разря да третьего .регистра К-го блока, входы третьего регистра первого блока соедине ны с третьей группой входе устройства, первый, второй и третий управляющие входы второго коммутатора соеданены со ответственно с управляющими шинами ум ножения, деления а извлечения корня уст ройства, выход первого коммутатора m го блока ((т1- 1, .,., и) соединен со вхо дом hi го разряда Btoporo регистра того же блсжа. Для досггижения поставленной цели первый коммуп-атор каждого блока усгройсп-ва содержит также элемент И-И/1И., первая группа входов которого соединена со вторым и первым управлякацим входами коммутатора, а вторая группа входов - с первым и вторьпи н третьим управляющими входами коммутатора. Кроме того, второй коммутатор каждого К-а-о (К- 1, ..., и) блока устройства содержит VI элементов И-ИЛИ (по одному в каждом разряде ) причем первая групла входов каждого Элемента И-ИЛИ соединена с первым управляющим, вторым и третьим входами коммутатора, вторая группа входов соединена со вторым управляющим, первым и четвертым входами ксадмутатора, первый и второй входы третьей группы входов первого - h -го элементов И-ИЛИ соединен с третьим ynpsiB- лякяцим и первым входами коммутатора, третий вход третьей группы входов (К + -f 1)-го элемента И-ИЛИ соединен с четвертым входом коммутатора, а третьи входы третьей группы входов остальных элементов, соединены с третьими входами коммутатора. На чертеже представлена функциональная схема арифметического устройства (изображены первые два блока устройства) Каждый блок арифметического устройства содержит регистры 1-3, комбинациош1Ый сумматор 4, узел S анализа переполнения комбинационного сумматора 4, триггер 6, первый коммутатор 7, представляющий собой элемент И-ИЛИ, и второй коммутатор 8, содержалий элементы И-ИЛИ 9-11 (всего второй коммутатор 8 содержит VI элементов И-ИЛИ, по числу разрядов регистра 2). , Регистр 1 1-го блока устройства предназначен для хранения и выдачи делимого, множителя, подкоренного выражения, регистры 1 остальных блоков служат для храншиЯ;, сдвига влево и выдачи остатков при делении и извлечении квадратного корня или частных сумм при умножении. Выходы регистров 1 соединены с входами сумматоров 4 тех же блоков устройства, .1 - е выходы сумматоров 4 прел авдущих блоков соединены с (i + 1)-ми входами регистров 1 псйследующих блоков. Зна. ковые разряды сумматоров 4ч К-ых блоков через узлы 5 анализа переполнения комбинаМяонных сумматоров 4 и первые коммутаторы 7 соединены с Кнми входами регистров 2, а через триггеры 6 переполнения-с И -ми разрядами регистров О; 1 ё выходы регистров 3 предыдущих блоков . соединешл с (1 - 1 )-мк входами регист ров 3 последующих блоков. Регистры 2 соединены следующим образом. 1-е прямые выходы предыдущих регастров 2 соединены с i -ми входами последующих регистров 2, кроме (К+ 1) ых выходов регистров 2. К-ых блоков уст ройства (К- 1, ..., П-1), соединяющихся с К-ми входами последующих регистров 2 через коммутаторы 7. Инверс11ые и прямые выходы регистров 2 соеди нень также с входами коммутаторов 8, Входы первой группы входов каждого элементе И-ИЛИ 9-11 соединены с упраВ ляющей шиной умножение ( К ), с первым выходом регистра 3 и с прямым вы ходом соответствующего разряда рёгнсггра 2. Входы второй группь входов этих же элементов соединены с управляющей шиной деление ( : ), с инверсным выходсм соответствующего разряда регистра 2 и с выходом триггера б переполнения. Входы третьей группы входов соединены с управляющей шиной извлечение квадратного корня (тГ), с инверсным вьрсодом (для И-ИЛИ коммутатора 8 Кнго блсжа устройства) или с прямым в ходом (для всех остальных элементов И-ИЛИ коммутатора 8) регистра 2 и с выходом триггера 6 переполнения. Входы первой группы входов элемента И-ЛЛИ коммутатора 7 соединены с управлякядей шиной умножение, .деление а входы второй группы входов соединены с упр авляющей шнной извлечение квад- ратного корня и с тактирующим входом ТИ2. Сложение производится только младщих разрядах с запоминанием переноса в отдельных триггерах, не показанных на чертеже, с последующей перезаписью результата предыдущей ступени обработки в последующую. Умножение массива чисел в арифметическом устройстве происходит следующим образом. Первое множимое поступает в регистры 2 1-го блока, а первый множитель - в регистр 3, причем он располагается таким образом, что 1чй разряд регистра 3 - младщий разряд множителя. Умножение производят, младшими разрядами вперед при неподвижном множимом последовательнотпараллельньш спобЪбом. В первой ступени обработки все разряды множимого регистра 2 умножают на 1нй младший разряд множителя регистра 3, Если 1-ый разряд множителя равен едшппте, содержимое регистра 2 проходит на сумма-; тор .4 и складывается с нулевыми зпачениями реЛ{Стрп 1. В сумматоре 4 образуется первая частичная сумма произведения первого множимого на 1-й разряд первого множителя. Со сдвигом вправо первая частичная сумма передается в регистр 1 2-го блока. Первое множимое переписывают в регистр 2 прямо, а множитель - в регистр 3со сдвигом влево, так что отбрасывается его 1-й младший разряд. Во втором такте в освободившиеся регистры 1-го блока nocTynaipT два следую- . щих числа, которые надо перемножить. Аналогичным образом получают в сумматфе 4 первую частичную сумму произведения BTOpoix) множимого на 1-й разряд второго множителя. . Одновременно во 2-ом блсже в сумматоре 4 складывают первую частичную сумму регистра 1 с частичным произведением первого множимого регистра 2 на 2-й разряд первого мно)«адтеля, получая таким образом вторую частичную сумму первой пары сомножителей. Далее производят перезапись содержимых регистров и сумматоров 1-га и 2-го блоков в последующие и прием третьей пары сомножителей в 1-й блок. Таким образом, на выходе сумматора 4II -го блока полное произведение первой пары чисел будет достигнуто через h т.актов, а произведение всех последующих пар чисел будет появляться на выходе сумматора через каждый такт.. Число тактов для In П -разрядных чисел равно m -l4h. Деление вьшолняют методом деления, бёа восстановления Остатка. Первое делимое заносят в регистр 1 блока, первый делитель - в регистр 2. Частное получают в регистре 3, причем, старший разряд заносят в |1-й разряд регистра. Вычитание производят сложением в обратном модифицированном коде. Передачу остатка из сумматора 4 в регистр 1 последующего блока производят с одним едваГ(Ж. влево, но так как цепи сдвига построены с одним сдвигом вправ.о, то для получения необходимого сдвига производят два сдвига влево в регистре 1. Делитель передают прямо в регистр 2, а цифры частного передают на регистр 3 со сдвигом влево. Последующие пары цифр поступают в освободившиеся регистры. Окончательный результат V; : : . , деления получают на вьГхбде регистра 3 h-ro блока. Знаковые разряды сумматора 4 через узел 5 анализа переполнения ко лбкявшонного сумматора 4 и триггер 6 перепол- имения управляют восстановлением остатка в комбинационном сумматоре 4 и определяют цифру частного. При п6п05китепьном остатке в регистр 3 в Ц-и разряд записывают , а при отрицательном -О, восстанавливают предыдущий остаток, ве производя вьиитания в сумматоре 4. Извлечение йад йгйого корня вШолняют школьным методом. Все Иййгры 1 н 2 н триггеры 6 сбрасывают в О, а затем регистры 2 устанавливают в 1. Пераёё йойкй рёйнс е i JJ fflWliofef в регистр 1, а затем в сумматор йроисзсодит вычитание (сложение в обрат НОМ модифицированном коде) сбдарЖмбго peirjiCTpa 2 с пропуском разряда . (101111 ...). Знаковый разряд определя |т :-| Ййё1Шё%ёрёбгчз Чй рШуП& Ша в обратнЬм коде, который записывают во вто{)й5 акте ТИ 2 через коммута 7 в 1-Й разряд регистра 2. При полоАйтельной сумме 1 на выходе тртхтера 6 не Йренйтствувт сложеИШб содер:)йимда гистров 1 и 2, результат записывают 0. При отрицательной сумме производят во тбтайовпение аначшия подкоренного выражения, а в результат записывают 1. Содерж0моё сумматора 4 перешсьгвают в регистр 1 SHT-O блока ййаЯб Шёо Шёрациа деиеаия (со сдаигом влево на два разряда). Значение 1-го разрйда регистра 2 Пёрсзписывают в этот же разряд регистра 2 последующего блока; В бснободившийся регистр 1-го бйбай йринйм ют новое подксфевное значение. В 1-ом блоке йрЬй§водя ШёраййЮНад вторым операндом, одновременно во второй ступени продолжают действия над вторым операндом. Результат получают на вьпсо де регистра 2 -fo блока в обратном ко .- -:г--:;;«---,- . . . - Арифметическое устройство при миниMfljtbHbix дополнениях пригодно для об-, работки операндов, представленных с пла вающей задятой. Совмещение операций во времейи позволили получить структуру устрБЙстЁа бо лее экономичную по объему оборудования и количеству связей между узлами, чем щяй. параллельной работе отдельных арифметичейсйх узлов. Формула б р е т е н и я 1. Арифметическое устройство, содержащее 11 последовательно соединенных однотипных блоков, причем каждый блок содержит два регистра, комбинационный Сумматор и триггер, выходы первого регистра каждого блока соединены с первой грутгпоЙ входов комбинационного сумматора того же блока, выход i -го разряда (i - О, ..., in-l) кобминационного сумматора ( К- 1)-го блока { К,-, 2, ..., П ) сх)единен со входом ( i + 1 )-го разряда первого регистра К,-го блока, выход i что разряда второго регистра ( К- 1)гр блока под слючен ко входу i -го разряда второго регистра Х-го блока, первого и второго регистров первого блока соединены с первой и второй rpjranaivJH входов уо т л и ч аю щ е е с я тем, что, с целью расширения функциональных возможностей устройЬТва, заключающегося в возможности выполненияопераций деления и извлечения квадратного корня, каждый блок устрой|Сгва, содержит третий регистр, узел анализа перепоШёния комбинационного сумматора, первый и вторвй коммутаторы, входы узла анализа переполнения комбинационного сумматора каждого блока соединены с выходами знакового разряда комбинационного сумматора, а выход подключён ко входу триггера и первому первого коммутатора, выхОд триггера подкяючен ко входу ti-ro разряда третьего рэгисгра и первому входу каждого разряда второго коммутатора, второй вход которого соединен с выходом первого разря- . да третьего регистра, третий и четвертый входа соёдинеHbt с прямым и инверсным вьйсОдами соответствующего разряда второго регистра, выходы второго коммутатора соединены со второй группой входов комбинаив онйЬгЧ)°6умМа ора, второй вход первого коммутатора К-го блока соединен с выходом К -го разряда второго регистра (К- l)-j:o блока, второй вход первого коммутатора первого блока соединен bo устройства, первый, второй к .третий управляющие входы первого коммутаггора соединены срответсгвенно с управлйкяцей шикрй умножения и деления, управлякицей шиной извлечения корня и тактсжой шиной уЬгррйсгва, выход i -го разряда третьего регистра (is 2, ..., и ) ( К- 1)-го блока соединен со входом (i - 1)-го разряда третьего регистра блока, входы третьего регистра пербого блока соединены с третьей группой входов устройства, первый, второй и третий управляющие входы второго коммутатора соединены соответственно с управляющими, шинами умножения, деления и извлечения корня устройства, вькод первого коммутатора m -го блока (щ 1, .... h ) соединен со входом т-го разряда второго регнсггра того же блока. 2.Арифметичесжое устройство по п. 1, отличающееся тем, что первый коммутатор каждого блока устройства содержит элемент И-ИЛИ, первая групйа входов которого соединена со вторым и первым управлякнцвм входами коммутатор ра, а вторая группа входов - с первым и вторым и третьим управляющими входами коммутатора. 3.Арифметическое устройство по п. 1, отличающееся тем, что второй коммутатор каждого k -го (К 1, .., п) блока устройства содержит И элементов И-ИЛИ (по одному в каждом раа 70 4 ряде), причем первая группа входов каждого элемента ИЛЛИ соединена с первым управлякнцнм, вторым и третьим входами коммутатора, вторая группа входов соединена со BTOjbiM управляющим, первым и четвертым входами коммутатора, первый и второй входы третьей группы входов первого - И -го элемента И-44ЛИ соединены с третьим управляющим и первым входами коммутатора, третий вход третьей группы входов ( К+ 1) элемента И-41ЯИ соединен с четвертым входом коммутатора, а третьи входы группы входов остальных элементов И-ИЛИ соединены с третьими входами коммутетора. Источники внформаши, принятые во внимание при экспертизе 1. Авторское свидетельство. СССР NJ 234753, кл.6 Об F 7/38, 1967. 2. Патент 3535498, кл. 235-164, 1970. 3. Авторское свидетельство СССР hb 479111, кл. Q 06 F 7/52, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1979 |

|

SU849206A2 |

| Арифметическое устройство | 1979 |

|

SU798825A1 |

| Арифметическое устройство | 1982 |

|

SU1089577A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Арифметическое устройство | 1985 |

|

SU1290299A1 |

| Арифметическое устройство | 1978 |

|

SU711570A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Арифметико-логическое устройство | 1988 |

|

SU1599853A1 |

| Устройство для умножения | 1981 |

|

SU1012245A1 |

| Матричное устройство для умножения и сложения | 1977 |

|

SU657434A2 |

Авторы

Даты

1979-12-15—Публикация

1976-10-25—Подача