Изобретение относится к информа- ционно-нэмерительной и вычислительной технике и может быть использовано для получения квадратичной зависимости при построении автоматических измерительно-вычислительных устройств, например, при линеаризации характеристик частотных датчиков.

Цель изобретения- повышение точности выполняемой операции, которая достигается за счет введения накапливающего сумматора.

Введение в устройство накапливающего сумматора позволяет перейти от суммирования одноразрядных приращений интеграла (квадрата входного числа), как это имеет место в известном устройстве, к суммированию как одноразрядных приращений, так и (m-n)-разрядных приращений интеграла (резуль- тата, что приводит к повьппению кости. Одноразрядные приращения интегральной суммы (результата операции поступают на вход переноса накапливающего сумматора с выхода логического блока, а (m-n)-разрядные приращения - на его кодовые входы с выхода m-n старших разрядов tn-разрядного счетчика.

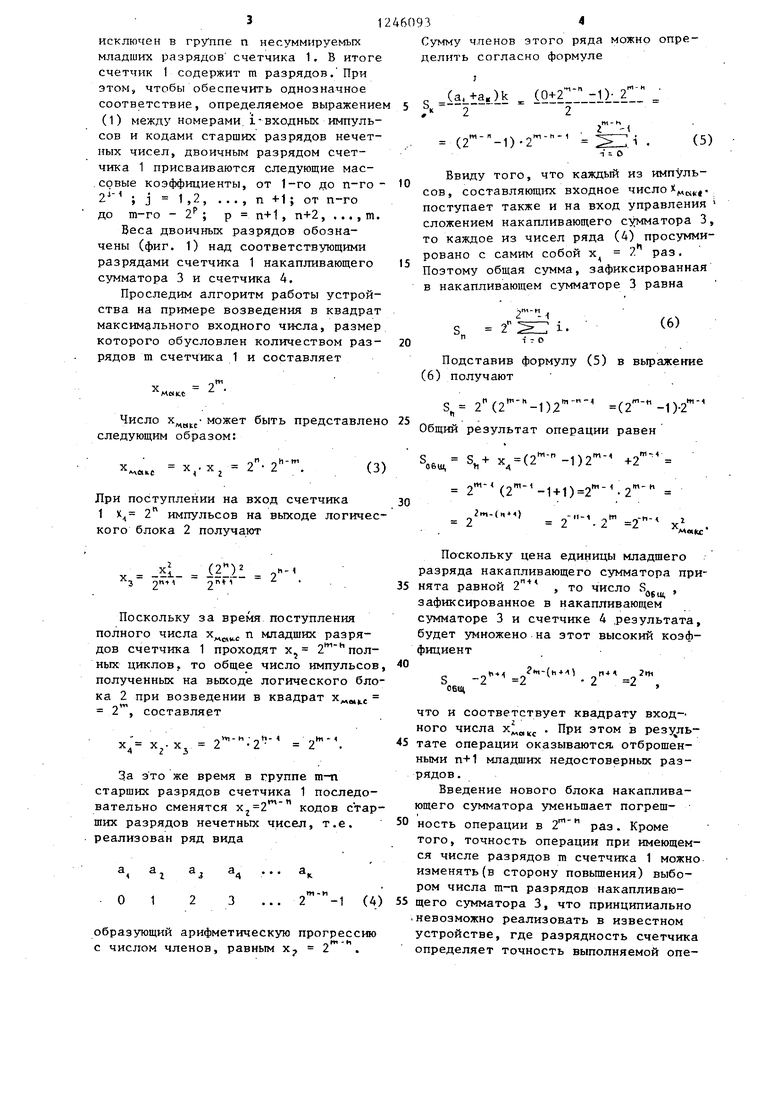

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - структура логического блока 2.

Устройство содержит ш-разрядный счетчик 1 - формирователь двоичных нечетных чисел, логический блок 2, состоящий из набора К элементов И и одного (К + 1)-входового элемента ИЛИ (фиг. 2), накапливающий сумматор 3 и счетчик 4 результата.

В ш-разрядном счетчике 1 выделены три, приблизительно равные по количеству разрядов группы: группа тп-п старших разрядов, группа n-k-1 сред- них разрядов (числа п и k связаны соотношением ) и группа k+1 младших разрядов. Группа,k-+-1 младших разрядов счетчика 1 совмещает в себе функции программного счетчика цифро- частотного интегратора и младшшс разрядов счетчика, формирующего значения дйоичньпс символов подынтеграль ной.функции. Это сделано для того, чтобы устройство работало по моди- фицированному алгоритму, основанному на совмещении в реальном времени, процедур, описываемых выражениями

У(х) .2: (21-1) х

(1)

f.K(

z(t) -i2K ( 1dx)dy ktS (2)

0 0

согласно которым формируются (m-n)- разрядные и -одноразрядные приращения интегральной суммы (результата операции), фиксируемой в накапливающем сумматоре и счетчике результата. Устройство, реализующее указанный алгоритм, благодаря введению накапливающего сумматора, лишено отмеченных недостатков.

Устройство работает следующим образом.

Вначале по шине Установка нуля осуществляется обнуление счетчика 1, накапливающего сумматора 3 и счетчика 4 результата. Затем число-импульс„ г / , оТ Ч

ныи КОД x OixiZ ) поступает на вход счетчика 1, причем каждый из входных импульсов поступает также на вход управления сложением (вход переменной интегрирования) накапливающего сумматора 3. Нечетные числа, формируемые в счетчике 1, являются дискретными значениями подынтегральной функции, нарастающей по линейному закону (1), старшие разряды которых представляют собой код (m-n)-разрядных приращений интегральной суммы (результата операции), фиксируемой в накапливающем сумматоре 3. На вход переноса сумматора 3 поступают одноразрядные приращения, формируемые с помощью п младших разрядов счетчика 1 и логического блока 2.

Имп:ульсы, появляющиеся на выходе логического блока 2 (одноразрядные приращения), выполняют функцию коррекции погрешности результата операции, возникающей из-за отсутствия накапливающего сумматора в области п младшшс разрядов счетчика 1. Импульсы переполнения накапливающего сумматора подсчитываются счетчиком 4.

Результат операции находится в накапливающем сумматоре 3 и счетчике 4.

Для получения требуемого алгоритма обработки кодов старших разрядов нечетных чисел счетчик 1 содержит на один разряд меньше, чем необходимо для представления максимального нечетного числа 2х. (нечетЖ J I ЛИ КС

нее число 2 -1 состоит из ш + 1 единиц и требует счетчика, содержащего m + 1 разрядов). Этот разряд

исключен в группе п несуммируемых младших разрядов счетчика 1, В итоге счетчик Г содержит m разрядов. При этом чтобы обеспечить однозначное соответствие, определяемое выражение (1) между номерами.i- входных импульсов и кодами старших разрядов нечетных чисел, двоичным разрядом счетчика 1 присваиваются следующие массовые коэффициенты, от 1-го до п-го - 2 ; j 1.2, ..., п +1; от п-го до т-го -2 ; р п+1 , п+2, ... , т.

Веса двоичных разрядов обозначены (фиг. 1) над соответствующими разрядами счетчика 1 накапливающего сумматора 3 и счетчика 4.

Проследим алгоритм работы устройства на примере возведения в квадрат максимального входного чи-сла, размер которого обусловлен количеством разрядов m счетчика 1 и составляет

Сумму членов этого ряда можно определить согласно формуле

, (a.+a,)k (Ol2:i 4) 5 S,2 2

()

1 .

(5)

Ввиду того, что каждый из импульсов, составляющих входное число х,., поступает также и на вход управления сложением накапливающего сумматора 3, то каждое из чисел ряда (4) просуммировано с самим собой х - раз. Поэтому общая сумма, зафиксированная в накапливающем сумматоре 3 равна

(6)

20

Подставив формулу (5) в вьфажекие (6) получают

MMice 2

Число ,j- может быть представлено следующим образом:

о oh-m MOkC - 4 X 2 - / .

Лри поступлении на вход счетчика 1 х 2 импульсов на выходе логического блока 2 получают

, - 5L - i2:)i И-.

3 1 9 i. .

Поскольку за время поступления полного числа х п младших разрядов счетчика 1 проходят х нь1х циклов, то общее число импульсов полученных на выходе логического блока 2 при возведении в квадрат 2, составляет

-п,- и - и- т - 4

х х. х 2 -2- 2

За э то же время в группе m-n старших разрядов счетчика 1 последовательно сменятся кодов стар- щих разрядов нечетньпс чисел, т.е. реализован ряд вида

а аJ а а ... а

012 3 ... (4)

образующий арифметическую прогрессию с числом членов, равным х-, 2.

25

S ) ( Общий результат операции равен

Soe S.-b х ()2 -

мм 2

30

(2 - -И-1) 2

2т-(цч)

((с

Поскольку цена единицы младшего разряда накапливающего сумматора при- нята равной 2 , то число S , зафиксированное в накапливающем сумматоре 3 и счетчике 4 .результата, будет умножено на этот высокий коэффициент

S . 2 2

Общ

что и соответствует квадрату вход-- ного числа . При этом в резууть- тате операции оказываются, отброщен- ными п+1 младших недостоверных разрядов.

Введение нового блока накапливающего сумматора уменьшает погрещ-

ность операции в раз. Кроме

того, точность операции при имеющемся числе разрядов m счетчика 1 можно изменять (в сторону повьппения) выбором числа m-n разрядов накапливающего сумматора 3, что принципиально Невозможно реализовать в известном устройстве, где разрядность счетчика определяет точность выполняемой oneрации, которая в этом случае является невысокой.

Формула изобретения

Устройство для возведения в квадрат число-импульсного кода, содержащее входной счетчик и К элементов И,

п- 1

где -К 9 Р этом п определяется требуемой точностью при фиксированной разрядности входного счетчика т, выход i-ro разряда входного счетчика соединен с первым входом i-ro .элемента И (i 1,К), выход (К + 1) +1 разряда входного счетчика соединен с вторым входом i-ro элемента И, входы сброса входного и выходного счетчиков с одноименным входом устройства, счетный вход входного счетчика является информационным входом устройства, о т л и ч а ю щ

К-

Н, Тупица

Ф(4г.2

I

Составитель Д. Хан-Магомедов Техред Н.Бонкало

Заказ 4002/42

Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35 Раушская наб„, д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

е с я тем, что, с целью повышения точности, в него введены элемент ИЛИ и накапливающий сумматор, информаци- онные входы которого подключены к выходам (m-n) старших разрядов входного счетчика, выход переноса накапливающего сумматора подключен к счетному входу выходного счетчика, а вход

переноса - к выходу элемента ИЛИ, i-й вход которого подключен к выходу i,-ro элемента И, а (К + 1)вход - к выходу К -ь I разряда входного счет- чика, вход управления сложением и

вход сброса накапливающего сумматора, соединенные информационным входом и входом сброса устройства соответственно, выходы накапливающего сумматора являются выходами (m-n) младших

разрядов результата устройства счетчика, результата, выходы выходного счетчика являются выходами m старших разрядов счетчика результата.

Корректор Е. Сирохман

| название | год | авторы | номер документа |

|---|---|---|---|

| Квадратор | 1985 |

|

SU1319026A1 |

| Устройство для возведения п-разрядных чисел в квадрат | 1979 |

|

SU911520A1 |

| Устройство для извлечения квадратного корня | 1980 |

|

SU1099318A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| Многоканальный накапливающий сумматор по произвольным модулям | 2024 |

|

RU2837596C1 |

| Устройство для определения действующего значения сигнала | 1983 |

|

SU1141421A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

Изобретение относится к области вычислительной техники. Цель изобре:тения - повьшение точности вьтолняемой операции, которая достигается за счет введения накапливающего сумматора. Устройство содержит т-разряд- ный двоичный счетчик, счетчик результата, логический блок, состоящий из К элементов И и элемента ИЛИ, накапливающий сумматор с соответствующими связями. Принцип работы устройства основан на суммировании одноразрядньк и (m-n)-разрядных приращений интеграла (результата). Одноразрядные приращения результата поступают на вход переноса накапливающего сумматора с выхода логического блока, а (m-n)- разрядные приращения - на его кодовые входы с выхода (m-n) старщих разрядов т-разрядного счетчика. 2 ил. .с о (Л 4i Од ;& оо

| Данчеев В.П | |||

| Цифровое устройство воспроизведения квадратичной временной зависимости | |||

| -Автоматика и вычислительная техника | |||

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

| Спускная труба при плотине | 0 |

|

SU77A1 |

Авторы

Даты

1986-07-23—Публикация

1985-01-07—Подача