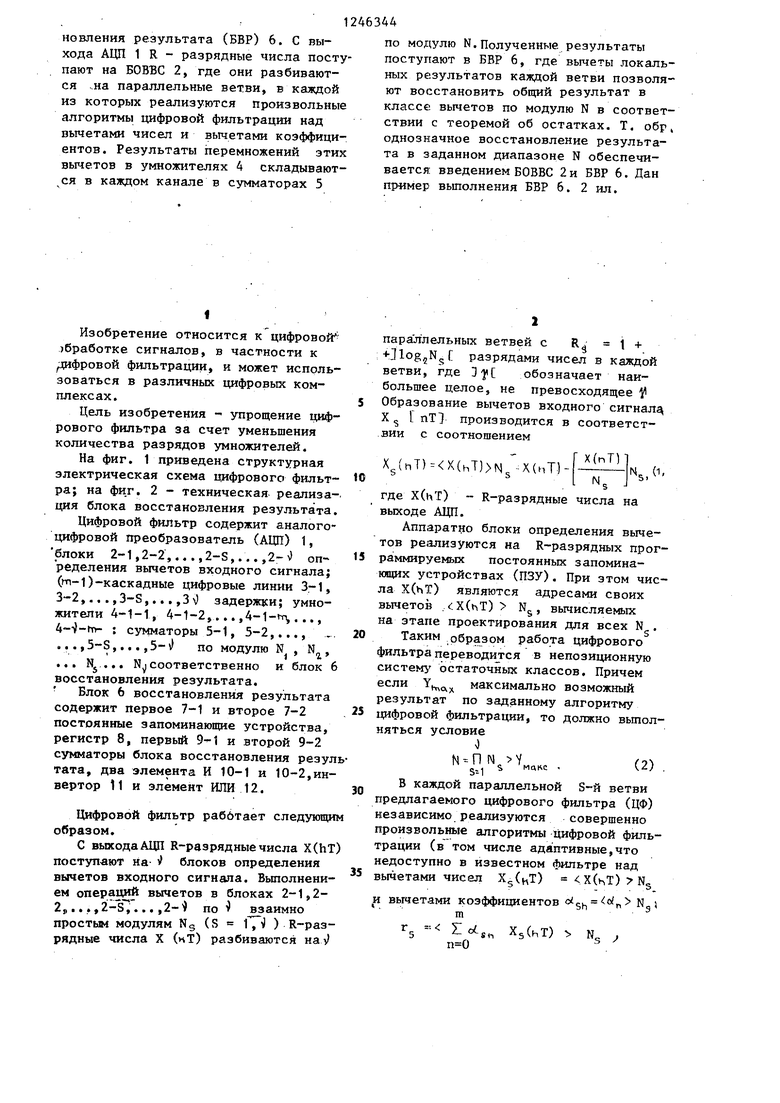

новления результата (БВР) 6. С выхода АЦП 1 R - разрядные числа поступают на БОВВС 2, где они разбиваются .на параллельные ветви, в каждой из которых реализуются произвольные алгоритмы цифровой фильтрации над вычетами чисел и вьгчетамн коэффициентов. Результаты перемножений этих вычетов в умножителях 4 складываются в каждом канале в сумматорах 5

Изобретение относится к цифровой обработке сигналов, в частности к р1фровой фильтрации, и может использоваться в различных цифровьпс комплексах.

Цель изобретения - упрощение цифрового фильтра за счет уменьшения количества разрядов умножителей.

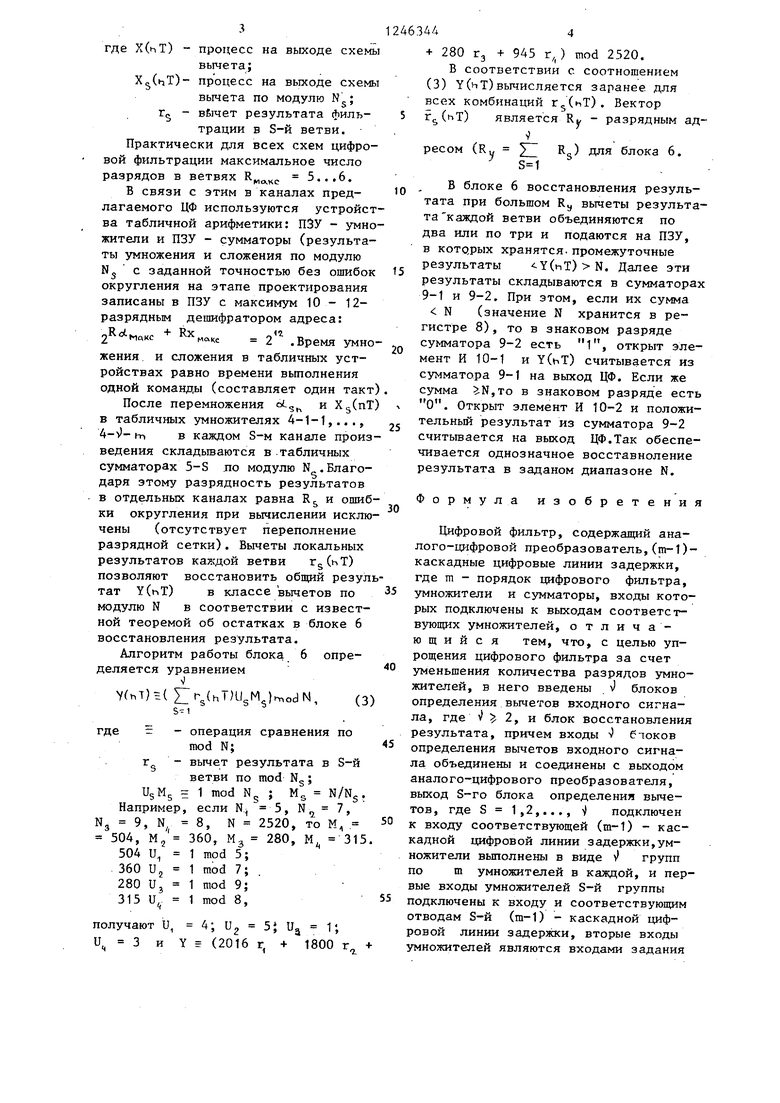

На фиг. 1 приведена структурная электрическая схема цифрового фильт- ра; на . 2 - техническая реализация блока восстановления результата.

Цифровой фильтр содержит аналого- цифровой преобразователь (АЦП) 1,

блоки 2-1,2-2,.. .,2-S,... ,2-1) on- ределения вычетов входного сигнала; (т-1)-каскадные цифровые линии 3-1, ,... ,3-S,... ,3 ) задержки; умножители 4-1-1, 4-1-2,... ,4-1-tT(,..., 4-т1-1тг- : сумматоры 5-1, 5-2,..., .. .. . ,5-S,... ,5- по модулю N , N , ... N ,. Ngсоответственно и блок 6 восстановления результата. Блок 6 восстановления результата содержит первое 7-1 и второе 7-2 постоянные запоминающие устройства, регистр 8, первый и второй 9-2 сумматоры блока восстановления резултата, два элемента И 10-1 и 10-2,инвертор 11 и элемент ИЛИ 12.

Цифровой фильтр раббтает следующим образом.

С выхода АЦП R-разрядные числа X(hT) пocтyп aют на- V блоков определения вычетов входного сигнала. Выполнением операций вычетов в блоках 2-1,2- 2 S...2- sT..., 2- по взаимно простым модулям Ng (S 1, i) ) R-разрядные числа X (нТ) разбиваются HaV

46344

по модулю N. Полученные результаты поступают в БВР 6, где вычеты локальных результатов каждой ветви позволяют восстановить общий результат в классе вычетов по модулю N в соответствии с теоремой об остатках. Т. обр, однозначное восстановление результата в заданном диапазоне N обеспечивается: введением БОВВС 2 и БВР 6. Дан пример выполнения БВР 6. 2 ил.

параллельных ветвей с R 1 + - -Jlog Nj. С разрядами чисел в каждой ветви, где 3 обозначает наибольшее целое, не превосходящее Образование вычетов входного сигналу X I пТ1 производится в соответствии с соотношением

X fhT)(hT)N, x(hT.) {1,

S5 N5 J

где XdiT) - R-разрядные числа на выходе АЦП.

Аппаратно блоки определения вычетов реализуются на R-разрядных программируемых постоянных запоминающих устройствах (ПЗУ). При этом числа X(hT) являются адресами своих вычетов ,:X(hT) Ng, вычисляемых на этапе проектирования для всех N

Таким образом работа цифрового фильтра переводится в непозиционную систему остаточных классов. Причем если Y, максимально возможный результат по заданному алгоритму цифровой фильтрации, то должно вьтол- няться условие

s

Н-П N V

S-1 S

(2)

В каждой параллельной S-й ветви предлагаемого цифрового фильтра (ЦФ) независимо реализуются совершенно произвольные алгоритмы Цифровой фильтрации (в том числе адаптивные,что недоступно в известном фильтре над вычетами чисел Хд(нТ) Х(ьТ) Ng

и вычетами коэффициентов sh 3

m

Гд - TcL, Хз(нТ) Ng ,

где X(hT) - процесс на вьгходе схемы

вычета; Xo(hT)- процесс на выходе схемы

вычета по модулю г - вб1чет результата фильтрации в S-й ветви. Практически для всех схем цифровой фильтрации максимальное число разрядов в ветвях . 5...6.

В связи с этим в каналах предлагаемого ЦФ используются устройства табличной арифметики: ПЗУ - умножители и ПЗУ - сумматоры (результаты умножения и сложения по модулю NJ с заданной точностью без ошибок округления на этапе проектирования записаны в ПЗУ с максимум 10 - 12- разрядным дешифратором адреса:

р -j J. IRv12.

2 .Время умножения . и сложения в табличных устройствах равно времени вьшолнения одной команды (составляет один такт) После перемножения о -д и Xg(nT) в табличных умножителях А-1-1,..., hi в каждом S-M канале произведения складьшаются в табличных сумматорах 5-S ло модулю N .Благодаря этому разрядность результатов в отдельных каналах равна R и ошибки округления при вычислении исключены (отсутствует переполнение разрядной сетки). Вычеты локальных

результатов каждой ветви rg(hT) позволяют восстановить общий результат У(мТ) в классе вычетов по модулю N в соответствии с известной теоремой об остатках в блоке 6 восстановления результата.

Алгоритм работы блока 6 определяется уравнением V

V(hT)( г (hT)U ,

(3)

где

- - операция сравнения по

mod N; г - вычет результата в S-й

ветви по mod Ng; UgMg 1 mod Ng ; Mg N/N5. Например, если N 5, N 7, N3 9, N, 8, N 2520, то M, . 504, N2 360, Mg 280, M 315. 504 U, 1 mod 5; 360 Uj 1 mod 7; . 280 Uj 1 mod 9; 315 U 1 mod 8,

получают и, 4; и 2 5{ иj 1;

U 3 и Y (2016 r + 1800 r +

(3)

124634Д4

+ 280 Гз + 945 г,,) mod 2520.

В соответствии с соотношением (3) Y(hТ)вычисляется заранее для всех комбинаций ) . Вектор 5 Гс(ьТ) является Ry - разрядным V

ресом (Ry

Rg) для блока 6.

, В блоке 6 восстановления результата при большом Ry вычеты результата каждой ветви объединяются по два или по три и подаются на ПЗУ, в кото,рых хранятся, промежуточные

результаты Y(nT) N. Далее эти результаты складываются в сумматорах 9-1 и 9-2, При этом, если их сумма N (значение N хранится в регистре 8), то в знаковом разряде сумматора 9-2 есть 1, открыт элемент И 10-1 и Y(hT) считывается из сумматора 9-1 на выход ЦФ. Если же сумма N,To в знаковом разряде есть О. Открыт элемент И 10-2 и положительный результат из сумматора 9-2 считьгоается на выход ЦФ.Так обеспечивается однозначное восставноление результата в заданом диапазоне N.

30

Формула изобретения

Цифровой фильтр, содержащий аналого-цифровой преобразователь, (ni-1)- каскадные цифровые линии задержки, где m - порядок цифрового фильтра,

35 умножители и сумматоры, входы которых подключены к вьосодам соответствующих умножителей, отличающийся тем, что, с целью упрощения цифрового фильтра за счет

уменьшения количества разрядов умножителей, в него введены . N) блоков определения вычетов входного сигнала, где t 2, и блок восстановления результата, причем входы ч) блоков определения вычетов входного сигнала объединены и соединены с выходом аналого-цифрового преобразователя, выход S-ro блока определения вычетов, где S 1,2,..., V подключен

к входу соответствующей (т-1) - каскадной цифровой линии задержки,умножители выполнены в виде групп по m умножителей в каждой, и первые входы умножителей S-й группы

45

55

подключены к входу и соответствующим отводам S-и (т-1) - каскадной цифровой линии задержки, вторые входы умножителей являются входами задания

512463446

значений вычетов коэффициентоз цифро- блока восстановления результата, вого фильтра, а выходы сумматоров соединены с соответствующими входами

,выход которого является выходом ц рового фильтра.

блока восстановления результата,

,выход которого является выходом цифрового фильтра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1985 |

|

SU1356214A1 |

| Цифровой фильтр | 1988 |

|

SU1617635A1 |

| Систолический процессор для вычисления полиномиальных функций | 1988 |

|

SU1608689A1 |

| ЦИФРОВОЙ АНАЛИЗАТОР СПЕКТРА | 1989 |

|

RU2018144C1 |

| Система надежного облачного хранения с регулируемой избыточностью данных | 2021 |

|

RU2782681C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОЗИЦИОННЫХ СУММАТОРОВ ПО МОДУЛЮ | 2002 |

|

RU2231823C2 |

| Цифровой демодулятор сигналов с двухуровневой амплитудно-фазовой манипуляцией и относительной оценкой амплитуды символа | 2022 |

|

RU2790140C1 |

| МОДУЛЯРНЫЙ ПОЛИНОМИАЛЬНЫЙ ВЫЧИСЛИТЕЛЬ СИСТЕМ БУЛЕВЫХ ФУНКЦИЙ | 2015 |

|

RU2586575C1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ СДВИГА ФАЗ ГАРМОНИЧЕСКИХ СИГНАЛОВ | 2020 |

|

RU2751020C1 |

| Цифровой фильтр | 1979 |

|

SU898592A1 |

Изобретение может быть использовано при цифровой обработке сигналов. Цель изобретения - упрощение устройства за счет уменьшения количества разрядов умножителей.Устройство содержит аналого-цифровой преобразователь (АЦП) 1, блоки определения вычетов входного сигнала (БОВВС) 2, (п-1)-каскадные цифровые линии задержки 3, умножители 4, сумматоры 5 по модулю N и блок восста(Л ) I S-S & со 4 3-) , .1 5-У Ю

У(пТ}

Фиг, 2

Со ставитель С.Музьщ к Редактор Н.Бобкова Техред Л.Олейник Корректор М.Пожо

Заказ 4020/54 Тираж 816 Подписное ВНИШШ Государственного комитета СССР

по делам изобретений и открыт:нй 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| СПОСОБ СТАБИЛИЗАЦИИ ВИТАМИНСОДЕРЖАЩИХ ЖИРОВ И МАСЕЛ К ОКИСЛЕНИЮ | 1992 |

|

RU2032722C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| СПОСОБ СТИМУЛЯЦИИ РЕПАРАТИВНЫХ И ТРОФИЧЕСКИХ ПРОЦЕССОВ В ТКАНЯХ ОРГАНИЗМА | 1994 |

|

RU2095067C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-07-23—Публикация

1984-12-07—Подача