Изобретение относится к вычислительной технике и может быть использовано в информационно-измерительных системах и системах управления.

Целью изобретения является повышение точности спектрального анализа.

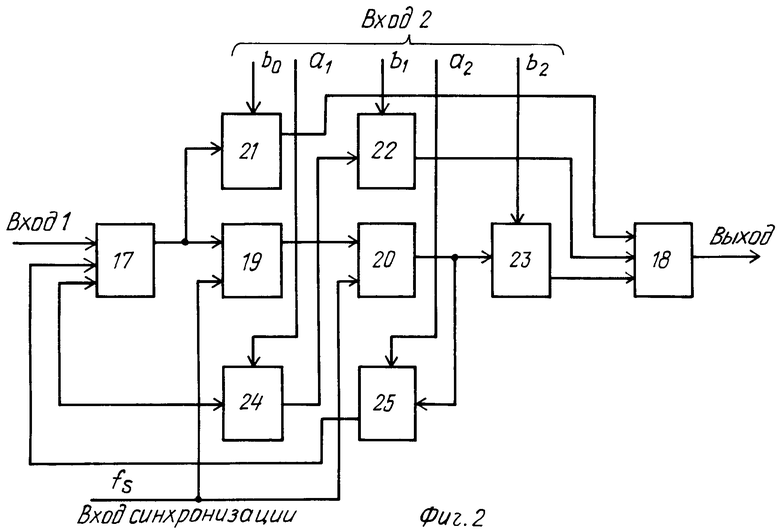

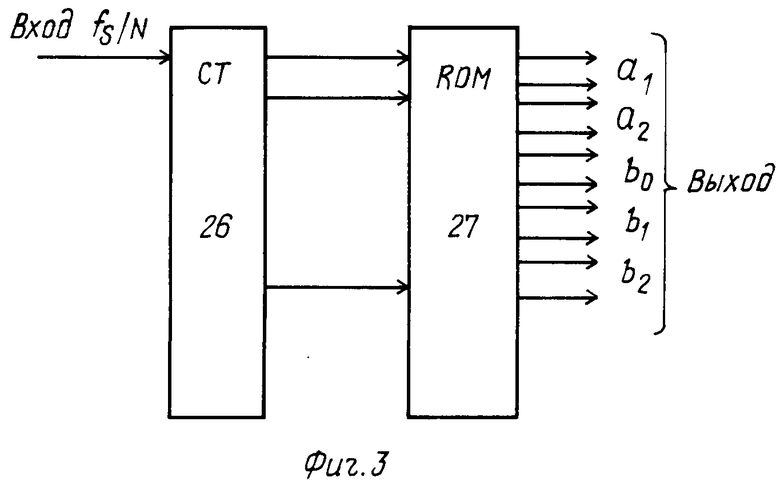

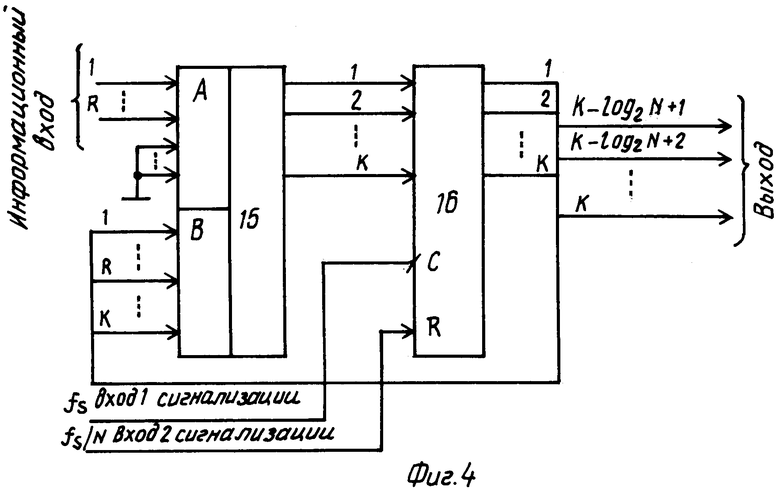

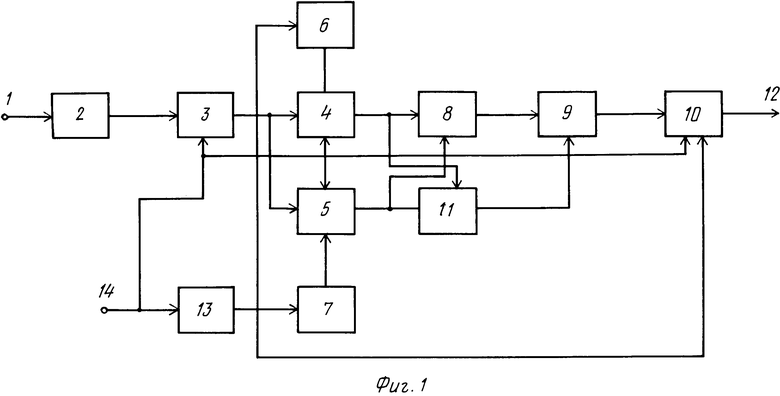

На фиг.1 показана структурная схема предлагаемого цифрового анализатора спектра; на фиг.2 - пример реализации цифрового фильтра; на фиг.3 - пример реализации блока изменения частоты среза; на фиг..4 - блок усреднения.

Цифровой анализатор спектра включает вход аналогового сигнала 1, аналоговый фильтр 2 нижних частот (ФНЧ), аналогово-цифровой преобразователь 3 (АЦП), цифровые фильтры 4, 5 (ЦФ), блоки 6, 7 изменения частот среза, блок 8 вычитания, умножитель 9, блок 10 усреднения, сумматор 11, выход устройства 12, блок 13 синхронизации, вход синхронизации 14, блок усреднения 10 включает комбинационный К-разрядный сумматор 15 и К-разрядный регистр 16.

В состав ЦФ (фиг.2) входят сумматоры 17, 18, регистры 19, 20 задержки, умножители 21, 22, 23, 24, 25. Для синхронизации работы таких ЦФ нужна частота дискретизации fs = 1/ Δ t, с которой на вход фильтра поступают отсчеты входного сигнала x(n) и происходит запись промежуточных данных в регистры 19 и 20 задержки, а на выход ЦФ поступают отсчеты отфильтрованного сигнала x1(n). На второй информационный вход ЦФ поступает набор коэффициентов его умножителей. В состав блоков изменения частоты срезa (БИЧС) 6, 7 (фиг.3) входят счетчик 26, на вход синхронизации которого поступает частота fs/N, выход счетчика заведен на адресные входы постоянных запоминающих устройств (ПЗУ) 27, а первая, вторая, третья, четвертая и пятая группы выходов ПЗУ задают коэффициенты цифровых фильтров 4 и 5 соответственно a1' , a2' , b0' , b1' - b2' и a1'' , a2'' , b0'' , b1'' , b2'' и являются выходом блока. Коэффициент пересчета счетчика равен числу подлежащих анализу участков спектра и определяет количество наборов коэффициентов ЦФ. При подаче на вход счетчика частоты fs/N изменяется состояние счетчика и адрес ПЗУ, поэтому смена наборов коэффициентов на выходе БИЧС происходит один раз за N периодов дискретизации Δ t.

Функция блока синхронизации предложенного анализатора спектра заключается в делении входной частоты дискретизации fs на N (где N - параметр усреднения). Такой блок может быть реализован на микросхемах счетчиков, например, 133ИЕ7.

Цифровой анализатор спектра работает следующим образом.

Аналоговый сигнал с входа 1 устройства проходит через аналоговый ФНЧ 2 для ограничения высокочастотных составляющих спектра и устранения возможных ошибок наложения. На второй вход синхронизации блока 10 усреднения, который является входом установки нуля регистра 16 и на счетные входы счетчиков 26 БИЧС поступает первый импульс синхрочастоты fs/N. При этом происходит обнуление регистра 16 блока усреднения 10 и из ПЗУ 27 блоков 6, 7 изменения частот среза значения наборов коэффициентов a1' , a2' , b0' , b1', b2' и a1' , a2'' , b0'' , b1'' , b2'' поступают на вторые информационные входы коэффициентов цифровых фильтров 4 и 5. Указанные наборы коэффициентов соответствуют анализируемой в данный момент полосе частот входного сигнала. Со входа синхронизации 14 устройства частота дискретизации fs поступает на входы синхронизации АЦП 3, регистров 19, 20, ЦФ 4 и 5, первый вход синхронизации регистра 16 блока 10 усреднения. С выхода АЦП отсчеты сигнала x(n), где n - текущий номер отсчета, поступают на первые информационные входы ЦФ 4 и 5. При этом ЦФ 4 и 5 имеют частоты среза f1 и f2, что определяется соответствующими наборами коэффициентов. С выхода ЦФ 4 сигнал x1(n) поступает на первый вход сумматора 11 и прямой вход блока 8 вычитания, а с выхода ЦФ 5 сигнал x2(n) поступает на второй вход сумматора 11 и инверсный вход блока 8 вычитания. Сигналы с выходов блока 8 вычитания и сумматора 11 поступают на первый и второй входы умножителя 9, с выхода которого их произведение поступает на информационный вход блока 10 усреднения, где проходит на первый вход сумматора 15, при этом на второй вход сумматора 15 поступает значение числа, хранящегося в регистре 16, а на выходе сумматора 15 формируется сумма этих чисел. При поступлении нового синхроимпульса частоты fs указанная сумма фиксируется в регистре 16, а с выхода АЦП поступает новый отсчет сигнала x(n+1) и алгоритм обработки одного отсчета повторяется. Через N периодов Δ t в регистре 16 накапливается сумма из N значений y1(n), старшие К разряды которой могут быть считаны с выхода 12 анализатора спектра (отбрасывание младших log2 N разрядов соответствует усреднению мощности сигнала по N). В итоге формируется значение средней мощности сигнала, лежащего в полосе частот Δ f1 = f1-f2. Далее с приходом нового импульса частоты fs/N с выхода блока 13 синхронизации, происходит сброс регистра 16 блока 10 усреднения, увеличение на единицу значений счетчиков 26 блоков 6, 7 изменения частот cреза, выборка новых наборов коэффициентов цифровых фильтров из ПЗУ, соответствующих новым значениям частот среза f3 и f4 и алгоритм работы анализатора спектра повторяется для новой полосы частот Δ f2 = f3 - f4.

В результате последовательной настройки анализатора на различные полосы частот формируется спектр мощности сигнала с высокой точностью.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ взвешивания движущихся объектов | 1990 |

|

SU1800269A1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ РАЗБРОСА ПАРАМЕТРОВ ФОТОЧУВСТВИТЕЛЬНЫХ ЭЛЕМЕНТОВ МНОГОЭЛЕМЕНТНОГО ПРИЕМНИКА | 1992 |

|

RU2025905C1 |

| СПОСОБ КОМПЕНСАЦИИ РАЗБРОСА ПАРАМЕТРОВ ФОТОЧУВСТВИТЕЛЬНЫХ ЭЛЕМЕНТОВ ФОТОПРИЕМНОГО УСТРОЙСТВА | 1992 |

|

RU2105427C1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| МОНОИМПУЛЬСНАЯ РЛС | 2004 |

|

RU2267137C1 |

| МАЛОГАБАРИТНЫЙ РАДИОЛОКАТОР ТРАНСПОРТНОГО СРЕДСТВА | 1997 |

|

RU2117964C1 |

| СПОСОБ ИЗМЕРЕНИЯ ВЫСОТЫ МОРСКИХ ВОЛН С ЛЕТАТЕЛЬНОГО АППАРАТА НА ПЛАВУ | 1996 |

|

RU2112925C1 |

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2008 |

|

RU2393641C1 |

| Цифровой рекурсивный фильтр | 1988 |

|

SU1578720A1 |

| Аналого-цифровой преобразователь с цифровой коррекцией | 1982 |

|

SU1069157A1 |

Изобретение относится к вычислительной технике и может быть использовано в информационно-измерительных системах и системах управления. Цифровой анализатор спектра состоит из входа устройства, аналогового фильтра 2 нижних частот, аналого-цифрового преобразователя 3, двух цифровых фильтров 4,5 двух блоков 6,7 изменения частот среза блока 8 вычитания, сумматора 11, умножителя 9, блока 10 усреднения, выхода 12 устройства и блока 13 синхронизации. 3 ил.

ЦИФРОВОЙ АНАЛИЗАТОР СПЕКТРА, содержащий последовательно соединенные фильтр нижних частот и аналого-цифровой преобразователь, выход которого соединен с входами первого и второго цифровых фильтров, первый и второй блоки изменения частоты среза цифровых фильтров, последовательно соединенные, блок вычитания, умножитель и блок усреднения, блок синхронизации, причем вход аналогового фильтра нижних частот соединен с входом устройства, вторые информационные входы цифровых фильтров подключены соответственно к выходам первого и второго блоков изменения частоты среза, выход первого цифрового фильтра соединен с прямым входом блока вычитания, выход второго цифрового фильтра соединен с инверсным входом блока вычитания, выход блока усреднения соединен с выходом устройства, вход синхронизации устройства соединен с входами синхронизации аналого-цифрового преобразователя, первого и второго цифровых фильтров, входом блока синхронизации и первым входом синхронизации блока усреднения, а выход блока синхронизации соединен с входами первого и второго блоков изменения частот среза и вторым входом синхронизации блока усреднения, отличающийся тем, что, с целью повышения точности спектрального анализа, в него введен сумматор, первый вход которого соединен с выходом первого цифрового фильтра и вторым входом блока вычитания, второй вход соединен с выходом второго цифрового фильтра, а выход подключен к второму входу умножителя.

| Мизин И.А., Матвеев А.А., Цифровые фильтры, М.: Связь, 1979, с.190-191. |

Авторы

Даты

1994-08-15—Публикация

1989-07-24—Подача