f

Изобретение относится к вычислительной технике и предназначено для получения импульсных сигналов, расположенных симметрично входным в заданном интервале при сохранении их длительности.

Цель изобретения - расширение

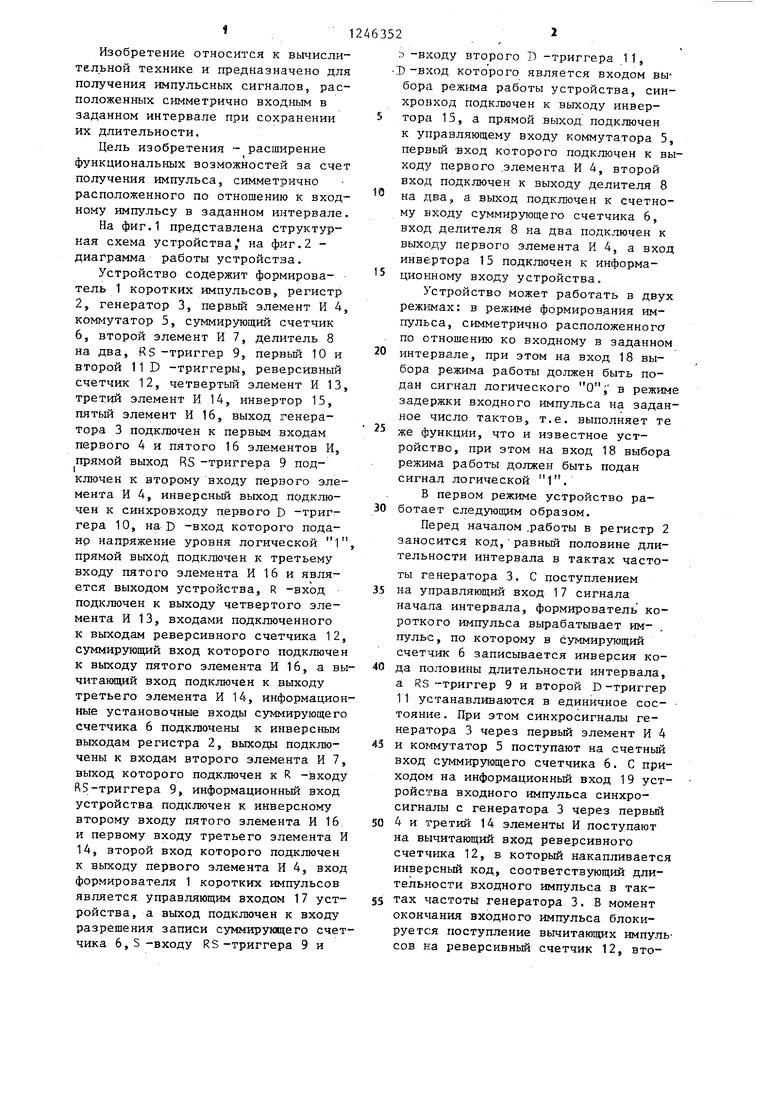

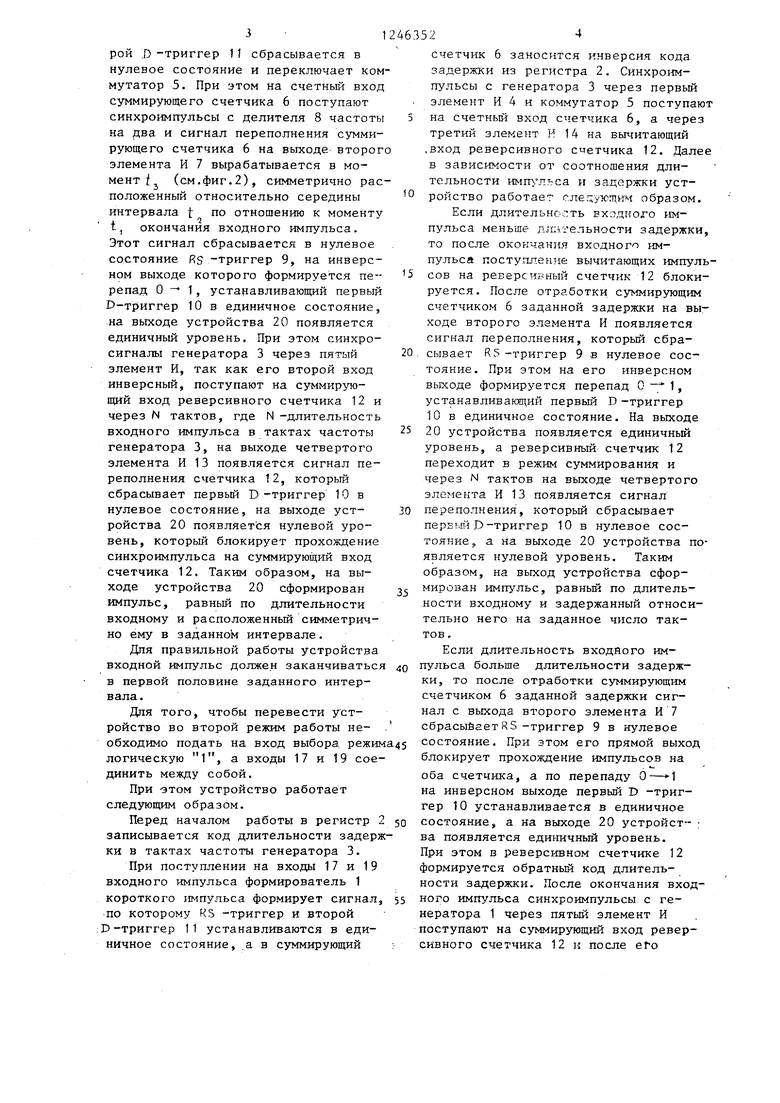

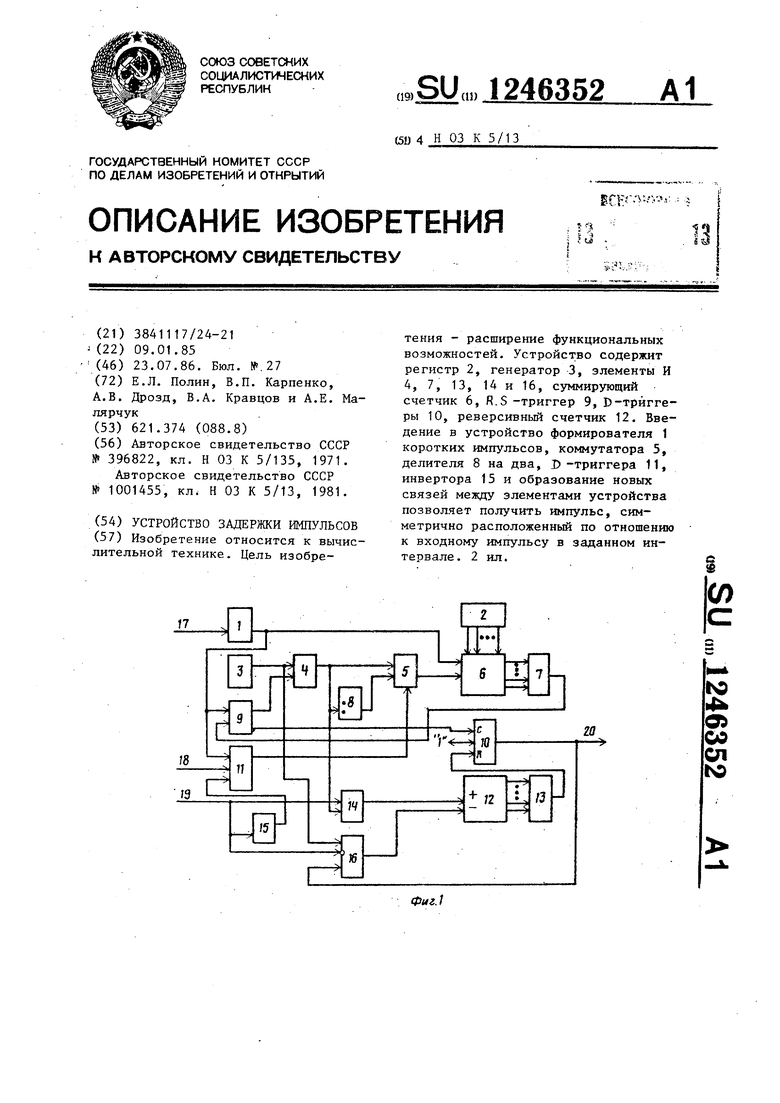

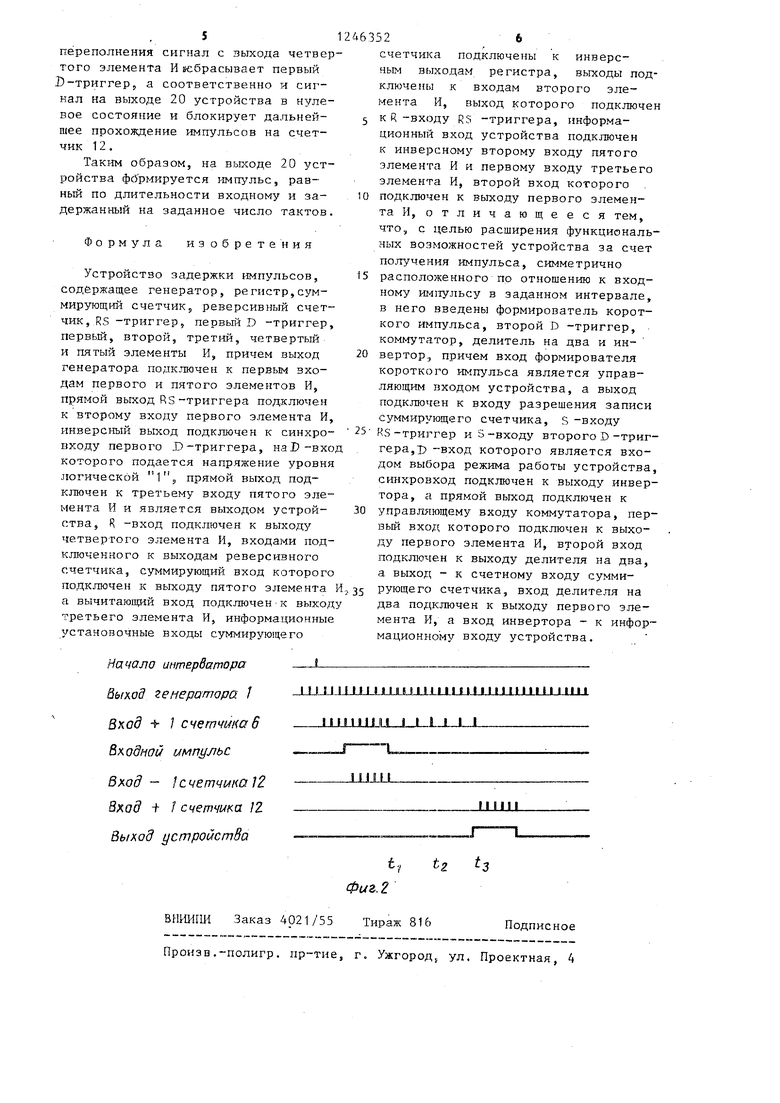

функциональных возможностей за счет получения импульса, симметрично расположенного по отношению к входному импульсу в заданном интервале. На фиг.1 представлена структурная схема устройства, на фиг.2 - диаграмма работы устройства.

Устройство содержит формирователь 1 коротких импульсов, регистр 2, генератор 3, первый элемент И 4, коммутатор 5, суммирующий счетчик 6, второй элемент И 7, делитель 8 на два, RS -триггер 9, первый 10 и второй 11 D -триггеры, реверсивный счетчик 12, четвертый элемент И 13, третий элемент И 14, инвертор 15, пятый элемент И 16, выход генератора 3 подключен к первым входам первого 4 и пятого 16 элементов И, прямой выход RS -триггера 9 подключен к второму входу первого элемента И 4, инверсный выход подключен к синхровходу первого D -триггера 10, на) -вход которого подано напряжение уровня логической 1 прямой выход подключен к третьему входу пятого элемента И 16 и является выходом устройства, R -вход подключен к вьпсоду четвертого элемента И 13, входами подключенного к выходам реверсивного счетчика 12, суммирующий вход которого подключен к выходу пятого элемента И 16, а вычитающий вход подключен к выходу третьего элемента И 14, информационные установочные входы суммирующего счетчика 6 подключены к инверсным выходам регистра 2, выходы подключены к входам второго элемента И 7, выход которого подключен к R -входу RS-триггера 9, информационный вход устройства подключен к инверсному второму входу пятого элемента И 16 и первому входу третьего элемента И 14, второй вход которого подключен к выходу первого элемента И 4, вход формирователя 1 коротких импульсов является управляющим входом 17 устройства, а выход подключен к входу разрешения записи cyммиpyюп eго счетчика 6,5 -входу RS -триггера 9 и

, 15

20

25

246352;

:5 -входу второго D -триггера 1 1, D -вход которого является входом выбора реж1- ма работы устройства, син- хровход подключен к выходу инвертора 15, а прямой выход подключен к управляющему входу коммутатора 5, первый -вход которого подключен к выходу первого .элемента И 4, второй вход подключен к выходу делителя 8 на два,, а. выход подключен к счетному входу суммирующего счетчика 6, вход делителя 8 на два подключен к выходу первого элемента И 4, а вход инвертора 15 подключен к информа- ционноьгу входу устройства.

Устройство может работать в двух режимах: в режиме формирования импульса, симметрично расположенного по отношению ко входному в заданном интервале, при этом на вход 18 выбора режима работы должен быть подан сигнал логического в режиме задержк:и входного импульса на заданное число тактов, т.е. выполняет те же функции, что и известное устройство, при этом на вход 18 выбора режима работы должен быть подан сигнал логической 1.

В первом режиме устройство работает следующим образом.

Перед началом .работы в регистр 2 заносится код, равный половине длительности интервала в тактах частоты генератора 3. С поступлением на управляющий вход 17 сигнала начала интервала, формирователь короткого импульса вырабатывает импульс, по которому в суммирующий счетчик 6 записывается инверсия кода половины длительности интервала, а RS -триггер 9 и второй D-триггер 11 устанавливаются в единичное сое- тояние. При этом синхросигналы генератора 3 через первый элемент И 4 и коммутатор 5 поступают на счетньй вход суммирующего счетчика 6. С приходом на информационный вход 19 устройства входного импульса синхросигналы с генератора 3 через первьй 4 и третий 14 элементы И поступают на вычитающий вход реверсивного счетчика 12, в который накапливается инверсньй код, соответствующий длительности входного импульса в тактах частоты генератора 3. В момент окончания входного импульса блокируется поступление вычитающих импуль сов в а реверсивный счетчик 12, вто30

35

40

43

SO

55

рой ;D -триггер 11 сбрасывается в нулевое состояние и переключает коммутатор 5. При этом на счетный вход суммирующего счетчика 6 поступают синхроимпульсы с делителя 8 частоты на два и сигнал переполнения суммирующего счетчика 6 на выходе второго элемента И 7 вырабатывается в момент f (см,фиг.2), симметрично расположенный относительно середины интервала t по отношению к моменту t, окончания входного импульса. Этот сигнал сбрасывается в нулевое

состояние KS -триггер 9, на инверсном выходе которого формируется перепад О - 1, устанавливающий первый D-триггер 10 в единичное состояние, на выходе устройства 20 появляется единичный уровень. При этом синхросигналы генератора 3 через пятый элемент И, так как его второй вход инверсный, поступают на суммирующий вход реверсивного счетчика 12 и через N тактов, где N -длительность входного импульса в тактах частоты генератора 3, на выходе четвертого элемента И 13 появляется сигнал переполнения счетчика 12, который сбрасывает первый D-триггер 10 в нулевое состояние, на выходе устройства 20 появляется нулевой уровень, который блокирует прохождение синхроимпульса на суммирующий вход счетчика 12. Таким образом, на выходе устройства 20 сформирован импульс, равньй по длительности входному и расположенный симметрично ему в заданном интервале.

Для правильной работы устройства

входной импульс должен заканчиваться 40 пульса больше длительности задержв первой половине заданного интервала.

Для того, чтобы перевести устройство во второй режим работы неки, то после отработки суммирующ1-1м счетчиком 6 заданной задержки сигнал с выхода второго элемента И 7 сбрасыЁает RS-триггер 9 в нулевое

обходимо подать на вход выбора режима45 состояние. При этом его прямой выход

логическую 1, а входы 17 и 19 соеблокирует прохождение импульсов на оба счетчика, а по перепаду на инверсном выходе первый D -триггер 10 устанавливается в единичное

динить между собой.

При этом устройство работает следующим образом.

Перед началом работы в регистр 2 50 состояние, а на выходе 20 устройст- записывается код длительности задерж- ва появляется единичный уровень, ки в тактах частоты генератора 3. При этом в реверсивном счетчике 12

При поступлении на входы 17 и 19 формируется обратный код длитель- входного импульса формирователь 1 ности задержки. После окончания вход- короткого гмпульса формирует сигнал, 55 ного импульса синхроимпульсы с ге- по которому KS -триггер и второй :D-триггер 11 устанавливаются в единичное состояние, .а в суммирующий :

нератора 1 через пятый элемент И поступают на суммирующий вход реверсивного счетчика 12 и после его

10

246352счетчик 6 заносится инверсия кода задержки из регистра 2. Синхроимпульсы с генератора 3 через первый элемент И 4 и коммутатор 5 поступают 5 на счетный вход счетчика 6, а через третий элемент И 14 на ВЕ)1читающий .вход реверсивного счетчика 12. Далее в зависимости от соотношения длительности импл л са и задержки устройство работает елецутеш.им образом.

Если длительность входного импульса меньше длительности задержки, то после окончания входного импульса поступление вычитающих импуль15 сов на реверсивный счетчик 12 блокируется. После отработки суммирующим счетчиком 6 заданной задержки на выходе второго элемента И появляется сигнал переполнения, который сбра20, сывает R 5-триггер 9 в нулевое состояние. При этом на его инверсном выходе формируется перепад О - 1, устанавливающий первый D-триггер 10 в единичное состояние. На выходе

25 20 устройства появляется единичный уровень, а реверсивный счетчик 12 переходит в режим суммирования и через N тактов на выходе четвертого элемента И 13 появляется сигнал

30 переполнения, который сбрасывает первьш D-триггер 10 в нулевое состояние ,, а на выходе 20 устройства появляется нулевой уровень. Таким образом, на выход устройства сфорj, мирован импульс, равный по длительности входному и задержанный относительно него на заданное число тактов .

Если длительность входного имки, то после отработки суммирующ1-1м счетчиком 6 заданной задержки сигнал с выхода второго элемента И 7 сбрасыЁает RS-триггер 9 в нулевое

блокирует прохождение импульсов на оба счетчика, а по перепаду на инверсном выходе первый D -триггер 10 устанавливается в единичное

формируется обратный код длитель- ности задержки. После окончания вход- ного импульса синхроимпульсы с ге-

нератора 1 через пятый элемент И поступают на суммирующий вход реверсивного счетчика 12 и после его

5

переполнения сигнал с выхода четветого элемента И (сбрасывает первый D-Tpnrrep, а соответственно и сигнал на выходе 20 устройства в нулевое состояние и блокирует дальнейшее прохождение импульсов на счетчик 12,

Таким образом, на выходе 20 устройства формируется им пульс, равный по длительности входному и задержанный на заданное число тактов

Формула изобретения

Устройство задержки импульсов, содержащее генератор, регистр,суммирующий счетчик5 реверсивный счетчик, RS -триггер, первый D -триггер, первый, второй, третий, четвертый и пятый элементы И, причем выход генератора подключен к первым входам первого и пятого элементов И, прямой выход RS-триггера подключен к второму входу первого элемента И, инверсный выход подключен к синхро- входу первого JD-триггера, на)-вхо которого подается напряжение уровня логической I, прямой выход подключен к третьему входу пятого элемента И и является выходом устройства, R -вход подключен к выходз четвертого элемента И, входами подключенного к выходам реверсивного счетчика, суммирующий вход которого

подключен к выходу пятого элемента И, 35рующего счетчика, вход делителя на

а вычитающий вход подключенк выходудва подключен к выходу первого элетретьего элемента И, информационныемента И, а вход инвертора - к инфорустановочные входы суммирующегомадионному входу устройства.

счетчика подключены к инверсным ВЕ,1ходам регистра, выходы подключены к входам второго элемента И, выход которого подключен

кR -входу RS -триггера, информа- дионный вход устройства подключен к инверсному второму входу пятого элемента И и первому входу третьего элемента И, второй вход которого подключен к выходу первого элемента И, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет получения импульса, симметрично

расположенного по отношению к входному импульсу в заданном интервале, в него введены формирователь короткого ш пульса, второй D -триггер, коммутатор, делитель на два и инвертор., причем вход формирователя короткого импульса является управляющим входом устройства, а выход подключен к входу разрешения записи суммирующего счетчика, S -входу

К5-трИ1тер и S-входу второго D-триггера, и -вход которого является входом выбора режима работы устройства, синхровход подключен к выходу инвертора, а прямой выход подключен к

управляющему входу коммутатора, первый вход которого подключен к выходу первого элемента И, второй вход подключен к выходу делителя на два, а выход - к счетному входу суммиНачало интерватора Выкод генератора / Вкод 1 счетчика 6 В)(одной импульс

Вмд - 1счетч1 ка12 Вкод -i- / счетчика /2 Вы код устройства

jJJJJjm-LJLU-iJJJ.i-IJ.i-0 11 И И И I М I I И И llillllJLLLJ L L LJ-J

ПИП

ПИП

ВНШШ Заказ 4021/55 Тираж 816 Подписное Пронэв.-полигр. пр-тие, г, Ужгород ул. Проектная, 4

t, tz t3

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регулирования расхода | 1984 |

|

SU1171759A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Преобразователь код - широтно-импульсный сигнал | 1990 |

|

SU1793545A1 |

| Устройство для измерения отклонения сопротивления от заданного значения | 1986 |

|

SU1536322A1 |

| Устройство привязи к сигналам точного времени | 1987 |

|

SU1522146A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Устройство поэлементной синхронизации | 1987 |

|

SU1517142A1 |

| Устройство задержки прямоугольных импульсов | 1981 |

|

SU1003321A1 |

| Устройство для предварительной фильтрации входных сигналов узкополосных цифровых фильтров | 1990 |

|

SU1739481A1 |

Изобретение относится к вычислительной технике. Цель изобретения - расширение функциональных возможностей. Устройство содержит регистр 2, генератор 3, элементы И 4, 7, 13, 14 и 16, суммирующий счетчик 6, R.S -триггер 9, D-триггеры 10, реверсивный счетчик 12. Введение в устройство формирователя 1 коротких импульсов, коммутатора 5, делителя 8 на два, D -триггера 11, инвертора 15 и образование новых связей между элементами устройства позволяет получить импульс, симметрично расположенный по отношению к входному импульсу в заданном интервале. 2 ил. 7 (Л N9 1 Од СО СП N9 фиг. /

| 0 |

|

SU396822A1 | |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство задержки импульсов | 1981 |

|

SU1001455A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-07-23—Публикация

1985-01-09—Подача