Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Целью изобретения является повышение надежности функционирования счетчика.

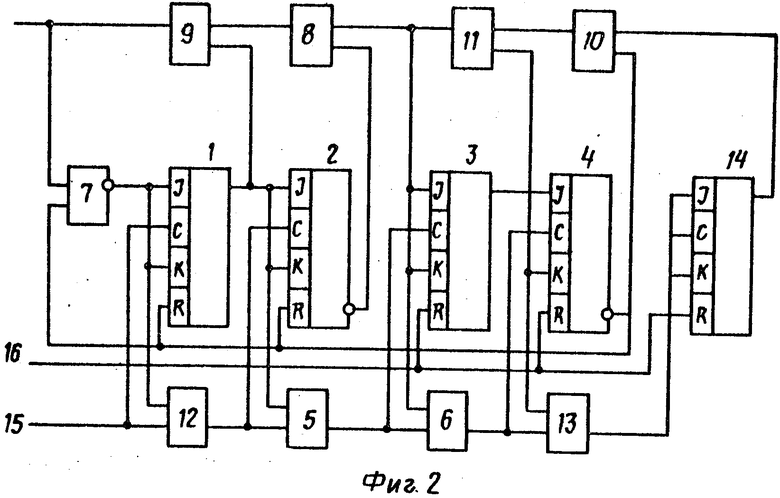

На фиг. 1 и 2 представлены соответственно первый и второй варианты предлагаемого счетчика.

Счетчик, показанный на фиг. 1, содержит первый 1, второй 2, третий 3 и четвертый 4 IK-триггеры, первый 5 и второй 6 логические элементы ИЛИ, третий логический элемент 7 ИЛИ-НЕ, четвертый 8, пятый 9, шестой 10 и седьмой 11 логические элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, восьмой 12 и девятый 13 логические элементы ИЛИ и пятый триггер 14.

Входная шина 15 соединена со счетным входом триггера 1 и первым входом элемента ИЛИ 12, второй вход которого соединен с I и К-входами триггера 1 и выходом элемента ИЛИ 7. Выход элемента ИЛИ 12 соединен со счетным входом триггера 2 и вторым входом элемента ИЛИ 5, первый вход которого соединен с выходом триггера 1, I и K-входами триггера 2 и первым входом элемента ИЛИ 13. Второй вход элемента ИЛИ 13 соединен с инверсным выходом триггера 2, а выход элемента ИЛИ 13 - с R-входом триггера 3. Выход элемента ИЛИ 5 соединен с С-входами триггеров 3 и 4 и с первым входом элемента ИЛИ 6, второй вход которого соединен с прямым выходом триггера 2 и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8, а выход - с I, С и К-входами триггера 14. Прямой выход триггера 14 соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10, второй вход которого соединен с инверсным выходом триггера 4, а выход - с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11. Второй вход элемента 11 соединен с прямым выходом триггера 3 и первым входом элемента ИЛИ 7, а выход - с I и К-входами триггера 3 и со вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8, выход которого соединен с I и K-входами триггера 4 и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9. Второй вход элемента 9 соединен с инверсным выходом триггера 1, а выход - со вторым входом элемента ИЛИ 7. Второй вход 16 устройства соединен с R-входами триггеров 1, 2, 4 и 14.

Двоично-десятичный счетчик, показанный на фиг. 2, содержит первый 1, второй 2, третий 3 и четвертый 4 IК-триггеры, первый 5 и второй 6 логические элементы ИЛИ, третий 7 логический элемент ИЛИ-НЕ, четвертый 8, пятый 9, шестой 10 и седьмой 11 логические элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, восьмой 12 и девятый 13 логические элементы ИЛИ и пятый триггер 14.

Первый вход 15 соединен со счетным входом первого триггера 1 и первым входом элемента ИЛИ 12, второй вход которого соединен с I и К-входами триггера 1 и выходом элемента ИЛИ 7. Выход элемента ИЛИ 12 соединен со счетным входом триггера 2 и вторым входом элемента ИЛИ 5, первый вход которого соединен с прямым выходом триггера 1, I и К-входами триггера 2 и вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9. Выход элемента ИЛИ 5 соединен с первым входом элемента ИЛИ 6 и со счетным входом триггера 3. Второй вход элемента ИЛИ 6 соединен с I и К-входами триггера 3, выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11 и вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8. Выход элемента ИЛИ 6 соединен с первым входом элемента ИЛИ 13 и счетным входом триггера 4. Второй вход элемента ИЛИ 13 соединен с прямым выходом триггера 3, I и К-входами триггера 4 и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12. Выход элемента ИЛИ 9 соединен с I, С и К-входами триггера 14, прямой выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10, второй вход которого соединен с инвертирующим выходом триггера 4, R -входами триггера 1 и 2 и вторым входом элемента ИЛИ 5, а выход - с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11.

Второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 соединен с инвертирующим выходом триггера 2, а выход - с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9, выход которого соединен с первым входом элемента 7. Второй вход 16 соединен с R-входами триггеров 3, 4 и 14.

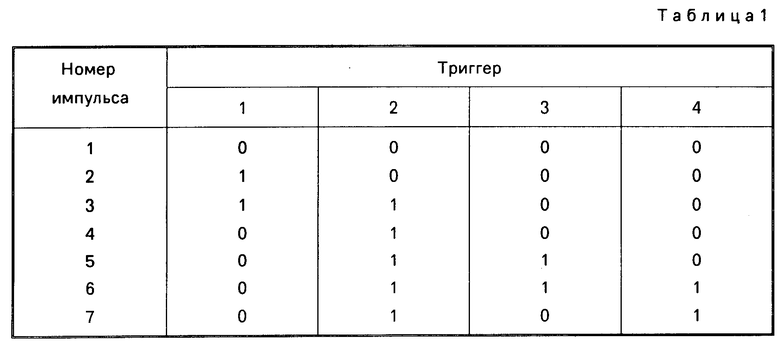

Двоично-десятичный счетчик по первому варианту работает следующим образом.

После подачи питания и установки счетчика в исходное состояние положительным импульсом по второму входу 16 все триггеры счетчика находятся в состоянии логического "0". Первый, второй, третий и четвертый триггеры счетчика переключаются по переднему, а пятый - по заднему фронтам счетного импульса. После установки счетчика в исходное состояние на первом входе элемента 10 и на обоих выходах элемента 7 присутствует потенциал логического "0", а на его выходе - потенциал логической "1", который по I-входу дает разрешение на переключение триггера 1 и запрет на прохождение счетного импульса на выход элемента ИЛИ 12. Поэтому первый счетный импульс, поступающий по входу 15, переключает триггер 1 в состояние логической "1". Потенциал логического "0" с инверсного выхода триггера 1, поступая на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9, приводит к появлению на его выходе потенциала логической "1", которая, проходя через элемент 7, инвертируется. Потенциал логического "0" с выхода элемента 7 дает запрет по IК-входам на переключение триггера 1 и разрешение на прохождение следующего счетного импульса через элемент ИЛИ 12. Потенциал логической "1" с прямого выхода триггера 1 дает разрешение по I-входу на переключение триггера 2 и запрет на прохождение счетного импульса на выход элемента ИЛИ 5. Второй счетный импульс, проходя через элемент ИЛИ 12, переключает триггер 2 в состояние логической "1". Потенциал логической "1" с прямого выхода триггера 2 поступает на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 (что приводит к появлению потенциала логического "0" на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9) и, проходя через элемент ИЛИ-НЕ 7, инвертируется. Потенциал логической "1" с выхода элемента 7 по К-входу дает разрешение на переключение триггера 1 и запрет на прохождение счетного импульса на выход элемента ИЛИ 12. Третий счетный импульс переключает триггер 1 в состояние логического "0". Потенциал логического "0" с прямого выхода триггера 1 дает запрет по IК-входам на переключение триггера 2 и разрешение на прохождение счетного импульса на выход элемента ИЛИ 5. Потенциал логической "1" с инверсного выхода триггера 1, поступая на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9, приводит к появлению на его выходе потенциала логической "1", которая, проходя через элемент 7, инвертируется. Потенциал логического "0" с выхода элемента 7 дает запрет по IК-входам на переключение триггера 1 и разрешение на прохождение следующего счетного импульса через элемент ИЛИ 12. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11 присутствует потенциал логической "1", который дает разрешение по I-входу на переключение триггера 3. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 присутствует потенциал логического "0", который дает запрет по IК-входам на переключение триггера 4. Четвертый счетный импульс, проходя через элементы ИЛИ 12 и 5, переключает триггер 3 в состояние логической "1". Четвертый счетный импульс не проходит на выход элемента ИЛИ 6, так как с прямого выхода триггера 2 на второй вход элемента ИЛИ 6 поступает потенциал логической "1". Потенциал логической "1" с прямого выхода триггера 3 после прихода четвертого счетного импульса поступает на второй вход элемента 7, что приводит к подтверждению потенциала логического "0" на его выходе и запрету по IК-входам на переключение триггера 1 и разрешению на прохождение следующего счетного импульса на выход элемента ИЛИ 12. Потенциал логической "1" с прямого выхода триггера 3 поступает на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11, что приводит к появлению на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11 потенциала логического "0", запрещающего по IК-входам переключение триггера 3, и к появлению на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 потенциала логической "1", разрешающего по I-входу переключение триггера 4. Пятый счетный импульс переключает триггер 4 в состояние логической "1". В дальнейшем счетчик переключается в соответствии с табл. 1.

После прохождения девятого счетного импульса счетчик принимает состояние, при котором на IК-входах всех триггеров присутствует потенциал логического "0", запрещающий их переключение, а на соответствующих входах элементов ИЛИ 12, 5 и 6 потенциал логического "0", разрешающий прохождение на их выходы следующего счетного импульса. Поэтому десятый счетный импульс не переключает триггеры 1-4 и проходит через элементы ИЛИ 6, 7 и 9 на вход триггера 14, переключая его в "1". Это вызывает появление на первом входе элемента 10 потенциала логической "1" с выхода пятого триггера. После этого начинается обратный счет в соответствии с табл. 1.

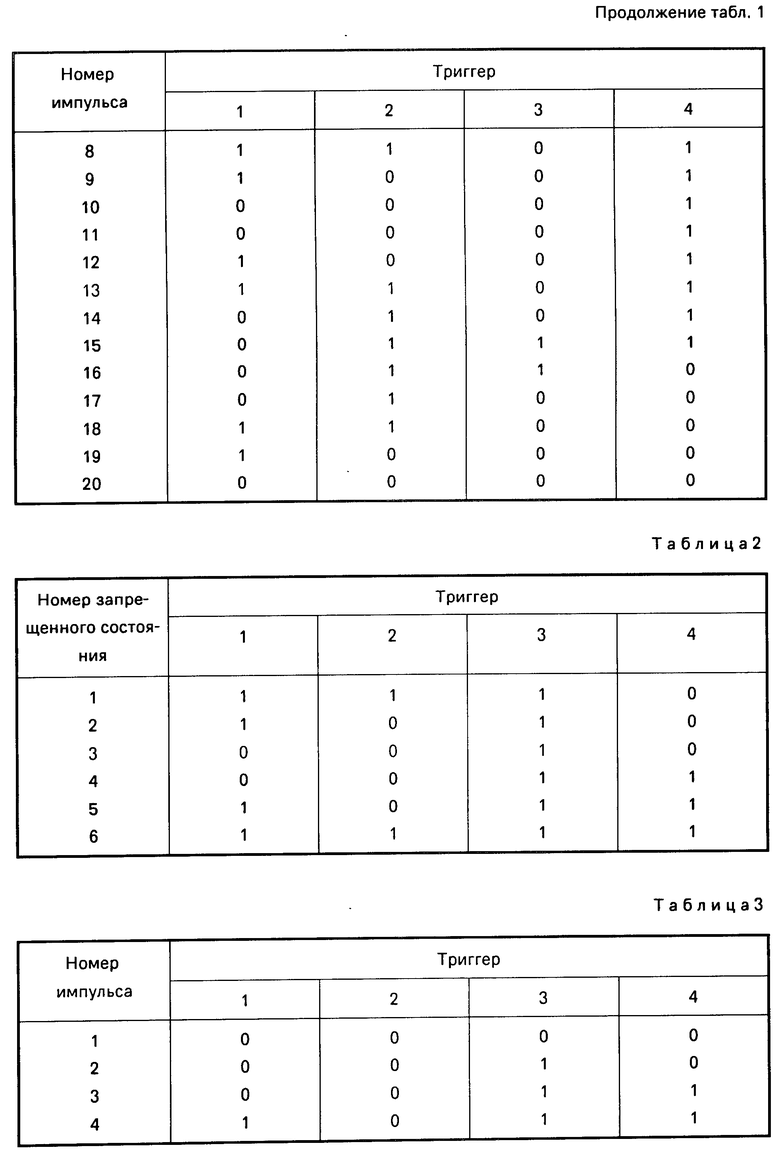

Анализ рабочих состояний табл. 1 и запрещенных состояний табл. 2 счетчика показывает, что любые комбинации состояний триггеров 1 и 2 кроме "01" в сочетании с состоянием "1" триггера 3 присущи только запрещенным состояниям счетчика. В то же время комбинация состояний "01" триггеров 1 и 2 в сочетании с состояниями "0" или "1" триггера 3 соответствует только рабочим состояниям счетчика. Поэтому элемент ИЛИ 13, на выходе которого потенциал логического "0" бывает только при наличии комбинации состояний "01" триггеров 1 и 2, позволяет в принципе исключить нахождение счетчика в запрещенных состояниях. Действительно, при любых комбинациях состояний триггеров 1 и 2, кроме "01", триггер 3 принудительно удерживается в обнуленном состоянии по R -входу потенциалом логической "1" с выхода элемента ИЛИ 13, что соответствует только рабочим комбинациям состояний счетчика. При появлении комбинации состояний "01" триггеров 1 и 2 на выходе элемента ИЛИ 13 появляется потенциал логического "0", который снимает запрет по R-входу на переключение триггера 3. Но и в этом случае возможные комбинации состояний триггеров 1, 2 и 3 соответствуют рабочим состояниям счетчика.

Таким образом, помехи, изменяющие состояние счетчика, могут установить его только в одно из рабочих состояний.

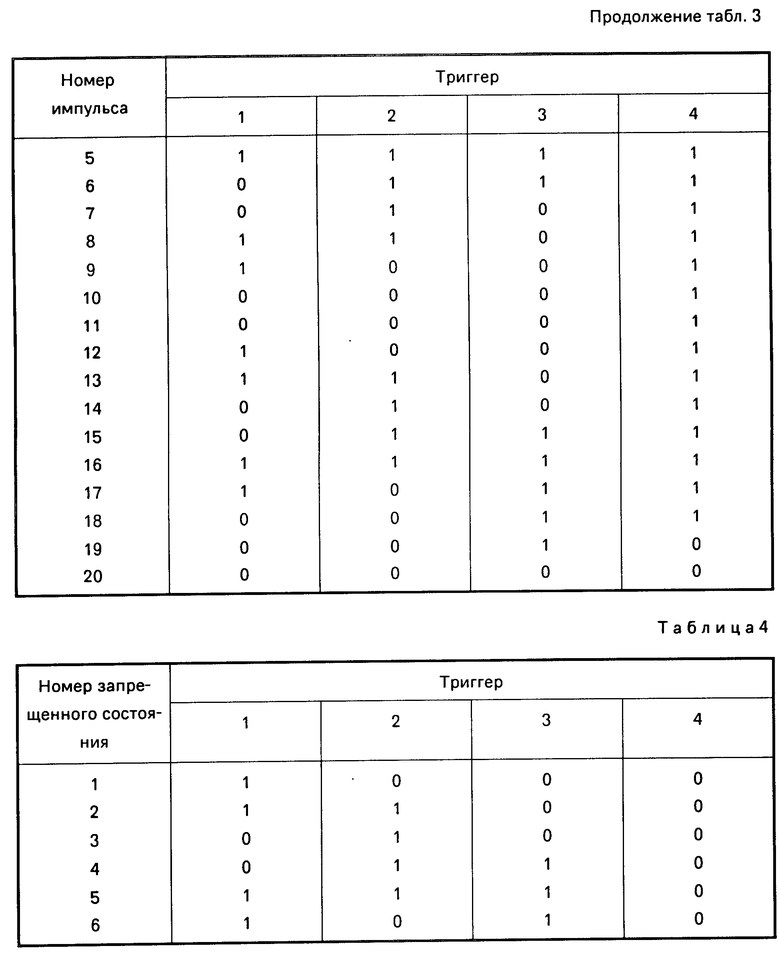

Двоично-десятичный счетчик по второму варианту работает аналогично первому в соответствии с табл. 3.

Различие состоит в использовании других комбинаций состояний, используемых в качестве рабочих, и соответственно других способов исключения запрещенных состояний.

После подачи питания и установки второго варианта счетчика в исходное состояние положительным импульсом по второму входу 16 все триггеры счетчика находятся в состоянии "0". Триггеры счетчика переключаются по переднему фронту счетного импульса. После установки счетчика в исходное состояние на вход элемента ИЛИ-НЕ 7 поступает потенциал логической "1" с инверсного выхода триггера 4, которая, проходя через элемент 8, инвертируется. Потенциал логического "0" с выхода элемента 7 дает запрет по IК-входам на переключение триггера 1 и разрешение на прохождение счетного импульса через элемент ИЛИ 12. Потенциал логического "0" с прямого выхода триггера 1 дает запрет по IК-входам на переключение триггера 2 и разрешение на прохождение счетного импульса через элемент ИЛИ 5. Вследствие наличия потенциала логического "0" на первом входе элемента 10, логической "1" на инверсном выходе триггера 4 и логического "0" на прямом выходе триггера 3 с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11, потенциал логической "1" поступает на IК-входы триггера 3 и вход элемента ИЛИ 6, давая разрешение на переключение триггера 3 по I-входу и запрет на прохождение счетного импульса на выход элемента ИЛИ 6. Поэтому первый счетный импульс проходит через элементы ИЛИ 12 и 5 и переключает триггер 3 в состояние логической "1", не изменяя состояния триггеров 1, 2, 4.

В дальнейшем счетчик переключается в соответствии с табл. 3.

После прохождения девятого счетного импульса счетчик принимает состояние, при котором на IК-входах всех триггеров присутствует потенциал логического "0", запрещающий их переключение, а на соответствующих входах элементов ИЛИ 6, 7, 8 и 9 потенциал логического "0", разрешающий прохождение на их выходы десятого счетного импульса, который, не переключая триггеры 1, 2, 3 и 4, проходит на выход элемента 13. Это вызывает переключение пятого триггера и появление на первом входе элемента 10 потенциала логической "1", после чего начинается обратный счет в соответствии с табл. 3.

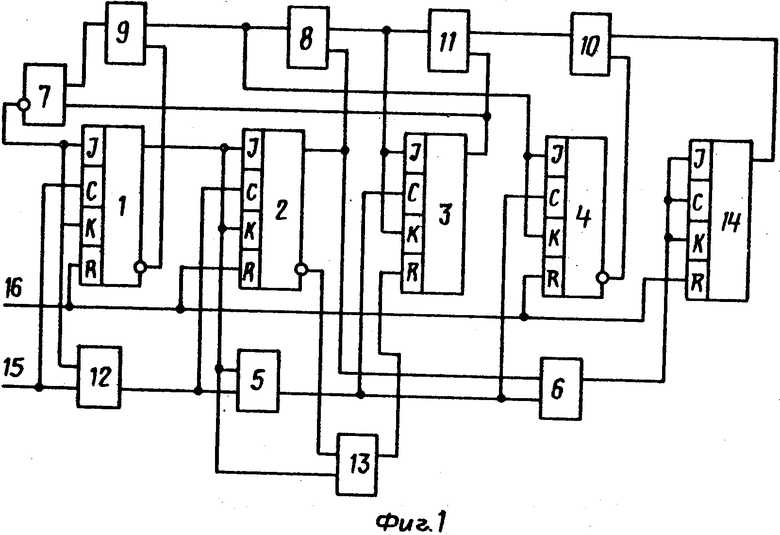

Из анализа рабочих состояний табл. 3 и запрещенных состояний табл. 4 второго варианта счетчика следует, что запрещенные состояния, которые определяются наличием состояния логического "0" триггера 4, исключаются связью инвертирующего выхода этого триггера с R -входами триггеров 1 и 2. При этом помехи, устанавливающие триггер 4 в состояние логического "0", ведут к появлению на его инвертирующем выходе потенциала логической "1". При этом сбрасывается в исходное состояние триггеров 1 и 2, что дает в итоге одну из рабочих комбинаций счетчика: "0000" или "0010".

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления очередностью обслуживания | 1987 |

|

SU1481765A2 |

| Многофункциональный регистр | 1986 |

|

SU1411828A1 |

| Цифровой частотно-фазовый дискриминатор | 1991 |

|

SU1826122A1 |

| СЧЕТНОЕ УСТРОЙСТВО | 1985 |

|

SU1344196A1 |

| Устройство для моделирования процесса обслуживания заявок | 1986 |

|

SU1524064A1 |

| Устройство для измерения частоты и периода | 1991 |

|

SU1824592A1 |

| МОДУЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2112269C1 |

| Квадратор | 1980 |

|

SU926652A1 |

| Устройство для измерения временных интервалов /его варианты/ | 1984 |

|

SU1255985A1 |

| Преобразователь пачки импульсов в прямоугольный импульс | 1985 |

|

SU1265982A1 |

| ДВОИЧНО-ДЕСЯТИЧНЫЙ РЕФЛЕКСНЫЙ СЧЕТЧИК | 1972 |

|

SU428557A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1994-11-30—Публикация

1983-12-05—Подача