Изобретение относится к автоматике и вычислительной технике и может найти применение при построении систем управления технологическими процессами.

Известно модульное устройство для программного управления и контроля, содержащее блок памяти, счетчик адреса, регистр микроопераций, мультиплексоры адреса и логических условий, демультиплексор, два регистра логических условий, регистр номера, два коммутатора, два дешифратора, шифратор, генератор тактовых импульсов, триггеры пуска и управления, блок элементов ИЛИ, группу элементов ИЛИ, два элемента И и два элемента ИЛИ (а.с. СССР N 1647519, кл. G 05 B 19/18; опубл. 07.05.91, БИ N 17).

Недостатками известного устройства являются значительное число внешних входов и выходов, требуемых для организации взаимодействия с другими аналогичными устройствами при построении управляющих систем, а также существенная зависимость этого числа от количества идентичных устройств в составе системы.

Наиболее близким к предлагаемому устройству по технической сущности является устройство для программного управления, содержащее блок памяти микрокоманд, счетчики адреса и времени задержки, регистр микроопераций, коммутатор направления приема адреса, триггер режима, шифратор направления приема управления, дешифратор направления передачи управления, шину микроопераций, элемент запрета, четыре элемента ИЛИ и два элемента И (а.с. СССР N 1800445, кл. G 05 B 19/18; опубл. 07.03.93; БИ N 9).

Недостатком данного устройства является узкая область применения, обусловленная низкой функциональной гибкостью, что объясняется следующими особенностями. При функционировании устройства в составе управляющей системы обеспечивается возможность приема управления (инициализации) как от внешнего устройства, так и от других аналогичных устройств. Прием управления происходит после появления единичного сигнала на одной из входных линий инициализации устройства и осуществляется с использованием фиксированного ("жесткого") адреса, который однозначно определяется номером входной линии, по которой поступает сигнал инициализации, т.е. номером другого устройства, выполняющего передачу управления. Принятый способ определения адресов приема управления не позволяет организовать возможность многократного приема управления от одного и того же устройства по различным адресам инициализации и, следовательно, вводит существенные ограничения на порядок размещения фрагментов микропрограмм в памяти отдельных модулей системы. Так, например, если при реализации s-й микропрограммы имеет место передача управления между устройствами l и m (l _→ m), то передача управления вида l _→ m при реализации другой (t-й) микропрограммы оказывается невозможной, так как приводит к инициализации устройства m с одного и того же "жесткого" адреса. В силу аналогичных причин невозможны последовательности передач управления вида l _→ m, m _→ n, ..., q _→ l, l _→ m при реализации одной микропрограммы. Рассмотренные особенности организации взаимодействия устройства с другими аналогичными устройствами снижают его функциональную гибкость и, таким образом, существенно ограничивают область применения.

Технической задачей изобретения является расширение области применения устройства на основе организации возможности многократного приема управления от одного и того же аналогичного устройства по различным адресам при неизменной (минимальной) сложности межмодульного интерфейса.

Техническая задача решается тем, что в модульное устройство для программного управления, содержащее блок памяти микрокоманд, счетчик адреса, регистр микроопераций, счетчик времени задержки, коммутатор направления приема адреса, триггер режима, дешифратор направления передачи управления, шифратор признака микропрограммы, элемент запрета, шину микроопераций, первый и второй элементы И, с первого по четвертый элементы ИЛИ, причем входы шифратора признака микропрограммы с первого по l-й (где l - максимальное число идентичных устройств, образующих управляющую систему) соединены с входами инициализации устройства с первого по l-й соответственно, выход первого элемента ИЛИ подключен к J-входу триггера режима и к первому и второму управляющим входам коммутатора направления приема адреса, выход которого соединен с информационным входом счетчика адреса, выход которого соединен с адресным входом блока памяти микрокоманд, выход микроопераций которого подключен к информационному входу регистра микроопераций, выход которого соединен с информационным входом элемента запрета, выход которого подключен к шине микроопераций, выход признака формата блока памяти микрокоманд подключен к управляющему входу дешифратора направления передачи управления, к первому входу второго элемента ИЛИ и к K-входу триггера режима, прямой выход которого соединен с управляющим входом элемента запрета, а также с вторым входом второго элемента ИЛИ, выход которого подключен к первым входам первого и второго элементов И, выход адреса/номера модуля блока памяти микрокоманд соединен с информационным входом дешифратора направления передачи управления, с первым информационным входом коммутатора направления приема адреса и группой входов третьего элемента ИЛИ, выход которого соединен с управляющим входом счетчика адреса, выход времени задержки блока памяти микрокоманд подключен к информационному входу счетчика времени задержки, выход переноса которого соединен с синхровходом и счетным входом счетчика адреса, информационный выход счетчика времени задержки подключен к входам четвертого элемента ИЛИ, выход которого соединен с управляющим входом счетчика времени задержки, первый вход синхронизации устройства соединен с синхровходом триггера режима и с вторым входом первого элемента И, выход которого подключен к синхровходу и счетному входу счетчика времени задержки, второй вход синхронизации устройства является вторым входом второго элемента И, выход которого соединен с синхровходом регистра микроопераций, дополнительно введены шифратор адреса приема управления, регистр признака микропрограммы, счетчик количества передач управления, триггер настройки, группа из l-1 элементов ИЛИ, с третьего по шестой элементы И, пятый элемент ИЛИ и элемент задержки, причем входы инициализации устройства с первого по l-й соединены с соответствующими входами пятого элемента ИЛИ, выход которого подключен к первым входам третьего и четвертого элементов И и к синхровходу триггера настройки, на D-входе которого постоянно находится потенциал логической единицы, инверсный выход триггера настройки соединен с вторым (инверсным) входом третьего элемента И и с вторым входом четвертого элемента И, выход которого подключен к входу элемента задержки, выход которого подключен к синхровходу регистра признака микропрограммы, информационный вход которого соединен с выходом шифратора признака микропрограммы, выход третьего элемента И подключен к первому входу первого элемента ИЛИ, выход которого соединен со счетным входом счетчика количества передач управления, выход которого в объединении с выходом регистра признака микропрограммы подключен к входу шифратора адреса приема управления, выход которого соединен с вторым информационным входом коммутатора направления приема адреса, l-й вход инициализации устройства соединен с вторым входом первого элемента ИЛИ, а также с первыми входами первого, второго,..., (l-1)-го элементов ИЛИ группы, вторые входы которых подключены к первому, второму, . . ., (l-1)-му выходам дешифратора направления передачи управления соответственно, а выходы являются первым, вторым,...,(l-1)-м выходами передачи управления устройства соответственно, выход признака формата блока памяти микрокоманд соединен с третьим и четвертым управляющими входами коммутатора направления приема адреса, с первым входом пятого элемента И и с первым входом шестого элемента И, выход которого соединен с входом сброса регистра микроопераций, выход переноса счетчика времени задержки подключен к второму входу шестого элемента И и к второму входу пятого элемента И, выход которого подключен к входам сброса регистра признака микропрограммы, счетчика количества передач управления и триггера настройки, выход признака конца микропрограммы блока памяти микрокоманд соединен с третьим входом пятого элемента И и с входом третьего элемента ИЛИ.

Сущность изобретения заключается в следующем.

Предлагаемое устройство совместно с другими аналогичными устройствами (модулями) включается в состав управляющей системы, которая обеспечивает возможность реализации микропрограмм значительной сложности путем распределения их фрагментов между различными устройствами и организации возможности последовательной передачи управления. Передача и прием управления между каждой парой устройств осуществляется путем подачи единичных сигналов по двум физическим линиям и использования фиксированных ("жестких") адресов приема управления, что обеспечивает минимальную сложность межмодульного интерфейса. В отличие от прототипа, где адрес приема управления однозначно определяется номером входа, на который поступает сигнал передачи управления (направлением приема управления), в предлагаемом устройстве указанный адрес не зависит от направления приема управления, а определяется порядковым номером текущей передачи управления данному устройству (номером обращения к данному устройству) и признаком выполняемой микропрограммы. Для обеспечения возможности запуска системы со стороны внешнего устройства (центрального процессора) каждый модуль имеет дополнительный вход, а номер выполняемой микропрограммы однозначно задается номером модуля, запускаемого при инициализации управляющей системы первым.

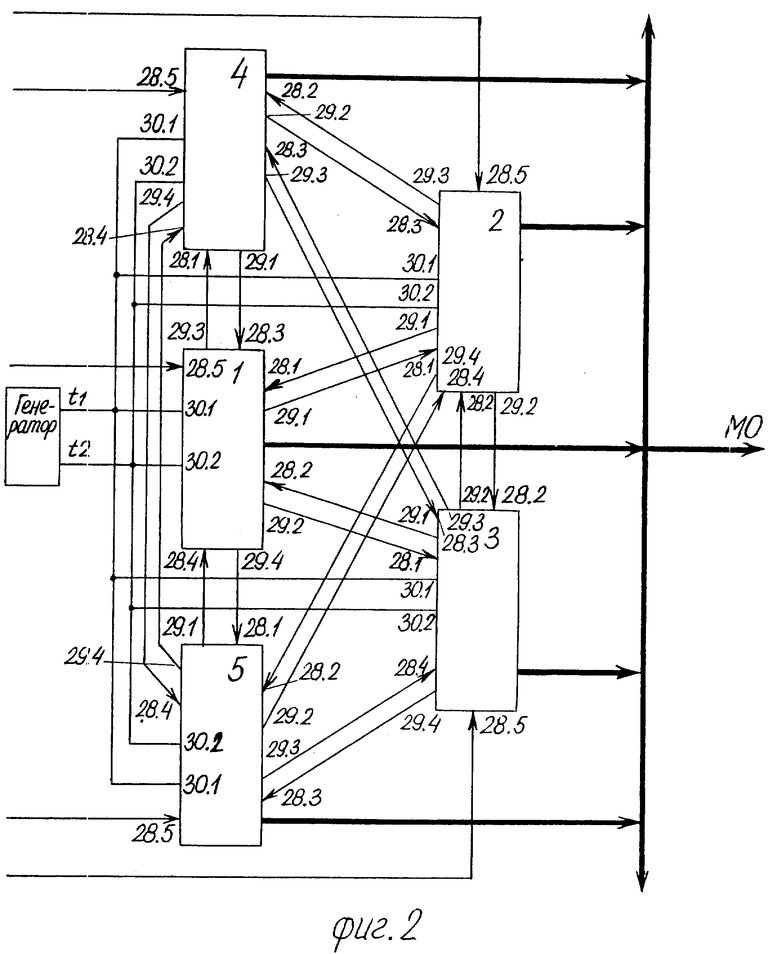

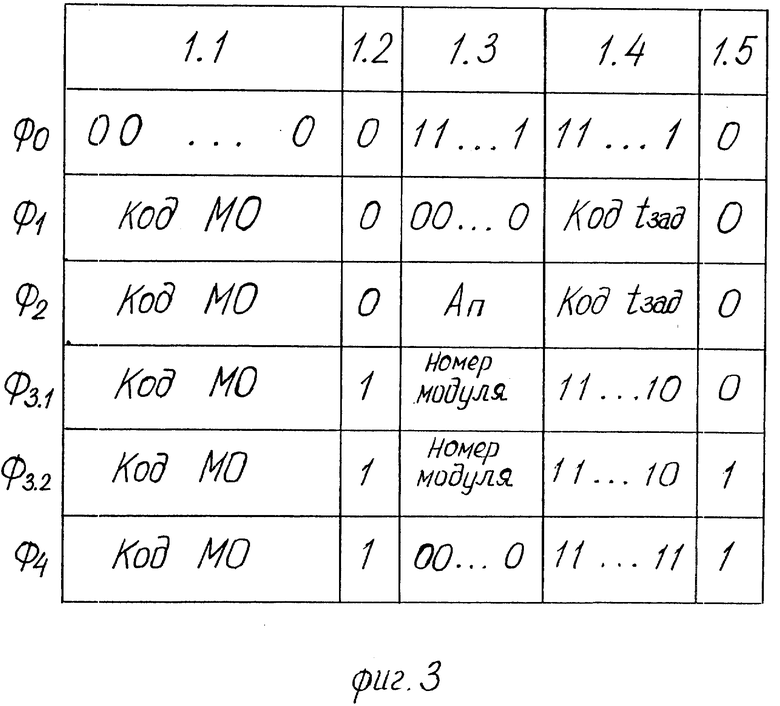

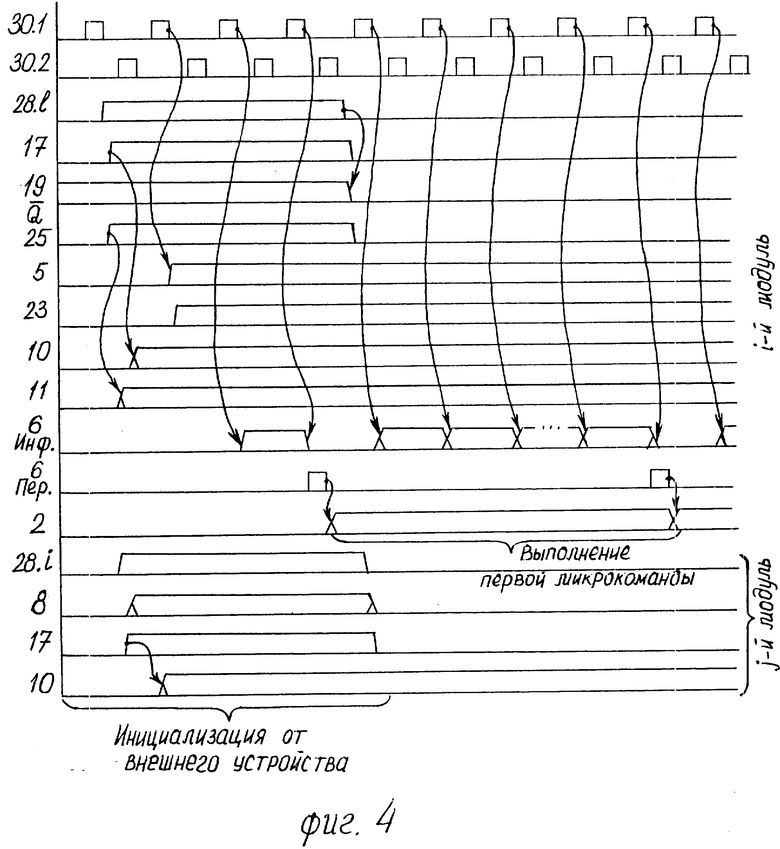

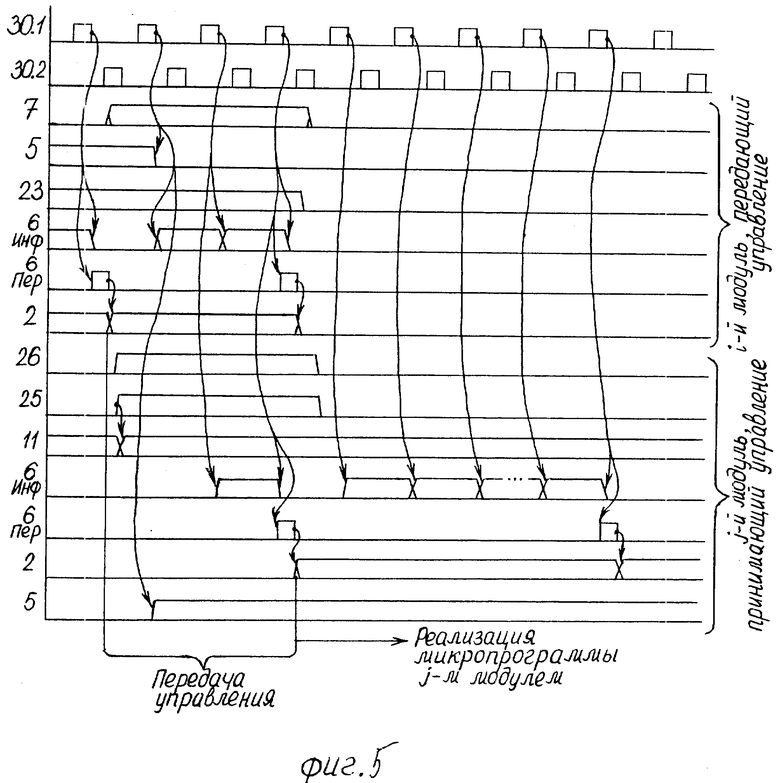

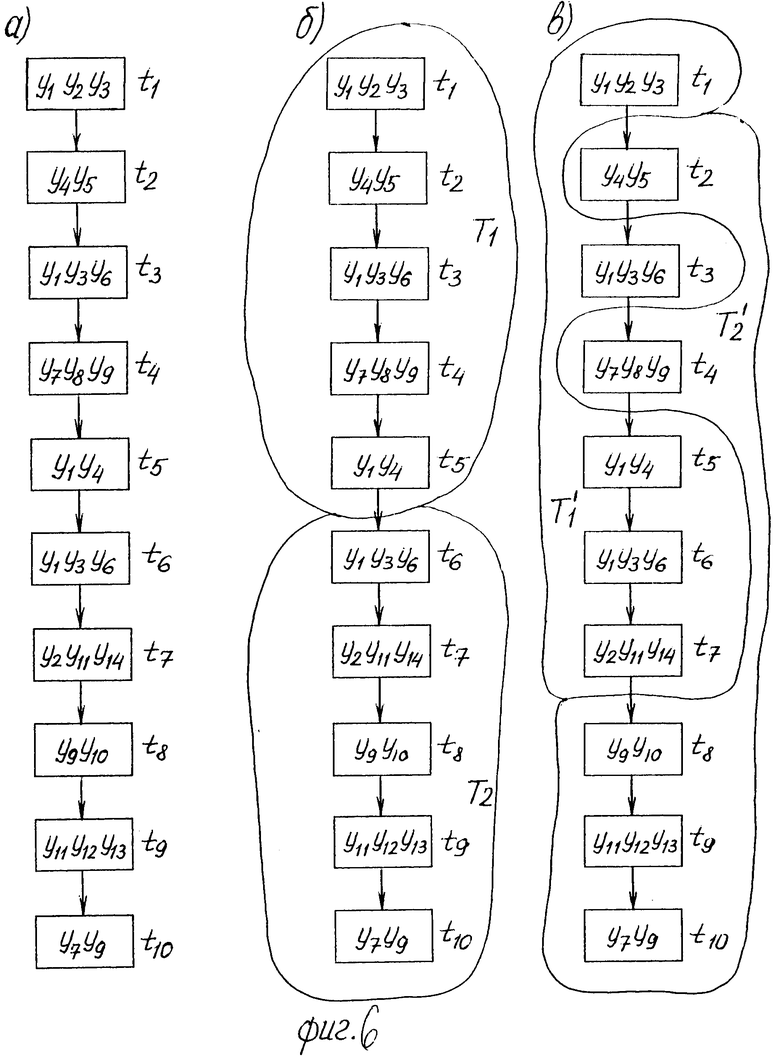

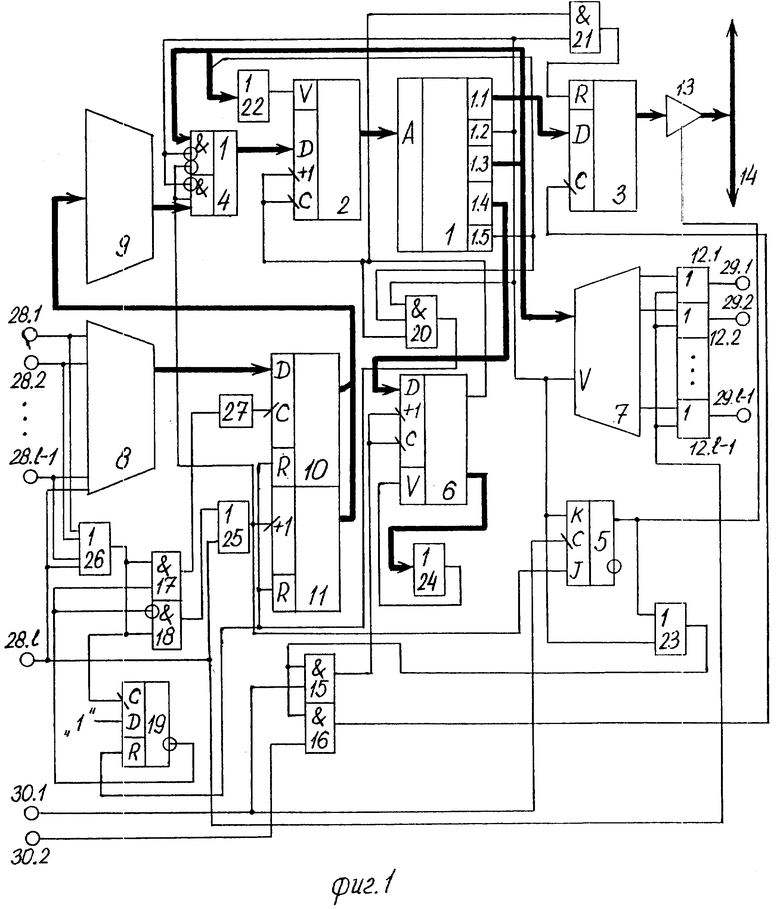

Сущность изобретения поясняется чертежами, где на фиг. 1 представлена функциональная схема модульного устройства для программного управления; на фиг. 2 - пример управляющей системы, построенной на базе пяти идентичных устройств; на фиг. 3 - форматы микрокоманд, реализуемых устройством; на фиг. 4, 5 приведены временные диаграммы работы устройства при инициализации от внешнего устройства, выполнении фрагмента микропрограммы (фиг. 4), передаче и приеме управления от другого аналогичного устройства (фиг. 5), а на фиг. 6 дан пример алгоритма управления.

Модульное устройство для программного управления (фиг. 1) содержит блок 1 памяти микрокоманд, счетчик 2 адреса, регистр 3 микроопераций, коммутатор 4 направления приема адреса, триггер 5 режима, счетчик 6 времени задержки, дешифратор 7 направления передачи управления, шифратор 8 признака микропрограммы, элемент 13 запрета, шину 14 микроопераций, первый 15 и второй 16 элементы И, третий 22, второй 23, четвертый 24 и первый 25 элементы ИЛИ, причем входы шифратора 8 признака микропрограммы с первого по l-й (где l - максимальное число идентичных устройств, образующих управляющую систему) соединены с входами 28.1-28.l инициализации устройства соответственно, выход элемента ИЛИ 25 подключен к J-входу триггера 5 режима и к первому и второму управляющим входам коммутатора 4 направления приема адреса, выход которого соединен с информационным входом счетчика 2 адреса, выход которого соединен с адресным входом блока 1 памяти микрокоманд, выход 1.1 микроопераций которого подключен к информационному входу регистра 3 микроопераций, выход которого соединен с информационным входом элемента 13 запрета, выход которого подключен к шине 14 микроопераций, выход 1.2 признака формата блока 1 памяти микрокоманд подключен к управляющему входу дешифратора 7 направления передачи управления, к первому входу элемента ИЛИ 23 и к K-входу триггера 5 режима, прямой выход которого соединен с управляющим входом элемента 13 запрета, а также с вторым входом элемента ИЛИ 23, выход которого подключен к первым входам элементов И 15 и 16, выход 1.3 адреса/номера модуля блока 1 памяти микрокоманд соединен с информационным входом дешифратора 7 направления передачи управления, с первым информационным входом коммутатора 4 направления приема адреса и группой входов элемента ИЛИ 22, выход которого соединен с управляющим входом счетчика 2 адреса, выход 1.4 времени задержки блока 1 памяти микрокоманд подключен к информационному входу счетчика 6 времени задержки, выход переноса которого соединен с синхровходом и счетным входом счетчика 2 адреса, информационный выход счетчика 6 времени задержки подключен к входам элемента ИЛИ 24, выход которого соединен с управляющим входом счетчика 6 времени задержки, первый вход синхронизации 30.1 устройства соединен с синхровходом триггера 5 режима и с вторым входом элемента И 15, выход которого подключен к синхровходу и счетному входу счетчика 6 времени задержки, второй вход синхронизации 30.2 устройства является вторым входом элемента И 16, выход которого соединен с синхровходом регистра 3 микроопераций, а также дополнительно введенные шифратор 9 адреса приема управления, регистр 10 признака микропрограммы, счетчик 11 количества передач управления, группу элементов ИЛИ 12.1-12.l-1, четвертый 17 и третий 18 элементы И, триггер 19 настройки, пятый 20 и шестой 21 элементы И, пятый элемент ИЛИ 26 и элемент 27 задержки, причем входы 28.1-28.l инициализации устройства соединены с соответствующими входами элемента ИЛИ 26, выход которого подключен к первым входам элементов И 17, 18 и к синхровходу триггера 19 настройки, на D-входе которого постоянно находится потенциал логической единицы, инверсный выход триггера 19 настройки соединен с вторым (инверсным) входом элемента И 18 и с вторым входом элемента И 17, выход которого подключен к входу элемента 27 задержки, выход которого подключен к синхровходу регистра 10 признака микропрограммы, информационный вход которого соединен с выходом шифратора 8 признака микропрограммы, выход элемента И 18 подключен к первому входу элемента ИЛИ 25, выход которого соединен со счетным входом счетчика 11 количества передач управления, выход которого в объединении с выходом регистра 10 признака микропрограммы подключен к входу шифратора 9 адреса приема управления, выход которого соединен с вторым информационным входом коммутатора 4 направления приема адреса, вход 28.l инициализации устройства соединен с вторым входом элемента ИЛИ 25, а также с первыми входами элементов ИЛИ 12.1-12. l-1, вторые входы которых подключены к первому, второму,..., (l-1)-му выходам дешифратора 7 направления передачи управления соответственно, выходы элементов ИЛИ 12.1-12. l-1 являются выходами 29.1-29.l-1 передачи управления устройства соответственно, выход 1.2 признака формата блока 1 памяти микрокоманд соединен с третьим и четвертым управляющими входами коммутатора 4 направления приема адреса, с первым входом элемента И 20 и с первым входом элемента И 21, выход которого соединен с входом сброса регистра 3 микроопераций, выход переноса счетчика 6 времени задержки подключен к второму входу элемента И 21 и к второму входу элемента И 20, выход которого подключен к входам сброса регистра 10 признака микропрограммы, счетчика 11 количества передач управления и триггера 19 настройки, выход 1.5 признака конца микропрограммы блока 1 памяти микрокоманд соединен с третьим входом элемента И 20 и с входом элемента ИЛИ 22.

Назначение элементов модульного устройства для программного управления (фиг. 1) заключается в следующем.

Блок 1 памяти микрокоманд предназначен для хранения и выдачи микрокоманд, входящих в различные фрагменты микропрограмм, закрепленные за текущим устройством. Блок 1 не имеет специальных управляющих входов, и информация на его выходе появляется непосредственно после установления на его входе очередного адреса.

Счетчик 2 адреса обеспечивает формирование исполнительного адреса следующей микрокоманды и в зависимости от уровня сигнала на его управляющем входе функционирует либо в счетном режиме (при нулевом управляющем сигнале), либо в режиме приема параллельного кода с информационного входа (при единичном управляющем сигнале), осуществляя соответственно естественную и принудительную адресацию следующей микрокоманды.

Регистр 3 микроопераций предназначен для приема, временного хранения, а также для выдачи сигналов микроопераций на шину 14 микроопераций.

Коммутатор 4 обеспечивает выбор направления приема адреса следующей микрокоманды и формирует нулевой адрес при функционировании текущего устройства в режиме передачи управления другому аналогичному устройству.

Триггер 5 режима предназначен для управления режимами работы устройства. Единичное состояние триггера 5 соответствует рабочему режиму устройства, а нулевое - либо исходному состоянию, либо состоянию ожидания передачи управления от другого устройства.

Счетчик 6 времени задержки служит для управления временем обработки микрокоманд, т. е. задания времени присутствия сигналов микроопераций на шине 14 и аналогично счетчику 2 функционирует либо в режиме счета, либо в режиме приема информации - кода времени задержки - в параллельном коде. Первый из указанных режимов активизируется при единичном, а второй - при нулевом уровне сигнала на управляющем входе счетчика 6. Момент переполнения счетчика 6 при работе в счетном режиме индицируется появлением импульса p переноса на одноименном выходе.

Дешифратор 7 обеспечивает выбор направления передачи управления при функционировании устройства в режиме передачи управления другому аналогичному устройству. Выбор указанного направления состоит в возбуждении единичного сигнала на выходе дешифратора 7, соответствующем коду номера модуля, которому передается управление. Дешифратор 7 имеет специальный управляющий вход (V) и функционирует только при наличии на этом входе единичного уровня сигнала. Число выходов дешифратора 7 определяется максимально возможным числом l устройств в составе управляющей системы и равно l-1.

Шифратор 8 признака микропрограммы введен для преобразования номера входной линии (входа) инициализации устройства, по которой поступает единичный сигнал, в код признака выполняемой микропрограммы, используемый совместно с кодом номера текущей передачи управления данному устройству для формирования адреса приема управления.

Шифратор 9 служит для преобразования кода признака выполняемой микропрограммы, объединенного с кодом текущей передачи управления данному устройству, в адрес начала фрагмента микропрограммы (адрес приема управления) в блоке 1.

Регистр 10 предназначен для приема, хранения и выдачи кода признака микропрограммы. Запись указанного кода в регистр 10 осуществляется при инициализации управляющей системы от внешнего устройства; состояние регистра 10 остается неизменным до момента окончания выполнения всех фрагментов микропрограммы, закрепленных за текущим устройством. Этот момент индицируется появлением единичной метки конца микропрограммы в формате очередной микрокоманды, считываемой из блока 1.

Счетчик 11 количества передач управления предназначен для формирования кода номера текущей передачи управления данному устройству. Исходное состояние счетчика 11 является нулевым, а изменение состояния происходит в момент возникновения положительного (0 _→ 1) перепада уровня сигнала на счетном входе при возбуждении одного из входов 28.1-28.l инициализации устройства.

Группа элементов ИЛИ 12 введена для объединения сигналов передачи управления, формируемых дешифратором 7, и сигнала настройки системы на выполнение требуемой микропрограммы, поступающего с входа 28.l устройства. При настройке системы единичный сигнал с входа 28.l i-го устройства через элементы ИЛИ 12.1-12.l-1 одновременно проходит на выходы 29.1-29.l-1 устройства, поступает на соответствующие входы 28.i остальных устройств и формирует на выходах шифраторов 8 устройств признак выполняемой микропрограммы, который в дальнейшем фиксируется в регистрах 10. Признак выполняемой микропрограммы однозначно определяется номером устройства, инициализируемого от внешнего устройства при запуске системы.

Элемент 13 запрета служит для разрешения и блокировки доступа к шине 14 микроопераций, которая, в свою очередь, обеспечивает передачу управляющих сигналов с выходов всех модулей управляющей системы на вход объекта управления.

Элементы И 15, 16 служат для блокировки подачи тактовых импульсов t1 и t2 соответственно на синхровход, счетный вход счетчика 6 и на синхровход регистра 3 микроопераций.

Элемент И 17 предназначен для формирования сигнала записи кода признака выполняемой микропрограммы в регистр 10 при работе устройства в режиме настройки и блокировки модификации содержимого регистра 10 при возникновении сигнала передачи управления от другого устройства в ходе реализации микропрограммы.

Элемент И 18 служит для формирования сигнала приема управления при передаче управления от другого устройства и блокировки процесса приема управления при работе устройства в режиме настройки на выполнение требуемой микропрограммы.

Триггер 19 настройки предназначен для управления прохождением сигналов через элементы И 17 и 18, а также индикации текущего режима работы устройства. На D-входе триггера 19 постоянно присутствует потенциал логической единицы и данный триггер переходит в единичное состояние по заднему фронту (срезу) сигнала на его синхровходе.

Элемент И 20 служит для формирования сигнала сброса регистра 10, счетчика 11 и триггера 19 после завершения выполнения устройством всех закрепленных за ним фрагментов текущей микропрограммы.

Элемент И 21 служит для формирования сигнала сброса регистра 3 микроопераций после реализации устройством очередного фрагмента текущей микропрограммы.

Элементы ИЛИ 22 и 24 предназначены для формирования сигналов управления счетчиками 2 и 6 соответственно.

Элемент ИЛИ 23 служит для формирования сигнала управления (разрешения/блокировки) элементами И 15, 16,

Элемент ИЛИ 25 предназначен для объединения сигналов приема управления, возникающих соответственно при инициализации устройства со стороны внешнего устройства (на входе 28.l устройства) и передаче управления от другого аналогичного устройства (на выходе элемента И 18).

Элемент ИЛИ 26 предназначен для объединения сигналов, поступающих на входы 28.1-28.l инициализации устройства, и управления переключением триггера 19, а также управления элементами И 17, 18.

Элемент 27 задержки обеспечивает сдвиг переднего фронта сигнала записи информации в регистр 10 на время установления кода признака выполняемой микропрограммы на выходе шифратора 8.

Работу предлагаемого устройства рассмотрим на примере функционирования модульной системы программного управления, состоящей из множества идентичных устройств и реализующей комплекс сложных микропрограмм, число которых определяет число модулей l в составе системы.

Первоначально все регистры, счетчики и триггеры устройства (фиг.1) находятся в состоянии логического нуля, поэтому элемент 13 запрета переведен в состояние высокого импеданса, а нулевой код с выхода счетчика 2 поступает на адресный вход блока 1 и обеспечивает считывание микрокоманды специального формата ФО (фиг.3), размещенной в ячейке блока 1 с нулевым адресом. На выходе 1.2 блока 1 находится нулевой сигнал (признак формата микрокоманды). Этот сигнал и нулевой сигнал с прямого выхода триггера 5 режима обусловливают наличие нулевого уровня сигнала на выходе элемента ИЛИ 23 и тем самым блокируют элементы И 15 и 16. На выходе 1.5 блока 1 также присутствует нулевой сигнал: элемент И 20 закрыт, а нулевой сигнал с выхода 1.2 блока 1 запрещает работу дешифратора 7 и обусловливает наличие нулевых сигналов на выходах 29.1-29.l-1 устройства.

Функционирование устройства (и системы в целом) начинается с приходом на вход 28.l единичного сигнала инициализации от внешнего устройства (центрального процессора). Будем считать, что сигнал инициализации поступает на вход 28. l i-го устройства (модуля) и, таким образом, определяет выполнение i-й микропрограммы, начальный фрагмент (а, возможно, и другие фрагменты) которой закреплен за i-м устройством. Рассматриваемый сигнал инициализации выполняет множество функций и наряду с запуском i-го устройства осуществляет настройку других устройств на исполнение i-й микропрограммы.

Единичный сигнал с входа 28.l i-го устройства:

а) поступает на l-й вход шифратора 8 и совместно с нулевыми сигналами, находящимися на его первом, втором,..., (l-1)-м входах, формирует признак i-й (выполняемой) микропрограммы. Признак i-й микропрограммы с выхода шифратора 8 подается на информационный вход регистра 10;

б) через элемент ИЛИ 26 проходит на первые входы элементов И 17 и 18 и синхровход триггера 19. Так как триггер 19 первоначально находится в нулевом состоянии, единичный сигнал с его инверсного выхода блокирует элемент И 18 и открывает элемент И 17. В связи с этим единичный сигнал инициализации устройства через элемент И 17 и элемент 27 задержки поступает на синхровход регистра 10 и фронтом производит запись присутствующего на информационном входе данного регистра признака i-й микропрограммы, обеспечивая тем самым настройку i-го устройства на реализацию i-й микропрограммы;

в) через элемент ИЛИ 25 поступает на счетный вход счетчика 11 и фронтом увеличивает его содержимое на единицу: на выходе счетчика 11 образуется код "0. . .01" первой передачи управления i-му устройству. Код "0...01" с выхода счетчика 11 совместно с признаком i-й микропрограммы с выхода регистра 10 поступает на вход шифратора 9 и формирует на его выходе "жесткий" адрес (A

г) через элемент ИЛИ 25 проходит на J-вход триггера 5, а также на первый и второй управляющие входы коммутатора 4, подготавливая триггер 5 к переключению в единичное состояние и настраивая коммутатор 4 на прием информации с выхода шифратора 9. Адрес A

д) через элементы ИЛИ 12.1-12.l-1 поступает на выходы 29.1-29.l-1 устройства соответственно и обеспечивает настройку других устройств системы на реализацию i-й микропрограммы.

Процесс настройки устройств системы на реализацию i-й микропрограммы рассмотрим на примере настройки устройства Mj,  , j ≠ i.

, j ≠ i.

Единичный сигнал с выхода 29.j i-го устройства передается на вход 28.i j-го устройства, далее поступает на соответствующий вход шифратора 8 и формирует на его выходе признак i-й микропрограммы (данный признак является, аналогично прототипу, результатом преобразования номера входа 28.i, т.е. направления приема управления в некоторое двоичное число (код)). Одновременно этот же сигнал проходит через элемент ИЛИ 26 и поступает на первые входы элементов И 17, 18, а также на синхровход триггера 19. Поскольку последний находится в исходном (нулевом) состоянии, единичный сигнал с его инверсного выхода блокирует элемент 18, запрещая интерпретацию поступающего сигнала инициализации как сигнала передачи управления. В то же время единичный сигнал с выхода элемента 26 проходит через открытый элемент И 17, через элемент 27 задержки и фронтом заносит в регистр 10 признак i-й микропрограммы, установленный на выходе шифратора 8. Так как элемент И 18 заблокирован, на выходе элемента ИЛИ 25 сохраняется нулевой уровень сигнала, счетчик 11 остается в исходном (нулевом) состоянии, а на J-входе триггера 5 формируется нулевой сигнал и состояние этого триггера в дальнейшем остается неизменным.

На этом настройка j-го устройства на реализацию i-й микропрограммы завершается. Ее результатом является нулевое состояние счетчика 11 и наличие признака выполняемой микропрограммы в регистре 10.

Теперь снова перейдем к рассмотрению функционирования i-го устройства.

Тактовый импульс t1, появляющийся на входе 30.1 i-го устройства, поступает на синхровход триггера 5 и, поскольку на J-входе триггера 5 находится единичный сигнал инициализации, устанавливает этот триггер в единичное состояние, индицируя тем самым начало работы устройства. Единичный сигнал с прямого выхода триггера 5 открывает элемент 13 и обеспечивает возможность передачи кодов микроопераций с выхода регистра 3 на шину 14. Кроме того, этот же сигнал проходит через элемент ИЛИ 23, открывает элементы И 15 и 16 и тем самым разрешает прохождение тактовых импульсов t1 и t2 через элементы 15 и 16 соответственно.

Очередной импульс t2 с входа 30.2 устройства через элемент 16 проходит на синхровход регистра 3 и срезом производит запись в этот регистр нулевого кода с выхода 1.1 блока 1 (см.фиг. 3, формат ФО). Следующий импульс t1 поступает на синхровход триггера 5 и подтверждает его единичное состояние. Этот же импульс через элемент 15 проходит на синхровход и счетный вход счетчика 6. Поскольку счетчик 6 первоначально находится в нулевом состоянии, на выходе элемента ИЛИ 24 присутствует нулевой сигнал, обусловливающий работу счетчика 6 в режиме приема информации, и по срезу импульса t1 код "1...1" с выхода 1.4 блока 1 заносится в счетчик 6. Теперь на выходе элемента ИЛИ 24 образуется сигнал логической единицы и счетчик 6 переходит в режим счета. Очередной импульс t2 вновь фиксирует нулевой код в регистре 3.

Следующий импульс t1 через элемент И 15 поступает на счетный вход и синхровход счетчика 6 и срезом увеличивает содержимое счетчика 6 на единицу. Однако, поскольку код в счетчике 6 является единичным, добавление к нему единицы приводит к переходу счетчика 6 в состояние "0...0" (переполнению) и обусловливает возникновение на выходе переноса счетчика 6 импульса p. Нулевой код с информационного выхода счетчика 6 поступает на вход элемента 24, устанавливает на его выходе нулевой сигнал и вновь переводит счетчик 6 в режим приема информации. В то же время импульс p с выхода переноса счетчика 6 подается на синхровход и счетный вход счетчика 2. Учитывая, что на выходе 1.3 блока 1 в исходном состоянии присутствует единичный код (см. фиг.3, формат ФО) и на выходе элемента ИЛИ 22 соответственно присутствует сигнал логической единицы, счетчик 2 работает в режиме приема информации с выхода коммутатора 4, где находится адрес A

После записи адреса инициализации A

Одновременно отрицательный перепад уровня сигнала с входа 28.l через элементы 12.1-12.l-1 i-го устройства и элементы ИЛИ 26 j-х устройств (j ≠ 1) распространяется на синхровходы триггеров 19 и также переводит их в единичное состояние. Нулевые сигналы с инверсных выходов триггеров 19 блокируют соответствующие элементы И 17 и тем самым запрещают последующую модификацию состояния регистров 10 при появлении единичных сигналов передачи управления на входах 28.1-28. l-1 устройств в ходе реализации системой i-й микропрограммы. В то же время элементы И 18 j-х устройств открываются, что обусловливает возможность модификации состояния счетчиков 11 при приеме управления от других устройств системы. Таким образом, все устройства системы оказываются подготовленными к реализации фрагментов i-й микропрограммы. Временные диаграммы работы устройства в режиме инициализации (настройки) и выполнения фрагмента микропрограммы представлены на фиг. 4.

Теперь перейдем к рассмотрению работы i-го устройства.

Адрес A

В дальнейшем тактовые импульсы t2 производят перезапись кода микроопераций с выхода 1.1 блока 1 в регистр 3, а импульсы t1 инициируют последовательное увеличение кода, записанного в счетчике 6. Как только после поступления очередного импульса t1 счетчик 6 из состояния "1...1" возвращается в состояние "0. . .0", на выходе элемента 24 формируется нулевой сигнал, а на выходе переноса счетчика 6 появляется импульс p. Счетчик 6 вновь переходит в режим приема информации, а импульс p поступает на счетный вход и синхровход счетчика 2 и срезом фиксирует в нем адрес следующей микрокоманды (фиг.4). Указанный адрес с выхода счетчика 2 подается на адресный вход блока 1 и обеспечивает считывание очередной микрокоманды реализуемого фрагмента. Выполнение считанной микрокоманды аналогично выполнению первой микрокоманды.

Формирование исполнительного адреса следующей микрокоманды может осуществляться двумя способами: а) путем увеличения адреса текущей микрокоманды на единицу: б) путем приема адреса принудительного перехода Aп с выхода коммутатора 4, т.е. на основе реализации режима естественной и принудительной адресации следующей микрокоманды соответственно.

1. Допустим, что текущая микрокоманда имеет формат Ф1 (фиг.3). В этом случае на выходе 1.3 блока 1 находится нулевой код, а на выходе элемента ИЛИ 22 устанавливается сигнал логического нуля. Данный сигнал подается на управляющий вход (V) счетчика 2 и переводит счетчик 2 в режим счета. Импульс p с выхода переноса счетчика 6 поступает на счетный вход счетчика 2 и инициирует операцию прямого счета: адрес текущей микрокоманды A, размещенный в счетчике 2, увеличивается на единицу и, поступая далее на адресный вход блока 1, обеспечивает считывание следующей микрокоманды из ячейки с адресом A + 1.

2. Если текущая микрокоманда имеет формат Ф2 (фиг.3), то на выходе 1.3 блока 1 появляется адрес принудительного перехода Aп. Этот адрес через коммутатор 4 проходит на информационный вход счетчика 2, а также, будучи отличным от нулевого, формирует единичный сигнал на выходе элемента 22. Единичный сигнал с выхода элемента 22 поступает на управляющий вход счетчика 2 и переводит последний в режим приема информации. Импульс p с выхода переноса счетчика 6 поступает на синхровход счетчика 2 и производит запись адреса Aп. Адрес Aп с выхода счетчика 2 подается на адресный вход блока 1 и формирует на его выходе очередную микрокоманду выполняемого фрагмента микропрограммы.

Процесс выполнения рассматриваемого фрагмента i-й микропрограммы продолжается до тех пор, пока очередная (h + 1)-я микрокоманда не будет иметь формат Ф3.1 (Ф3.2) (фиг.3).

Предположим, что очередная считанная из блока 1 микрокоманда имеет формат Ф3.1. В этом случае i-е устройство завершает выполнение текущего фрагмента микропрограммы и переходит в режим передачи управления другому аналогичному устройству. На выходе 1.2 блока 1 появляется сигнал логической единицы (признак формата), на выходе 1.4 образуется код "11...10", а на выходе 1.3 формируется код номера модуля, которому осуществляется передача управления.

Единичный сигнал с выхода 1.2 блока 1 открывает элемент И 21, поступает на первый вход элемента И 20, разрешает работу дешифратора 7, поступает на K-вход триггера 5, а также подается на первый вход элемента ИЛИ 23 и подтверждает тем самым наличие единичного уровня сигнала на его выходе. Кроме того, единичный сигнал с выхода 1.2 блока 1 поступает на третий и четвертый управляющие входы коммутатора 4 и формирует на его выходе нулевой код. Одновременно код номера запускаемого (j-го) модуля поступает на информационный вход дешифратора 7 и возбуждает сигнал логической единицы на его j-м выходе. Единичный сигнал (сигнал инициализации) с j-го выхода дешифратора 7 проходит через элемент ИЛИ 12.j на выход 29.j передачи управления устройства и обеспечивает запуск j-го устройства, за которым закреплен следующий фрагмент i-й микропрограммы. Очередной тактовый импульс t2 с входа 30.2 устройства через элемент И 16 проходит на синхровход регистра 3 и обеспечивает запись в данный регистр кода микроопераций последней микрокоманды, установленного на выходе 1.1 блока 1. Код микроопераций с выхода регистра 3 через открытый элемент 13 передается на шину 14 и возбуждает заданные микрооперации.

Сигнал инициализации, формируемый i-м устройством, с выхода 29.j подается на вход 28.i j-го устройства и затем через элемент ИЛИ 26 проходит на первые входы элементов И 17 и 18, а также на синхровход триггера 19. Поскольку триггер 19 находится в состоянии логической единицы, нулевой сигнал с его инверсного выхода блокирует элемент 17 и запрещает прохождение сигнала инициализации на синхровход регистра 10, исключая тем самым возможность модификации признака выполняемой микропрограммы. В то же время нулевой сигнал с инверсного выхода триггера 19 открывает элемент И 18 и сигнал инициализации через элемент 18 проходит на первый вход элемента ИЛИ 25, вызывая изменение уровня сигнала на выходе элемента 25 с нулевого на единичный. По перепаду уровня сигнала с выхода элемента 25 содержимое счетчика 11 увеличивается на единицу и, таким образом, на выходе счетчика 11 образуется код номера очередной (в рассматриваемом случае - первой) процедуры передачи управления j-му устройству.

Образующийся код с выхода счетчика 11 в объединении с признаком i-й микропрограммы с выхода регистра 10 поступает на вход шифратора 9 и формирует на его выходе "жесткий" адрес начала соответствующего фрагмента i-й микропрограммы в блоке 1 A

Очередной импульс t1 появляющийся на входах 30.1 i-го и j-го устройств, одновременно вызывает следующие действия.

1. i-е устройство (устройство, передающее управление). Импульс t1 с входа 30.1 поступает на синхровход триггера 5, а также через элемент И 15 проходит на синхровход и счетный вход счетчика 6. Поскольку на K-входе триггера 5 установлен сигнал логической единицы - признак формата микрокоманды передачи управления Ф3.1, срез импульса t1 вызывает переход триггера 5 в нулевое состояние. Нулевой сигнал с прямого выхода триггера 5 блокирует элемент 13 и отключает выход регистра 3 от шины 14. В то же время, несмотря на появление нулевого сигнала на прямом выходе триггера 5, на выходе элемента 23 сохраняется единичный уровень сигнала и, таким образом, переключение триггера 5 не приводит к блокировке элементов 15 и 16. Так как счетчик 6 находится в нулевом состоянии и на выходе элемента ИЛИ 24 соответственно присутствует нулевой сигнал, счетчик 6 работает в режиме приема информации. Таким образом, по срезу импульса t1 с выхода элемента 15 в счетчик 6 переписывается код "11. ..10", присутствующий на выходе 1.4 блока 1; на выходе элемента 24 появляется сигнал логической единицы и счетчик 6 переходит в режим счета.

2. j-е устройство (устройство, принимающее управление). Импульс t1 поступает на синхровход триггера 5 и, так как на J-входе триггера 5 находится единичный сигнал инициализации, а на K-входе - нулевой сигнал - признак формата микрокоманды ФО, устанавливает триггер 5 в состоянии логической единицы. Единичный сигнал с прямого выхода триггера 5 открывает элемент 13 и, кроме того, проходит через элемент ИЛИ 23 на входы элементов И 15 и 16. Поскольку триггер 5 переводится в единичное состояние срезом импульса t1, в момент появления единичного сигнала на первом входе элемента 15 импульс t1 на его втором входе уже отсутствует и, следовательно, на выходе элемента 15 сохраняется нулевой сигнал. Состояние счетчика 6 также неизменно.

Очередной импульс t2 не вызывает никаких изменений.

Следующий импульс t1 поступает на синхровходы триггеров 5 i-го и j-го устройств и подтверждает их состояния. Одновременно этот импульс проходит через элементы 15 и вызывает: увеличение содержимого счетчика 6 i-го устройства на единицу и фиксацию кода "11...1" в счетчике 6 j-го устройства. Таким образом, на выходах счетчиков 6 обоих рассматриваемых устройств появляются коды "11. . .1", на выходах элементов ИЛИ 24 формируются сигналы логической единицы. Счетчик 6 j-го устройства переходит в режим счета.

Очередной импульс t2 вновь не вызывает никаких изменений.

Следующий импульс t1 снова подтверждает состояние триггеров 5 i-го и j-го устройства, а также проходит на выходы элементов И 15. Далее импульс t1 поступает на синхровходы и счетные входы счетчиков 6 рассматриваемых устройств и инициирует операции добавления единицы. Так как оба счетчика 6 (i-го и j-го устройств) находятся в состоянии "11...1", на их информационных выходах образуется код "00. ..0", а на выходах переноса одновременно возникают импульсы переполнения p. Счетчики 6 i-го и j-го устройств вновь возвращаются в режим приема информации.

Далее i-е устройство функционирует следующим образом. Импульс p с выхода переноса счетчика 6 поступает на счетный вход и синхровход счетчика 2 и, поскольку на выходе элемента 22 установлен сигнал логической единицы (обусловленный наличием ненулевого кода номера модуля на выходе 1.3 блока 1), а на выходе коммутатора 4 сформирован нулевой код (обусловленный блокировкой коммутатора 4 единичным сигналом с выхода 1.2 блока 1), обнуляет счетчик 2. На выходе блока 1 появляется микрокоманда формата ФО, размещенная в ячейке с нулевым адресом. В то же время импульс p через открытый элемент И 21 проходит на вход сброса регистра 3 и устанавливает данный регистр в нулевое состояние.

После появления на выходе блока 1 микрокоманды формата ФО на выходе 1.2 блока 1 формируется сигнал логического нуля. Этот сигнал поступает на управляющий вход дешифратора 7, формирует на всех выходах дешифратора 7 потенциал логического нуля и тем самым снимает сигнал инициализации с выхода 29.j. Одновременно этот же сигнал разрешает работу коммутатора 4, блокирует элементы И 20 и 21 и, кроме того, обусловливает появление нулевого уровня сигнала на выходе элемента ИЛИ 23. Нулевой сигнал с выхода элемента 23 закрывает элементы И 15 и 16, и подача импульсов t1 и t2, синхронизирующих работу элементов i-го устройства, прекращается.

Единичный код с выхода 1.3 блока 1 поступает на входы элемента ИЛИ 22, формирует на выходе элемента 22 сигнал логической единицы и, таким образом, переводит счетчик 2 в режим приема информации с выхода коммутатора 4. В регистре 10 по-прежнему зафиксирован код признака i-й микропрограммы, триггер 19 находится в состоянии логической единицы, а на выходе счетчика 11 присутствует код номера последней передачи управления i-му устройству; рассматриваемое устройство готово к реализации очередной процедуры приема управления со стороны другого аналогичного устройства и выполнению следующего фрагмента i-й микропрограммы.

Теперь рассмотрим ход работы j-го устройства (устройства, принимающего управление). Импульс p с выхода переноса счетчика 6 j-го устройства подается на синхровход и счетный вход счетчика 2 и срезом заносит в счетчик 2 адрес приема управления A

Таким образом, i-е устройство заканчивает работу и переходит в состояние ожидания, а j-е устройство начинает выполнение следующего фрагмента i-микропрограммы. Передача управления между другими устройствами в дальнейшем осуществляется аналогично. Временные диаграммы работы устройства в режиме приема и передачи управления представлены на фиг. 5.

Если реализованный фрагмент i-й микропрограммы для i-го устройства является последним, т. е. при дальнейшем выполнении данной микропрограммы другими устройствами запуск i-го устройства не предусмотрен, вместо микрокоманды формата Ф3.1 на выходе блока 1 появляется микрокоманда формата Ф3.2 (фиг. 3), отличающаяся от первой только наличием единичного признака конца микропрограммы в поле 1.5 формата микрокоманды. В силу идентичности содержимого полей 1.1-1.4 микрокоманд форматов Ф3.1 и Ф3.2 ход выполнения считываемой микрокоманды аналогичен ходу реализации микрокоманд формата Ф3.1 и имеет следующее единственное отличие.

Единичный сигнал с выхода 1.5 блока 1 открывает элемент И 20 и поэтому импульс p, возникающий на выходе переноса счетчика 6 после переполнения, через элемент И 20 проходит на входы сброса регистра 10, счетчика 11 и триггера 19 и возвращает их в состояние логического нуля. Единичный сигнал с инверсного выхода триггера 19 открывает элемент И 17 и блокирует элемент И 18, что обеспечивает возможность последующей записи в регистр 10 признака очередной выполняемой микропрограммы. Таким образом, i-е устройство переходит в исходное состояние и тем самым подготавливается к реализации фрагментов других микропрограмм.

В то же время завершение всех фрагментов i-микропрограммы, закрепленных за i-м устройством, в общем случае не означает окончания работы всей системы. Функционирование управляющей системы завершается только тогда, когда в ходе реализации некоторым s-м устройством i-й микропрограммы на выходе блока 1 появляется микрокоманда, имеющая формат Ф4 (фиг. 3). В этом случае на выходе 1.2 блока 1 формируется сигнал логической единицы - признак формата микрокоманды, на выходе 1.4 устанавливается единичный код (определяющий обработку данной микрокоманды без задержки), на выходе 1.5 аналогично микрокоманде формата Ф3.2 образуется единичный признак конца микропрограммы, а на выходе 1.3 блока 1 появляется нулевой код.

Единичный сигнал с выхода 1.2 блока 1 открывает элемент И 21, поступает на второй вход элемента И 20, блокирует коммутатор 4, подтверждает наличие единичного уровня сигнала на выходе элемента ИЛИ 23, а также поступает на K-вход триггера 5, подготавливая его переключению в состояние логического нуля. Этот же сигнал подается на управляющий вход дешифратора 7, однако, поскольку на информационный вход дешифратора 7 поступает нулевой код с выхода 1.3 блока 1, на его выходах сохраняется нулевой уровень сигнала и ни на одном из выходов 29.1-29.l-1 устройства не возникает единичный потенциал. Реализуется передача управления несуществующему (фиктивному) устройству с нулевым номером. Одновременно единичный сигнал с выхода 1.5 блока 1 через элемент ИЛИ 22 поступает на управляющий вход счетчика 2 и переключает его в режим приема информации. Этот же сигнал открывает элемент И 20.

Следующий импульс t1 поступает на синхровход триггера 5 и возвращает триггер 5 в нулевое состояние, обеспечивая блокировку элемента 13 запрета. Этот же импульс через элемент И 15 проходит на счетный вход и синхровход счетчика 6 и срезом инициирует перезапись в счетчик 6 кода "11...1". На выходе элемента ИЛИ 24 возникает единичный сигнал и счетчик 6 переходит в режим счета. Очередной импульс t1 подтверждает нулевое состояние триггера 5 и вновь через элемент 15 поступает на счетный вход и синхровход счетчика 6. По срезу импульса t1 счетчик 6 переполняется, переходит в состояние "00...0" и вырабатывает импульс переноса p.

Импульс p с выхода переноса счетчика 6, во-первых, поступает на счетный вход и синхровход счетчика 2 и заносит в него нулевой код, сформированный на выходе коммутатора 4, во-вторых, через элемент 21 подается на вход сброса регистра 3 и устанавливает его в состояние логического нуля и, в-третьих, проходит через элемент 20 и обнуляет регистр 10, счетчик 11, а также триггер 19. На выходе блока 1 вновь появляется микрокоманда формата ФО (фиг. 3), размещенная в ячейке с нулевым адресом, а единичный сигнал с инверсного выхода триггера 19 блокирует элемент И 18, одновременно открывая элемент И 17. На этом работа s-го устройства и управляющей системы в целом заканчивается, все модули системы находятся в исходном состоянии. Система готова к выполнению очередной микропрограммы.

Таким образом, введенные в устройство дополнительные элементы и обусловленные ими связи обеспечивают возможность организации многократного приема управления (запуска) устройства от другого аналогичного устройства с использованием множества фиксированных ("жестких") адресов. Наличие указанной возможности позволяет исключить ограничения, накладываемые на способ распределения фрагментов микропрограмм между различными устройствами, которые возникают в процессе построения управляющих систем на основе прототипа, и, следовательно, повышает функциональную гибкость и расширяет область целесообразного применения устройства.

Целесообразность использования предлагаемого технического решения поясним следующим примером.

Пусть требуется построить управляющую систему, реализующую алгоритм управления, представленный на фиг. 6а и содержащий десять вершин (каждой из которых соответствует одна микрокоманда) N= 10, при условии, что емкость блока 1 памяти микрокоманд W=5. Очевидно, что для реализации приведенного алгоритма (микропрограммы) необходимо построение системы, состоящей как минимум из двух идентичных устройств M1 и M2.

Первоначально разобьем алгоритм на два фрагмента T1={t1,..., t5} и T2={ t6, ..., t10} и закрепим фрагмент T1 за модулем M1, T2 - за модулем M2 (фиг. 6б). В данном случае множество микроопераций модуля M1 будет содержать микрооперации S1= { y1,...,y9} и, следовательно, разрядность операционной части микрокоманд будет равна m1=9. Аналогично для модуля M2: S2={y1, y2, y3, y6, y7, y9,... y14} и разрядность операционной части микрокоманд m2=11. Принятый способ разбиения алгоритма (микропрограммы) на фрагменты не является оптимальным, поскольку существует другой способ, позволяющий реализовать рассматриваемый алгоритм без управления числа модулей в составе управляющей системы и в то же время сократить разрядность операционной части микрокоманд как для первого, так и для второго модуля. Таким способом является следующий (фиг. 6в): T'1={t1, t3, t5, t6, t7}, T'2={t2, t4, t8, t9, t10}.

Закрепим выделенные фрагменты T'1 и T'2 за модулями M1 и M2 соответственно и получим следующие множества микроопераций: S1={y1,...,y4, y6, y11, y14} и S2={y4, y5, y7,...,y13}. Теперь разрядности операционных частей микрокоманд для модулей M1 и M2 будут равными соответственно m1=7, m2=9, т.е. уменьшатся на dm=2. Учитывая, что в случае использования второго (оптимального) способа разбиения микропрограммы на фрагменты в ходе выполнения микропрограммы необходимо осуществление трех передач управления от модуля M1 модулю M2 и двух - от модуля M2 модулю M1, реализация данного способа системой, построенной на базе прототипа, невозможна. Действительно, после выполнения модулем M1 микрокоманды t3 и передачи управления модулю M2 последний будет переходить не к микрокоманде t4, а вновь возвращаться к реализации микрокоманды t2.

В то же время при использовании предлагаемого устройства данный способ разбиения микропрограммы на фрагменты и распределения фрагментов микропрограммы между различными модулями является допустимым, поскольку адрес приема управления при реализации микропрограммы формируется, исходя из номера процесса передачи управления, и не зависит от номера модуля, передающего управление. Так после поступления сигнала инициализации от внешнего устройства имеет место первая передача управления модулю M1. Модуль M1 приступает к считыванию микрокоманды t1 по адресу A1. После выполнения модулем M2 микрокоманды t2 осуществляется вторая по порядку передача управления модулю M1 и теперь M1 производит считывание микрокоманды t3 по адресу A2 и т.д.

Таким образом, использование предлагаемого устройства в рассмотренном случае позволяет выбрать оптимальный (рациональный) способ распределения фрагментов микропрограмм и тем самым сократить длину операционной части микрокоманд. Кроме того, отсутствие ограничений на способ распределения фрагментов микропрограмм между различными устройствами повышает гибкость микропрограммирования управляющих систем. Описанные особенности предлагаемого технического решения подтверждают его преимущества по отношению к прототипу и обеспечивают возможность существенного расширения области применения устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

| УСТРОЙСТВО ПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2146064C1 |

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

| МОДУЛЬ СИСТЕМЫ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1998 |

|

RU2145434C1 |

| МОДУЛЬ МИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1997 |

|

RU2112272C1 |

| МОДУЛЬ МУЛЬТИМИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1999 |

|

RU2151421C1 |

| Устройство для программного управления | 1991 |

|

SU1800445A1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

Изобретение относится к автоматике и вычислительной технике. Применяется при построении систем управления технологическими процессами. Устройство содержит блок памяти микрокоманд, счетчик адреса, регистр микроопераций, счетчик времени задержки, коммутатор направления приема адреса, триггер режима, дешифратор направления передачи управления, шифратор признака микропрограммы, элемент запрета, шину микроопераций, пять элементов ИЛИ, шифратор адреса приема управления, регистр признака микропрограммы, счетчик количества передач управления, триггер настройки, группу элементов ИЛИ, шесть элементов И и элемент задержки. 6 ил.

Модульное устройство для программного управления, содержащее блок памяти микрокоманд, счетчик адреса, регистр микроопераций, счетчик времени задержки, коммутатор направления приема адреса, триггер режима, дешифратор направления передачи управления, шифратор признака микропрограммы, элемент запрета, шину микроопераций, первый и второй элементы И, с первого по четвертый элементы ИЛИ, причем входы шифратора признака микропрограммы с первого по l-й (где l - максимальное число идентичных устройств, образующих управляющую систему) соединены с входами инициализации устройства с первого по l-й соответственно, выход первого элемента ИЛИ подключен к J-входу триггера режима и к первому и второму управляющим входам коммутатора направления приема адреса, выход которого соединен с информационным входом счетчика адреса, выход которого соединен с адресным входом блока памяти микрокоманд, выход микроопераций которого подключен к информационному входу регистра микроопераций, выход которого соединен с информационным входом элемента запрета, выход которого подключен к шине микроопераций, выход признака формата блока памяти микрокоманд подключен к управляющему входу дешифратора направления передачи управления, к первому входу второго элемента ИЛИ и к К-входу триггера режима, прямой выход которого соединен с управляющим входом элемента запрета, а также с вторым входом второго элемента ИЛИ, выход которого подключен к первым входам первого и второго элементов И, выход адреса/номера модуля блока памяти микрокоманд соединен с информационным входом дешифратора направления передачи управления, с первым информационным входом коммутатора направления приема адреса и группой входов третьего элемента ИЛИ, выход которого соединен с управляющим входом счетчика адреса, выход времени задержки блока памяти микрокоманд подключен к информационному входу счетчика времени задержки, выход переноса которого соединен с синхровходом и счетным входом счетчика адреса, информационный выход счетчика времени задержки подключен к входам четвертого элемента ИЛИ, выход которого соединен с управляющим входом счетчика времени задержки, первый вход синхронизации устройства соединен с синхровходом триггера режима и с вторым входом первого элемента И, выход которого подключен к синхровходу и счетному входу счетчика времени задержки, второй вход синхронизации устройства является вторым входом второго элемента И, выход которого соединен с синхровходом регистра микроопераций, отличающееся тем, что в него дополнительно введены шифратор адреса приема управления, регистр признака микропрограммы, счетчик количества передач управления, триггер настройки, группа из (l-1) элементов ИЛИ, с третьего по шестой элементы И, пятый элемент ИЛИ и элемент задержки, причем входы инициализации устройства с первого по l-й соединены с соответствующими входами пятого элемента ИЛИ, выход которого подключен к первым входам третьего и четвертого элементов И и к синхровходу триггера настройки, на D-входе которого постоянно находится потенциал логической единицы, инверсный выход триггера настройки соединен с вторым (инверсным) входом третьего элемента И и с вторым входом четвертого элемента И, выход которого подключен к входу элемента задержки, выход которого подключен к синхровходу регистра признака микропрограммы, информационный вход которого соединен с выходом шифратора признака микропрограммы, выход третьего элемента И подключен к первому входу первого элемента ИЛИ, выход которого соединен со счетным входом счетчика количества передач управления, выход которого в объединении с выходом регистра признака микропрограммы подключены к входу шифратора адреса приема управления, выход которого соединен с вторым информационным входом коммутатора направления приема адреса, l-й вход инициализации устройства соединен с вторым входом первого элемента ИЛИ, а также с первыми входами первого, второго, ..., (l-1)-го элементов ИЛИ группы, вторые входы которых подключены к первому, второму, ..., (l-1)-му выходам дешифратора направления передачи управления соответственно, а выходы являются первым, вторым, ..., (l-1)-м выходами передачи управления устройства соответственно, выход признака формата блока памяти микрокоманд соединен с третьим и четвертым управляющими входами коммутатора направления приема адреса, с первым входом пятого элемента И и с первым входом шестого элемента И, выход которого соединен с входом сброса регистра микроопераций, выход переноса счетчика времени задержки подключен к второму входу шестого элемента И и к второму входу пятого элемента И, выход которого подключен к входам сброса регистра признака микропрограммы, счетчика количества передач управления и триггера настройки, выход признака конца микропрограммы блока памяти микрокоманд соединен с третьим входом пятого элемента И и с входом третьего элемента ИЛИ.

| FR, заявка, 2491654, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| РСТ, заявка, WO 86/04700, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| SU, кл | |||

| авторское свидетельство, 1800445, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1998-05-27—Публикация

1997-04-09—Подача