00

Изобретение относится к вычислительной технике и может быть использовано при построении узлов и устройств цифровых вьмислительных машин.

Цель изобретения - расширение функциональных возможностей регистра за счет выполнения операций счета и суммирования.

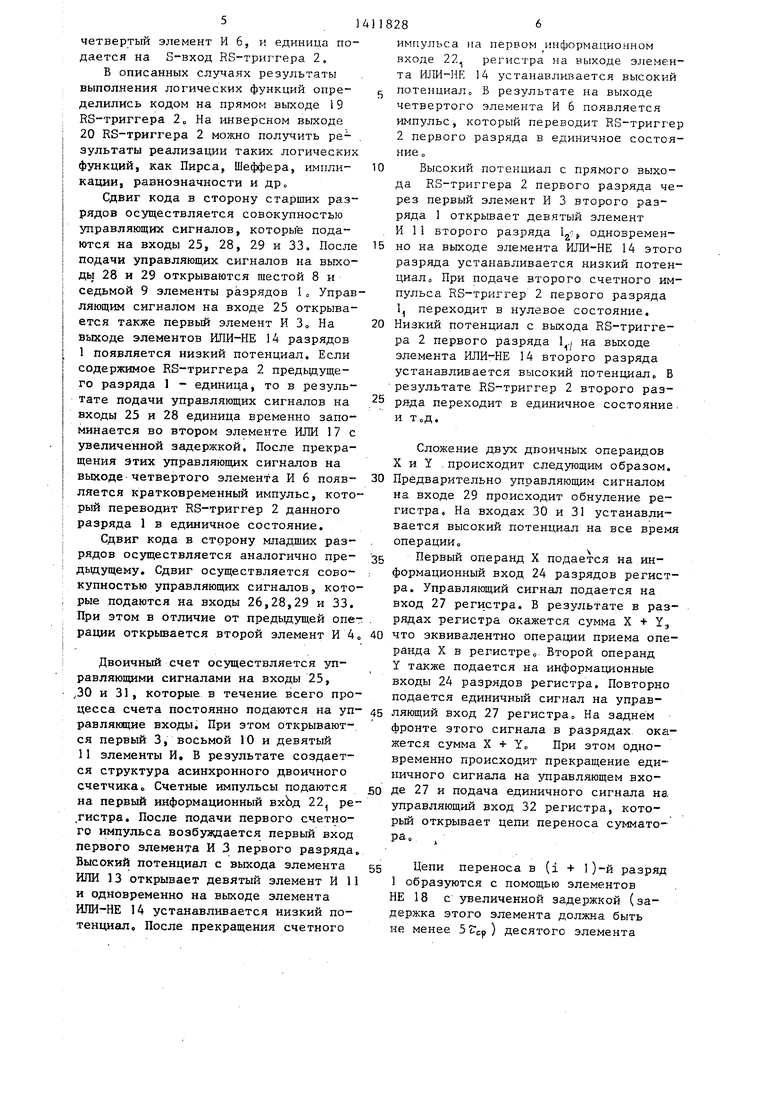

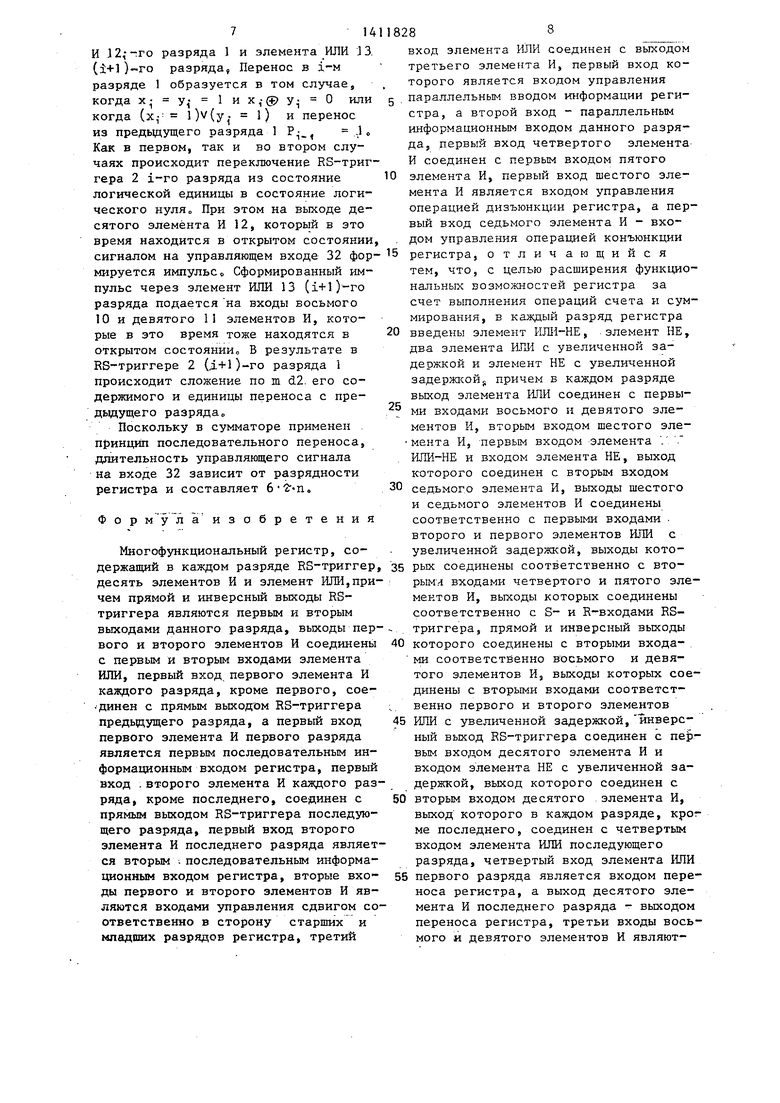

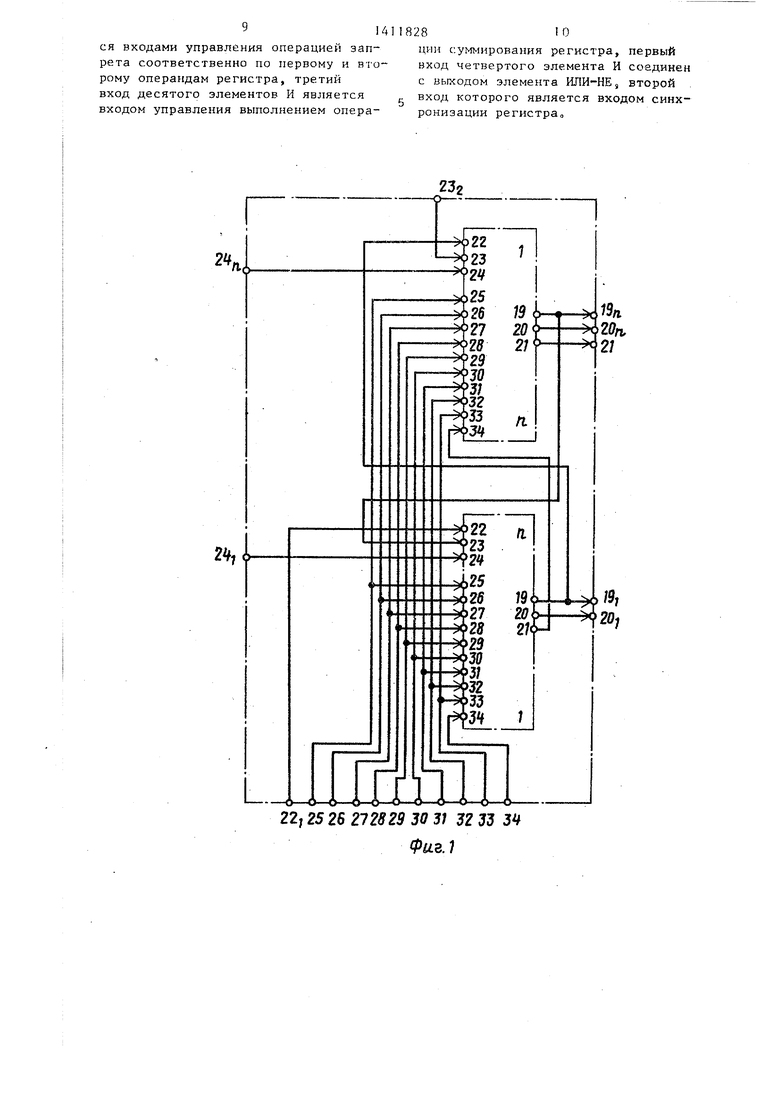

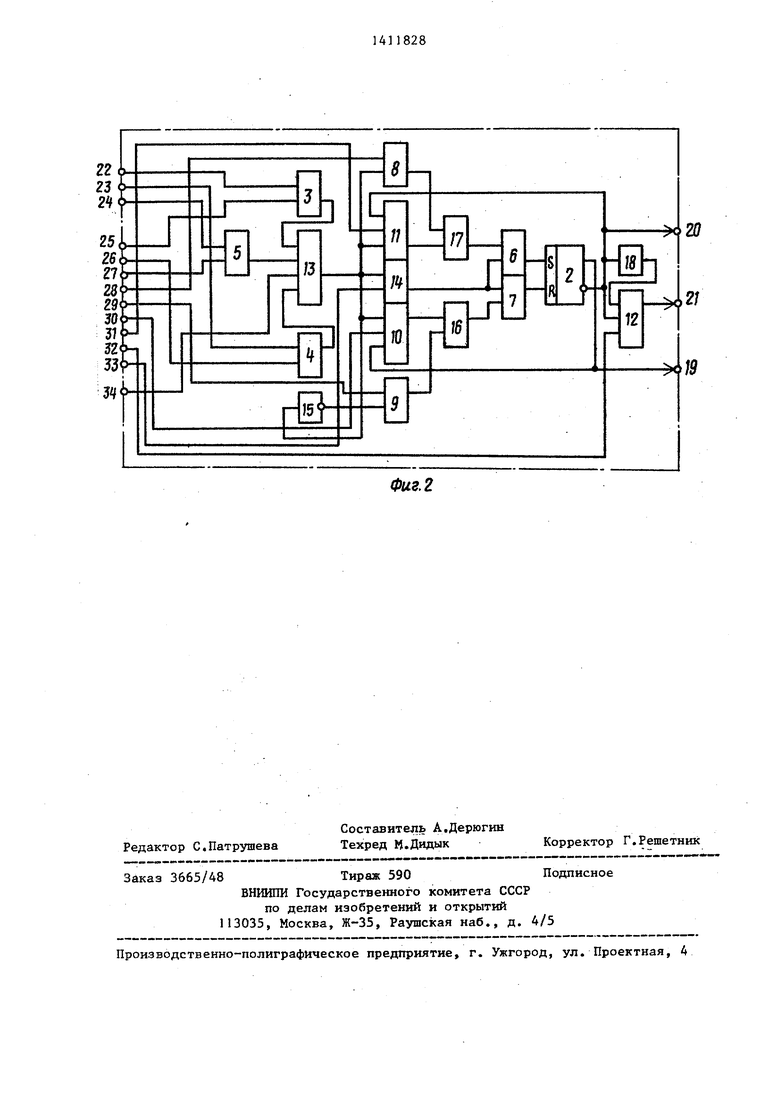

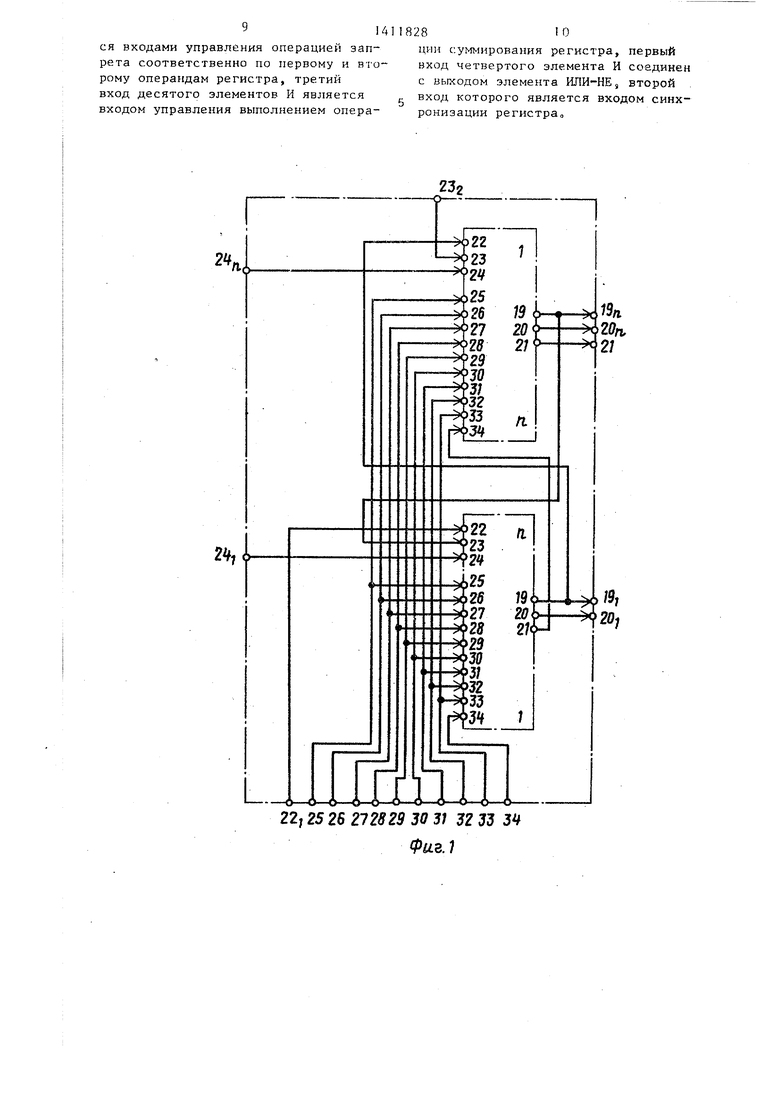

На представлена структурная схема многофункционального регистра; на фиг о 2 - схема одного его разряда

Многофункциональный регистр в каждом разряде 1 содержит RS-триггер 2, десять элементов И 3-12, элемент ИГШ 13, элемент ИЛИ-НЕ 14, элемент НЕ 15, два элемента ИЛИ 16 и 17 с увеличенной задержкой и элемент НЕ 18 с увеличенной задержкой

Прямой и инверсный входы RS-триг- гера 2 являются первым 19 и вторым 20 выходами данного разряда 1.

Многофункциональный регистр имеет . следующие информационные и управляю- щие входы и выходы: 19,- - первый (прямой)выход i-ro разряда регистра (i Ijn); 205 - второй (инверсный) выход i-ro разряда .регистра

(i Т,п); 21 - выход переноса реги- стра; 22 - первый последовательный информационный вход; 23 - второй пoc ледозательный шформационный вход; 241 параллельный информационный вход i-ro разряда регистра (1 1 п) 25 - вход управления сдвигом информации в сторону старших разрядов; 26 - вход управления сдвигом информации в сторону младших разрядов; 27 - вход управления параллельным приемом ин- формации; 28 - вход управления операцией дизъюнкции; 29 - вход управления операцией конъюнкции; 30 - вход управления операцией запрета по пер вому операнду; 31 - вход управления операцией запрета по второму операнду; 32 - вход управления выполнением операции суммирования; 33 - вход синхронизации регистра; 34 - вход переноса регистра

Четвертый 6 и пятый 7 элементы И, первый 16 и второй 17 элементы ИЛИ с увеличенной задержкой и элемент у ИЛИ-НЕ 14 разрядов 1 предназначены для формирования кратковременных импульсов. Основное назначение первого 16 и второго 17 элементов ИЛИ с увеличенной задержкой - кратковремен

5 0

5

0 5 0 5 0

ное хранение- информации с выходов элементов И 8 - 11„ Формирование импульсов на выходе четвертого 6 и пятого 7 элементов И происходит на заднем фронте управляющего сигнала Информационные сигналы одновременно поступают на вторые входы первого 16 и второго 17 элементов ИЛИ с увеличенной задержкой и на входе элемента ИЛИ-НЕ При поступлении единичного информационного сигнала на входы элемента ИЛИ-НЕ 14, на его выходе появляется нулевой сигнал, который закрывает четвертый 6 и пятый 7 элементы И После прекращения информационного сигнала открываются четвертый 6 и пятый 7 элементы И, которые остаются в открытом состоянии пока на выходе первого 16 и второго 17 элемента ИЛИ с увеличенной задержкой существует единичный сигнал При этом на выходе четвертого 6 или пятого 7 элемента И появляется кратковременный импульс Длительность и fflyльca t,;j,n должна быть не менее задержки переключения RS-триггера 2 - , Тое,. ммп тр о Таким образом, время задержки первого 16 и второго 7 элементов с увеличенной задержкой определяется г зе.д t-rp + э S где задержка элементов И 6 и 7 о

Длительность импульсных управляющих сигналов равна t, 6 Тер, Отметим также, что длительность паузы между очередными управляющими сигналами должна быть не менее

Многофункциональный регистр в разных режимах работает следуилцим образом

Рассмотрим как происходит обнуление регистра. С этой целью на вход 29 регистра подается управляющий сигнал, который открьшает седьмой элемент И 9 разряда 1, поскольку на втором входе седьмого элемента И 9 в данный момент находится единичный сигнал. Сигнал с выхода элемента И 9 через первый элемент ИЛИ 16 с увеличенной задержкой и пятый элемент И 7 (который в это время находится в открытом состоянии) подается на К-вход ЕБ-триггера 2 Обнуление также можно осуществить с помощью одновременной подачи управляющих сигналов на входы 29 и 33 регистра. При этом открывается седьмой элемент И 9 и на выходе первого элемента ИЛИ 16 с увеличенной задержкой

31

появляется логическая единица, однако открывание пятого элемента И 7 не происходит, поскольку на его-втором входе присутствует логический нуль, После прекращения управляющих сигналов на входах 29 и 33 на выходе элемента ИЛИ-НЕ и появляется высокий потенциал, который открьшает пятый элемент И 7„ В результате на его выходе появляется высокий потенциал, который существует в течение времени, достаточного для переключения RS-триггера из-за сохранения высокого потенциала на выходе элемента ИЛИ 16 с увеличенной задержкой

Код для ввода в регистр подается на информационные входы 24 24 разрядов }о Ввод осуществляется одновременной подачей совокупности управляющих сигналов на входы 27,28, 29 и 33 о Единичный сигнал подается на второй вход элемента ИЛИ-НЕ 14, соответственно на его выходе появляется низкий потенциал. Одновременно открываются третий 5, шестой 8 и пятый 9 элементы Ио Если вводимый код единица, то на второй вход шестого элемента И 8 подается высокий потенциал, а на второй вход седьмого элемента И 9 - низкий потенциало В результате на выходе шестого элемента И 8 появляется высокий потенциал, который поступает во второй элемент ИЛИ 17 с увеличенной задержкой. После превращения управляющих сигналов на втором входе четвертого элемента И 6 появляется высокий потенциал, в результате чего на S-вход RS-триггера 2 будет подана единица Если вво- .димый код нуль, то открывается соответственно седьмой 9 и пятый 7 эле менты И, и высокий потенциал подается на В-вход RS-триггера 2. Таким образом, в разрядах 1 происходит преобразование вводимого монофазного ко да в парафазный код и его запоминание, поэтому предварительная установка регистра на нуль не требуется.

Все логические функции в многофункциональном регистре выполняются на основе уравнения S + R + + Qt Будем считать, что операнд У находится в регистре, а операнд X подается на информационные входы 24,- регистры (i 1 ,п) е,

Для выполнения диз ьюнкции двух операндов X и Y следует операнд X подавать на информационные входы

1828-

разрядов 24 , , а Y предварительно записать в регистре, т„е, Q. У- Если Р. О и S X, то Qt, XVy, с С этой целью управляющие сигналы подаются на управляющие входы 27 и 28 регистра При этом срабатывают третий 5, щестой 8 и четвертый 6 элементы И и X подается на S-вход RS0 триггера 2 Если регистр управляющим сигналом на входе 29 предварительно установить в нулевое состояние, тогда 0.+ X, Тое осуществляется параллельный ввод кода

5 Для выполнения операции конъюнкции необходимо,чтобы S О и R X. . Если Q. Y, тогда Q, X Y, С этой целью следует управляющие сигналы подавать на входы 27 и 29 реги0 стра. При этом открываются седьмой элемент И 7, на первый вход которого через.элемент НЕ 15 подается инверсное значение операнда Х, В результате в RS-триггере 2 окажется произ5 ведение X Y

Запрет по X осуществляется на основе уравнения X Y, а запрет - на основе уравнения Qt,.

Q X Y. Запрет по X вьтолняется подачей управляющих сигналов на входы 27 и 31 регистра При этом открываются третий 5 и девятый 11 элементы И и сигнал в виде функции X Y подается на S-вход RS-триггерао Для осуществления операции запрета по Y сладует подавать управляющий сигнал на вход 30 регистра в сочетании с управлякяцим сигналом на входе 27, Если одновременно подавать управляющие сигналы на входы 27,30 и 31, тогда на прямом выходе RS-триггера 2 получим логическую функцию X-Y.VX-Y, .т.е. в RS-триггере окажется сумма

. X®Yo Открываются третий 5, восьмой 10 и девятый 11 элементы И разрядов 1, Пусть, например, Y. , .Х- подается на информационный вход 24 с При этом на выходе элемента ИЛИ-НЕ 14 появляется низкий потенци5

0

0

5

ал, а на выходе восьмого элемента И 10 - высокий потенциал После прекращения управляющих сигналов на входы 27, 30 и 31 высокий потенциал появляется на выходе элемента ИЛИ-НЕ 14, который открывает пятый элемент И 7о В результате RS-триггер 2 переходит в нулевое состояние. Если Y. О, то открывается соответственно

четвертый элемент И 6, к единица подается на S-вход RS-трнггера 2.

В описанных результаты выполнения логических функций определились кодом на прямом выходе i 9 RS-триггера 2„ На инверсном выходе 20 КЗ-триггера 2 можно получить результаты реализации таких логических функций, как Пирса, Шеффера, импликации, равнозначности и др.

Сдвиг кода в сторону старших разрядов осуществляется совокупностью управляющих сигналов, которы е подаются на входы 25, 28, 29 и 33. После подачи управляющих сигналов на выходы 28 и 29 открываются шестой 8 и седьмой 9 элементы разрядов 1, Управляющим сигналом на входе 25 открывается также первый элемент И Зо На выходе элементов ИЛИ-НЕ 14 разрядов 1 появляется низкий потенциал. Если содержимое RS-триггера 2 предьщуще- го разряда 1 - единица, то в результате подачи управляющих сигналов на входы 25 и 28 единица временно запоминается во втором элементе ИЛИ 17 с увеличенной задержкой. После прекращения Этих управляющих сигналов на выходе четвертого элемента И 6 появляется кратковременньш импульс, который переводит RS-триггер 2 данного разряда 1 в единичное состояние.

Сдвиг кода в сторону младших разрядов осуществляется аналогично предыдущему. Сдвиг осуществляется совокупностью управляющих сигналов, которые подаются на входы 26,28,29 и 33, При этом в отличие от предыдущей one рации открывается второй элемент И 4

Двоичный счет осуществляется управляющими сигналами на входы 25, ,30 и 31, которые в течение всего про

импульса на первом информационном входе 22 регистра на выходе элемента ИЛИ-НЕ 14 устанавливается высокий потенциал В результате на выходе четвертого элемента И 6 появляется импульс, который переводит RS-триггер 2 первого разряда в единичное состояние о

Высокий потенциал с прямого выхода RS-триггера 2 первого разряда через первый элемент И 3 второго разряда 1 открывает девятый элемент И 11 второго разряда , одновременно на выходе элемента Ш1И-НЕ 14 этого разряда устанавливается низкий потенциал При подаче второго счетного импульса RS-триггер 2 первого разряда Ц переходит в нулевое состояние. Низкий потенциал с выхода RS-триггера 2 первого разряда 1,/ на выходе элемента ИЛИ-НЕ 14 второго разряда устанавливается высокий потенциал Б результате RS-триггер 2 второго разряда переходит в единичное состояние. и т„д.

Сложение двух двоичных операндов X и Y .происходит следующим образом,

Предварительно управляющим сигналом на входе 29 происходит обнуление регистра. На входах 30 и 31 устанавливается высокий потенциал на все время операции

Первый операнд X подается на информационный вход 24 разрядов регистра. Управляющий сигнал подается на вход 27 регистра, В результате в разрядах регистра окажется сумма X + Y,

что эквивалентно оператдии приема операнда X в регистре. Второй операнд У также подается на информационные входы 24 разрядов регистра. Повторно подается единичный сигнал на управ

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный регистр сдвига | 1983 |

|

SU1176385A1 |

| Многофункциональный регистр | 1988 |

|

SU1624529A1 |

| Универсальный вычислительный автомат | 1983 |

|

SU1196844A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

| Функциональный преобразователь | 1991 |

|

SU1807498A1 |

| Устройство для программного управления позиционного типа | 1983 |

|

SU1158976A1 |

| Последовательный сумматор | 1989 |

|

SU1633392A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Вычислительное устройство | 1983 |

|

SU1167604A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении узлов и устройств цифровых вычислительных машин,, Целью изобретения является расширение функциональных возможностей регистра за счет выполнения операций счета и суммирования. Для зтого в каждый разряд регистра введены элемент ИЛИ-НЕ, элемент НЕ, два злемен- та ИЛИ с увеличенной задержкой и зле- мент НЕ с увеличенной задержкой. Как и прототип, регистр позволяет выполнять поразрядные логические функции, сдвиг в сторону старших и младших разрядов, а также функции после- довательного счетчика и накапливающего сумматора с последовательным петзеносом. 2 ил. (Л

десса счета постоянно подаются на уп- 45 ляющий вход 27 регистра На заднем

равляющие входы. При этом открываются первый 3, восьмой 10 и девятый 11 элементы И, В результате создается структура асинхронного двоичного счетчика Счетные импульсы подаются на первый информационный вхЬд 22 ре- .гистра. После подачи первого счетного импульса возбуяадается первый вход первого элемента И 3 первого разряда, Высокий потенциал с выхода элемента ИЛИ 3 открывает девятый элемент И 11 и одновременно на выходе элемента ШШ-НЕ 14 устанавливается низкий потенциал. После прекращения счетного

фронте этого сигнала в разрядах окажется сумма X Уо При этом одновременно происходит прекращение единичного сигнала на управляющем вхо- де 27 и подача единичного сигнала иа управляющий вход 32 регистра, который открывает цепи переноса сумматора. ,

Цепи переноса в (i + 1)-й разряд 1 образуются с помощью элементов НЕ 18 с увеличенной задержкой (задержка этого элемента должна быть не менее 5 2Гср ) десятого элемента

714

И ) 2, -го разряда 1 и элемента ИЛИ J 3. (1+1 )-го разряда, Перенос в i -M разряде 1 образуется в том случае, когда х- У{ 1 и х,-@) у- 0 или когда (х,-- l)v(y. 1) и перенос из предыдущего разряда 1 Р -J « Как в первом, так и во втором случаях происходит переключение RS-триг- гера 2 i-ro разряда из состояние логической единицы в состояние логического нуля При этом на выходе десятого элемента И 12, который в это время находится в открытом состоянии сигналом на управляющем входе 32 формируется импульс Сформированный импульс через элемент ИЛИ 13 (i+l)ro разряда подается на входы восьмого 10 и девятого 11 элементов И, которые в это время тоже находятся в открытом состояниио В результате в RS-триггере 2 (,1+1)-го разряда 1 происходит сложение по m 6.2. его содержимого и единицы переноса с пре- дьщущего разряда.,

Поскольку в сумматоре применен принцип последовательного переноса, длительность управляющего сигнала на входе 32 зависит от разрядности регистра и составляет .

Форм у л а изобретения

Многофункциональный регистр, содержащий в каждом разряде RS-триггер десять элементов И и элемент ИЛИ,причем прямой и инверсный выходы RS- триггера являются первым и вторым выходами данного разряда, выходы первого и второго элементов И соединены с первым и вторым входами элемента ИЛИ, первый вход первого элемента И каждого разряда, кроме первого, сое- динен с прямым выходом RS-триггера предьщущего разряда, а первый вход первого элемента И первого разряда является первым последовательным информационным входом регистра, первый вход .второго элемента И каждого разряда, кроме последнего, соединен с прямым выходом RS-триггера последующего разряда, первый вход второго элемента И последнего разряда является вторым - последовательным информационным входом регистра, вторые входы первого и второго элементов И являются входами управления сдвигом соответственно в сторону старших и младших разрядов регистра, третий

88

вход элемента ИЛИ соединен с выходом третьего элемента И, первый вход которого является входом управления

параллельным вводом информации регистра, а второй вход - параллельным информационным входом данного разряда, первый вход четвертого элемента И соединен с первым входом пятого элемента И, первый вход шестого элемента И является входом управления операцией дизъюнкции регистра, а первый вход седьмого элемента И - вхо- дом управления операцией конъюнкции

регистра, отличающийся

тем, что, с целью расширения функ1що- нальных возможностей регистра за счет выполнения операций счета и суммирования, в каждый разряд регистра

введены элемент ИЛ11-НЕ, -элемент НЕ, два элемента ИЛИ с увеличенной задержкой и элемент НЕ с увеличенной задерж1сой причем в каждом разряде выход элемента ИЛИ соединен с первыми входами восьмого и девятого элементов И, вторым входом шестого элемента И, первым входом элемента . . ШШ-НЕ и входом элемента НЕ, выход которого соединен с вторым входом седьмого элемента И, выходы шестого и седьмого элементов И соединены соответственно с первыми входами . второго и первого элементов ИЛИ с увеличенной задержкой, выходы которых соединены соответственно с вто- рым-.-i входами четвертого и пятого элементов И, выходы которых соединены соответственно с S- и Н-входами RSтриггера, прямой и инверсный выходы

которого соединены с вторыми входа- ми соответственно восьмого и девятого элементов И, выходы которых соединены с вторыми входами соответственно первого и второго элементов

ИЛИ с увеличенной задержкой,инверсный выход RS-TpHrrepa соединен с первым входом десятого элемента И и входом элемента НЕ с увеличенной задержкой, выход которого соединен с

вторым входом десятого элемента И, выход которого в каждом разряде, крог ме последнего, соединен с четвертым входом элемента ИЛИ последующего разряда, четвертый вход элемента 1ШИ

первого разряда является входом переноса регистра, а выход десятого элемента И последнего разряда - выходом переноса регистра, третьи входы восьмого и девятого элементов И являют-

ся входами управления операцией запрета соответственно по первому и второму операндам регистра, третий вход десятого элементов И является входом управления выполнением опера.

22,25 26 272829 30 31 32 J3 3 Фаг. 1

ции суммирования регистра, первый вход четвертого элемента И соединен с вькодом элемента ИЛИ-НЕ, второй вход которого является входом синхронизации регистра.

Фиг. 2

| Майоров С.А., Новиков Г.И, Принципы организации цифровых машин Л,: Машиностроение, 1974, с.130, рис | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

Авторы

Даты

1988-07-23—Публикация

1986-04-15—Подача