Изобретение относится к импульсной технике и может быть использовано в вычислительных и измерительных устройствах.

Целью изобретения является повышение надежности счетного устройства за счет построения схемы на основе одноступенчатого D-триггера.

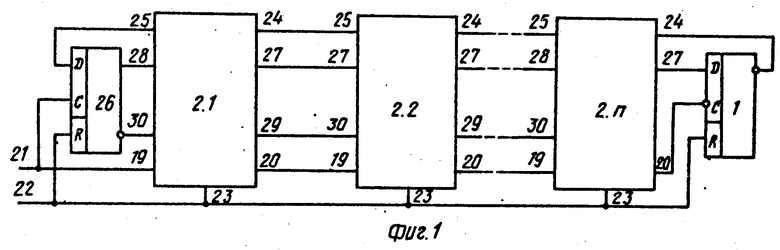

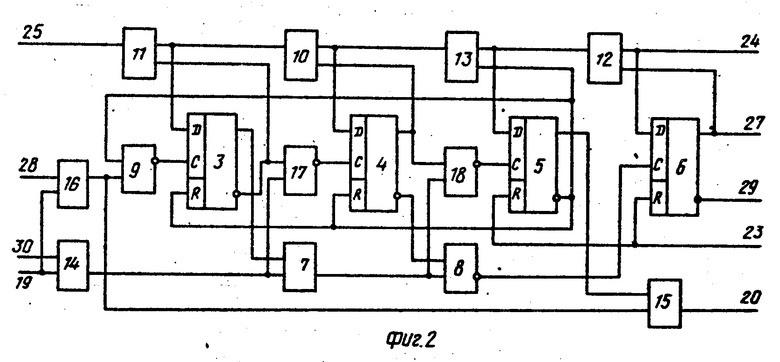

На фиг. 1 изображена схема счетного устройства; на фиг. 2 - отдельная группа разрядов счетного устройства.

Счетное устройство содержит первый дополнительный триггер 1, и в каждой группе 2 разрядов (фиг. 2) триггеры 3-6, логические элементы 7-18. Логические элементы 7, 14, 15 и 16 являются элементами ИЛИ, логические элементы 8, 9, 17 и 18 - элементами ИЛИ-НЕ, логические элементы 10-13 - элементами ИСКЛЮЧАЮЩЕЕ ИЛИ. Прямой выход триггера 3 соединен с первым входом логического элемента 7, выход которого соединен с первым входом логического элемента 8, выход логического элемента 10 - с первым входом логического элемента 11, выход логического элемента 12 - с первым входом логического элемента 13, выход логического элемента 14 - с вторым входом логического элемента 7, выход логического элемента 8 - с С-входом триггера 6, первый вход логического элемента 15 - с прямым выходом триггера 5, выход логического элемента 13 - с первым входом логического элемента 10, первый вход логического элемента 9 - с R-входами триггеров 3 и 4. Первый вход 19 логического элемента 14 каждой группы разрядов, кроме первой, соединен с выходом 20 логического элемента 15 предыдущей группы разрядов. Первый вход логического элемента 14 первой группы разрядов соединен с первым выходом 21 (фиг. 1) счетного устройства, второй вход 22 которого соединен с R-входами 23 триггеров 9 и 10 всех групп разрядов, выход 20 логического элемента 15 последней группы разрядов соединен с С-входом дополнительного триггера 1. Первый вход 24 логического элемента 12 каждой группы разрядов, кроме последней, соединен с выходом 25 логического элемента 11 последующей группы разрядов. Счетное устройство также содержит дополнительный триггер 26, а в каждой группе разрядов первый вход логического элемента 16 соединен с первым входом логического элемента 14, а выход - с вторыми входами логических элементов 9 и 15. С-входы триггеров 3-5 соединены с выходами соответственно логических элементов 9, 17 и 18, прямые выходы триггеров 4 и 6 во всех группах разрядов соединены соответственно с вторыми входами логических элементов 10 и 12.

D-входы триггеров 3-6 соединены соответственно с первыми входами логических элементов 11, 13 и 12. Второй вход логического элемента 8 соединен с инверсным выходом триггера 4, а первый вход - с первым входом логического элемента 18, второй вход которого соединен с прямым выходом триггера 4. Второй вход логического элемента 7 соединен с первым входом логического элемента 17, второй вход которого соединен с инверсным выходом триггера 3, инверсный выход триггера 5 - с вторым входом логического элемента 13 и первым входом логического элемента 9. Прямой выход 26 триггера 6 каждой группы разрядов, кроме последней, соединен с первым входом 27 логического элемента 16 последующей группы разрядов. Прямой выход 26 триггера 6 последней группы разрядов соединен с D-входом дополнительного триггера 1. Инверсный выход 28 триггера 6 каждой группы разрядов, кроме последней, соединен с вторым входом 29 логического элемента 14 последующей группы разрядов. D-вход второго дополнительного триггера соединен с выходом 25 логического элемента 11 первой группы разрядов, прямой выход - с первым выходом логического элемента 16 первой группы разрядов, инверсный выход - с вторым входом логического элемента 14 первой группы разрядов, в С-вход - с первым входом 21 счетного устройства. Инверсный выход дополнительного триггера 1 соединен с первым входом 24 логического элемента 12 последней группы разрядов. R-входы дополнительных триггеров 1 и 26 соединены с вторым входом 22 счетного устройства.

В качестве триггеров групп разрядов, а также в качестве дополнительных триггеров 1 и 26 в устройстве использованы одноступенчатые D-триггеры, причем триггеры групп разрядов и второй дополнительный триггер тактируются сигналом высокого уровня, а первый дополнительный триггер - сигналом низкого уровня.

Счетчик работает следующим образом.

По второму 22 входу установки на R-входы триггеров 1, 5, 6, 26 поступает импульс установки счетчика в исходное состояние. На инверсном выходе триггера 5 появляется сигнал высокого уровня, который обнуляет триггеры 3 и 4. С выхода 25 первой группы разрядов на D-вход триггера 26 поступает сигнал высокого уровня, свидетельствующий о том, что на входы поступает нечетное число логических "1" (по две - с каждой группы разрядов и одна - с инверсного выхода триггера 1). Счетными импульсами для счетчика по первому входу 21 являются сигналы низкого уровня, а для триггера 26 по С-входу тактовыми импульсами являются сигналы высокого уровня, т.е. паузы между счетными импульсами. Во время паузы между импульсом установки и первым счетным импульсом на С-вход триггера 26 поступает сигнал высокого уровня, и триггер 26 устанавливается в единичное состояние. При этом на вход 28 логического элемента 16 первой группы разрядов поступает сигнал высокого уровня, а на вход 19 логического элемента 14 первой группы разрядов - сигнал низкого уровня. Элементы ИЛИ 16, ИЛИ-НЕ 17 и 8 для счетного импульса заперты, а элементы ИЛИ 14 и 7, ИЛИ-НЕ 18 - открыты. Первый счетный импульс проходит через элементы ИЛИ 14 и 7, инвертируется элементом ИЛИ-НЕ 18 и в виде сигнала высокого уровня поступает на С-вход триггера 5, на D-вход которого воздействует сигнал высокого уровня, поступающий с логического элемента 12 и триггер 5 переключается в единичное состояние. При этом снимаются сигнал установки в "0" с R-входов триггеров 3 и 4 и сигнал запрета на прохождение счетного импульса - с второго входа элемента ИЛИ-НЕ 9, устанавливается сигнал запрета на второй вход элемента ИЛИ 15, число логических "1" в счетном устройстве становится четным, и на D-вход триггера 26 поступает сигнал низкого уровня. В паузе между первым и вторым счетными импульсами триггер 26 переключается в нулевое состояние. Элемент ИЛИ 14 для счетного импульса закрывается, а элемент ИЛИ 16 - открывается.

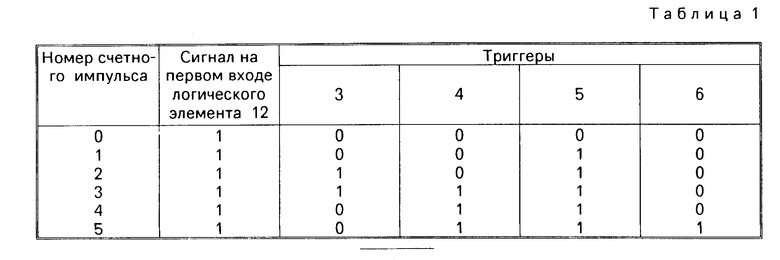

Второй счетный импульс проходит через элемент ИЛИ 16, инвертируется элементом ИЛИ-НЕ 9 и в виде сигнала высокого уровня поступает на С-вход триггера 3, на D-вход которого воздействует сигнал высокого уровня. Триггер 1 переключается в единичное состояние. При этом снимается сигнал запрета на прохождение счетного импульса через элемент ИЛИ-НЕ 17, устанавливается сигнал запрета на первом входе элемента ИЛИ 7, и на D-вход триггера 26 поступает сигнал высокого уровня. Во время паузы между вторым и третьим счетными импульсами триггер 26 переключается в единичное состояние. Третий счетный импульс проходит через элемент ИЛИ 14, инвертируется элементом ИЛИ-НЕ 17 и в виде сигнала высокого уровня поступает на С-вход триггера 4, на D-вход которого воздействует сигнал высокого уровня. Триггер 4 переключается в единичное состояние. При этом снимается сигнал запрета с второго входа элемента ИЛИ-НЕ 8, подается сигнал запрета на первый вход элемента ИЛИ-НЕ 18 и на D-вход триггера 26 поступает сигнал низкого уровня. Во время паузы между третьим и четвертым счетными импульсами триггер 26 переключается в нулевое состояние. В дальнейшем счетчик переключается в соответствии с табл. 1.

После прохождения девятого счетного импульса (в общем случае i.10-1-го импульса, где i = 1, 2, 3...) элементы ИЛИ 14 и ИЛИ-НЕ 9 для счетных импульсов заперты, а элементы ИЛИ 16 и 15 - открыты, и десятый счетный импульс (в общем случае i.10-й импульс, где i = 1, 2, 3...) проходит с первого входа 21 на вход 20 логического элемента 15 данной группы разрядов, не изменяя состояния триггеров 3-6, входящих в ее состав. Этот импульс является первым (для общего случая i-м, где i = 1, 2, 3...) счетным импульсом для следующей группы разрядов.

Запрещенные состояния счетной декады приведены в табл. 2.

Установка счетчика в запрещенное состояние, например в результате воздействия помехи, исключена благодаря воздействию сигнала высокого уровня с инверсного выхода триггера 5 на R-входы триггеров 3 и 4.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2037958C1 |

| Устройство для управления | 1986 |

|

SU1418650A1 |

| Устройство управления последовательностью операций цифрового вычислителя | 1984 |

|

SU1198521A1 |

| Реверсивный счетчик импульсов | 1982 |

|

SU1042185A1 |

| Устройство для кодирования | 1985 |

|

SU1287294A1 |

| Счетчик с накоплением | 1985 |

|

SU1269254A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| СЧЕТЧИК (ЕГО ВАРИАНТЫ) | 1983 |

|

SU1246864A1 |

| Формирователь сигналов специальной формы | 1988 |

|

SU1550604A1 |

| Счетчик импульсов с цифровой индикацией | 1984 |

|

SU1231602A1 |

Изобретение относится к импульсной технике, может быть использовано в вычислительных и измерительных устройствах. Цель изобретения - повышение надежности счетного устройства за счет построения схемы на основе одноступенчатых D-триггеров. Устройство содержит первый дополнительный триггер, в каждой группе разрядов четыре триггера, три элемента ИЛИ, четыре элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, два элемента ИЛИ - НЕ. Для достижения поставленной цели в устройство введены второй дополнительный триггер, элемент ИЛИ, два элемента ИЛИ - НЕ. 2 ил.

СЧЕТНОЕ УСТРОЙСТВО, содержащее первый дополнительный триггер и в каждой группе разрядов четыре триггера и девять логических элементов, из которых первый, восьмой и девятый выполнены в виде элементов ИЛИ, третий логический элемент выполнен в виде элемента ИЛИ - НЕ, четвертый, пятый, шестой, седьмой логические элементы выполнены в виде элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, прямой выход первого триггера соединен с первым входом первого логического элемента, выход которого соединен с первым входом второго логического элемента, выход четвертого логического элемента соединен с первым входом пятого, выход шестого логического элемента - с первым входом седьмого, выход восьмого логического элемента с вторым входом первого, выход второго логического элемента - с С-входом четвертого триггера, первый вход девятого логического элемента - с прямым выходом третьего триггера, выход седьмого логического элемента - с первым входом четвертого логического элемента, первый вход третьего логического элемента - с R-входами первого и второго триггеров, первый вход восьмого логического элемента каждой группы разрядов, кроме первой, - с выходом девятого логического элемента предыдущей группы разрядов, первый вход восьмого логического элемента первой группы разрядов - с первым входом счетного устройства, второй вход которого соединен с R-входами третьего и четвертого триггеров, выход с девятого логического элемента последней группы разрядов соединен с С-входом первого дополнительного триггера, первый вход шестого логического элемента каждой группы разрядов, кроме последней - с выходом пятого логического элемента последующей группы разрядов, отличающееся тем, что, с целью повышения надежности, в него введены второй дополнительный триггер и в каждую группу разрядов - десятый логический элемент, выполненный в виде элемента ИЛИ, одиннадцатый и двенадцатый логические элементы, выполненные в виде элементов ИЛИ - НЕ, первый, второй, третий и четвертый триггеры каждой группы разрядов и второй дополнительный триггер выполнены в виде одноступенчатых D-триггеров с тактированием сигналами высокого уровня, а первый дополнительный триггер выполнен в виде одноступенчатого D-триггера с тактированием сигналами низкого уровня, в каждой группе разрядов второй логический элемент выполнен в виде элемента ИЛИ - НЕ, первый вход десятого логического элемента соединен с первым входом восьмого, а выход - с вторыми входами третьего и девятого, С-входы первого, второго, третьего триггеров соединены с выходами соответственно третьего, одиннадцатого и двенадцатого логических элементов, прямые выходы второго и четвертого триггеров соединены соответственно с вторыми входами четвертого и шестого логических элементов, D-входы первого, второго, третьего и четвертого триггеров соединены соответственно с первыми входами пятого, четвертого, седьмого и шестого логических элементов, второй вход второго логического элемента соединен с инверсным выходом второго триггера, а первый вход - с первым входом двенадцатого логического элемента, второй вход которого соединен с прямым выходом второго триггера, второй вход первого логического элемента соединен с первым входом одиннадцатого, второй вход которого соединен с инверсным выходом первого триггера, инверсный выход третьего триггера соединен с вторым входом седьмого и первым входом третьего логических элементов, прямой выход четвертого триггера каждой группы разрядов, кроме последней, соединен с первым входом десятого логического элемента последующей группы разрядов, прямой выход четвертого триггера последней группы разрядов соединен с D-входом первого дополнительного триггера, инверсный выход четвертого триггера каждой группы разрядов, кроме последней, соединен с вторым входом восьмого логического элемента последующей группы разрядов, D-вход второго дополнительного триггера соединен с выходом пятого логического элемента первой группы разрядов, прямой выход - с первым входом десятого логического элемента первой группы разрядов, инверсный выход - с вторым входом восьмого логического элемента первой группы разрядов, а С-вход - с первым входом счетного устройства, инверсный выход первого дополнительного триггера соединен с первым входом шестого логического элемента последней группы разрядов, R-входы первого и второго дополнительных триггеров соединены с вторым входом счетного устройства.

| СЧЕТЧИК (ЕГО ВАРИАНТЫ) | 1983 |

|

SU1246864A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1994-11-15—Публикация

1985-11-05—Подача