Изобретение относится к контрольно- измерительной технике и может быть использовано для контроля микросхем полупроводниковой памяти или других микросхем, содержащих триггерные ячейки.

Цель изобретения - расширение функциональных возможностей способа путем обеспечения возможности прогнозирования работоспособности микросхем в диапазоне температур и отбраковки потенциально негодных микросхем и довышение достовер- 10 нбети за счет исключения пропуска микросхем, потенциально негодных в диапазоне температур. ;

Сущность способа заключается в следующем.

Основной причиной отказа полупровод- никовых запоминающих устройств (ЗУ) является отказ отдельных ячеек памяти, выполненных, например, на триггерах, связанный с недостаточным уровнем коэффициентов усиления транзисторов, составляющих элемент памяти, либо с большим уровнем токов утечки.

Как правило, отказавщие в диапазоне рабочих температур ячейки памяти имеют отклонение параметров температуре.

Отклонение параметров отдельных ячеек памяти связано с локальной дефектностью, а следовательно, не может быть выявлено при технологическом контроле в процессе производства.

Для нахождения дефектных ячеек памяти необходимо оценить параметры каждой ячейки, входящей в состав накопителя ЗУ.

Общим параметром, зависящим и от величины коэффициента усиления и от уровня

ленного заряда и, следовательно, при последующем считывании информация не соответствует ранее записанной.

Время снятия питания, равное времени рассасывания избыточного заряда, можно рассчитать по формуле

/с.п X , 2n//vfi(l-awa,-)

где /с.п. - время снятия питания;

/л/, /, - предельные частоты прямого и инверсного коэффициентов передачи;

aN, а,- - прямой и инверсный коэффициенты передачи тока в схеме с общей базой;

PN, р, - прямой и инверсный коэффициенты передачи тока в схеме с общим эмиттером.

Например, исходя из требуемых парамет- „,. ров ячеек памяти, было рассчитано время снятия питания, которое для микросхем оперативного запоминающего устройства (ОЗУ) серии 185РУ4 составило 150 мкс.

В микросхемах ОЗУ серии 185 РУ4, которые проверили на функционирование на устаи при комнатной 25 новке «1 КОМАТ-ПО, подвергали контролю параметры ячеек памяти по дополнительной тестовой последовательности.

30

Сначала производят запись «1 последовательно во все ячейки памяти, затем переводят микросхемы в режим хранения. После этого снимают питающее напряжение микросхемы до «О в течение 150 мкс (время равное времени рассасывания избыточного заряда). После истечения 150 мкс подают питающее напряжение (для данного приметоков утечки, является время рассасывания 35 ра оно равно 5 В), а затем переводят микро40

избыточного заряда открытого плеча триг- герной ячейки памяти, которое уменьшается с увеличением токов утечки и ухудшением параметров транзисторов, в частности, при уменьшении их коэффициента усиления.

Сравнивая время рассасывания избыточного заряда в ячейке памяти с эталонном, можно выявить дефектные ячейки, так как для них вследствие малых коэффициентов усиления и больших токов утечки время рассасывания меньше допустимого (эталон- 45 ного).

При отключении питающего напряжения полупроводникового ЗУ происходит выключение генератора тока, задающего ток через ячейки памяти, начинается рассасывание избыточного заряда, накопленного во включенном элементе ячейки памяти (триггерная ячейка состоит из двух элементов - вентилей), а так как время снятия питания устанавливают равным времени рассасывания избыточного заряда для ячеек памяти, имеющих расчетный уровень параметров, обеспечивающих работоспособность ЗУ в диапазоне температур, то в дефектных ячейках памяти происходит полное рассасывание накоп50

55

схемы в режим считывания; при этом производят считывание «1 последовательно во всех ячейках памяти. В случае наличия при считывании «О вместо «1 микросхему бракуют, поскольку за время /с.п одна из ячеек памяти этой микросхемы успела переключиться, а значит время рассасывания транзистора в открытом элементе этой ячейки памяти меньше допустимого, что свидетельствует о заниженном значении его коэффи-- циента усиления и увеличенном значении тока утечки. Такая микросхема является потенциально ненадежной при работе в диапазоне температур.

Аналогичным образом производят проверку и отбраковку при записи и считывании «О.

Для подтверждения указанного способа были установлены адреса отказавших ячеек на забракованных микросхемах и замерены параметры транзисторов, составляющих ячейку памяти.

Прямые коэффициенты усиления оказались заниженными в 2-3 раза в дефектных ячейках памяти, а часть ячеек имели значительную величину тока утечки.

Сначала производят запись «1 последовательно во все ячейки памяти, затем переводят микросхемы в режим хранения. После этого снимают питающее напряжение микросхемы до «О в течение 150 мкс (время равное времени рассасывания избыточного заряда). После истечения 150 мкс подают питающее напряжение (для данного примера оно равно 5 В), а затем переводят микро

5

0

5

схемы в режим считывания; при этом производят считывание «1 последовательно во всех ячейках памяти. В случае наличия при считывании «О вместо «1 микросхему бракуют, поскольку за время /с.п одна из ячеек памяти этой микросхемы успела переключиться, а значит время рассасывания транзистора в открытом элементе этой ячейки памяти меньше допустимого, что свидетельствует о заниженном значении его коэффи-- циента усиления и увеличенном значении тока утечки. Такая микросхема является потенциально ненадежной при работе в диапазоне температур.

Аналогичным образом производят проверку и отбраковку при записи и считывании «О.

Для подтверждения указанного способа были установлены адреса отказавших ячеек на забракованных микросхемах и замерены параметры транзисторов, составляющих ячейку памяти.

Прямые коэффициенты усиления оказались заниженными в 2-3 раза в дефектных ячейках памяти, а часть ячеек имели значительную величину тока утечки.

Указанным способом контроля были отбракованы микросхемы, потенциально негодные для работы в диапазоне температур, причем отбраковка осуществлена при комнатной температуре.

Таким образом, кратковременное отключение напряжения питания на время /с.п позволяет выявить потенциально негодные микросхемы полупроводниковой памяти, к числу которых относятся микросхемы, ячейки памяти которых успевают переключиться за время /с.п, что расширяет функциональные возможности способа и повышает достоверность контроля за счет исключения незабра- кования потенциально негодных микросхем.

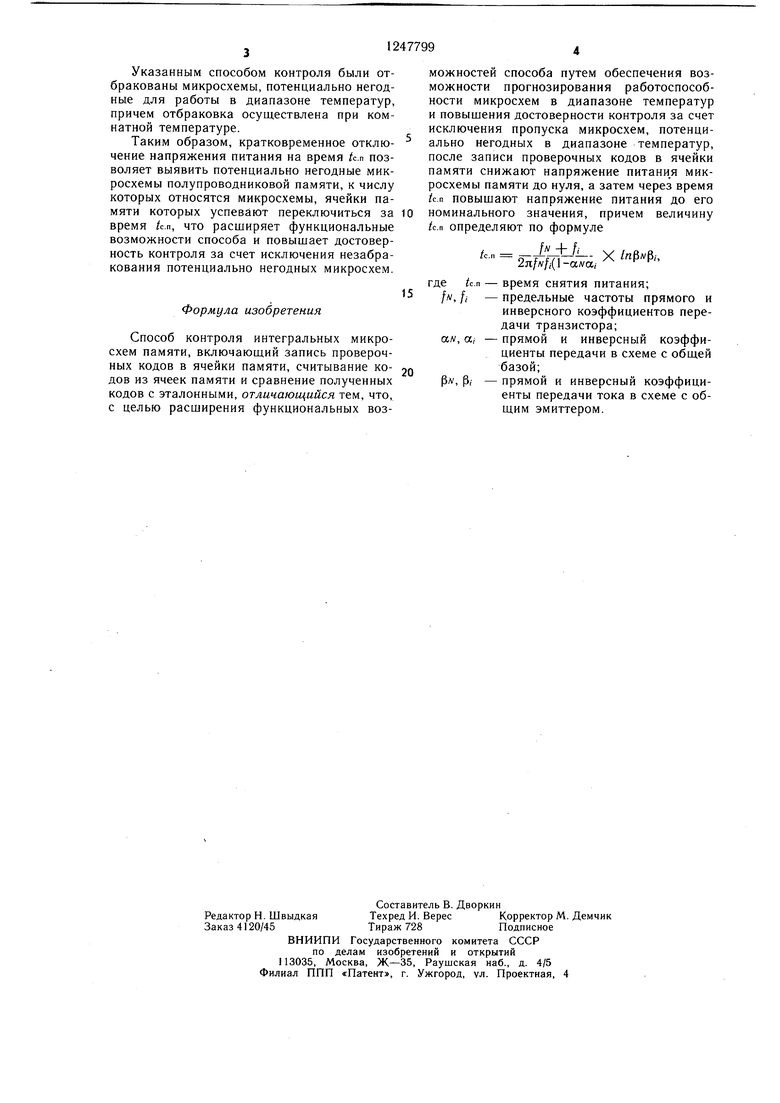

Формула изобретения

Способ контроля интегральных микросхем памяти, включающий запись проверочных кодов в ячейки памяти, считывание ко- дов из ячеек памяти и сравнение полученных кодов с эталонными, отличающийся тем, что, с целью расширения функциональных воз

можностей способа путем обеспечения возможности прогнозирования работоспособности микросхем в диапазоне температур и повышения достоверности контроля за счет исключения пропуска микросхем, потенциально негодных в диапазоне температур, после записи проверочных кодов в ячейки памяти снижают напряжение питани я микросхемы памяти до нуля, а затем через время /с.п повышают напряжение питания до его номинального значения, причем величину /с.п определяют по формуле

/с.п X 2nfNfi(-a.Na.i

где с.п - время снятия питания;

IN, fi - предельные частоты прямого и инверсного коэффициентов передачи транзистора;

aw, а, - прямой и инверсный коэффициенты передачи в схеме с общей базой;

PW, р,- - прямой и инверсный коэффициенты передачи тока в схеме с общим эмиттером.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ контроля интегральных микросхем памяти | 1987 |

|

SU1594458A1 |

| СПОСОБ РАЗБРАКОВКИ МИКРОСХЕМ ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА ПО УРОВНЮ БЕССБОЙНОЙ РАБОТЫ | 2008 |

|

RU2371731C1 |

| Способ тестирования микросхем энергонезависимой памяти и устройство для его осуществления | 2023 |

|

RU2821349C1 |

| СПОСОБ РАЗБРАКОВКИ ПАРТИИ ИНТЕГРАЛЬНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ ПО РАДИАЦИОННОЙ СТОЙКОСТИ | 2003 |

|

RU2249228C1 |

| Оперативное запоминающее устройство | 1978 |

|

SU868831A1 |

| МЕТОДЫ НЕРАЗРУШАЕМОГО СЧИТЫВАНИЯ ИНФОРМАЦИИ С ФЕРРОЭЛЕКТРИЧЕСКИХ ЭЛЕМЕНТОВ ПАМЯТИ | 2006 |

|

RU2383945C2 |

| Способ контроля ТТЛ итегральных схем | 1989 |

|

SU1675804A1 |

| ЦИФРОВОЙ КРЕМНИЕВЫЙ ФОТОУМНОЖИТЕЛЬ ДЛЯ ВРП-ПЭТ | 2006 |

|

RU2411542C2 |

| Способ контроля микросхем со скрытыми дефектами | 1987 |

|

SU1511721A1 |

| ЯЧЕЙКА ЭНЕРГОНЕЗАВИСИМОЙ ЭЛЕКТРИЧЕСКИ ПЕРЕПРОГРАММИРУЕМОЙ ПАМЯТИ | 2010 |

|

RU2436190C1 |

Изобретение относится к контрольно- измерительной технике. Может использоваться для контроля микросхем (МКС) но- лупроводниковой памяти или других МКС, содержащих триггерные ячейки. Цель изобретения - расширение функциональных возможностей способа - достигается путем обеспечения возможности прогнозирования работоспособности МКС в диапазоне температур и отбраковки потенциально негодных МКС и повышения достоверности за счет исключения пропуска МКС, потенциально негодных в диапазоне температур. Способ предусматривает кратковременное отключение напряжения питания на время tc.n - время снятия питания, что позволяет выявить потенциально негодные МКС полупроводниковой памяти, к числу которых относятся МКС, ячейки памяти которых успевают переключиться за время tc.n. Величину с.п определяют по математической формуле, приведенной в описании изобретения. Способ предусматривает также запись проверочных кодов в ячейках памяти, их считывание и сравнение полученных кодов с эталонными. i л 1C

| Шумное Д | |||

| В., Николаевский И | |||

| Ф | |||

| Транзисторы в микрорежиме | |||

| М.: Советское радио, 1978, с | |||

| Пюпитр для работы на пишущих машинах | 1922 |

|

SU86A1 |

| Способ контроля ТТЛ интегральных схем | 1982 |

|

SU1056088A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Измерение параметров цифровых интегральных микросхем | |||

| Под редакцией Эйдука- са Д | |||

| Ю | |||

| М.: Радио и связь, 1982, с | |||

| Спускная труба при плотине | 0 |

|

SU77A1 |

Авторы

Даты

1986-07-30—Публикация

1985-02-08—Подача