Изобретение относится к контрольно-измерительной технике и может быть использовано для контроля микросхем полупроводниковой памяти или других микросхем, содержащих триг- герные ячейкио

Целью изобретения является увеличение достоверности контроля за счет выявления потенциально дефектных ячеек памяти.

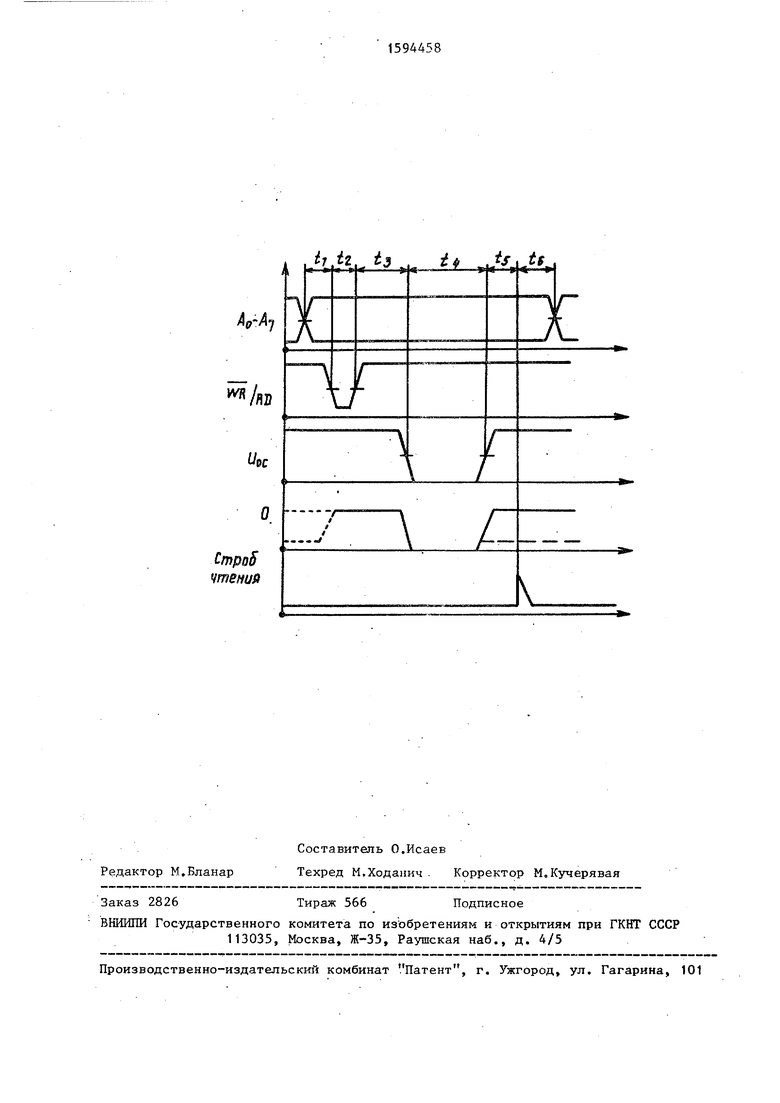

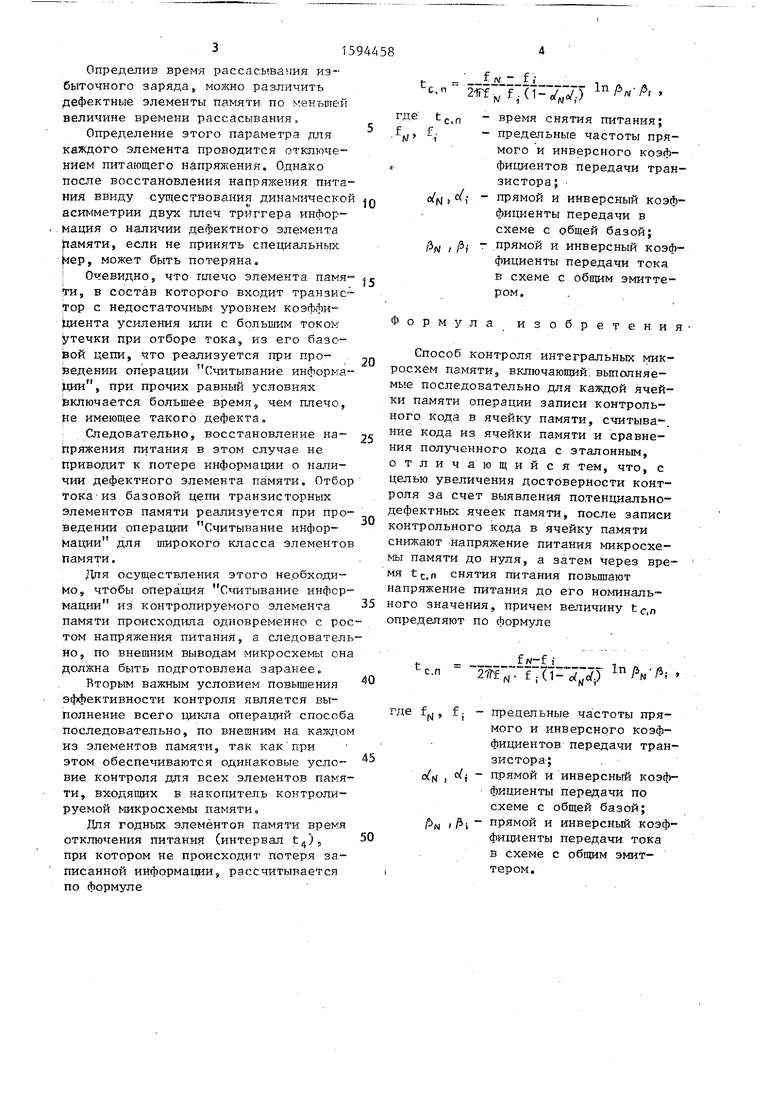

На чертеже представлены временные диаграммы способа контроля для интегральных микросхем.

Основной причиной отказа отдельньк ячеек памяти является недостаточный уровень коэффициента усиления транзисторов, входящих в элемент памяти, либо большой уровень токов утечки.

Как правило, отказавшие в диапазоне рабочих температур элементы памяти имеют отклонение этих же параметров и при нормальной температуре, которое связано с локальной дефектностью, а следовательно, может быть выявлено при технологическом контроле в процессе производства о

Для нахождения дефектных элементов памяти необходимо оценивать параметры каждой ячейки памяти, входящей в состав накопителя ЗУ.

Общим параметром, зависящим от величины коэффициента усиления и от 5ФОВНЯ токов утечки, является время рассасывания избыточного заряда ранее открытого плеча элемента памяти.

СД

сд

00

15

Определив время рассасывания избыточного зарядаS можно различить дефектные элементы памяти по меньвтей величине времени рассасывания.

Определение этого параметра для каждого элемента проводится отключением питающего напряясения. Однако после восстановления напряжения питания ввиду существования динамичесвюй асимметрии двух плеч триггера информация о наличии дефектного элемента- памяти, если не принять специальных , может быть потеряна. I Очевидно5 что плечо элемента памя™ №, в состав которого входит транзистор с недостаточным уровнем коэффи- икента усиления или с большим током утечки при отборе тока, из его базовой цепи, ато реализуется при про- зедении операции Считывание информации, при прочих равный условиях бключается большее время, чем плечо, не имеющее такого дефекта, i Следовательно, восстановление напряжения питания в этом случае не Приводит к потере информации о наличии дефектного элемента памяти. Отбор Тока-из базовой цепи транзисторных элементов памяти реализуется при про- йеден1-ш операщ-ш Считывание информации для широкого класса элементов памяти.

осуществления этого необходимо, чтобы операция Считывание информации из контролируемого элемента памяти происходила одновременно с ростом напряжения питания, а следовательно, по внешним выводам микросхемы она должна быть подготовлена заранее.

Вторым важным условием повышения эффективности контроля является выполнение всего цикла операций способа последовательно, по внешним на кажд:ом из элементов памяти, так как гфи этом обеспечиваются одинаковые условие контроля для всех элементов памяти, входящих в накопитель контролируемой микросхемы памяти,

Дпя годных элементов памяти время отключения питания (интервал t), при котором не происходит потеря записанной информации, рассчитывается по формуле

С,п

frv- f,()

где f...

с,г1 время снятия питания;

f,. - предельные частоты прямого и инверсного коэффициентов передачи транзистора;

, c/f - прямой и инверсный коэффициенты передачи в схеме с общей базой;

I -Прямой И инверсный коэффициенты передачи тока в схеме с общим эмиттером.

Ф о р м зг

л а

и

обретени

Способ контроля интегральных микросхем памяти, включающий, вьтолняе- мые последовательно для каждой ячейки памяти операции записи контрольного кода в ячейку памяти, считывание кода из ячейки памяти и сравнения полученного кода с эталонным, отличающийся тем, что, с целью увеличения достоверности контроля за счет выявления потенциально- дефектных ячеек памяти, после записи контрольного кода в ячейку памяти снижают Напряжение питания микросхемы памяти до нуля, а затем через время tc.n снятия питания повьшают напряжение питания до его номиналь- ного значения, причем величину t.n определяют по формуле

40

С.П

- fw-fj 1 f()

0

5

где f.

N

f

предельные частоты прямого и инверсного коэффициентов передачи транзистора-;

) 1 ггрямой и инверсный коэффициенты передачи по схеме с общей базой;

AN Ai прямой и инверсный коэффициенты передачи тока в схеме с общим эмиттером.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ контроля интегральных микросхем памяти | 1985 |

|

SU1247799A1 |

| Способ тестирования микросхем энергонезависимой памяти и устройство для его осуществления | 2023 |

|

RU2821349C1 |

| СПОСОБ РАЗБРАКОВКИ МИКРОСХЕМ ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА ПО УРОВНЮ БЕССБОЙНОЙ РАБОТЫ | 2008 |

|

RU2371731C1 |

| СПОСОБ РАЗБРАКОВКИ ПАРТИИ ИНТЕГРАЛЬНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ ПО РАДИАЦИОННОЙ СТОЙКОСТИ | 2003 |

|

RU2249228C1 |

| Способ регистрации логического состояния ячейки сегнетоэлектрической памяти для предотвращения потери данных при чтении и выявлении ячеек с повышенной степенью деградации и устройство блока для его реализации | 2024 |

|

RU2840059C1 |

| УСТРОЙСТВО ТЕЛЕКОНТРОЛЯ АБОНЕНТОВ | 1997 |

|

RU2114458C1 |

| Ячейка памяти на основе комплементарных МОП-транзисторов | 1989 |

|

SU1640738A1 |

| Устройство для контроля микросхем памяти (его варианты) | 1984 |

|

SU1166180A1 |

| ИНТЕГРИРОВАННАЯ В СБИС ТЕХНОЛОГИИ КМОП/КНИ С n+ - И p+ - ПОЛИКРЕМНИЕВЫМИ ЗАТВОРАМИ МАТРИЦА ПАМЯТИ MRAM С МАГНИТОРЕЗИСТИВНЫМИ УСТРОЙСТВАМИ С ПЕРЕДАЧЕЙ СПИНОВОГО ВРАЩЕНИЯ | 2012 |

|

RU2515461C2 |

| Устройство для программирования микросхем постоянной памяти | 1982 |

|

SU1134964A1 |

Изобретение относится к контрольно-измерительной технике в микроэлектронике и предназначено для отбраковки запоминающих устройств, имеющих дефектные ячейки памяти. Целью изобретения является увеличение достоверности контроля за счет выявления потенциально дефектных ячеек памяти. Для каждой ячейки памяти проводится цикл операций: запись информации, снижение напряжения питания микросхемы до нуля, выдержка в этом состоянии на время достаточное для рассасывания избыточного заряда в дефектных ячейках, установление режима считывания по внешним выводам микросхемы, повышение напряжения питания до напряжения, лежащего в области устойчивой работы микросхемы, считывание информации и сравнение ее с записанной ранее. 1 ил.

| Способ контроля интегральных микросхем памяти | 1985 |

|

SU1247799A1 |

| кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Конопелько В.К., Лосев В.В Надеж- ное хранение информации в полупроводниковых запоминающих устройствах.- М.: Радио и связь, 1986, с.93. | |||

Авторы

Даты

1990-09-23—Публикация

1987-12-08—Подача