ЬА) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупроводниковое запоминающее устройство с произвольной выборкой | 1984 |

|

SU1215135A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Полупроводниковое запоминающее устройство | 1978 |

|

SU748508A1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2047919C1 |

| Устройство для контроля полупроводниковой оперативной памяти | 1981 |

|

SU991516A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU949721A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU262181A1 |

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1986 |

|

SU1439679A1 |

| Оперативное запоминающее устройство | 1985 |

|

SU1283854A1 |

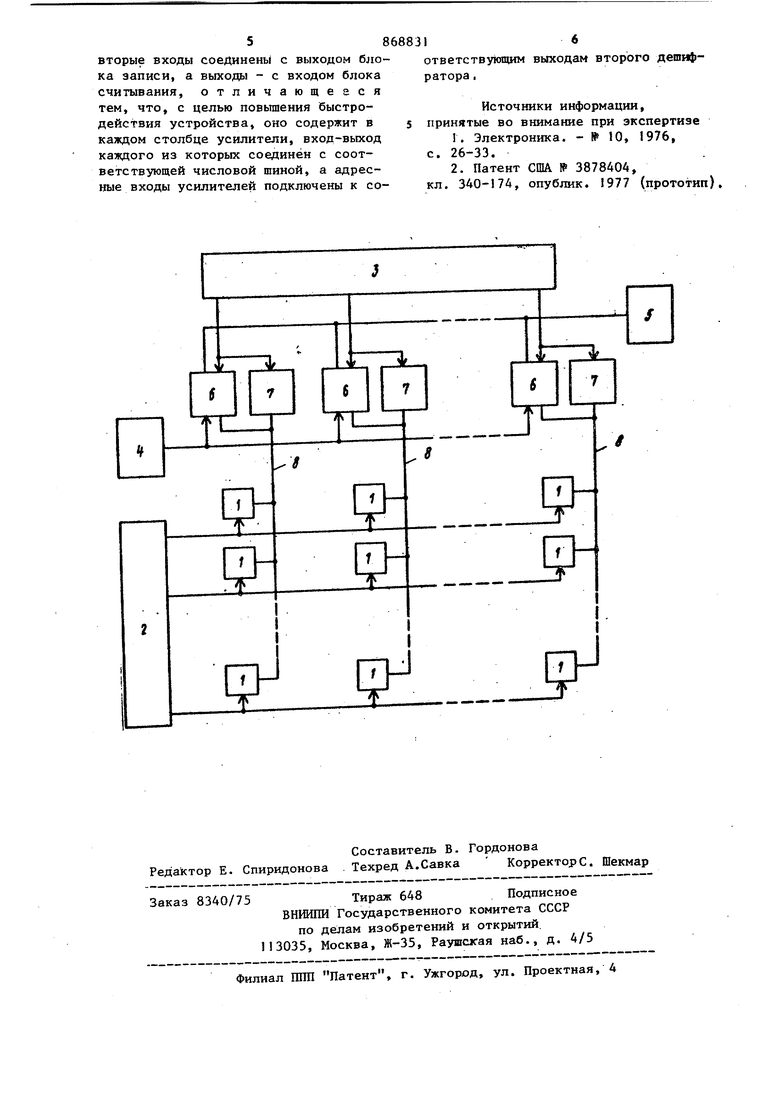

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам. Известны динамические МДП-оператив ные запоминающие устройства {ОЗУ), на пример, ТМ 4070 и. Обязательным злементом динамического ОЗУ является столбцовый усилитель считывания (усилитель считывания регенерации). В функции этих усилителей входят усиление сигналов считывания в режиме считьюания и работа в составе схемы регенерации совместно с таймером и коммутационным устройством. Назначение схемы регенерации - восстановление информации во всех ячейках памяти, где она хранится в виде заряда на запоминающем конденсаторе и с течением времени разрушается в результате действия токов утечки. Известны МЦП оперативные запоминаю щне устройстия (ОЗУ), выполненные на базе ячеек памяти (ЯТТ) с внутренней .p.4UMi;rt 122 Недостатком этих устройств является низкое быстродействие, обусловленное большой дпительностью процесса регенерации в ячейках памяти выбранной строки накопителя. Известно оперативное запоминающее устройство, которое содержит ячейки памяти с внутренней регенерацией, два дешифратора, блоки записи и считывания блоки управления в каждом cVan6ЦеНедостатком указанного устройства является низкое быстродействие, обусловленное длительным процессом регенерации в полувыбранных ЯП, т. е. в ячейках выбранной строки матрицы, Условия регенерации в таких ЯП существенно отличаются от условий регенерации в не выбран Hbjx ЯП, так как в последних в процессе регенерации информация считывается на небольшую по величине внутреннюю емкость ЯП, тогда как в полувыбранных ячейках к этой емкости добавляется несоизмеримо болыпая 38 емкость числовой шины. Следовательно, в полувыбранных ЯП регенерация уже не является внутренней. Время считывания информации из вь ранной ЯП при достаточно чувствительном усилителе считывания значительно меньше времени тыяания из полувыбранных ячеек при регенерации информации в последних. Таким образом, время цикла в ОЗУ, выполненном на базе ЯП с внутренней регенерацией, определяется временем регенерации в полувыбранных ячейках. Цель изобретения - повышение быстродействия оперативного запоминающего устройства, выполненного на базе ячеек памяти с внутренней регенерацией. Поставленная цель достигается feM, что в оперативное запоминающее устройство. содержащее ячейки памяти, соединенные по матричной схеме, два дешифратора, блоки записи и считывания, блок управления в каждом столбце, причем выходы первого дешифратора соединены с адресными входами соответствующих ячеек памяти, информационные входы ВЫХОДЫ которых соединены с входамивыходами соответствующих блоков управления, первые входы которых соединены с выходами второго дешифратора вторые входы соединены с вькодом блока записи, а выходы - с входом блока считывания, введены усилители в кажды столбец, вход-выход каждого из которых соединен с соответствующей Числовой шиной соответствующего столбца, а адресные входы усилителей Подключены к соответствующим выходам второго дешифратора. На чертеже изображено оперативное запоминающее устройство. Устройство содержит ячейки 1 памяTVi; первый дешифратор 2, второй дешиф ратор 3, блок 4 записи, блок 5 считывания, блоки 6 управления, усилители 7; числовую шину 8. В оперативном запоминающем устройстве выходы первого дешифратора 2 соединены с адресными . входами соответствующих ячеек памяти J информационные входы-выходы которых соединены с входами-выходами соот ветствующих блоков управления 6, первые входы которых соединены с вьпсодами второго дешифратора 3, вторые входы соединены с выходом блока 4 записи а выходы - с входом блока 5 считывания , вход-выход каждого из усилителей 7 соединен с соответствующей числовой шиной 8, а адресный вход - с соответс вующим выходом второго дешифратора 3. 1 Устройство работает следующим образом. В режиме считывания или записи дешифратор 2 возбуждает одну из строк матрицы, отпирая адресные транзисторы во всех ЯП 1 этой строки. Одновременно с дешифратором 2 работает дешифратор 3, возбуждающий блок 6 управления в одном из столбцов матрицы. Блок управления подключает выбранную числовую шину 8 к блоку 5 считывания в режиме считывания или блоку 4 записи в режиме записи. Одновременно с считыванием или записью в выбранную ЯП, во всех остальных ячейках происходит регенерация. В процессе регенерации информации в полувыбранных ЯП заряд соответствующих числовых шин осуществляется лишь до уровня напряжения, определяемого чувствительностью усилителей 7. Далее регенерация осуществляется через усилители 7, которые форсируют заряд соответствующих числовых шин. В режиме записи усилитель 7 выбранного столбца отключается сигна: ом соответствующего выхода дешифратора 3. При реализации изобретения в ОЗУ с инЛоомапионной емкостью 1024 бита (микросхема К535 РУ2) усилители 7 занималиплощадь кристалла около 0,7 мм при общей площади кристалла 19,5 мм . В то же время они позволяют уменьшить длительность тактового импульса считывания с 1,25 МКС до 0,5 МКС и сделать минимальное время цикла равным 2 мкс (вместо 2,5 в микросхеме К 535 РУ 2). Таким образом, исследования экспериментальных образцов предлагаемого изобретения показьшгцот, что увеличение площади кристалла на 3,6% позволяет повысить быстродействие более чем на 25%. Формула изобретения Оперативное запоминающее устройство, содержащее ячейки памяти, соединенные по матричной схеме, два дешифратора, блоки записи и считывания, блок управления в каждом столбце, причем выходы первого дешифратора соединены с адресными входами соответствующих Ячеек памяти, информационные входывыходы которых соединены с входамивыходами соответствующих блоков управления, первые входы которых соединены с выходами второго дешифратора.

вторые входы соединены с выходом блока эаписи, а выходы - с входом блока считывания, отличающегся тем, что, с целью повьппения быстродействия устройства, оно содержит в каждом столбце усилители, вход-выход каждого из которых соединён с соответствующей числовой шиной, а адресные входы усилителей подключены к соответствующим выходам второго дешифратора ,

Источники информации, принятые во внимание при экспертизе

кл. 340-174, опублик. 1977 (прототип).

Авторы

Даты

1981-09-30—Публикация

1978-07-04—Подача