Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении отказоустойчивых вычислительных комплексов повышенной надежности .

Цель изобретения - уменьшение времени контроля вычислительного комплекса в регламентном режиме за счет исключения проверок неисправных структур и уменьшение времени восстановления работоспособной структуры вычислительного комплекса за счет переключения на каждом шаге восстановления максимально допустимого числа его функциональных блоков.

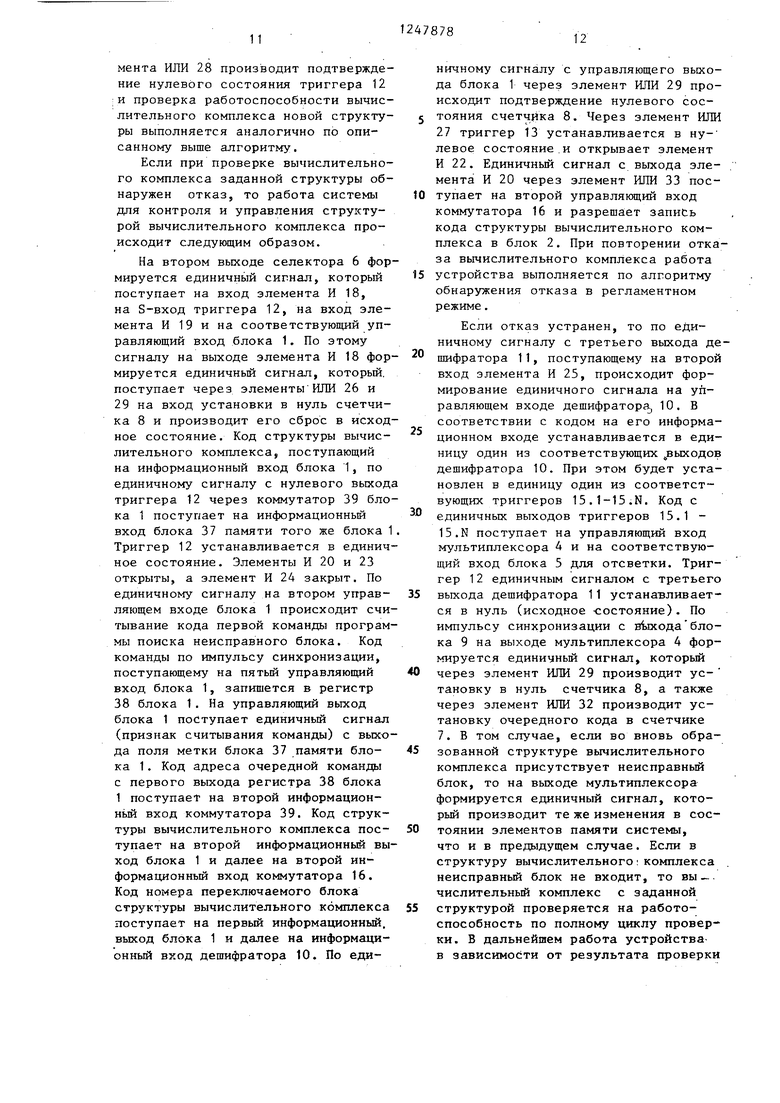

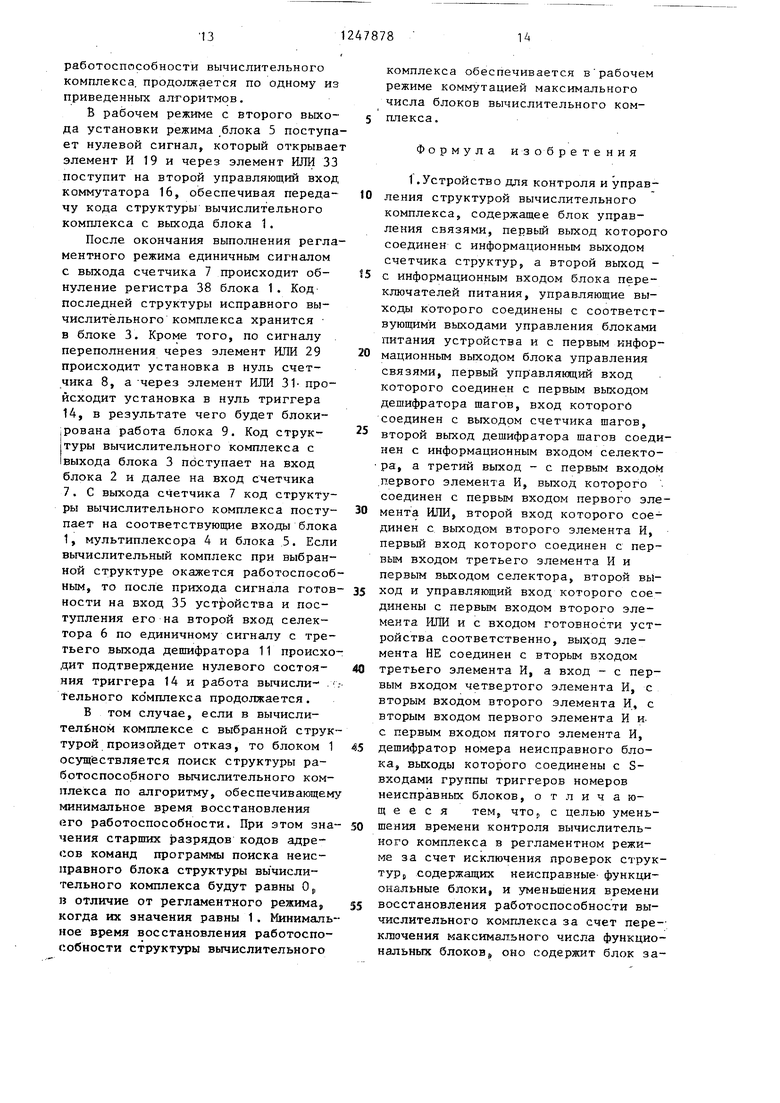

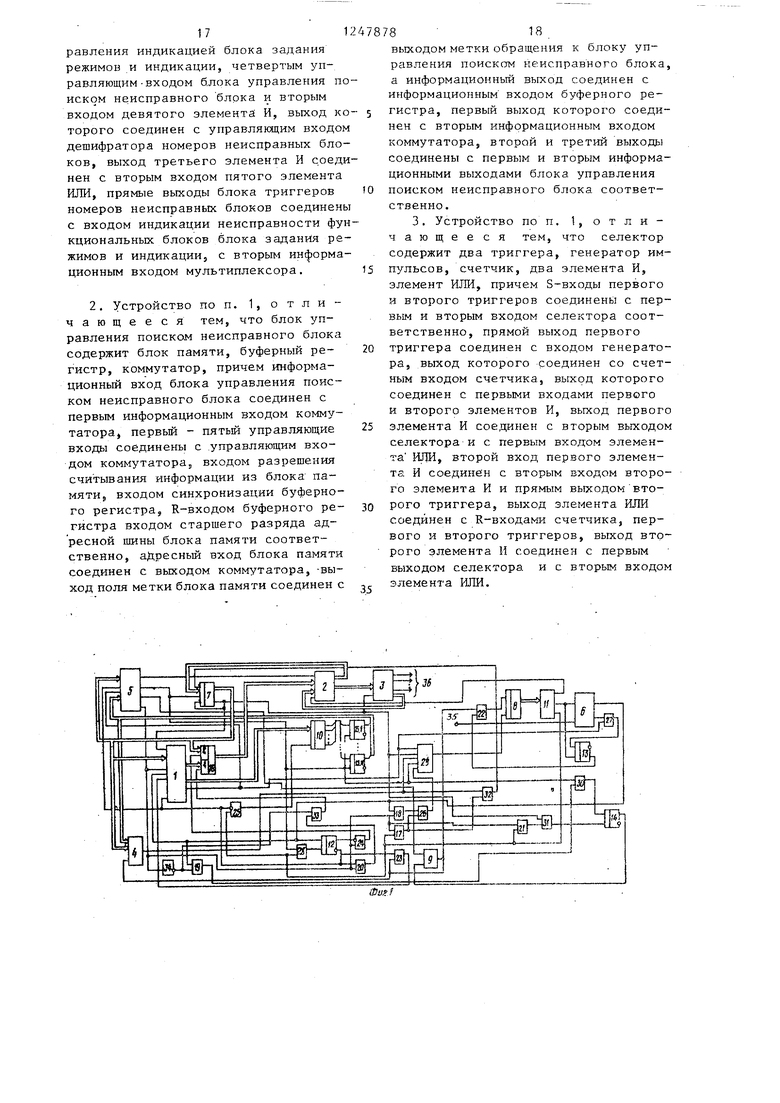

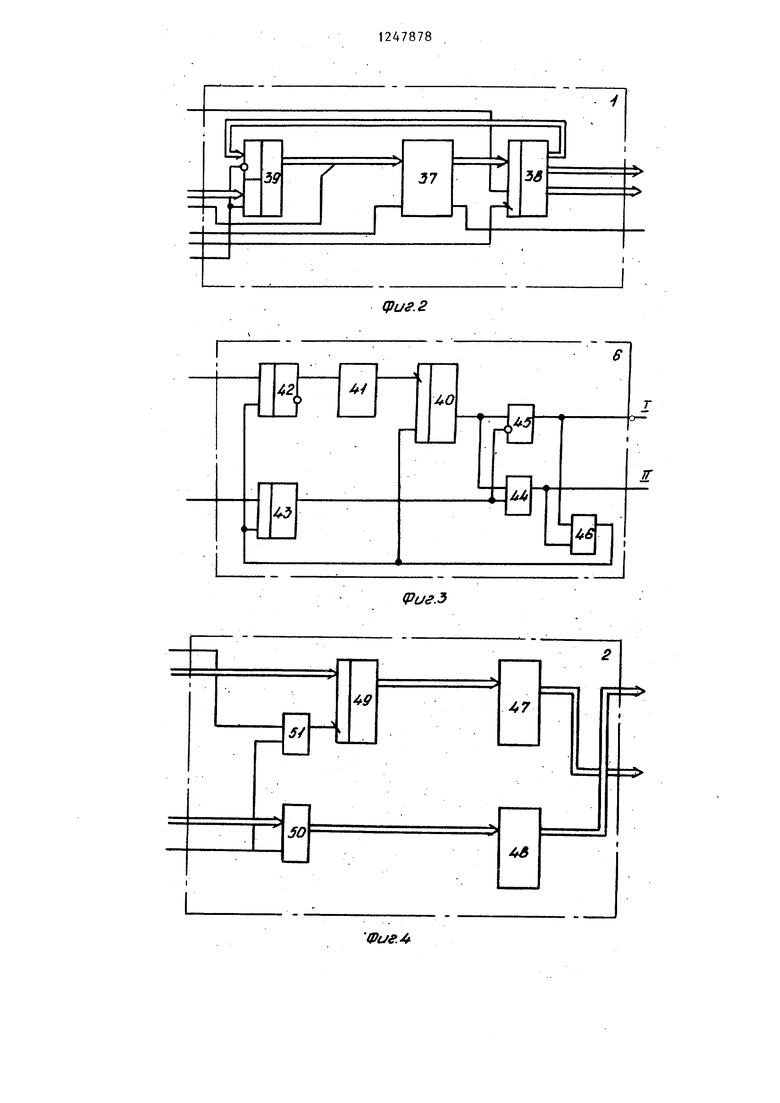

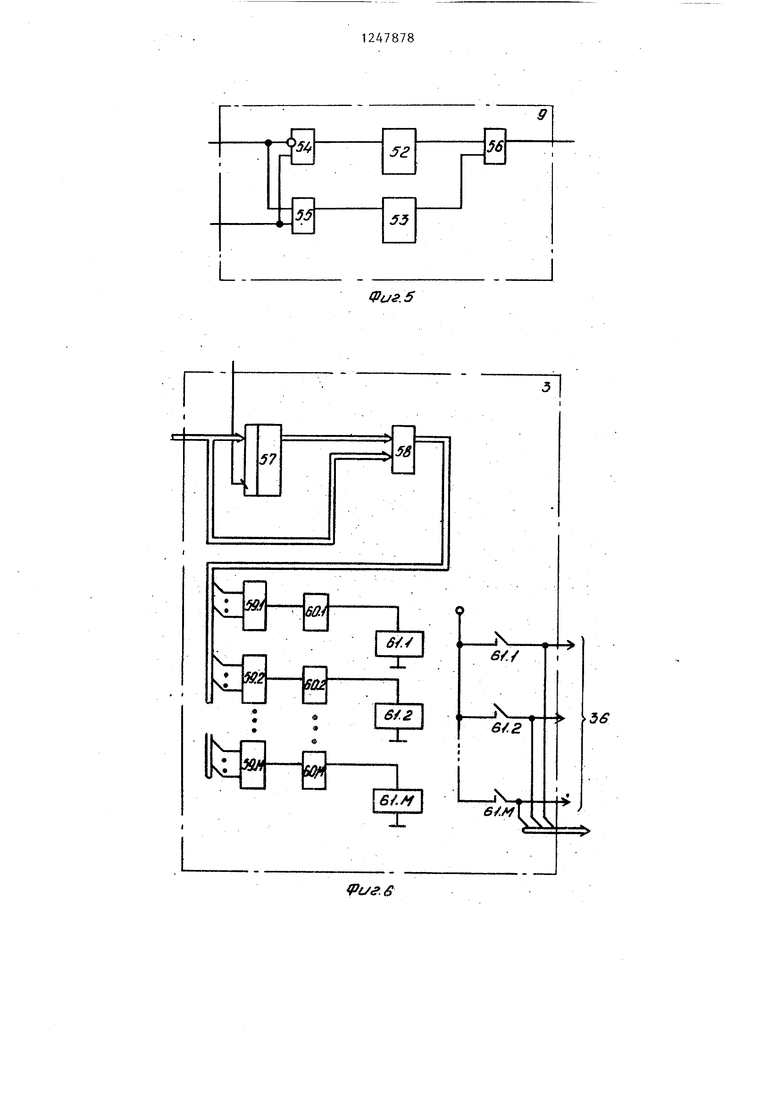

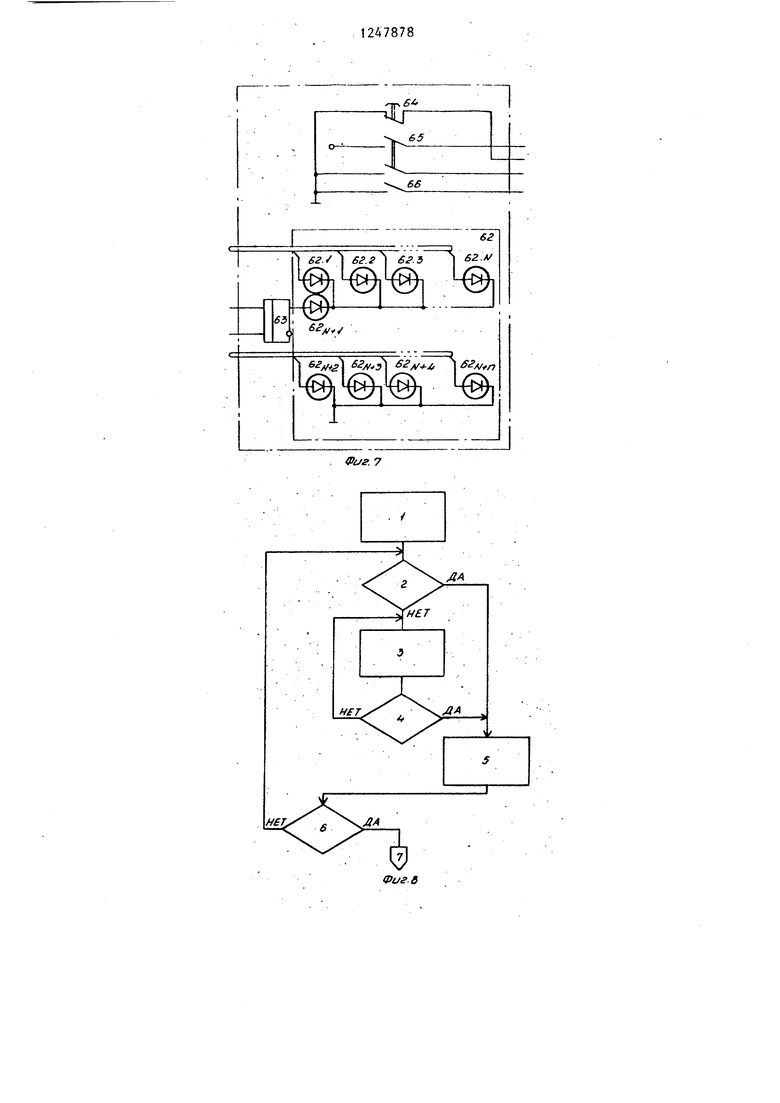

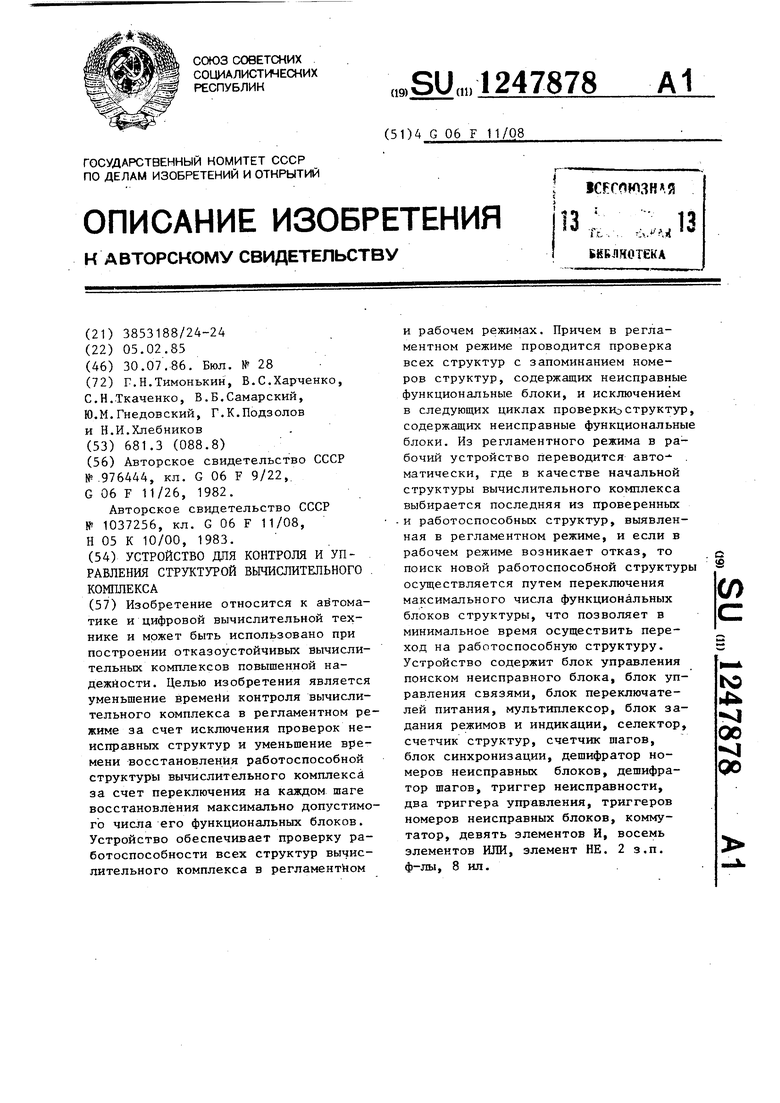

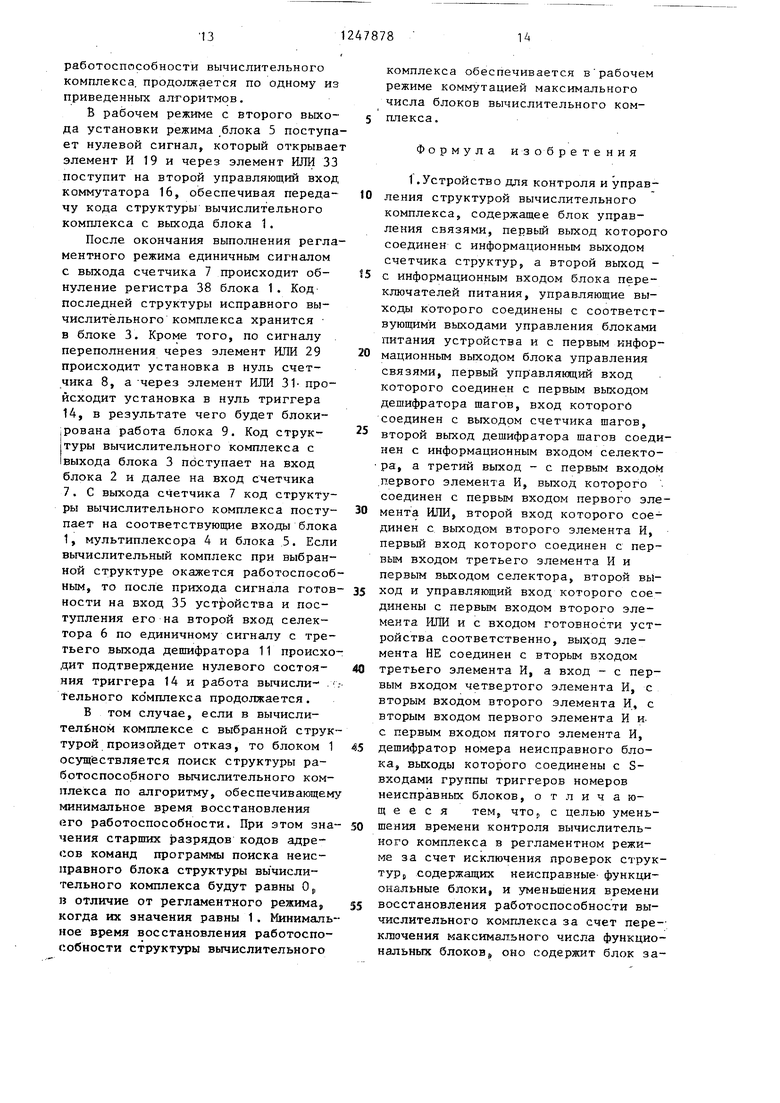

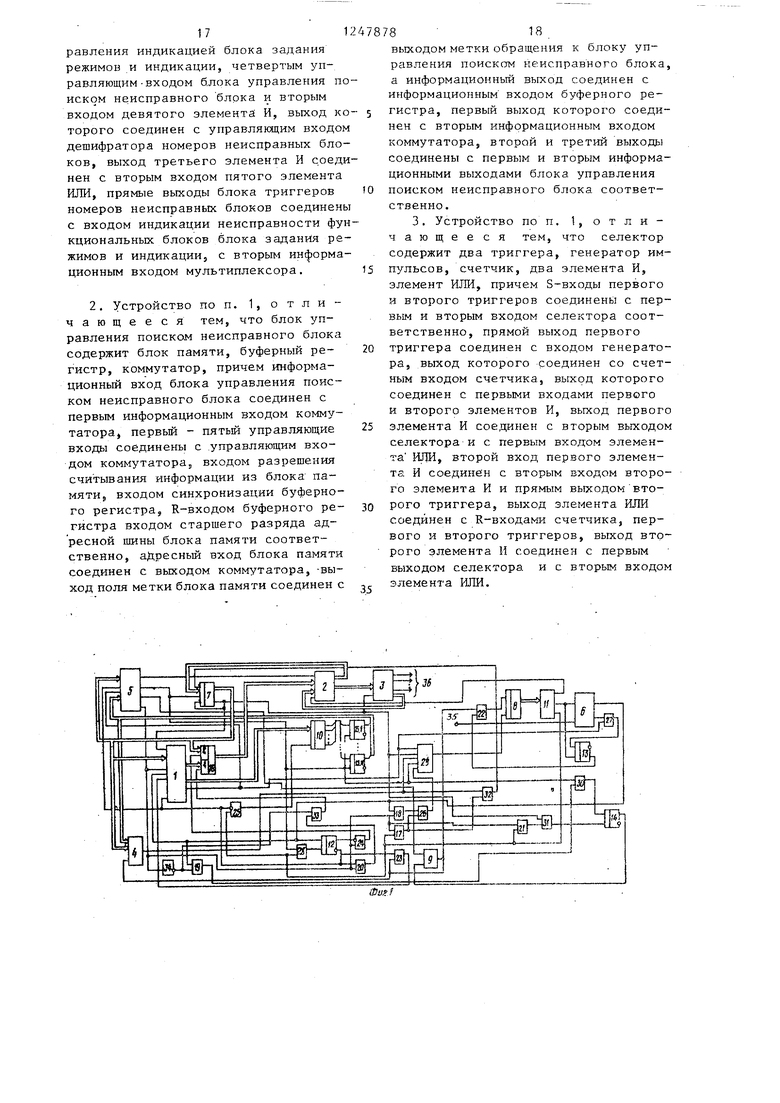

На фиг. 1 представлена блок-схема устройства для контроля и управления структурой вычислительного комплек- са; на фиг.. 2 - блок-схема блока управления поиском неисправного блока на фиг. 3 - блок-схема селектора н а фиг. 4 - функциональная схема блока управления связями; на фиг.5 - то же,блока синхронизации; на фиг.6 - то же, блока переключателей питания , на фиг. 7 - то же, блока задания режимов и индикации; на фиг. 8 и 9 представлены алгоритмы работы устройства.

Устройство содержит блок 1 управления поиском неисправного блока, блок 2 управления связями, блок 3 переключателей питания, мультиплексор 4, блок 5 задания режимов и индикации, селектор 6, счетчик 7 структур, счетчик 8 шагов, блок 9 синхронизации, дешифратор 10 номеров не-- исправных блоков, дешифратор 11 шагов, триггер 12 неисправности, первый и второй триггеры 13 и 14 управления, блок 15.1-15.N триггеров, номеров неисправных блоков, коммутатор 16, первый - девятьш 17-25 элементы И, первый - восьмой 26-33 элементы ИЛИ, элемент НЕ 34, вход 35 готовности устройства, группа выходов управления блоками питания 36.

Блок управления поиском неисправного блока содержит блок 37 памяти, буферный регистр 38, коммутатор 39.

Селектор содержит счетчик 40, генератор 41 импульсов, первый 42 и второй 43 триггеры, первый 44 и второй 45 элементы И, элемент 46 ИЛИ.

Блок управления связями содержит первый и второй преобразователи 47 и- 48 соответственно, буферньй ре

5

0

5

0

5

0

5

O

5

гистр 49, блок 50 элементов И, элемент И 5 1 ..

Блок синхронизации содержит генератор 52 импульсов высокой частоты, генератор 53 импульсов низкой ч асто- ты, первый и второй элементы И 54 и 55 соответственно, элемент ИЛИ 56.

Блок переключателей питания со- д ержит: буферный регистр 57, блок 58 элементов ИЛИ, первьй - М-й элементы ИЛИ 59.1-59.М, первый.- М-й усилители 60.1-60.М, первое - М исполнительное реле Р 61.1-61.М, но.рмаль- но разомкнутые контакты X 61.1 - X 61.М исполнительных реле Р 61.1 - 61,М.

Блок задания режимов и индикации содержит блок 62 светодиодов 62.1 - 62.М+П триггер 63 индикации, кнопку 64 сброса, тумблер 65 вида работы, тумблер 66 режима работы.

Первый выход установки режимов блока 5 задания ре.жимов и индикации соединен с вторым управляющим входом блока 2 управления связями. Первый информационный выход блока 2 управления связями соединен с информационным входом счетчика 7 структур. Второй информационный выход блока 2 управления связями соединен с информационным входом блока 3 переключателей питаний. Управляющие выходы блока 3 переключателей питания образуют группу управляющих выходов 36 устройства, а -также соединены с первым информационным входом блока 2 управления связями. Выходы дешифратора 10 номеров неисправных блоков соединены с S-входами соответствующих триггеров 15.1-15.N, Выход начальной установки блока 5 задания режимов и индикации соединен с R- входом счетчика 7 структур и R-входа- ми группы триггеров 15.1-15iN номеров неисправных блоков с первым входом четвертого элемента ИЛИ 29, с первым входом пятого элемента ИЛИ 30 и с первым входом третьего элемента ИЛИ 28. Второй выход установки режимов блока 5 задания режимов и индикации соединен с первым входом четвертого и пятого элементов И 20, 21 соответственно с вторыми входами первого, второго и восьмого элемей- тов И 17, 18 и 24 соответственно, и через элемент НЕ 34 с вторыми входами третьего элемента И 19 и восьмого элемента ИЛИ 33, Выход управления

3

синхронизацией блока установки режимов и индикации соединен с первым управляющим входом блока 9 синхронизации. Выход счетчика 8 шагов соединен со входом дешифратора 11 шагов, первый выход которого соединен с первым управляющим входом блока 2 управления связями, второй - с первым входом селектора 6, и с S-входом первого триггера 13 управления, а третий - с первым входом первого элемента И 17, со вторым входом пятого элемента И 21 с вторым входом третьего элемента ИЛИ 28 и с первым входом девятого элемента И 25. Выход первого элемента И 17 соединен с первым входом первого элемента: ИЛИ 26 и с вторым входом седьмого элемента ИЛИ 32. Вход .35 готовности устройства соединен с вторым входом селектора 6. Первьш выход селектора 6 соединен с первым входом второго элемента И 18, с первым входом третьего элемента И 19, с S-входом триггера 12 неисправности и третьим управляющи. входом блока 1 управления поиском неисправного блока. Второй выход селектора 6 соединен с первым входом второго элемента ИЛИ 27. Выход второго элемента И 18 соединен с вторым входом первого элемента ИЛИ 26. Информационный выход счетчика 7 структур соединен с вторым информационным входом коммутатора 16, с информационньтм входом блока 1 управления поиском неисправного блока, первым информационным входом мультиплексора 4 и входом индикации структуры блока 5 задания режимов и индикации. Первый информационный выход блока 1 управления поиском неисправного блока соединен с информационным входом дешифратора 10 номеров неисправных . блоков, а второй информационный выход соединен с первым информационным входом коммутатора 16. Выход коммутатора 16 соединен с вторым информационным входом блока 2 управления -связями. Управляющий выход блока 1 управления поиском неисправного блока соединен с вторым входом второго элемента ИЛИ 27,- с вторым входом четвертого элемента ИЛИ 29 управления индикацией блока 5 задания режимов и индикации. Прямой выход триггера 12 неисправности сое- динен с первым входом восьмого эле-;

А7878-4 . .

мента И 24, а инверсный выход - с вторым входом седьмого элемента И 23, с вторым входом четвертого элемента ИЛИ 20, с вторым входом девя- 5 того элемента И 25, с четв-ертым управляющим входом блока 1 управления поиском неисправного блока и вторым входом управления индикацией блока 5 задания, режимов и индикации. Выход 10 восьмого элемента И 24 соединен с первым управляющим входом коммутатора 16. Выход четвертого элемента И 20 соединен с первым входом восьмого элемента ИЛИ 33. Выход восьмого t5 (Элемента ИЛИ 33 .соединен с вторым управляющим входом коммутатора 16. Выход третьего элемента ИЛИ 28 соединен с R-входом триггера 12 неисправности. Выход первого элемента 20 ИЛИ 26 соединен с четвертым входом четвертого элемента ИЛИ 29. Выход .второго элемента ИЛИ 27 соединяем с R-входом первого триггера 13 управления, прямой выход которого соеди- 25 нен с первым входом шестого элемента И 28 . Выход шестого элемента И 22 соединен со счетным входом счет-- чика 8 шагов, R-вход которого соединен с выходом четвертого элемен-

0 та ИЛИ 29. Выход девятого элемента И 25 соединен с управлякщим входом дешифратора 10 номеров неисправных блоков. Прямые выходы блока триггеров 15.1-15.N соединены с вто5 рым информационным входом мультиплексора 4 и с входом индикации номеров неисправных структур блока 5 задания режимов и индикации S-вход второго триггера 14 управления сое0 динен с выходом пятого элемента ИЛИ . 30, а вход с выходом щестого элемента ИЛИ 31. Прямой выход второго триггера 14 управления соединен со вторым входом блока синхронизации 9,

5 выход которого соединен со вторым

входом шестого элемента И 22, с первым входом седьмого элемента И 23 и управляющим входом мультиплексора. Выход переполнения счетчика 7

0 структур соединен со счетным входом счетчика 7 структур, со вторым управляющим входом блока 1 управления поиском неисправного блока, с третьим входом четвертого элемента ИЛИ

5 29, с управляющим входом блока 3

переключения питания и с первым входом шестого элемента ИЛИ 21, второй вход которого соединен с выходом

пятого элемента И 21. Выход мультиплексора 4 соединен с четвертым входом четвертого элемента ИГШ 29 и с первым входом седьмого элемента ИЛИ 32, выход которого соединен со счет нькл входом счетчика 7 структур.Выход седьмого элемента И 23 соединен с пятым управляющим входом блока 1 управления поиском неисправного бло- ка. Выход третьего элемента И 19 соединен со вторым входом пятого элемента ИЛИ 30.

Информационный вход блока 1 уп-. равления поиском неисправного блока соединен с первым информационным

входом коммутатора 39. Первьш - третий управляющие входы блока 1 управления поиском неисправного блока соединены с управляющим входом коммутатора 39, входом разрешения считывания информации блока 37 памяти и входом синхронизации буферного регистра 38 соответственно. Выход коммутатора 39 соединен с адресным входом блока 37 памяти. Информационный выход блока 37 памяти соединен с информационным входом буферного регистра 38. Первый выход буферного регистра 38 соединен с вторым инфор- мационным входом коммутатора 39. Второй и третий выходы буферного регистра 38 соединены с вторым и первым информационными выходами блока 1 управления поиском неисправного блока соответственно. Выход поля метки блока 38 памяти соединен с управляющим выходом блока 1 управления поиском- неисправного блока. Четвертый и пятьй управляющие входы блока управления поиском неисправного блока соединены с R-входом регистра 38 и входом стар ;Шего разряда шины адреса блока 37 памяти соответственно.

Первый вход селектора 6 соединен с S-входом первого триггера 42. Единичный выход первого триггера 42 соединен с входом генератора 41 импульсов. Второй вход селектора 6 соедине с S-входом второго триггера 43. Пря- мой выход fToporo триггера 43 соединен с вторыми входами первого и второго элeмeнtoв И 44 и 45 соответственно .

Выход генератора 41 соединен со счетным входом счетчика 40. Выход переполнения .счетчика 40 соединен с первыми входами первого и второго

элементов И .44 и 45. Выход первого элемента И 44 соединен с первым выходом селектора 6 и первым входом элемента ИЛИ 46. Выход второго элемента И 45 соединен с вторым выходом селектора 6 и вторым входом элемента ИЛИ 46. Выход элемента ИЛИ 46 соединен с R-входами счетчика 40 и первого и второго триггеров 42 и 43 соответственно .

Блок 1 управления поиском неисправного блока предназначен для реализации оптимального алгоритма поиска работоспособной структуры вычислительного комплекса как в регламентном режиме, так и в рабочем режиме. Блок 2 управления связями предназначен для преобразования кодов структур вычислительного комплекса с целью определения номеров устройств питания тех блоков вычислительного комплекса, которые образуют его .выбранную структуру. Блок 3 переключателя питания предназначен для организации цепей питания выбранной структуры вычислительного комплекса.

Мультиплексор 4 предназначен для формирования импульсов счета счетчика 6 структур при выборе неработоспособной структуры вычислительного комплекса.

Блок 5 управления режимами и индикации предназначены для установления режимов и видов работы устройства.

Селектор 6 предназначен для организации временной селекции сигналов готовности работоспособных структур

вычислительного комплекса. I

Счетчик 7 ст1$уктур предназначен

для перебора (формирования кодов) возможных структур вычислительного комплекса, а счетчик 8 шагов - для управления проверками работоспособности структур вычислительного комплекса в регламентном режиме.

Блок 9 синхронизации предназначен для организации синхронного режима работы системы.

Дешифратор 10 номеров неисправных блоков предназначен для формирования сигналов управления группой триггеров 15.1-15.N номеров неис- нравных блоков при обнаружении неисправности.

Дешифратор 11 шагов предназначен ,цля формирования сигналов управления

.

режимов проверки выбранной структуры вычислительного комплекса.

Триггер 12 отказа предназначен для фиксации факта отказа при проверках работоспособности выбранных структур вычислительного комплекса.

Первый триггер 13 управления предназначен для управления работой счетчика 8 шагов, второй триггер 14 управления - для управления работой блока 9 синхронизации.

Блок 15.1-15.N триггеров номеров неисправных блоков предназначен для фиксации отказа первого - N-ro функциональных блоков выбранных струк- тур вычислительного комплекса при их отказах.

Коммутатор 16 предназначен для передачи кода структуры вычислительного комплекса в блок 2 управления связями.

Первый элемент И 17 предназначен для формирования сигналов .синхронизации работы блокэ 1 управления поиском неисправного блока, второй элемент И 18 - для формирования сигнала установки в нуль счетчика 8 шагов при возникновении отказов в работе выбранной структуры вычислительного комплекса, третий элемент И 19 - для формирования сигналов установки в единицу второго триггера 14 при возникновении отказов, в работе выбранной структуры вычислительного комплекса, четвертьш эле- мент И 20 - для формирования сигнала разрешения передачи кода структуры вычислительного комплекса с выхода блока 1 управления поиском неисправного блока, пятый элемент И 21 - для формирования сигнала установки в нуль второго триггера 14 управления, шестой-элемент И 28 - для формирования сигналов (импульсов) счета для работь счетчика 8 шагов, седьмой эле мент И 23 - дпя формирования импульсов синхронизации блока 1 управления поиском неисправного блока, восьмой элемент И 24 - для формирования сигнала разрешения передачи кода струк- туры вычислительного комплекса в бло 2 управления связями с выхода счётчика 7 структур, девятый элемент И 25 - для формирования разрешающего с 1гнала для дешифратора 10 номеров неисправных блоков.

Первый элемент ИЛИ 26 предназначен для передачи сигнала установки

в нуль счетчика 8 шагов, второй элемент ШТИ 27 - для передачи сигнала установки в нуль первого триггера 13 управления, третий элемент ИЛИ 28 для пере.дачи сигнала установки в нуль триггера 12 отказов, четвертый эле- мент ИЛИ 29 - для формирования сигнала установки в нуль счетчика 8 шагов пятьш элемент ИЛИ 30 - для передачи сигнала установки в единицу второго триггера 14 управления, седьмой элемент ИЛИ 32 предназначен для передачи сигналов (импульсов) счета на счетный вход счетчика 7 структур.

Восьмой элемент ИЛИ 33 предназначен для передачи сигнала управления передачей Кода структуры вычислительного комплекса с выхода блока 1 поиском неисправного блока на соответствующий вход блока 2 управления свя3 ЯМИ..

Элемент НЕ 34 предназн ачен для-управления работой пятого элемента И 2 и управления передачей кодов структу вычислительного комплекса с выхода блока 1 управления поиском неисправного блока на соответствующий вход блока 2 управления связями.

Вход 35 готовности устройства обеспечивает управление -работой селектора 6.

Группа выходов 36 блока 3 переключателей питания обеспечивает управление подключением источников питания функциональных блоков вычислительного комплекса.

Блок 37 памяти блока 1 предназначен для хранения кодов структур вычислительного комплекса.

Буферный регистр 38 блока 1 предназначен для записи и хранения на время проверки работоспособности кодов проверяемых структур вычислительного комплекса.

Коммутатор 39 блока 1 предназначен для передачи кодов адресов ячеек блока 37 памяти с выхода буферного регистра 38 и с выхода счетчика 7 структур.

Счетчик 40 селектора 5 предназначен для формирования времейного .интервала проверки работоспособности структуры вычислительного комплекса.

Генератор 41 импульсов предназначен для формирования тактовых импульсов для работы селектора 6.

Первый триггер 42 предназначен для управления работой генератора 41 импульсов.

Второй триггер 43 предназначен для фиксации сигнала готовности, поступающего с соответствующего входа 39 устройства.

Первый элемент И 44 селектора 6 предназначен для формирования сиг- нала нормы в работе вычислительного комплекса.

Второй элемент И 45 селектора 6 предназначен для формирования сигнала отказа в работе вычислительного комплекса.

Элемент ИЛИ 46 селектора 6 пред- назначен для передачи сигнала установки в нуль счетчика 44, первого и второго триггеров 42 и 43 соответственно.

Устройство для контроля и улрав- ления структурой вычислительного комплекса работает следующим образом.

В исходном состоянии все элементы памяти находятся в нулевом состоянии (цепи установки в нуль и цепи питания на фиг. 1 - 3 условно не показаны). Устройство работает в регламентном и рабочем режимах. .

В регламентном режиме с первого и второго .управляющего выходов блока 5 поступают единичные сигналы, причем первый из них поступает в блок 2 и разрешает его функционирование . В блоке 5 нажатием кнопки формируется сигнал установки в нулевое состояние, который устанавливает в нуль счетчик 7, триггеры 15.1 - 15.N, а также поступает через элемент ШШ 28 на R-вход триггера 12, через элемент ИЛИ 29 - на R-вход счетчика 8 и через элемент ШШ 30 - на вход триггера 14. Триггер 14 по этому сигналу устанавливается в единицу и разрешает работу блока 9. На выходе блока 9 появляются единичные сигналы. Код 000...О с выхода счетчика 7 поступает на первый информационный вход коммутатора 16, на информационный вход блока 1 и на информационный вход мультиплексора 4. Единичньй сигнал с второго управляющего выхода блока 5 поступает на первый управляющий вход блока 1, через элемент НЕ 34 - на вход элемента И 19 и через элемент ИЛИ 33 на второй управляющий вход .коммутатора 16. Кроме того, этот сигнал поступает на входы элементов И 20 и 24, 21, 17 и-18. Код номера исходной

структуры с выхода коммутатора 16 поступает на второй информационный вход блока 2. Со второго информационного выхода блока 2 код управления источниками питания поступает на вход блока 3, который формирует единичные сигналы на своих соответствующих управляющих выходах 36 и осуществляет включение необходимых

источников питания. После установки в нуль счетчика 8 на первом выходе дешифратора 11 появляется единичный сигнал, который поступает на первый управляющий вход блока 2 и разрешает его работу. Первый импульс с выхода блока 9 поступает на прямой вход элемента И 22 и формирует на его выходе единичный сигнал, который устанавливает код 000...01 в счетчике 8. В соответствии с единичным кодом счетчика 8 на втором выходе дешифратора 11 появится единичный сигнал, который поступит на первый вход селектора 6 к на S-вход триггера 13. По этому сигналу элемент И 22 будет закрыт на все время селекции. Селектор 6 начинает свою работу.

При исправности вычислительного комплекса выбранной структурой на

вход 35 системы поступает единичный сигнал готовности, который формирует единичный сигнал на втором выходе селектора 6. По этому сигналу через элемент ИЖ 27 происходит установка

в исходное (нулевое) состояние триггера 13, который вновь открывает элемент R 22. По очередному импульсу с выхода блока 9 происходит увеличение на единицу содержимого счетчика

8. На третьем выходе дешифратора 11 формируется единичный сигнал, кото- рьш поступает на входы элементов И 17, 21-и 25, а также на вход элемента ШШ 28. На выходе элемента И 17

формируется единичньй сигнал, который поступает через элемент ИЛИ 26 на вход элемента ИЛИ 29 и через него на вход установки в нуль счетчика 8. Кроме того, единичньй сигнал с вьпсода элемента И 17,поступает через

элемент ИЛИ 32 на счетньй вход счетчика 7,, формируя в нем очередной код. Единичный сигнал с выхода эле,

мента ИЛИ 28 производит подтверждение нулевого состояния триггера 12 ;и проверка работоспособности вычислительного комплекса новой структу- ры выполняется аналогично по описанному выше алгоритму.

Если при проверке вычислительного комплекса заданной структуры обнаружен отказ, то работа системы для контроля и управления структурой вычислительного комплекса происходит следующим образом.

На втором выходе селектора 6 формируется единичный сигнал, который поступает на вход элемента И 18, на S-вход триггера 12, на вход элемента И 19 и на соответствующий управляющий вход блока 1, По этому сигналу на выходе элемента И 18 фор- мируется единичньй сигнал, который, поступает через элементы ИЛИ 26 и 29 на вход установки в нуль счетчика 8 и производит его сброс в исходное состояние. Код структуры вычислительного комплекса, поступающий на информационный вход блока 1, по единичному сигналу с нулевого выхода триггера 12 через коммутатор 39 блока 1 поступает на информационньй вход блока 37 памяти того же блока 1 Триггер 12 устанавливается в единичное состояние. Элементы И 20 и 23 открыты, а элемент И 24 закрыт. По единичному сигналу на втором управ- ляющем входе блока 1 происходит считывание кода первой команды программы поиска неисправного блока. Код команды по импульсу синхронизации, поступающему на пятый управляющий вход блока 1, запшиется в регистр 38 блока 1. На управляющий выход блока 1 поступает единичный сигнал (признак считывания команды) с выхода поля метки блока 37 памяти бло- ка 1. Код адреса очередной команды с первого выхода регистра 38 блока 1 поступает на второй информационньй вход коммутатора 39. Код структуры вычислительного комплекса пос- тупает на второй информационный выход блока 1 и далее на второй информационный вход коммутатора 16. Код номера переключаемого блока структуры вычислительного комплекса поступает на первый информационный, выход блока 1 и далее на информационный вход дещифратора 10. По еди25

5

10 5203D. 3540455055ничному сигналу с управляющего выхода блока 1 через элемент ИЛИ 29 происходит подтверждение нулевого состояния счетчика 8. Через элемент ИЛИ 27 триггер 13 устанавливается в ну- левое состояние.и открывает элемент И 22. Единичньй сигнал с выхода элемента И 20 через элемент ИЛИ 33 поступает на второй управляющий вход коммутатора 16 и разрешает запись кода структуры вычислительного комплекса в блок 2. При повторении отказа вычислительного комплекса работа устройства выполняется по алгоритму обнаружения отказа в регламентном режиме.

Если отказ устранен, то по единичному сигналу с третьего выхода дешифратора 11, поступающему на второй вход элемента И 25, происходит формирование единичного сигнала на управляющем входе дешифратора 10. В соответствии с кодом на его информационном входе устанавливается в единицу один из соответствующих ыходов дешифратора 10. При этом будет установлен в единицу один из соответствующих триггеров 15.1-15.N. Код с единичных выходов триггеров 15.1 - 15.N поступает на управляющий вход мультиплексора 4 и на соответствующий вход блока 5 для отсветки. Триггер 12 единичным сигналом с третьего выхода дешифратора 11 устанавливается в нуль (исходное -состояние). По импульсу синхронизации с вi Ixoдa блока 9 на выходе мультиплексора 4 формируется единичньй сигнал, который через элемент ИЛИ 29 производит ус- тановку в нуль счетчика 8, а также через элемент ИЛИ 32 производит установку очередного кода в счетчике 7. В том случае, если во вновь образованной структуре вычислительного комплекса присутствует неисправный блок, то на выходе мультиплексора формируется единичный сигнал, который производит те же изменения в состоянии элементов памяти системы, что и в предыдущем случае. Если в структуру вычислительного: комплекса неисправный блок не входит, то вы - , числительньй комплекс с заданной структурой проверяется на работоспособность по полному циклу проверки. В дальнейшем работа устройства в зависимости от результата проверки

работоспособности вычислительного комплекса, продолжается по одному из приведенных алгоритмов,

В рабочем режиме с второго вько- да установки режима блока 5 поступает нулевой сигнал, который открывает элемент И 19 и через элемент ИЛИ 33 поступит на второй управляющий вход коммутатора 16, обеспечивая передачу кода структуры вычислительного комплекса с выхода блока 1.

После окончания выполнения регламентного режима единичньм сигналом с выхода счетчика 7 происходит обнуление регистра 38 блока 1. Код последней структуры исправного вычислительного комплекса хранится в блоке 3. Кроме того, по сигналу переполнения через элемент ИЛИ 29 происходит установка в нуль счетчика 8, а -через элемент ИЛИ 31- происходит установка в нуль триггера 14, в результате чего будет блокирована работа блока 9. Код структуры вычислительного комплекса с выхода блока 3 поступает на вход блока 2 и далее на вход счетчика 7. С выхода счетчика 7 код структуры вычислительного комплекса поступает на соответствующие входы блока 1, мультиплексора 4 и блока 5. Если вычислительный комплекс при выбранной структуре окажется работоспособным, то после прихода сигнала готовности на вход 35 устройства и поступления его на второй вход селектора 6 по единичному сигналу с третьего выхода дешифратора 11 происходит подтверждение нулевого состояния триггера 14 и работа вычисли- . тельного ко мплекса продолжается.

В том случае, если в вычисли- телбном комплексе с выбранной структурой произойдет отказ, то блоком 1 осуществляется поиск структуры работоспособного вычислительного комплекса по алгоритму, обеспечивающему минимальное время восстановления его работоспособности. При этом значения старших разрядов кодов адресов команд программы поиска неисправного блока структуры вы числи- тельного комплекса будут равны О„ 13 отличие от регламентного режима, когда их значения равны 1. Минимальное время восстановления работоспособности структуры вычислительного

комплекса обеспечивается в рабочем режиме коммутацией максимального числа блоков вычислительного ком- плекса.

Формула изобретения

1.Устройство для контроля и управления структурой вычислительного комплекса, содержащее блок управления связями, первый выход которого соединен с информационным выходом счетчика структур, а второй выход с информационным входом блока переключателей питания, управляющие выходы которого соединены с соответствующими выходами управления блоками питания устройства и с первым информационным выходом блока управления связями, первый управлякщий вход которого соединен с первым выходом дешифратора шагов, вход которого соединен с выходом счетчика шагов,

второй выход дешифратора шагов соединен с информационным входом селекто- ра, а третий выход - с первым входом .первого элемента И, выход которого . соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с, выходом второго элемента И, первый вход которого соединен с первым входом третьего элемента И и первьм выходом селектора, второй вь1ход и управляющий вход которого соединены с первым входом второго элемента ИЛИ и с входом готовности устройства соответственно, выход элемента НЕ соединен с вторым входом

третьего элемента И, а вход - с первым входом четвертого элемента И, с вторым входом второго элемента И, с вторым входом первого элемента И и. с первым входом пятого элемента И,

дешифратор номера неисправного блока, выходы которого соединены с S- входами группы триггеров номеров неисправных блоков, отличающееся тем, что,, с целью уменьшения времени контроля вычислительного комплекса в регламентном режиме за счет исключения проверок структур .содержащих неисправные- функциональные блоки, и уменьшения времени

восстановления работоспособности вычислительного комплекса за счет переключения максимального числа функциональных блоков оно содержит блок за

Дания режимов и индикации, блок управления поиском неиспрайного блока блок синхронизации, мультиплексор, два триггера управления, триггер неисправности, коммутатор, шестой - девятый элементы И, третий - восьмо элементы ИЛИ, причем первый выход установки режимов блока задания режимов и индикации соединен с вторы управляющим входом блока управления связями, а второй выход установки режимов - с первым управляющим входом блока управления поиском неисправного блока и с входом элемента НЕ, выход управления синхронизацие блока задания режимов и индикации соединен с первым входом блока синхронизации, а выход начальной установки - с R-входами счетчика структ и группы триггеров номеров неисправных блоков, с первым входом третьегр элемента ИЛИ, с первым входом четвертого элемента ИЛИ, с пе.рвым входом пятого элемента ИЛИ, выход метки обращения блока управления поиском неисправного блока соединен с первым входом управления индикацией блока задания режимов и индикации, с вторым входом четвертого элемента ИЛИ, с вторым входом второго элемента ИЛИ, выход которого соединен с R- входом первого триггера управления, S-вход которого соединен с вторьм выходом дешифратора шагов, а прямой выход соединен с первым входом шестого элемента И, выход которого соединен со счетным входом счетчика шагов, R-входы которого соединены с выходом четвертого элемента ИЛИ, первьш и второй информационные выхо- ды блока управления поиском неисправного блока соединены с информационным входом дешифратора номеров неисправных блоков и с первым инфо.р- мационным входом коммутатора соот- ветственно, выход коммутатора соединен с вторым информационным входом блока управления связями, выход переполнения счетчика структур соединен с третьим входом четвертого элемента ИЛИ, вторым управлякнцим входом блока управления поиском неисправного блока, с входом синхронизации счетчика структур, с входом синхронизации блока переключателей питания, с первым входом шестого элемента ИЛИ, второй вход пятого элемента И соединен с третьим выхо0

5

5 О 5

дом дешифратора шагов а выход соединен с вторым входом шестого элемента ИЛИ, выход которого соединен с входом второго триггера , ления, S-вход которого соединен с выходом пятого элемента ИЛИ, а прямой выход - с вторым входом блока синхронизации, выход которого соединен с управляющим входом мультиплексора, с первым входом седьмого элемента И и вторым входом шестого элемента И, выход мультиплексора соединен с первым входом седьмого элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, а выход соединен со счетным входом счетчика структур, информацион- ньй выход которого соединен с входом индикации структуры вычислительного комплекса блока задания режимов и индикации, с информационным входом блока управления поиском неисправ - .ного блока, первым информационным входом мультиплексора, вторым информационным входом коммутатора, четвертый и пятьш входы четвертого элемента ИЛИ соединены с выходами первого элемента ИЛИ и мультиплексора соответственно, первый выход селектора - с третьим управляющим входом блока управления поиском неисправного блока и с S-входом триггера неисправности, прямой выход которого соедине н с первым входом восьмого элемента И, второй в:цод которого соединен с вторым выходом установки режимов блока зад-ания режимов и индикации, а выход соединен с первым управляющим входом коммутатора, инверсный выход триггера неисправности- соединен с вторым входом четвертого элемента И, выход которого соединен с первым входом восьмого элемента ИЛИ, второй вход которого соединен с выходом элемента НЕ, а выход - с вторым управляющим входом коммутатора, третий выход дешифратора шагов соединен с первым входом девятого элемента И, с вторым входом третьего элемента ЩШ, выход которого соединен с R-входом триггера неисправности, инверсный выход которого соединен с вторым входом седьмого элемента И, выход которого соединен с пятым управляющим входом блока управления поиском неисправного блока, инверсный выход триггера неисправности соединен с вторым входом управления индикацией блока задания режимов и индикации, четвертым управляющим-входом блока управления поиском неисправного блока и вторым входом девятого элемента И, выход ко торого соединен с управляющим входом дешифратора номеров неисправных блоков, выход третьего элемента И с.оеди нен с вторым входом пятого элемента ИЛИ, прямые выходы блока триггеров номеров неисправных блоков соединены с входом индикации неисправности функциональных блоков блока задания режимов и индикации, с вторым информационным входом мультиплексора.

2, Устройство по п. 1, отличающееся тем, что блок управления поиском неисправного блока содержит блок памяти, буферный регистр, коммутатор, причем информационный вход блока управления поиском неисправного блока соединен с первым информационным входом коммутатора, первьй - пятьй управляющие входы соединены с управляющим входом коммутатора, входом разрешения считывания информации из блока памяти, входом синхронизации буферного регистра, R-входом буферного регистра входом старшего разряда адресной шины блока памяти соответственно, адресный вход блока памяти соединен с выходом коммутатора, -выход поля метки блока памяти соединен с

s О 5

0

5

0

выходом метки обращения к блоку управления поиском неисправного блока, а информационный выход соединен с информационным входом буферного регистра, первый выход которого соединен с вторым информационным входом коммутатора, второй и третий выходы соединены с первым и вторым информационными выходами блока управления поиском неисправного блока соответственно.

3. Устройство по п. 1, отличающееся тем, что селектор содержит два триггера, генератор импульсов, счетчик, два элемента И, элемент ИЛИ, причем S-входы первого и второго триггеров соединены с первым и вторым входом селектора соответственно, прямой выход первого триггера соединен с входом генератора, выход которого соединен со счетным входом счетчика, выход которого соединен с первыми входами первого и второго элементов И, выход первого элемента И соединен с вторым выходом селектора и с первым входом элемента ИДИ, второй вход, первого элемента И соединен с вторым входом второго элемента И и прямым выходом второго триггера, выход элемента ИЛИ соединен с R-входами счетчика, первого и второго триггеров, выход втр- рого элемента И соединен с первым выходом селектора и с вторым входом элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для контроля параметров | 1987 |

|

SU1444714A1 |

| Устройство для автоматического контроля генератора случайных чисел | 1982 |

|

SU1020837A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1278855A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1111171A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для контроля мультиплексора | 1990 |

|

SU1741136A1 |

| Устройство для выбора работоспособной структуры вычислительного комплекса | 1980 |

|

SU1037256A1 |

| Многоканальное устройство для контроля систем управления | 1985 |

|

SU1345200A1 |

| Устройство поиска неисправных блоков и элементов | 1989 |

|

SU1709351A1 |

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении отказоустойчивых вычислительных комплексов повышенной надежности. Целью изобретения является уменьшение времени контроля вычислительного комплекса в регламентном режиме за счет исключения проверок неисправных структур и уменьшение времени восстановления работоспособной структуры вычислительного комплекс за счет переключения на каждом шаге восстановления максимально допустимого числа его функциональных блоков. Устройство обеспечивает проверку работоспособности всех структур вычислительного комплекса в регламент юм и рабочем режимах. Причем в регламентном режиме проводится проверка всех структур с запоминанием номеров структур, содержащих неисправные функциональные блоки, и исключением в следующих циклах проверкиьструктур, содержащих неисправные функциональные блоки. Из регламентного режима в рабочий устройство переводится авто- матически, где в качестве начальной структуры вычислительного комплекса выбирается последняя из проверенных и работоспособных структур, выявленная в регламентном режиме, и если в рабочем режиме возникает отказ, то поиск новой работоспособной структуры осуществляется путем переключения максимального числа функциональных блоков структуры, что позволяет в минимальное время осуществить переход на работоспособную структуру. Устройство содержит блок управления поиском неисправного блока, блок управления связями, блок переключателей питания, мультиплексор, блок задания режимов и индикации, селектор, счетчик структур, счетчик шагов, блок синхронизации, дешифратор номеров неисправных блоков, дешифратор шагов, триггер неисправности, два триггера управления, триггеров номеров неисправных блоков, коммутатор, девять элементов И, восемь элементов ИЛИ, элемент НЕ. 2 з.п. ф-лы, 8 ил. g (Л ю 4 00 00

Фиг

59

37

5S

CPUS, г

(Риг.з

49

47

Фиг.-4

Физ5

JV6/.

b

т--

iV

в.г

.3

L-v

tf/yVT

u.S

Г

Фиг. 9

| Устройство для управления реконфигурацией микропрограммного процессора | 1981 |

|

SU976444A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для выбора работоспособной структуры вычислительного комплекса | 1980 |

|

SU1037256A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-30—Публикация

1985-02-05—Подача