Изобретение относится к цифровой вычислительной технике, в частности к средствам автоматизации контроля и поиска неисправностей в устройствах с дискретным характером функцио- .нированияо

Цель изобретения - повышение быстродействия устройства.

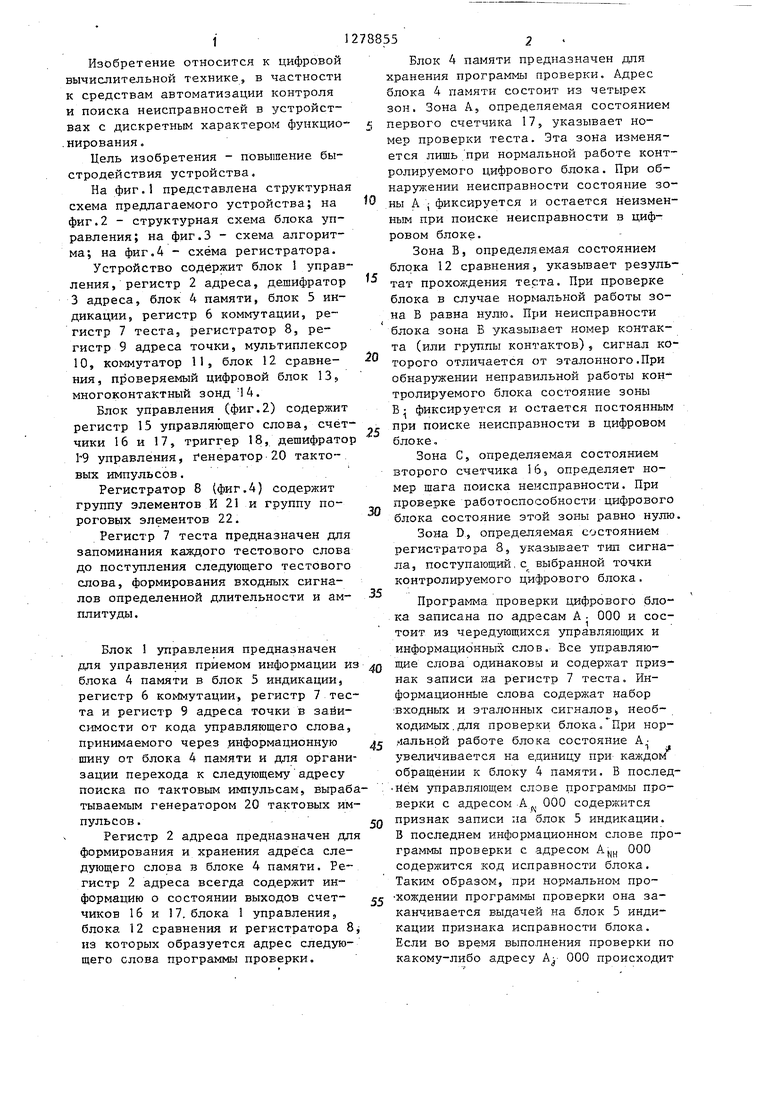

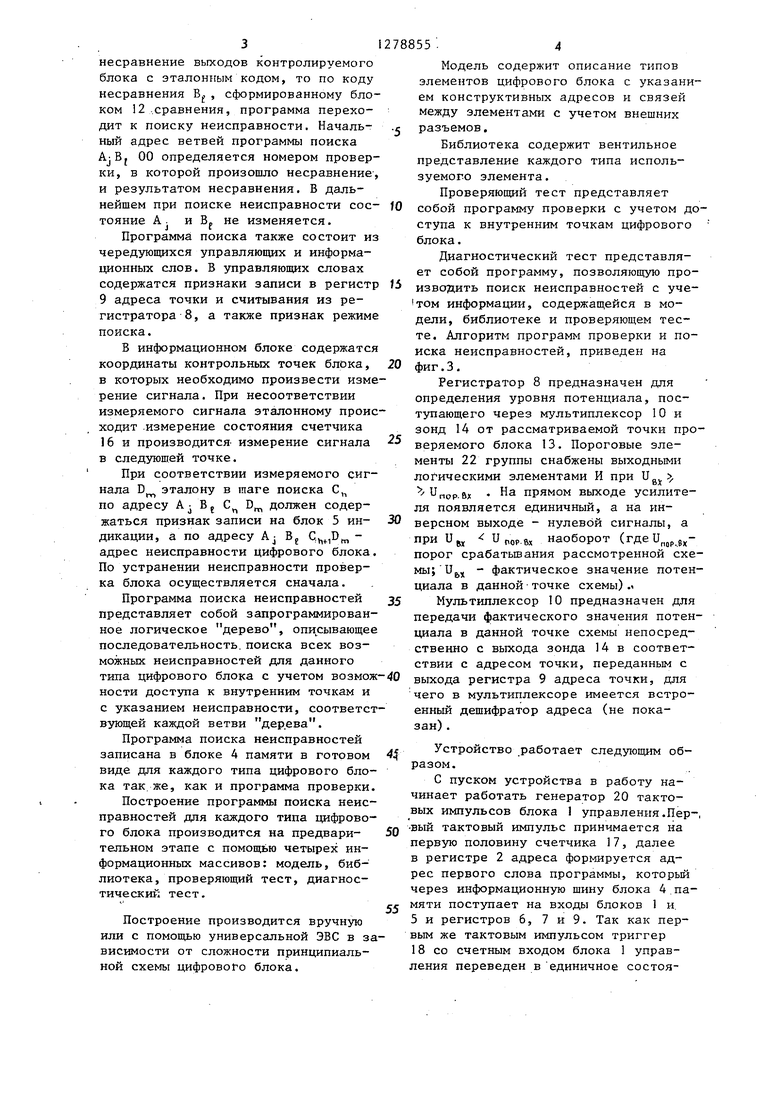

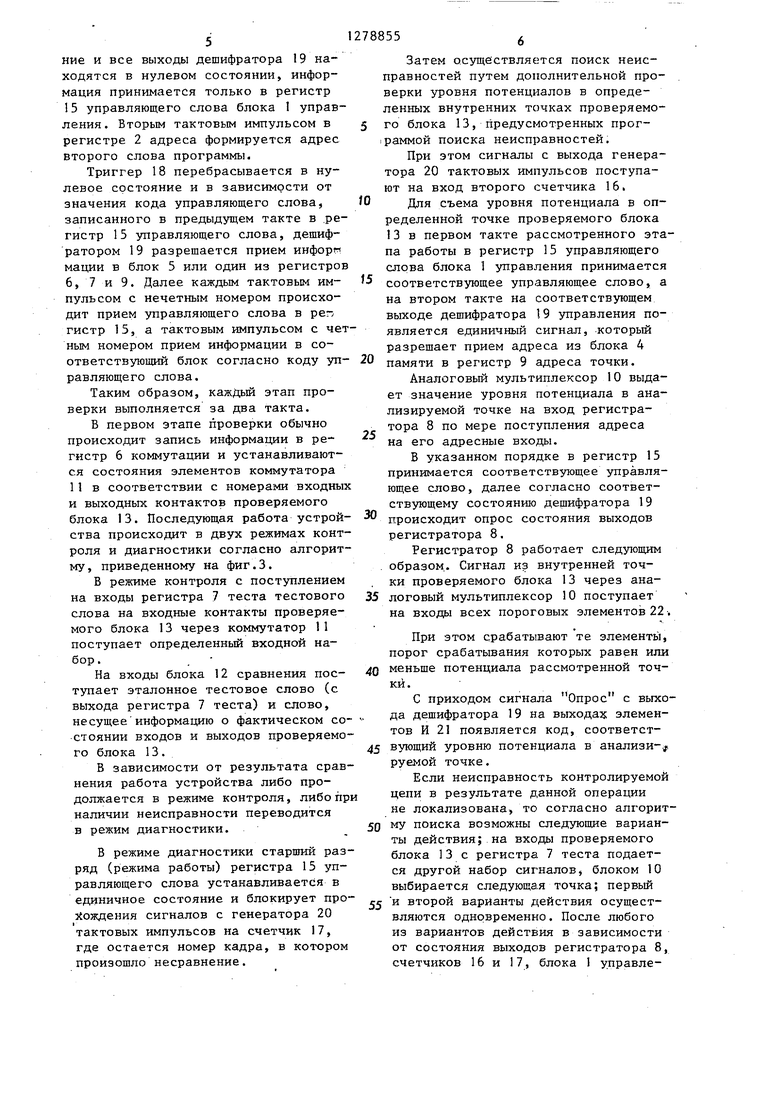

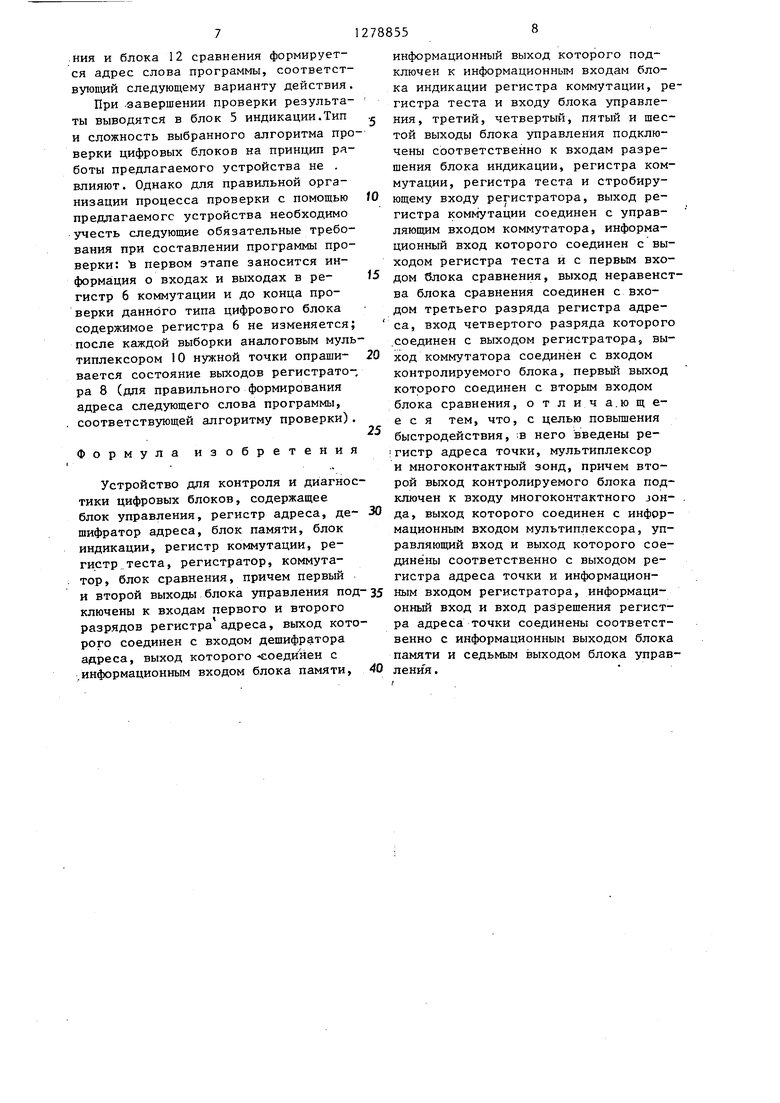

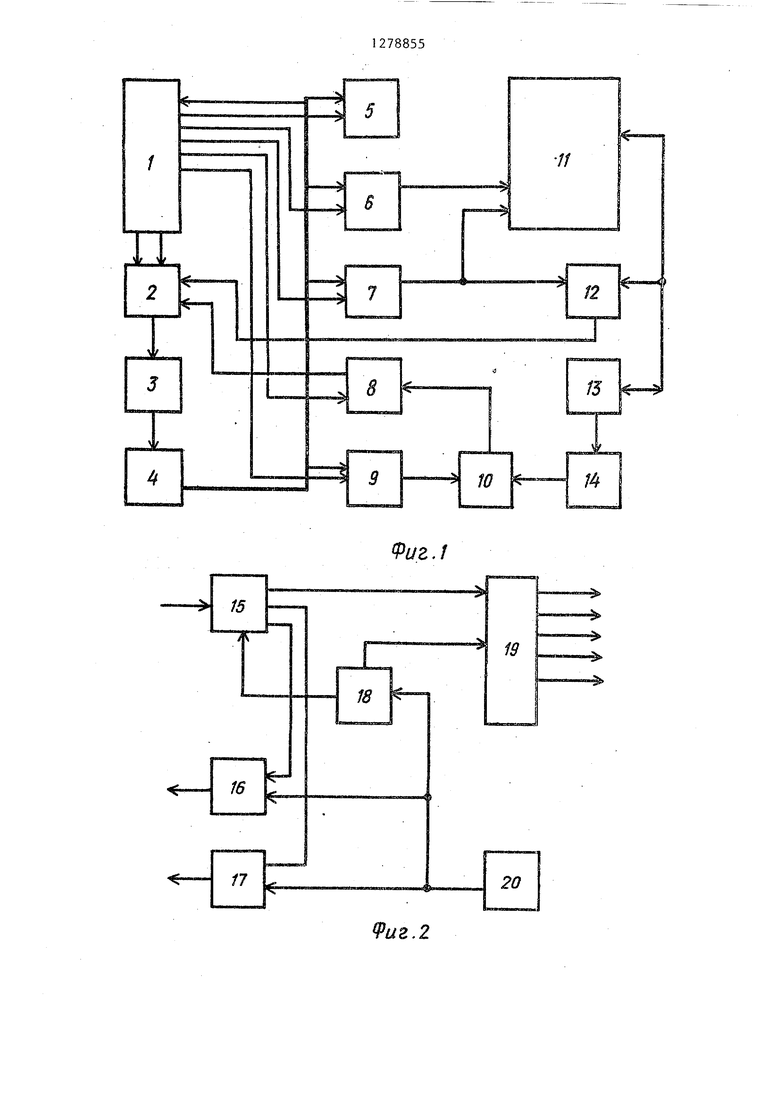

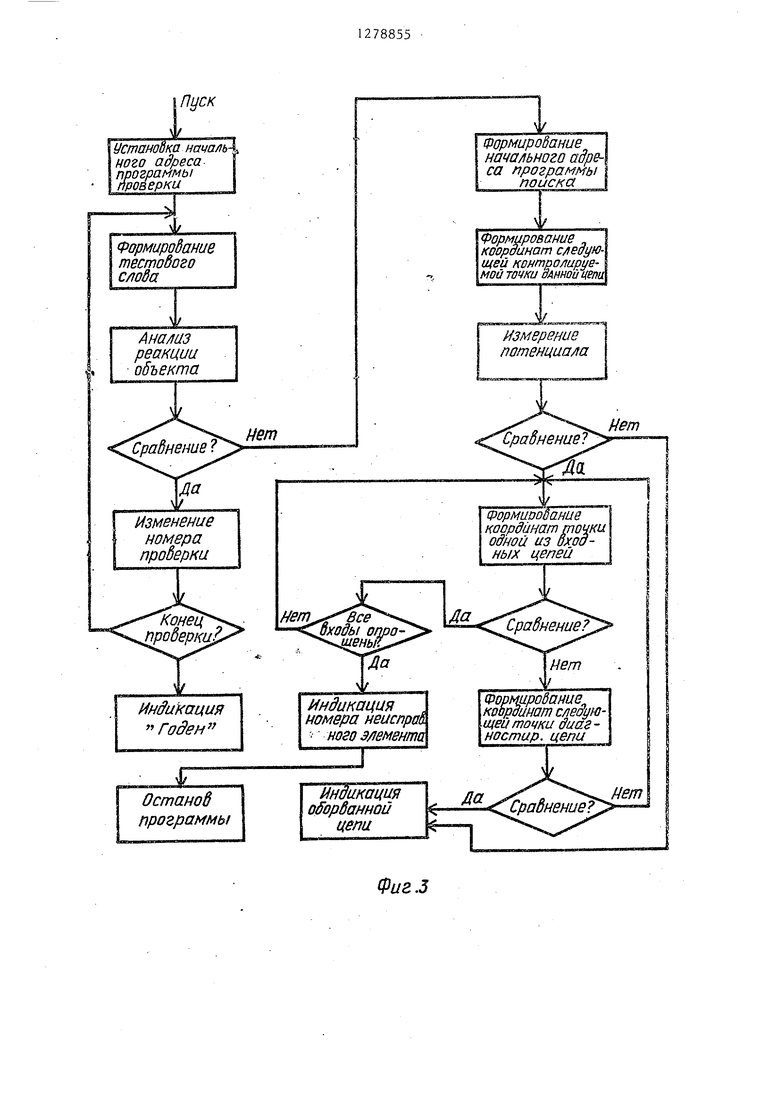

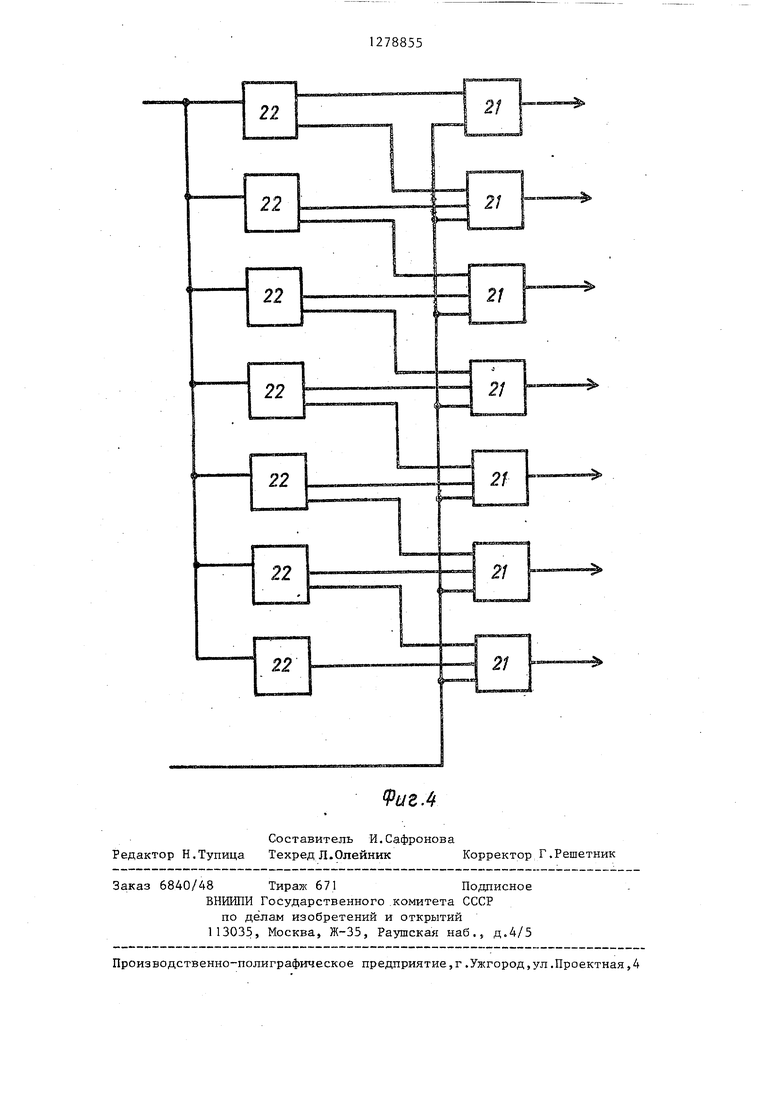

На фиг.1 представлена структурная схема предлагаемого устройства; на фиг.2 - структурная схема блока управления; на фиг.З - схема алгоритма; на фиг.4 - схема регистратора.

Устройство содержит блок 1 управления, регистр 2 адреса, дешифратор 3 адреса, блок 4 памяти, блок 5 индикации, регистр 6 коммутации, регистр 7 теста, регистратор 8, регистр 9 адреса точки, мультиплексор 10, коммутатор 11, блок 12 сравнения , проверяемый цифровой блок 13 j многоконтактный зонд М 4.

Блок управления (фиг.2) содержит регистр 15 управляющего слова, счетчики 16 и 17, триггер 18, дешифрато 19 управления, Генератор 20 тактовых импульсов.

Регистратор 8 (фиг.4) содержит группу элементов И 21 и группу пороговых элементов 22.

Регистр 7 теста предназначен для запоминания каждого тестового слова до поступления следующего тестового слова, формирования входных сигналов определенной длительности и амплитуды .

Блок 1 управления предназначен для управления приемом информации из блока 4 памяти в блок 5 индикации, регистр 6 коммутации, регистр 7 теста и регистр 9 адреса точки в зависимости от кода управляющего слова, принимаемого через информационную шину от блока 4 памяти и для организации перехода к следующему адресу поиска по тактовым импульсам, вырабатываемым генератором 20 тактовых импульсов .

Регистр 2 адреса предназначен для формирования и хранения адреса следующего слова в блоке 4 памяти. Регистр 2 адреса всегда содержит информацию о состоянии выходов счетчиков 16 и 17. блока 1 управления, блока 12 сравнения и регистратора 8 из которых образуется адрес следующего слова программы проверки.

10

788552

Блок 4 памяти предназначен дпя хранения программы проверки. Адрес блока 4 памяти состоит из четырех зон. Зона А, определяемая состоянием 5 первого счетчика 17, указывает номер проверки теста. Эта зона изменяется лишь,при нормальной работе контролируемого цифрового блока. При обнаружении неисправности состояние зоны А j фиксируется и остается неизменным при поиске неисправности в цифровом блоке.

Зона В, определяемая состоянием блока 12 сравнения, указывает резуль- тат прохождения теста. При проверке блока в случае нормальной работы зона В равна нулю. При неисправности блока зона В указывает номер контакта (или группы контактов), сигнал которого отличается от эталонного.При обнаружении неправильной работы контролируемого блока состояние зоны

20

5

0

5

5

п

0

5

Б- фиксируется и остается постоянным при поиске неисправности в цифровом блоке.

Зона С, определяемая состоянием второго счетчика 16, определяет номер шага поиска неисправности. При проверке работоспособности цифрового блока состояние этой зоны равно нулю.

Зона D., определяемая состоянием регистратора В, указывает тип сигнала, поступающий,с выбранной точки контролируемого цифрового блока.

Программа проверки цифрового блока записана по адресам А 000 и состоит из чередующихся управляющих и информационных слов. Все управляющие слова одинаковы и содержат признак записи на регистр 7 теста. Информационные слова содержат набор входных и эталонных сигналов необ-, ходимых.для проверки блока о При нормальной работе блока состояние А увеличивается на единицу при каждо / обращении к блоку 4 памяти. В послед- Нем зтравляющем слове программы проверки с адресом А 000 содержится признак записи па блок 5 индикации. В последнем информационном слове программы проверки с адресом А 000 содержится код исправности блока. Таким образом, при нормальном про- хождении программы проверки она заканчивается выдачей на блок 5 индикации признака исправности блока. Если во время выполнения проверки по какому-либо адресу А 000 происходит

несравнение выходов контролируемого блока с эталонным кодом, то по коду несравнения В, сформированному блоком 12 -.сравнения, программа переходит к поиску неисправности. Начальный адрес ветвей программы поиска AjBj 00 определяется номером проверки, в которой произошло несравнение, и результатом несравнения. В дальнейшем при поиске неисправности состояние А. и Bj не изменяется.

Программа поиска также состоит из чередующихся управляющих и информационных слов. В управляющих словах содержатся признаки записи в регистр 9 адреса точки и считывания из регистратора 8, а также признак режиме поиска.

В информационном блоке содержатся координаты контрольных точек блока, в которых необходимо произвести измерение сигнала. При несоответствии измеряемого сигнала эталонному происходит .измерение состояния счетчика 16 и ПРОИЗВОДИТСЯ измерение сигнала в следующей точке.

При соответствии измеряемого сигнала D эталону в таге поиска С

по адресу А- Bj С D должен содержаться признак записи на блок 5 индикации, а по адресу AJ В C,D - адрес неисправности цифрового блока. По устранении неисправности проверка блока осуществляется сначала.

Программа поиска неисправностей представляет собой запрограммированное логическое дерево, описывающее последовательность, поиска всех возможных неисправностей для данного типа цифрового блока с учетом возможности доступа к внутренним точкам и с указанием неисправности, соответствующей каждой ветви дер.ева.

Программа поиска неисправностей записана в блоке 4 памяти в готовом виде для каждого типа цифрового блока так. же, как и программа проверки.

Построение программы поиска неисправностей для каждого типа цифрового блока производится на предварительном этапе с помощью четырех информационных массивов: модель, библиотека, проверяющий тест, диагностический тест.

Построение производится вручную или с помощью универсальной ЭВС в зависимости от сложности принципиальной схемы цифрового блока.

Модель содержит описание типов элементов цифрового блока с указанием конструктивных адресов и связей

между элементами с учетом внешних разъемов.

Библиотека содержит вентильное представление каждого типа используемого элемента.

Проверяющий тест представляет

O собой программу проверки с учетом доступа к внутренним точкам цифрового блока.

Диагностический тест представляет собой программу, позволяющую про изводить поиск неисправностей с уче- том информации, содержащейся в модели, библиотеке и проверяющем тесте. Алгоритм программ проверки и поиска неисправностей, приведен на

0 фиг.З.

Регистратор 8 предназначен для определения уровня потенциала, поступающего через мультиплексор 10 и зонд 14 от рассматриваемой точки проверяемого блока 13. Пороговые элементы 22 группы снабжены выходными логическими элементами И при Ugjj:. х UOOP 5д . На прямом выходе усилителя появляется единичный, а на инверсном выходе - нулевой сигналы, а при Ug UpoP.Bx наоборот ( порог срабатьшания рассмотренной схе- Mbi; Uj - фактическое значение потенциала в данной точке схемы) .

5 Мультиплексор 10 предназначен для передачи фактического значения потенциала в данной точке схемы непосред- cTBeifflo с выхода зонда 14 в соответствии с адресом точки, переданным с

0 вьпсода регистра 9 адреса точки, для чего в мультиплексоре имеется встроенный дешифратор адреса (не показан) .

с Устройство работает следующим образом.

С пуском устройства в работу начинает работать генератор 20 тактовых импульсов блока 1 управления.Пер-,

Q -вый тактовый импульс принимается на первую половину счетчика 17, далее в регистре 2 адреса формируется адрес первого слова программы, который через информационную шину блока 4 пае мяти поступает на входы блоков 1 и. 5 и регистров 6, 7 и 9. Так как первым же тактовым импульсом триггер 18 со счетным входом блока 1 управления переведен в единичное состояние и все выходы дешифратора 19 находятся в нулевом состоянии, информация принимается только в регистр 15 управляющего слова блока 1 управления. Вторым тактовым импульсом в регистре 2 адреса формируется адрес второго слова программы.

Триггер 18 перебрасывается в нулевое состояние и в зависимости от значения кода управляющего слова, записанного в предыдущем такте в .регистр 15 управляющего слова, дешифратором 19 разрешается прием инфорр мации в блок 5 или один из регистров 6, 7 и 9. Далее каждым тактовым импульсом с нечетным номером происходит прием управляющего слова в регистр 15, а тактовым импульсом с четным номером прием информации в соответствующий блок согласно коду управляющего слова.

Таким образом, каждый этап проверки выполняется за два такта.

В первом этапе проверки обычно происходит запись информации в регистр 6 коммутации и устанавливаются состояния элементов коммутатора 11 в соответствии с номерами входных и выходных контактов проверяемого блока 13. Последующая работа устройства происходит в двух режимах контроля и диагностики согласно алгоритму , приведенному на фиг.3.

В режиме контроля с поступлением на входы регистра 7 теста тестового слова на входные контакты проверяемого блока 13 через коммутатор 11 поступает определенный входной набор.

На входы блока 12 сравнения поступает эталонное тестовое слово (с выхода регистра 7 теста) и слово, несущее информацию о фактическом состоянии входов и выходов проверяемого блока 13.

В зависимости от результата сравнения работа устройства либо продолжается в режиме контроля, либо пр наличии неисправности переводится в режим диагностики.

В режиме диагностики старший разряд (режима работы) регистра 15 управляющего слова устанавливается в единичное состояние и блокирует прохождения сигналов с генератора 20 I

тактовых импульсов на счетчик 17, где остается номер кадра, в котором произошло несравнение.

Затем осуществляется поиск неисправностей путем дополнительной проверки уровня потенциалов в определенных внутренних точках проверяемого блока 13, предусмотренных прог- Фаммой поиска неисправностей.

При этом сигналы с выхода генератора 20 тактовых импульсов поступают на вход второго счетчика 16.

Для съема уровня потенциала в определенной точке проверяемого блока 13 в первом такте рассмотренного этапа работы в регистр 15 управляющего слова блока 1 управления принимается

соответствующее управляющее слово, а на втором такте на соответствующем выходе дешифратора 19 управления появляется единичный сигнал, который разрешает прием адреса из блока 4

памяти в регистр 9 адреса точки.

Аналоговый мультиплексор 10 выдает значение уровня потенциала в анализируемой точке на вход регистратора 8 по мере поступления адреса на его адресные входы.

В указанном порядке в регистр 15 принимается соответствующее управляющее слово, далее согласно соответ- ствук1щему состоянию дещифратора 19 происходит опрос состояния выходов регистратора 8.

Регистратор 8 работает следующим образом.. Сигнал из внутренней точки проверяемого блока 13 через аналоговый мультиплексор 10 поступает на входы всех пороговых элементов 22.

При этом срабатывают те элементы, порог срабатывания которых равен или

меньше потенциала рассмотренной точки.

С приходом сигнала Опрос с выхода дещифратора 19 на выходам; элементов И 21 появляется код, соответствующий уровню потенциала в анапкзи- руемой точке.

Если неисправность контролируемой цепи в результате данной операции не локализована, то согласно алгоритму поиска возможны следующие варианты действия; на входы проверяемого блока 13 с регистра 7 теста подается другой набор сигналов, блоком 10 выбирается следующая точка; первый

и второй варианты действия осуществляются одновременно. После любого из вариантов действия в зависимости от состояния выходов регистратора 8, счетчиков 16 и 17, блока 1 управле

ния и блока 12 сравнения формируется адрес слова программы, соответст- вуюцц й следующему варианту действия. При .завершении проверки результаты выводятся в блок 5 индикации.Тип и сложность выбранного алгоритма проверки цифровых блоков на принцип работы предлагаемого устройства не . влияют. Однако для правильной организации процесса проверки с помощью предлагаемого устройства необходимо учесть следующие обязательные требования при составлении программы проверки: в первом этапе заносится ин- форма:ция о входах и выходах в регистр 6 коммутации и до конца проверки данного типа цифрового блока содержимое регистра 6 не изменяется; после каждой выборки аналоговым мультиплексором 10 нужной точки опрашивается состояние выходов регистрато-, ра 8 (дпя правильного формирования адреса следующего слова программы, соответствующей алгоритму проверки).

Формула изобретения

Устройство для контроля и диагностики цифровых блоков, содержащее блок управления, регистр адреса, дешифратор адреса, блок памяти, блок индикации, регистр коммутации, регистр, теста, регистратор, коммутатор, блок сравнения, причем первый и второй выходы блока управления подключены к входам первого и второго разрядов регистра адреса, выход которого соединен с входом дешифратора адреса, выход которого ч:оеди нен с .информационным входом блока памяти.

информационный выход которого подключен к информационным входам блока индикации регистра коммутации, регистра теста и входу блока управления, третий, четвертый, пятый и шестой выходы блока управления подключены соответственно к входам разрешения блока индикации, регистра коммутации, регистра теста и стробирующему входу регистратора, выход регистра коммутации соединен с управляющим входом коммутатора, информационный вход которого соединен с выходом регистра теста и с первым входом блока сравнения, выход неравенства блока сравнения соединен с входом третьего разряда регистра адре- са, вход четвертого разряда которого .соединен с выходом регистратора, выход коммутатора соединен с входом контролируемого блока, первый выход которого соединен с вторым входом блока сравнения, отлича.юще- е с я тем, что, с целью повьпиения быстродействия, .в него введены ре- гистр адреса точки, мультиплексор и многоконтактный зонд, причем второй выход контролируемого блока подключен к входу многоконтактного JOHда, выход которого соединен с информационным входом мультиплексора, управляющий вход и выход которого соединены соответственно с выходом регистра адреса точки и информационным входом регистратора, информационный вход и вход разрещения регистра адреса точки соединены соответственно с информационным выходом блока памяти и седьмым выходом блока управлени я.

15

17

иг.1

-

20

иг.г

Пуск i

Устаноока нта/1ь ного адреса программы проверкиI

А

Формиродаиие

тестового

слаба

Ана/1из

реакции

объекта

у

Формирование начального адреЛ са программы поиска.

f

Формирование , координат c/ieoyw- щей контролируемой Towu длиной цепа

Ж

Измерение потенциат

Нет

Изменение

номера

проверки.

Формиротние координат точки.

одной из оходных цепей

Нет

Ин&и кация Годен

2- а8иение

нет

ФортроВаиие коЬ здииат следующей точки диаг - ностир. цепи

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и локализации неисправностей цифровых блоков | 1982 |

|

SU1067507A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Устройство для тестового контроля больших интегральных схем | 1984 |

|

SU1218390A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

Изобретение относится к вычислительной технике и предназначено для. производственного контроля цифровых узлов радиоэлектронной аппаратуры. Целью изобретения является повышение:быстродействия за счет автоматического съема значений сигналов с внутренних точек цифрового узла. Это достигается наличием в устройстве многоконтактного зонда, аналогового мультиплексора и регистра адреса точки. Адрес контролируемой точки заносится в регистр адреса точки и подается на адресные входы аналогового мультиплексора. Аналоговый мультиплексор выдает значение уровня потенциала в анализируемой точке на вход регистратора (дискриминатора). Регистр адреса точки определяет код уровня потенциала в контролируемой точке. Адрес очередной контролируе- (Мой точки определяется программой проверки и кодом на выходе регистратора. 4 ил. о

Индикация оборванной цепи

е

М

Нет

Фиг.З

Составитель И.Сафронова Редактор Н.Тупица Техред Л.Олейник Корректор Г.Решетник

Заказ 6840/48 671Подаисное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4

игл

| Устройство для контроля логических схем | 1976 |

|

SU595735A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обнаружения и локализации неисправностей цифровых блоков | 1982 |

|

SU1067507A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-23—Публикация

1985-06-18—Подача