(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕКОНФИГУРАЦИЕЙ МИКРОПРОГРАММНОГО ПРОЦЕССОРА

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметико-логическое устройство | 1987 |

|

SU1531086A1 |

| Устройство обработки информации | 1986 |

|

SU1451710A1 |

| Микропроцессор | 1989 |

|

SU1756897A1 |

| Адаптивное вычислительное устройство | 1980 |

|

SU957214A1 |

| Вычислительное устройство | 1983 |

|

SU1170448A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Арифметико-логическое устройство связного процессора | 1978 |

|

SU765808A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| Операционное устройство | 1985 |

|

SU1367012A1 |

| Устройство для выполнения арифметических и логических операций над словами | 1978 |

|

SU767757A1 |

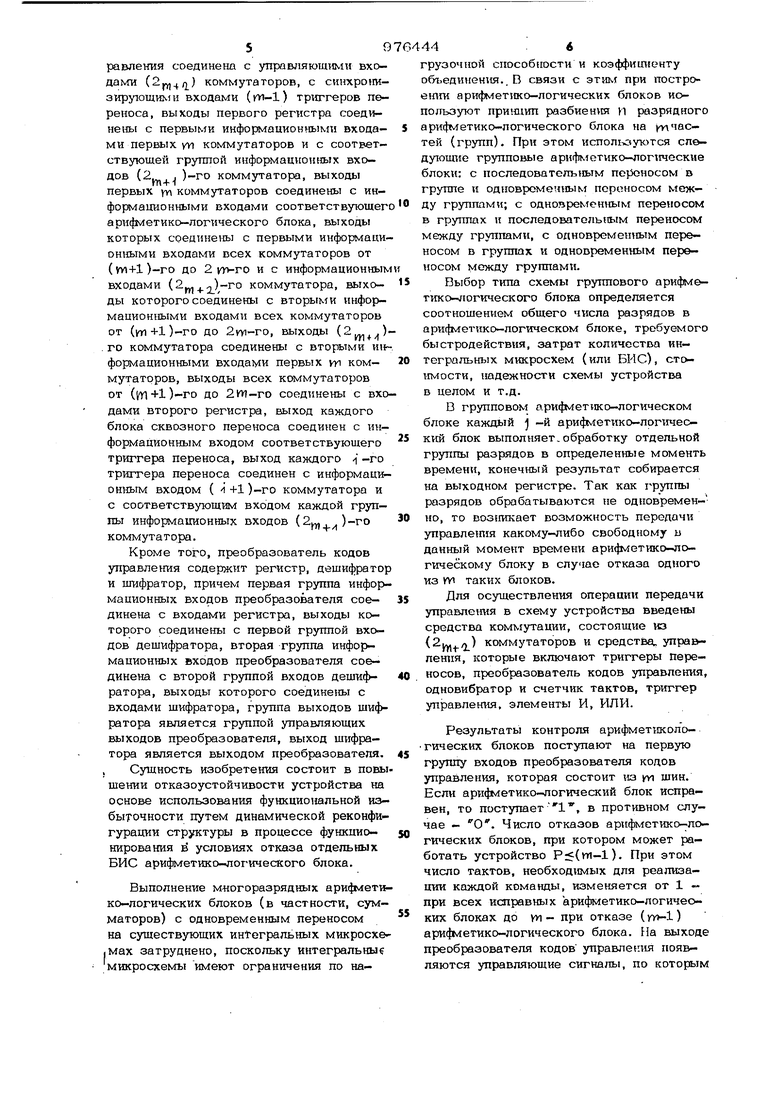

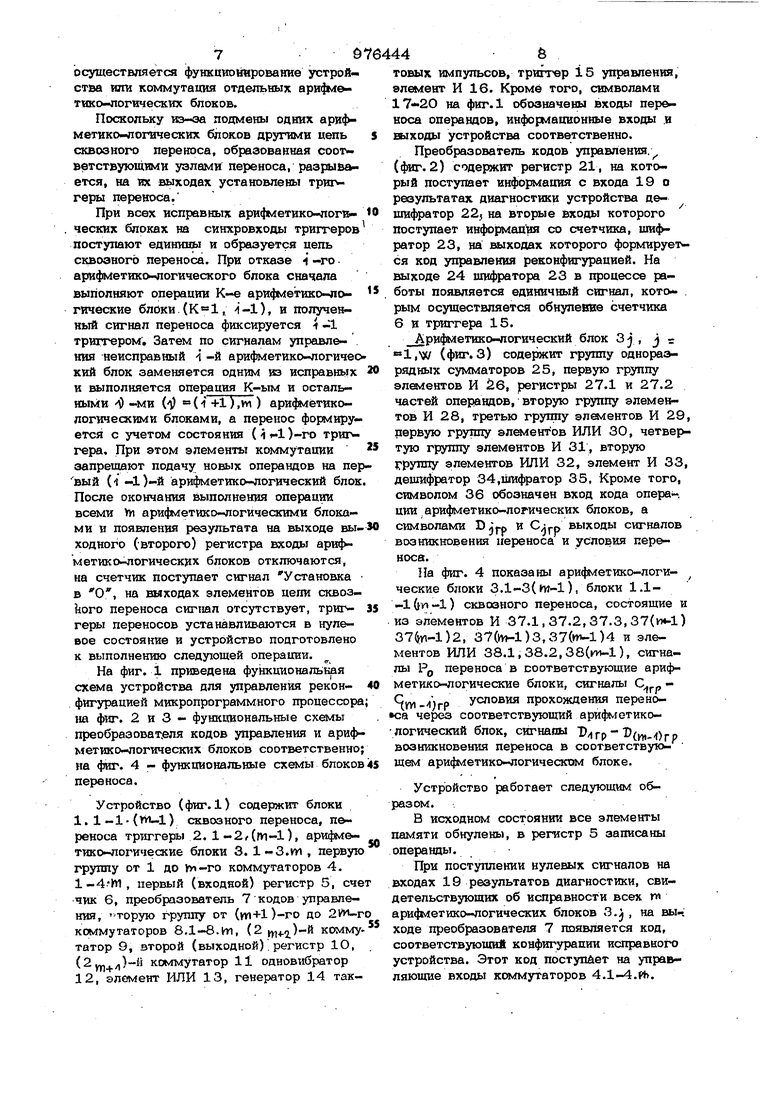

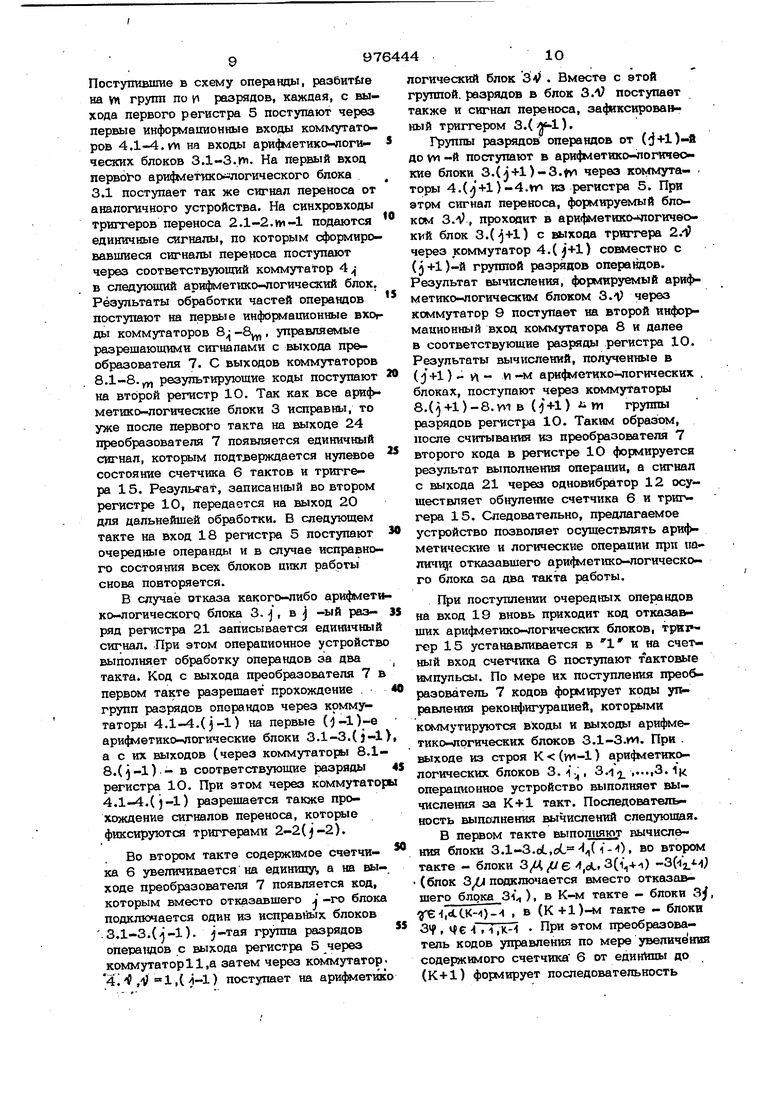

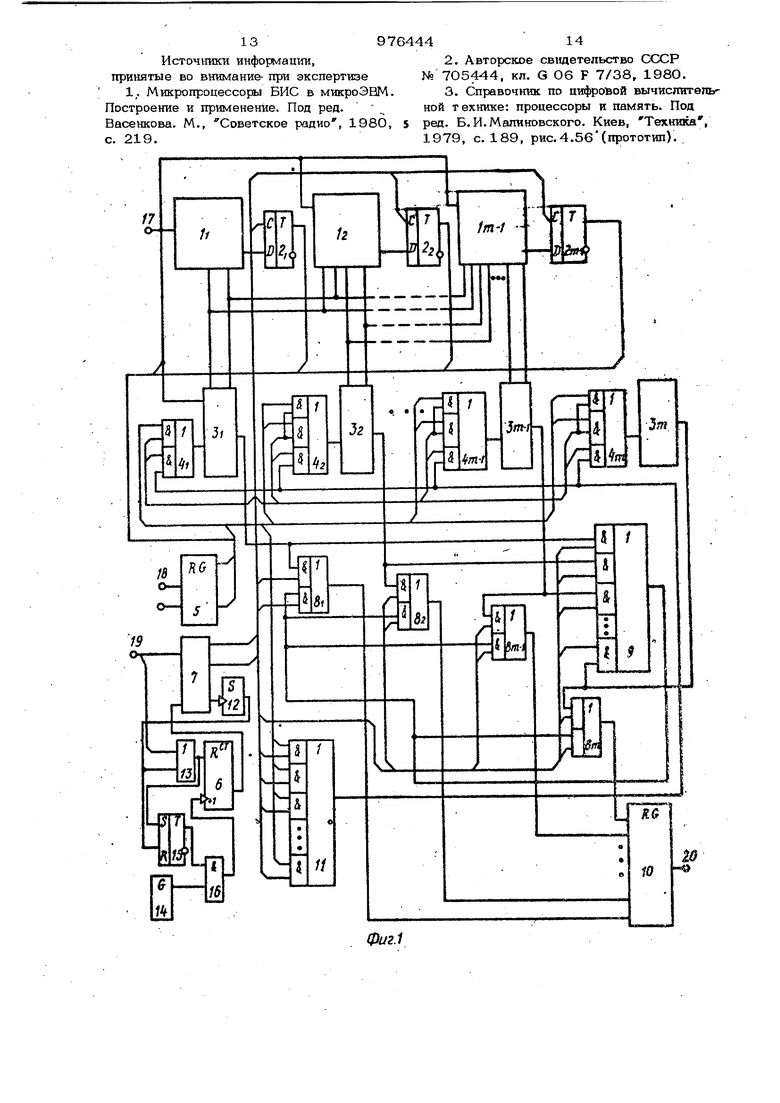

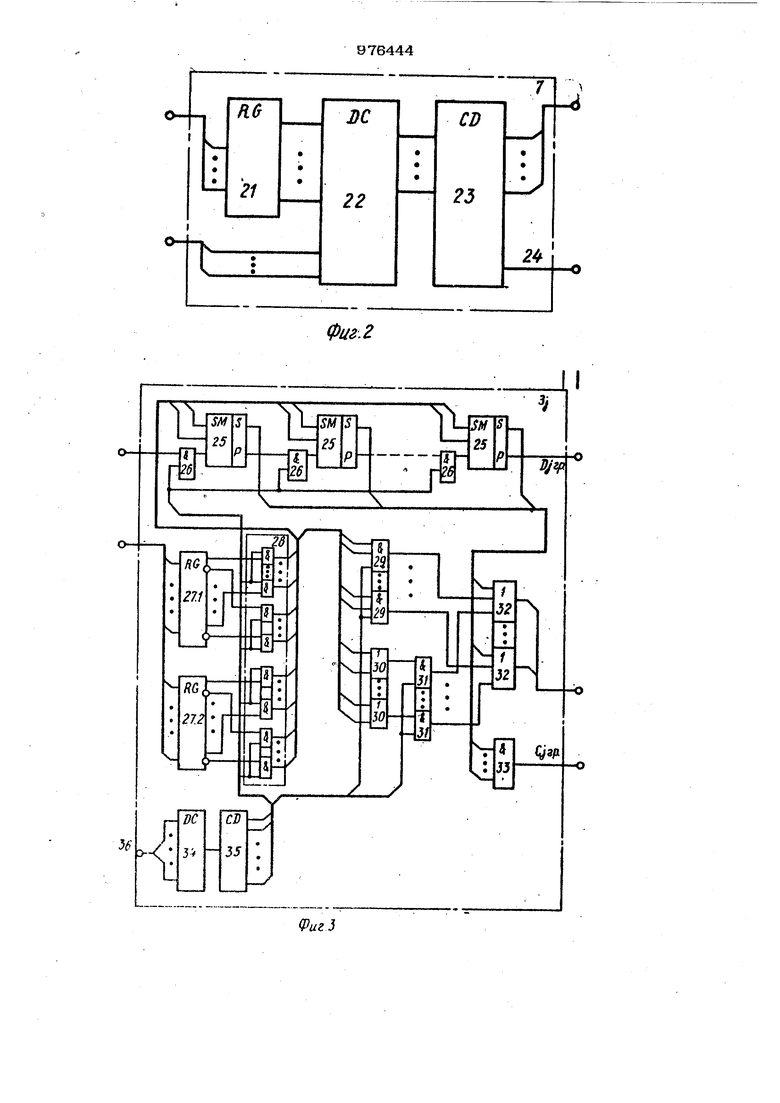

Изобретение относится к вычислитель ной. технике и может быть использовано при построении отказоустойчивых микропрограммных процессоров цифровых вычислительных систем. Известен блок программируемого интер фейса, построенный на БИС К587 ИК1 1 Недостатком блока является низкая функциональная надежность, так как при выходе из строя одной БИС К 587 ИК1 соответствующие ей внешние линии не управляются. В то же время функциональный резерв в виде оставшихся исправными БИС использован быть не может иэ-за отсутствия средств- реконфигурации. Известен операционный блок на микропроцессорах БИС К 589, а также операционный модуль на основе микропроцессора К 582 ИК 1 1. Недостатком их также является низкая функциональная надежность, обусповлениая отсутствием средств реконфигурации струк туры при отказах отдельных БИС. Известно также многоканальное операционное уст1 ойство, содержащее арифметико-логические блоки, регистры . Недостатком указанного устройства является низкая отказоустойчивость, которая вызвана невозможностью перестройки структуры при отказах. Наиболее близким по технияеской.сущности и достигаемому поломоттелькому эффект к предлагаемому является операционное устройство, допускающее наращивание обрабатываемых слов, содержащее Ы -1 блок сквозного переноса, у ари(} метико-логических блоков, первый н вуорой регистры, причем первые входы каждого блока сквозного переноса и вход переноса первого аримфетико-логического блока соединены с входом переноса, вход первого регистра является входом операндов устройства, выход второго регистра является выходом операционного устройства; выход условия переноса каждого -t -го арифметико-логического блока, где i меняется от 1 до1уу -1, соединен с (-j 1 )-м входом каждого j -го блока сквозного переноса, где j меняется от i до jn -1, выход группового переноса каждого 1 -го арифметико-логического блока соединен с ( 1+2)-м входом каж, дого j -го блока сквозного переноса. Разбитые на уп гругш операнды поступают на первый регистр и затем каждая группа поступает на соответствующий арифметико-логический блок, где проиоходит обработка поступившей инфорл ции. Одновремейно на шину переноса поступает единица переноса из предыдущих узлов, при наличии единицы переноса в одном из Kri арифметико-логических блоков на первом выходе появляется сигнал условия прохождения переноса через соответствующий узел переноса, а на втором выходесга-нал возникновения переноса в данном арифметико-логическом блоке. Блок перев носа организует сквозной перенос и вы- . числения в остальных арифметико-логических блоках происходят с учетом единицы переноса из младшего разряда. По соответствующим шинам результат вычисления записывается во второй (выходной регистр . Недостатком данного устройства является низкая отказоустойчивость, которая обусловлена тем, что при выходе из строя любой БИС ари(|ж 1етико-логинеского блока устройство выйдет из строя, так как част информации, обрабатываемая данным ариф .метико-лошческим блоком, будет потеря. на, что приведет к искажению конетного результата. Недостатком устройства также является функциональная избыточность (.9но состоит из однотипных функциональных узлов), которая не может быть использована для адаптации к условиям отказа. Т.е. структура устройства не предполагает идентификации отказавшего арифметико логического блока и передачи выполнения его фушсиий другому арифметико-логическому блоку, что снижает возможности при менения данного операционного устройства в современных вычислительных системах, требующих высоконадежных, гибких в управленик, самовосстанавливаемых структур. Так, например, при отказе -го ариф метико- 1огического блока вычисления могут быть организованы путем передачи А -ой части операндов на ( -i-l)-и или (4 +1)-й блоки после выполнения ими операций над (i-1)-й или (t +1)-й частями операндов. Однако в устройстве такая возможность не реализуется. Таким Образом, низкая отказоустойчивость указанного операционного устройства, обусловленная отсутствием средств реконфигурации его структуры на основе использования естественной функциональной избыточности, ограничивает функциональные возможности устройства и область его целесообразного применения, Оелью изобретения является повышение отказоустойчивости устройства за счет использования функциональной избыточности его структуры. Поставленн/ая цель достигается тем, что в устройство для управления реконфигурацией микропрограммного процессора, содержащее И1-1 блоков сквозного переноса, уп ери4метико-логических первый и второй регистры, причем вход переноса устройства соединен с первыми входами каждого блока сквозного переноса и входом переноса первого ариф метико-логического блока, входы операндов устройства соединены с входами перЁОГО регистра, выход второго регистра является информационным выходом устройства, выход услрвия переноса каждого арифметико-логического блока, где 1 1 - ( т-1), соединен с ( i +1 )-м вхоЛом каждого j -го блока сквозного переноса, где «1-{у)1-1), выход группового переноса каждого i -го арифметико-логического блока соединен с ( -j +2)-м вхоДОМ каждого j -го блока сквозного переноса, введены (2.„,„) коммутатора, (Ы-1) триггеров переноса, генератор таковых импульсов, счетчик, элемент И, элемент ИЛИ, одновибратор, преобразователь кодов управления и триггер управления, причем выход генератора соединен с первым входом элемента И, выход которого соединен со счетным входом счетчика. информационные входы устройства соединены с первой группой информационных ВХОДОВ преобразователя кодов управления И с группой входов элемента ИЛИ, выход которого соединен с установочньм входом счетчика и единичным входом триггера управления, единичный выход которого соединен с вторьш входом элемента И, информационные выходы счетчика соединены с второй группой входов преобразователя кодов управления, выход которого через одновибратор соединен с входом элемента ИЛИ и нулевым входом триггера управления, групш управляющих выходов преобразователя кодов у равления соединена с управляющими входами () коммутаторов, с синхронизирующими входами (кг1-1) триггеров переноса, выходы первого регистра соединены с первыми информационными входами первых уп коммутаторов и с соответствующей группой информациоч№1х входов (2, J )-го коммутатора, выходы первых YY коммутаторов соединеньт с информашшнными входами соответствующег ари(|метико-логического блока, выходы которых соединены с первыми информационными входами всех коммутаторов от ()-го до 2 vTt-ro и с информационным входами (2 2.) коммутатора, выходы которого соединены с вторыми информационными входами всех коммутаторов от (уг1+1)-го до 2vyi-ro, выходы (2j) . го коммутатора соединены с вторыми И1 формационными входами первых vri коммутаторов, выходы всех коммутаторов от (п+1)-го до 2И1-ГО соединены с вхо дами второго регистра, выход каждого блока сквозного переноса соединен с информадионным входом соответствующего триггера переноса, выход каждого -го триггера переноса соединен с информационным входом ( i +1 )-го коммутатора и с соответствующим входом каждой группы информационных входов (2 )-го коммутатора. Кроме того, преобразователь кодов управлеьгая содержит регистр, дещифратор и шифратор, причем первая группа информационных входов преобрзазователя соединена с входами регистра, выходы которого соединены с первой группой входов дешифратора, вторая группа инфо{ мационных входов преобразователя соединена с второй группой входов дешифратора, выходы которого соединены с входами шифратора, группа выходов шифратора является группой управляющих выходов преобразователя, выход шифратора является выходом преобразователя. , Сущность изобретения состоит в повы шении отказоустойчивости устройства на основе использования функциональной избыточности путем динамической реконфигурации структуры в процессе функпиоКирования и условиях отказа отдельных БИС арифметико-логического блока. Выполнение многоразрядных арифметико-логических блоков (в частности, сум- маторов) с одновременным переносом на существующих интегральных микросхе (Мах затруднено, поскольку интегральны микросхемы имеют ограничения по на944.6 грузочной способности и коэффициенту обт,единения.. В с этим при построетги ари({я 1етико-логических блоков иопользуют принпут paзбиeнvra п разрядного арифметико-логического блока на уулчастей (групп). При этом исполюуются следующие групповые арифметико-логические блоки: с последовательным переносом в группе и одновременным переносом меж- ДУ группами; с одновременным переносом в грутшах и последовательным переносом между группами, с одновременным переносом в группах и одновременным переносом между группами. Выбор типа схемы группового арифметико-логического блока определяется соотношением общего числа разрядов в арифметико-логическом блоке, требуемого быстродействия, затрат количества интегральных микросхем (или БИС), сто1п ости, надежности схемы устройства в целом и т.д. В групповом арифметико-логическом блоке каждый J -и арифметико-логичес й блок выполняет, обработку отдельной группы разрядов в определенные моменть времени, конечный результат собирается ™ выходном регистре. Так как группы разрядов обрабатываются не одновремен- но, то воз ткает возможность передачи управлешм какому-либо свободному Б данный момент времени арифметико-логическому блоку в случае отказа одного из W таких блоков. Для осуществления операции передачи управления в схему устройства введены средства коммутации, состоящие из (2 ,j) коммутаторов и средства„ упра&лешш, которые включают триггеры переносов, преобразователь кодов управления, одновибратор и счетчик тактов, триггер управления, элементы И, ИЛИ. Результаты контроля арифметиколо- гических блоков поступают на первую группу входов преобразователя кодов управления, которая состоит из км шин. Если арифметико.-логический блок исправен, то поступает , в противном случае - О. Число отказов арифметико-логических блоков, при котором может работать устройство Р:(и1-1). При этом число тактов, необходимых для реализации каждой команды, изменяется от 1 - при всех исправных арифметико-логичеоких блоках до т- при отказе (т-1) арифметико-логического блока. На выходе преобразователя кодов управления появляются управляющие сигналы, по которым Ьсуществпяегся функцшнирование устройства юга коммутация отдельных арифметико-логических блоков. Поскольку из-за подмены одних арифметико-пошческих блоков другими цепь сквозного переноса, образованная соот в тствующвми узлами переноса, разрывается, на их выходах установлены три1 геры переноса. При всех исправных арифметико-логи. ческих блоках на синхровходь триггеров поступают единишл и образуется цепь сквозного переноса. При отказе i -го арифметико-логического блока сначала выполняют операции К-е арифметшсо-логические блоки (К 1, i-l), и полученный сигнал переноса фиксируется 4-1 трштером. Затем по сигналам управления неисправный л -и арифметико-логичео кий блок заменяется одним из исправньтх и выполняется операция К-ым и остальными -ми ( в (1 +1) ,wi) арифметикологическими блоками, а перенос формируется с учетом состояния ()-ro трш гера. При этом элементы коммутации запрещают подачу новых операндов на пер вый (i -1)-и арифметико-логический блок После окончания выполнения операции всеми УИ арифметико-логическими блоками и появления результата на выходе выходного (второго) регистра входы ариф метико-логических блоков отключаются, на счетчик поступает сигнал Установка в О, на выходах элементов цепи сквозkoro переноса сигнал отсутствует, триггеры переносов устанавливаются в нулевое состояние и устройство подготовлено к выполнению следующей операции. На фиг. 1 приведена функциональная схема устройства для управления рекон. фигурацией микропрограммного процессора на фиг. 2 и 3 - функциональные схемы преобразователя кодов управления и ари(} метико-логических блоков соответственно на фиг. 4 - функциональные схемы блоков переноса. Устройство (фиг. 1) содержит блоки 1. 1 - 1 {W1-1) сквозного переноса, переноса триггеры 2. 1-2Дм-1), арифметико-логические блоки 3. l-3.ni , первую группу от 1 до коммутаторов 4. l-4hl, первый (входной) регистр 5, сче чик 6, преобразователь 7 кодов управления, торую группу от (к1П+1)-го до коммутаторов 8.1-8.И1, (2 у.}- комму татор 9, второй (выходной) регистр 10, (2у,)-й коммутатор 11 одновибратор 12, элемент ИЛИ 13, генератор 14 тактовых импульсов, триггер 15 управления, элемент И 16. Кроме того, символами 17-2О на фиг.1 обозначены входы пер&носа операндов, информационные входы .и выходы устройства соответственно. Преобразователь кодов управления. (фиг. 2) содержит регистр 21, на который поступает информация с входа 19 о результатах диагностики устройства дешифратор 22; на вторые входы которого поступает инфо змапия со счетчика, шиф ратор 23, на выходах которого формируется код управления реконфигурацией. На выходе 24 шифратора 23 в процессе работы появляется единичный сигнал, которым осуществляется обнулевве счетчика б и триггера 15. Арифметико-логический блок 3j, j г el,W (фиг.3) содержит группу одноразрядных сумматоров 25, первую группу элементов И 26, регистры 27.1 и 27.2 частей операндов, вторую группу элементов И 28, третью группу элементов И 29, первую группу элементов ИЛИ 30, четверо тую группу элементов И 31, вторую Группу элементов ИЛИ 32, элемент И 33, дешифратор 34,шифратор 35, Кроме того, символом 36 обозначен вход кода опера ции арифметико-логических блоков, а символами D,jj.p и выходы сигналов возникновения переноса и условия переноса. На фиг. 4 показаны арифметико-логические блоки 3.1-3(И7-1), блоки 1.1-l(fvi-l) сквозного переноса, состоящие и из элементов И 37.1, 37.2,37.3,37(и«-1) )2, 37(m-l)3,37(w-l)4 и элементов ИЛИ 38.1,38.2,38(км-1), сигналы Рр переноса в соответствующие ариф метико-логические блоки, сигналы С. „ Яш -VjrP условия прохождения переноса через соответствующий арифметикологический блок, сигнаяы D-irp- Ос.-Огр возникновения переноса в соответствующем арифметико-логическом блоке. Устройство работает следующим обазом. В исходном состоянии все элементы амяти обнулены, в регистр 5 записаны операнды. При поступлении нулевых сигналов на входах 19 результатов диагностики, свиетельствующих об исправности всех г« арифметико-логических блоков 3. , на вы-: ходе преобразователя 7 появляется код, соответствующий конфигурации исправного устройства. Этот код поступает на упра&ляющие входы коммутаторов 4.1-4.f1. Постутгавшие в схему операнда, разбитие на уу групп по у разрядов, каждая, с выхода первого регистра 5 поступают через первые информационные входы коммутаторов 4.1--4.VM на входы арифметико-поги ческих блоков 3.1-З.Ш. На первый вход nepBolo артфлетикочпогического блока ЗД поступает так же сигнал переноса от аналогичного устройства. На синхровходы триггеров переноса 2.1-2.уи-1 подаются единичные сигналы, по которым сформировавшиеся сигналы переноса поступают через соответствующий коммутатор в следующий арифметико-логический блок. Результаты обработки частей операндов поступают на первые информационные вхог ды коммутаторов 8 бу Управляемые разрешающими сигнапами с выхода преобразователя 7. С выходов коммутаторов 8.1-8. результирующие коды поступают на второй регистр Ю. Так как все арифметико-логические блоки 3 исправны, то уже после первого такта на выходе 24 преобразователя 7 появляется единичный сигнал, которым подтверждается состояние счетчика 6 тактов и триггера 15. Резулыгаг, записан1аз1й во втором регистре 10, передается на выход 20 для дальнейшей обработки. В следующем такте на вход 18 регистра 5 поступают очередные операнды и в случае исправного состояния всех блоков цикл работы снова повторяется. В случае отказа какого-либо арифмет ко-логическогр блока 3, , в j -ый раз- ряд регистра 21 записывается единичный сигнал. При этом операционное устройство выполняет обработку операндов за два такта. Код с выхода преобразователя 7 в первом такте разрешает прохождение . групп разрядов операндов через коммутаторы 4.1-4.(j-1) на первые (-1)-е арифметико-логические блоки 3.1 -3. {j -1 а с их выходов (через коммутаторы 8.18.(-1) - в соответствующие разряды регистра 10. При этом через коммутатор 4.1-4.()-1) разрешается также прохождение сигналов переноса, которые фиксируются триггерами 2-2(-2). Во втором такте содержимое счетчика 6 увеличивается на единицу, а на выходе преобразователя 7 появляется код, которым вместо отказавшего j -го блока подключается один из исправйых блоков . 3.1-3.(-J-1). -тая группа разрядов операвдов с выхода регистра 5 через коммутатор 11,а затем через коммутатор. 4.9 ,V ,( -i-l) поступает на арифметико логический блок 3V . Вместе с этой группой, разрядов в бпок З.Л7 поступает также и сигнал переноса, зафиксированный триггером 3.(). Группы разрядов операндов от (j-fl)-fl до Ум -и поступают в ари4метико-погичес кие блоки 3,(j-fl)-3.fvi через коммута- . торы 4.(+1)-4.1Г иэ регистра 5. При 9трм с 1гнал перекоса, формируемый блоком 3.V, проходит в арифметико-чтогичбокий блок 3.(-j-H) с выхода триггера 2/i через коммутатор 4.( j+1) совместно с (+1)-й группой разрядов операндов. Результат вычисления, формируемый арифметико-логическим блоком 3.1) через коммутатор 9 поступает на второй информационный вход коммутатора 8 и далее в соответствующие разряды регистра Ю. Результаты вычислений, полученные в () и-м арифметико-логических . блоках, поступают через коммутаторы 8.(+1)-8. в (-И) г группы разрядов регистра 10. Таким образцом, после считывания из преобразователя 7 второго кода в регистре 10 формируется результат выполнения операции, а сигнал с выхода 21 через одновибратор 12 осуществляет обнуление счетчика 6 и триггера 15. Следовательно, предлагаемое устройство позволяет осуществлять ари(| метические и лoгичecкvIe операции при tm личи5р отказавшего арифметико-логического блока за два такта работы. При поступлении очередных операндов на вход 19 вновь приходит код отказавших арифметико-логических блоков, триггер 15 устанавливается в и на счет- ный вход счетчика 6 поступают тактовые импульсы. По мере их поступления преобразователь 7 кодов формирует коды управления реконфигурацией, которыми коммутируются входы и выходь1 арифметико-члргических блоков 3.1-3.VM. При . выходе из строя К (vvi-l) ари4метикологических блоков 3.-i., 3.1-2. f-M. IK операционное устройство выполняет вычисления за K-l-l такт. Последовательность выполнения вычислений следующая. В первом такте выполняют вычисления блоки 3.1-3.oL,.if I-t), во втором такте - блоки .dLf 3() 3() (блок 3 подключается вместо отказавшего блока 3i ), в К-м такте - блоки 3, ,«LtK-1)- , в (К+1)-м такте - блоки , if е 4, 1,хч При этом преобразователь кодов управления по мере увеличения содержимого счетчика 6 от единй1Ы до (К+1) формирует последовательность кодов, которые управляют коммутаторами (4,8, 9 и 11. При выходе из строя (т-1)-го блока устройство производит . вычисления ocтaвши Icя работоспособным ари етико- огическим блоком, который за кп тактов последовательно обрабатывает m групп разрядов операндов. При этом преобразователь 7 кодов управления реконфигурацией последовательно формирует Р кодов, которые путем коммутации осу. шествляют последовательную передачу групп разрядов операндов в этот блок, а с его выхода - в соответствующие разряды регистра 1О. Таким образом, предлагаемое устройство существенно превосходит известное по отказоустойчивости. Применение уст ройства позволяет строить отказоустойчивые вычислительные системы,, обеспечивающие также требуемую производитель ность при заданной интенсивности техяи ческого обслуживания. Формула изобретения 1. Устройство для управления реконфигурацией микропрограммного процессора, содержащее () блоков сквозного , переноса, ари4мегтсо-логическ 1х блоков, перВ|1 1й и второй регистры, причем вход переноса устройства соединен с первыми входами каждого блока сквозного переноса и входом переноса первого ариф метико-логического блока, входы операнСдов устройства соединены с входами первого регистра, выход второго регистра является информационным выходом устрой ства, выход условия переноса каждоро 1 -го арифметико-логического блока, где i 1-(т-1), соединен .с (i-H)-M входом каждого -го блока сквозного переноса, .где } -(rvi-l), выход группового переноса каждбго 1 -го арифметико-логичес кого блока соединен с ( 1+2)-м входом каждого и-го блока сквозного переноса, отличающееся тем, что, с целью повышения. отказоустойчивости, в устройство введены (2ion-2) коммутатора {т-1) триггеров переноса, генератор тактовых импульсов, счетчик, элемент И, элемент ИЛИ, одновибратор, преобразователь кодов управления и триггер управления, причем выход генератора соединен с первым входом элемента И, выход которого соединен со счетным входом счет чика, информационные входы устройства соединены с первой группой информационных входов преобразователя кодов упра&ленвя и с группой входов элемента ИЛИ, выход которого соединен с установочным входом счетчика и единичным входом трштера управления, еди1гачный выход ко. торого соединен с входом элемента И, информационные выходы счетчика соединены с второй группой входов преобразователя кодов управления, выход которого через одновибратор соединен с входом элемента ИЛИ и нулевым входом триггера управления, группа управляющих вы ходов преобразователя кодов управления соединена с управляющими входами () коммутаторов, с синхронизирующмч и входами (m-l) триггеров переноса, выходы первого регистра соединены с первыми информационными входами первых км коммутаторов и с соответствующей группой информационных входов (2)+1)-го коммутатора, выходы первых (П коммутаторов соединены с инфор 1ационными входами соответствующего ари етико- 1огического блока, выходы которого соединены с первыми информационными входами всех коммутаторов от ( т+1 )-го до 2уу)-го и с информационными входами (2v)i+2)-ro коммутатора, выходы которого соединены с вторыми информационными входами всех коммутаторов от (ки+1)-го до 2 т-го, выходы (2 п1+1)-го .коммутатора соединены с вторыми информационными входами первых wi коммутаторов, выходы всех коммутаторов от )-го до 2w-ro соединены с входами второго регистра, выход каждого блока сквозного переноса соединен с информационным входом соответствующего триггера переноса, выход каждого -I-ro триггера переноса соединен с информационным входом ( +1 )-го коммутатора и с соответствующим входом каждой группы инфор мационных входов (2Vii+l)-ro коммутатора. 2. Устройство по п. 1, отличающее с я тем, что преобразователь кодов управления содержит регистр, дещифратор и щифратор, причем первая группа информационных входов преобразователя соединена с входами регистра, выходы которого соединены с первой группой входов дещифратора, вторая группа инфо1Ж1ационных входов преобразователя соединена е второй группой входов дешифратора, выходы которого соединены с входами шифратора, группа выходов цгифратора является грухшой управляющих Ш11ХОДОВ преобразователя, выход щифратора является выходом преобразователя.

1397644414

ИСТОЧ1ШКИ информации,2. Авторское сввдетельство СССР

принятые во внимание-при экспертизе№ 705fl44, кл, G 06 F 7/38, 198О.

1,. Микропроцессоры БИС в микроЭВМ.3. Справочник по цифровой вычистггепы

Построение и применение. Под ред. - ной технике: процессоры и память. Под

Васенкова. М., Советское радио , 1980, 5ред. Б.И.Малиновского. Киев, Техника,

с- 219.1979, с. 189, рис.4.56(прототип).

Авторы

Даты

1982-11-23—Публикация

1981-05-04—Подача