Изобретение относится к области вычислительной техники и цифровой автоматики и может ыть использовано в специализированных вычислительных системах, управляющих комплексах и информационно-измерительных устройствах.

Известно устройство для поиска неисправных блоков и элементов, содержащее регистры параметров объекта и параметров таблицу неисправностей, логическую матрицу сравнения двоичных кодов параметров от контролируемых блоков и двоичных кодов таблицы неисправностей, схему выбора номера неисправных блоков и блок индикации.

Однако повышение быстродействия достигается в известном устройстве за счет слишком высоких аппаратурных затрат, затрудняющих практическую реализацию устройства, так как сложность его в п раз оказывается больше, чем сам контролируемый объект.

Наиболее близким по технической сущности и достигнутому результату к предлагаемому изобретению является устройство поиска неисправных блоков и элементов, содержащее регистр столбцов и регистр параметров объекта, выходы которых соединены с последовательной цепью в биде блока сравнения, блока оценки, регистра оценки, блока выбора единицы, шифратора, первого и второго постоянного запоминающего устройства (ПЗУ), регистра выходного блока схем И-НЕ, блока схем Л, регистра результата и блока индикации, управление которыми осуществляет блок управления с независимым входом, выходы которого соединены со всеми регистрами ПЗУ, и блоком выбора единиц.

Недостатком данного устройства является его конструктивная сложность, выражающаяся в наличии шифратора, блока сравнения, нескольких регистров и сложного блока выбора единиц, а также его узкие функциональные возможности, ограничивающиеся реализацией только прямых функций поиска неисправных блоков и элементов и индикацией результата для анализа оператором. Кроме того, данное устройство не может чбь1ть использовано (без изменения в его структуре или внесения внешних блоков) в управляющих и микропроцессорных комплексах с автоматическим режимом принятия решения, так как не содержит цепей выдачи результата в такие комплексы и не имеет средств проверки достоверности контроля, т.е. было ли исправно само устройство поиска в процессе его работы: не может быть использовано устройство и для проверки элементов вычислительной техники типа

БИС ПЗУ, ПЛМ, дешифратор и другие, которые являются основой построения вычислительных и управляющих устройств.

Целью изобретения является расширение области применения устройства путем одновременного контроля разнородных типовых блоков вычислительной техники.

Поставленная цель достигается тем, что в устройство поиска неисправных блоков и

0 элементов, содержащее два блока памяти таблицы неисправностей, блок оценки кода исправности, регистр параметров объекта, первый блок элементов И, регистр результата, блок управления и блок индикации, вход

5 которого соединен с выходом прямого кода регистра результата, информационный вход которого связан с выходом первого блока элементов И, группы входов которого подключены к группе выходов блока оценки кода

0 исправности, согласно изобретению дополнительно введены два счетчика, два блока элементов ИЛИ, второй блОк элементов Ии блок контроля результата, установочные входы, информационные и индикационные выхо5 ды которого являются соответствующими. входами и выходами устройства, управляющий выход соединен с входом первого блока элементов И, группа -контрольных выходов связана с группой информационных входов

0 блока управления, тактовый вход подключен к выходу переполнения второго счетчика, а группа входов результата, первая группа входов первого блока элементов ИЛИ и группа выходов результата проверки устройства соединены с выходом обратного кода регистра результата, управляющий считыванием информации вход которого, управляющие считыванием информации входы регистра параметров объекта, регистра оценки первого и второго блоков памяти таблицы неисправностей, блока оценки кода исправности, входы счетчиков, вторая группа входов первого блока элементов ИЛИ, первая группа входов второго блока элементов И и группа входов синхронизации блока контроля результата связаны с группой выходов синхронизации блока управления, информационный выход, индикационные зыходы и вход запуска которого являются соответствующими выходами и входом устройства, адресные входы первого и второго блоков памяти таблицы неисправностей соединены с выходом первого счетчика, установочные входы счетчиков

5 служат соответствующими входами устройства, группы выходов блоков памяти таблицы неисправностей связаны с третьей и четвертой группами входов первого блока элементов ИЛИ, выход которого подключен к информационному входу регистра оценки и

к первому входу второго блока элементов ИЛИ, второй вход которого является информационным входом устройства,а выход соединен с информационным входом регистра параметров объекта, группа выходов которого связана с пятой группой входов первого блока элементов ИЛИ и с первой группой информационных входов блока оценки кода исправности, вход синхронизации которого подключен к выходу второго блока элементов И, а вторая группа информационных входов и вторая группа входов второго блока элементов И соединены с группой выходов регистра оценки.

В предлагаемом устройстве сохранены связи между вторым блоком элементов И, регистром peзyльтafa и блоком индикации и связи блока управления с двумя блоками памяти таблицы неисправностей, регистрами и вторым блоком элементов И, все остальные связи между известными и вновь введенными блоками являются новыми. К числу новых связей относятся все соединения с первым блоком элементов ИЛИ, т.е. выходы .первого блока и второго блоков памяти таблицы неисправностей, выход регистра параметров объекта, выход регистра результата и выход блока управления со входами первого блока элементов ИЛИ, а также соединения выхода первого блока элементов ИЛИ с входом регистра оценки и выхода регистраоценки с входами второго блока элементов И и блока оценки кода исправности, соединения выхода регистра результата с входом блока контроля результата и выхода блока контроля с входами первого блока элементов И и блока управления, а также выхода блока управления с входом блока контроля результата, выхода второго счетчика с входом блока контроля результата. Все новые связи вместе с вновь введенными блоками обеспечивают расширение области применения устройства путем одновременного контроля разнородных типовых блоков вычислительной техники. X

На фиг.1 представлена структурная схема устройства; на фи,г.2 - структурная схема устройства с детализацией комбинационных блоков; на фиг.З-то же, блока контроля результата; на фиг.4 - алгоритм работы предлагаемого устройства; на фиг;5 - граф переходов блока управления; на фиг.6 структурная схема блока управления с детализацией узла контроля правильности переходов; на фиг.7 - схема коммутатора; на фиг.8 - схема узла проверки контрольного кода; на фиг.9 - структурная схема шифратора, регистра, узла элементов И и счетчика блока управления; на фиг.10,11 - первый и

второй варианты реализации генератора импульсов; на фиг. 12 - временная развертка сигналов генератора для второго варианта реализации; на фиг. 13 - схема регистра

оценки и регистра параметров объекта; на фиг.14 - схема регистра результата.

На фиг. 1-6 обозначены входы и выходы: Со - установка нулевого состояния; Ci запись кода; Са - считывание прямого кода;.

Сз - считывание обратного кода; С4 - прибавление 1 к счетчику; Cs - синхронизация первого блока элементов И 11 (1 БлСхИ-11); Сб - ввод единицы через первый блок элементов ИЛИ4(1БлСхЙЛИ-4)на РгО-5;

С - синхронизация второго блока элементов И 6 (2БлСхИ-6); Снач - сигнал остановки устройства после завершения работы устройства; Сош - сигнал ошмбки переходов, останавливающий работу устройстйа; «2 устройство исправно; «2-устройство неисправно; а о - режим поиска неисправных блоков и элементов; а о - режим контроля исправности элементов вычислительной техники; а i - обнаружение неисправности;

а 1 - отсутствие неисправности; аз- конец ввода в устройство таблицы функций неисправностей; «3 - продолжение ввода в устройство таблицы функций неисправностей; Ao,Ai,A2,...A20 - операторы управления, содержательный смысл и набор микроопераций в которых приведены в табл.3.

Для лучшего понимания в дальнейшем микрооперациям управления приписаны номера тех блоков элементов, которыми они

управляют. Например, в блоке 15 триггеры 35 и 38 имеют сигналы управления Со(35), Со(38), элементы И 34, И 37, сигналы Ciis-l). Ci(37). ,

Устройство поиска неисправных блоков

и элементов содержит {фиг.1) первый счетчик (Сч) 1, выход которого соединен с адресными входами первого 2 и второго 3 блоков памяти таблицы неисправностей ПЗУ, группы выходов которых связаны с

третьей и четвертой группами входов первого блока элементов ИЛИ 4 (1 БлСхИЛИ), выход которого подключен к информационному входу регистра 5 оченки (РгО), группа выходов которого соединена с второй группой информационных входов второго блока элементов И 6 (2БлСхИ) и с второй группой информационных входов блока 7 оценки кода исправности (ВО), выход второго блока элементов И 6 (2БлСхИ)

соединен с входом синхронизации блока 7 оценки кода исправности (ВО), выход первого блока элементов ИЛИ 4 (1 ВлСхИЛИ) подключен к первому входу второго блока элементов ИЛИ 8 (2ВлСхИЛИ). второй-вход

9 которого является информационным входом уртроЯСтва, а выход соединен с информациркнымвхрдрм регистра 10 параметРО.В объекта (РгПО), группа выходов которого связана с пятой группой входов первого блока элементов ИЛИ (1БлСхИЛИ) и с первой группой информационных входов блока 7 оценки кода исправности (БО), группа выходов которого подклиэчена к группе входов пер врго блока элементов И 11 (1 Бл0хИ), выход которого связан с информационным входом регистра 12 результата (РгР), выход прямого кода которого соединён с блока 13 индикации (БИ) и с группой выхРдов 14 результатов проверки устройства, а выход обратного кода соединён с группой выходов 14 результатов проверки устройства, с первой группой входов первого блока элементов ИЛИ 4 (ТБлСхИЛИ) и с группой входов результата блока 15 контроля результата (БК), имеющего информационные выходы 16,17,индикационные выходы 1;8,19 и установочные входы 20-1,20-2, являющиеся соответствующими выходами и входами устройства, тактовый вход блока 15 контроля результата (БК) подключен к выходу переполнения

) второго.счетчика 21 (Сч), имеющего установочный вход 22, являющийся соответствующим вводом устройства, управляющий выход блока 16 крнтроля результата (БК) соединен с входом первого блока элементов И 11 (1БлСхИ), группа контрольных выходов блока 15 контроля результата (БК) связана с группой информационных входов блока 23 управления (БУ), имеющего вход 24 запуска, индикационные выходы 25,26,.информационный выход 27, являющиеся со ответствующими входом и выходом устройства, с группой выходов синхронизации блока 23 управления (БУ) связаны счетные входы счетчихов

1и 21, управляющие считыванием информации входы первого и второго блоков памяти таблицы неисправностей 2 и 3 (ПЗУ), вторая группа входов первого блока элементов ИЛИ 4(1 БлСхИЛ И), уНравляющий считыванием информации вход регистра оценки 5 (РгО), первая группа входов второго блока элементов И б (2БлСхИ), управляющие считыванием информации входы блока 7 оценки кода исправности (БО), регистра 10 параметров объекта (РгПО), регистра 12 результата (РгР) и группа входов синхронизации блока 15 контроля результата (БК), при этом первый счетчик 1 (Сч) имеет установочный вход 28-1, информационный выход 28-2 и индикационный выход 29, являющиеся соответствующими входом и выходами устройства.

Блоки 4,6,8,11 устройства и элемента

блока 7 оценки кода исправности, блока 15

|. контроля результата, блока 23 управления

типовые и реализуются серийными БИС из

типовых интегральных комплектов (например, логики К155). В частности все регистры 5,10,12 имеют типовую структуру на статических триггерах, , позволяют осуществить прием прямого кода (при подаче

0 сигнала С1),хранениеи выдачу прямого.(сигнал Са) или обратного (сигнал Сз) кода, при этом установка исходного (нулевого) состояния производится сигналом Со.

Считывание сигнала с единичного (С2

5 и нулевого (Сз) выходов триггеров регистра 5,10 производится через схемы ИЛИ (фиг.1,13), ас единичного и нулевого выходов триггеров регистра 12 производится раздельно (фиг, 1,14).

0 Счетчики 1,21 - обычные счетчики последовательного суммирования единиц, имеющие, кроме того, установочные входы 22,28 - 1, позволяющие занести параллельно начальный код. Этот тип счетчиков име5 ется в серийных типовых наборах логики.

Блок оценки кода исправности представляет собой (фиг.2) п элементов ИЛИ-НЕ

30.1,одни входы которых соединены с управляющим выходом С7(30) БУ23, а другие

0 соединены с соответствующими выходами регистра оценки 5, выход которых соединен с первым входом элементов И 30.2, выход котррых соединен с вторым входом соответствующего (каждому элементу

5 ИЛИ-НЕ 30.1, И 30.2) элемента ИЛИ-НЕ 30.3, выход которого, соединен с входом соответствующего элемента И первого блока элементов И 11, причем для любого 1-го элемента И 30.2 первый вход соединен

0 с 1-м выходом регистра оценки 5 через i-ю схему ИЛИ-НЕ 30.1, а все другие выхо,цы Рг05(дляУ 1,2n/i j), кроме i-ro, подаются на (п-1) других входов i-ro элемента И

30.2,соответствую щие 1-е выходы второго 5 блока элементов И 6 и регистра 10 параметров объекта являются третьими первым входами элементов ИЛИ-НЕ 30.3 блока оценки 7 (фиг.2). ,- .

Блок 13 индикации реализуется в виде 0 п светодиодов, каждый из которых соединен с потенциальным единичным выходом регистра 12 результата. Индикаторы 18,19,25,26 также выполняются в виде светодиодов по одному на каждый выход соответствующего 5 блока. Индикатор первого счетчика 29 со-. стоит из m светодиодов, где m - число разрядов счетчика.

Блоки памяти таблицы неисправностей - постоянные запоминающие устройства (ПЗУ 2,3) - типовые БИС ПЗУ с

электрическим или yльтpaфиoлeтoвы 4 стиранием или ферритовые ПЗУ для специальных управляющих систем автоматики с повышенными требованиями к механикоклиматическим режимам работы, а также любые типы ПЗУ в зависимости от типа систем управления для микропроцессорной системы, подлежащей поиску неисправностей. Если устройство поиска неисправных блоков и элементов используется только в конкретной микропроцессорной системе (следовательно, необходима запись одной единственной конкретной таблицы неисправностей), то целесообразно использовать ПЗУ с пережигаемыми перемычками, так как они обладают повышенным быстро действием по сравнению с другими тйпй-г ми БИС ПЗУ. Для каждого ПЗУ блок управления выдает две команды (Ci,C2). Причем в первое ПЗУ (2) и второе ПЗУ (3) записывается одна и та же таблица неисправностей, но запись производится таким образом, чтобы обеспечивалось считывание таблицы по столбцам из первого ПЗУ 2 и по строкам второго ПЗУ 3. Код адреса для обоих ПЗУ берется один и тот же с суммирующего счетчика 1. Для расширения области применения предлагаемого устройства вместо ПЗУ может включаться также программируемая логическая матрица, дешифратор, регистр, счетчик и другие блоки вычислительной техники.

БЛОК 15 контроля результата (фиг.З) включает в себя первый триггер Т 31, единичный вход которого подключен к тактовому входу О Jmax) блока, второй триггер Т 32, нулевой и единичный входы которого соединены соответственно с первым 20-1 и вторым 20-2 установочными входами блока, п входовый первый элемент ИЛИ 33, входы которого подключены к группе входов результата блока, а выход связан с вторым входом первого элемента И 34, выход И 34 подключен к единичному входу третьего триггера Т 35, прямой выход Т 35 соединен с первым входом второго элемента И 36 и индикационным выходом 18 блока, выход И 36 связан с информационным выходрм 16 блока, одновременно выход первого элемента ИЛИ 33 образует вторую последовательную цепь, при этом выход ИЛИ 33 связан с вторым входом третьего элемента И 37, выход которого подключен к единичному входу четвертого триггера Т 38, прямой выход которого соединен с первым входом четвертого элемента И 39 и индикационным выходом 19 блока, выход И 39 связан с информационным выходом 17 блока, прямые выходы третьего Т 35 и четвертого Т 38 триггеров соединены также

соответственно с вторым и третьим входами второго элемента ИЛИ 40, выход которого подключен к управляющему выходу блока, прямые и инверсные выходы всех триггеров(первого Т 31, второго Т 32,третьего Т 35 и четвертого Т 38) составляют группу контрольных выходов блока, при этом сигналы инверсных выходов триггеров 35, Т 38 образуют сигналы oi, Ой, прямых выходов триггеров Т 35,38 - сигналы «i, , сигналы прямого и инверсного выходов триггера Т 32 образуют сигналы оь, с, сигналы прямого и инверсного выходов триггера Т 31 образуют сигналы оз, CQ, первые

5 входы всех элементов И (первого И 34,

второго И 36, третьего И 37, четвертого И

39), первый вход второго элемента ИЛИ 40,

нулевые входы первого Т 31, третьего Т 35 и

четвертого Т 38 триггеров подсоединены к

0 группе входов синхронизации блока.

Группа контрольных выходов блока 15 связана струппой инфо мационных входов «о, 5), Оз, «3, «1, «2. «i, 02 блока управления 23 (БУ23), группа входов син5 хронизации блока 15 связана с группой выходов синхронизации блока 23 управления: Co,Ci,C2,C3 (PrPi2),C7 (Б07, 2БлСхИ6), . Со,С1,С2,Сз(РгП010),Со,С1,С2,Сз(Рг05),С1,С2 (1ПЗУ2),С1,С2 (2ПЗУЗ), Со,С2,С4 (Сч1),Со,й

0 (Сч21),С5(БК15),Со, Ci,C2(BK15).

Тактовый вход блока 15 подсоединен к выходу переполнения (j jmax) второго счетчика 21 (Сч21), а управляющий выход блока (выход второго элемента ИЛИ 40 С5(40) связан с входом первого блока элементов И (1БлСхИ11).

Блок 23 управления (БУ23) (фиг.6) включает шифратор 41 (Ш 41), к выходу которо- го подключен информационный вход

0 регистра 42 (Рг42), выходы регистра 42 связаны с группой входов узла элементов И 43 (БлСхИ43), выход которого соединен с входом обнуления счетчика 44 (Сч44), выход счетчика 44 соединен с информационным

5 входом дешифратора 45 (ДШ45), с выходом дешифратора 45 связана вторая группа входов узла проверки контрольного хода 46 (К Сх46) первая группа входов которого связана с группой

0 информационных входов, помеченных символами Оо, , оз, ей, «1, az, «1, Q2 блока 23 управления, подключенных к группе контрольных выходов блока 15 контроля результата.

ВЫ.ХОДЫ узла проверки контрольного кода 46 соединены с группой информационных входов коммутатора 47 (КМр47), выходы которого образуют группу выходов синхронизации блока 23 управления и связаны с вторым управляющим входом узла 48 контроля правильности переходов (БКП48), соединенным с одним входом элемента ИЛИ 106, и с входим управления выдачей результата узла 48 контроля правильности переходов, соединенным с одним входом элемента И 105, индикационные выходы 25,26 и информационный выход 27 узла 48 контроля правильности переходов являются соответствующими выходами блока 23 управления, первая и вторая группы информационных входов узла 48 контроля правильности переходов, соединенных с одним и другими входами схем 93-95 эквивалентности, связаны с выходами счетчика 44 и регистра 42,

Одна группа выходов узла 46 проверки контрольного кода, помеченная символом FI, соединена с входом шифратора 41, другая группа выходов узла 46 проверки контрольного кода, помеченная символом F2, соединена с четвертой группой информационных входов узла 48 контроля правильности переходов, связанных с входами элемента ИЛИ 108, выходы соответствующих разрядов дешифратора 45, помеченных символами тэо, таю, TaiSt соединены с третьей группой информационных входов узла 48 контроля правильности переходов, связанных с входами элемента ИЛИ 107, выход узла 46 проверки контрольного кода, помеченный символом Сч, соединен с вторым входом первого элемента ИЛИ 49, выход которого связан с нулевым входом первого триггера Т 50, инверсный и прямой выходы которого подключены к первым входам первого элемента И 51 и второго элемента И 52, а единичный вход соединен с выходом узла 46 проверки контрольного кода, помеченный символом РП, выходы элементов И 51, И 52 соединены соответственно со счетным входом счетчика 44 и входом узла элементов И 43, подачу тактовых импульсов для работы блока 2 управления осуществляет генератор 53 импульсов (ГИ53),. три выхода которого соединены с вторыми входами третьего элемента И 54, четвертого элемента И 55 и пятого элемента И 56, выход третьего элемента И 54, помеченный символом Г2, соединен с вторыми входами первого и второго элементов И 51,И 52 и с третьим входом синхронизации узла 48 контроля правильности переходов, связанным с нулевым входом триггера Т102, выход четвертого элемента И 55, помеченныйсимволом п, соединен с вторым входом синхронизации узла 48 контроля правильности переходов, связанным с одним входом элемента И 103,-выход пятого элемента И 56, помеченный символом Г, соединен с первым входом синхронизации узла 48 контроля правильности переходов, связанным, с одними входами элементов И 97, И 98, И-НЕ 109 и с управляющим входом дешифратора 45, первый вход второго элемента ИЛИ 57 соединен с инверсным выходом третьего триггера Т 63, нулевой вход которого соединен с входом 24 запуска, второй вход второго элемента ИЛИ 57 соединен с выходом ошибки узла 48 контроля правильности переходов, помеченным символом Сош и связанным с выходом элемента И 103, третий вход второго элемента ИЛИ 57 связан с выходом разряда дешифратора 45, помеченным символом гЭб. одновременно инверсный выход третьего триггера Т 63 соединен с первым входом первого элемента ИЛИ 49, с управляющим входом шифратора 41, помеченным символом Со(42), с входом узла элементов И 43, помеченных символом Со(44), с первым управляющим входом коммутатора 47, помеченным символом АО, с первым управляющим входом узла 48 контроля правильности переходов, связан-. ным с входом элемента ИЛИ 106, с одним выходом синхронизации группы выходов синхронизации блока 23 управления, помеченным символом Со и входом элемента НЕ

58первого элемента задержки, входящего в два последовательно соединенных элемента задержки, включающих элементы НЕ 58, НЕ 59, НЕ60,4НЕ 61, выход элемента НЕ

59первого элемента задержки соединен с вторым управляющим входом коммутатора 47, помеченным символом Aig, выход элемента НЕ 61 второго элемента задержки связан с единичным входом третьего триггера Т 63, прямой выход которого подключен к единичному входу второго триггера Т 62, к нулевому входу которого подсоединен выход второго элемента ИЛИ 57, прямой выход второго триггера Т 62 подсоединен к первым входам третьего элемента И 54, четвертого элемента И 55 и пятого элемента И 56.

Выходы узла 46 проверки контроль ного

кода Ai,A2Ais.Aao, выход Ао.от входа 24,

запуска, инверсного выхода третьего триггера Т 63, выход А 19 от выхода элемента НЕ 59 первого элемента задержки соединен с входами коммутатора 47 (фиг.6).

Коммутатор 47 (фиг.7) производит распределение микроопераций по элементам и блокам устройства поиска, выполняющих заданный оператор управления Ao.Ai, А2,Аз,...,А19,А20 (см.табл.З) и сострит из 32

элементов ИЛИ 47.1, ИЛИ 47. ИЛИ

47.32.

С выходом АО соединены входы элементов ИЛИ 47.1-47.8, при этом выход ИЛИ 47.1 образует сигйал Со(1), выход ИЛИ 47.2 - сигнал Со(15), выход ИЛИ 47.3 сигнал Со(5), выход ИЛИ 47.4 - сигнал Со(10), выход 47.5 - сигнал Со(12), выход ИЛИ 47.6 - сигнал Со(35), выход 47.7 - сигнал ео(38), выход 47.8 - сигнал Со(104).

С выходом AI соединены входы элементов ИЛИ 47.11. ИЛИ 47.17, ИЛИ 47.18, ИЛИ 47.30, выход ИЛИ 47.11 образует сигнал Ci(12), выход ИЛИ 47.17 - сигнал С2(5), выход элемента ИЛИ 47,18 - сигнал С2(10), выход ИЛИ 47.30 - сигнал С5(40).

С выходом А2 соединены входы элементов ИЛИ 47.9, ИЛИ 47.14, ИЛИ 47.29, выход ИЛИ 47.9 образует сигнал Ci(5), выход ИЛИ 47.14 - сигнал Ci(34). выход ИЛИ 47.29 сигнал Сз(12).

С выходом АЗ соединен вход элемента ИЛИ 47.5, выход ИЛИ 47.5 образует сигнал Со{12).

С выходом А4-соединены входы элементов ИЛИ 47.11. ИЛИ 47.17, ИЛИ 47.18, ИЛИ 47.27, ИЛИ 47.32, выход ИЛИ 47.11 образует сигнал Ci(12), выход ИЛИ 47.17 сигнал G2(5), выход ИЛИ 47.18 - сигнал С2(10), выход ИЛ И 47.27 -сигнал Сз(5), выход ИЛИ 47.32 - сигнал СтСб), ).

С выходом AS соединены входы элементов ИЛИ 47.10, ИЛИ 47.15, ИЛИ 47.29. выход ИЛИ 47.10 образует сигнал Ci(10), выход ИЛИ 47.15 - сигнал Ci(37). выход ИЛИ 47.29 сигнал Сз(12).

С выходом Аб соединены входы элементов ИЛИ 47.3, ИЛИ 47.5, ИЛИ 47.6, ИЛИ 47.7, ИЛИ 47.12, ИЛИ 47.13, ИЛИ 47.16, выход или 47.3 образует сигнал Со(5), ИЛИ 47.5 - сигнал Go(12), ИЛИ 47.6 - сигнал Со(35), ИЛИ 47.7 - сигнал Со(38), ИЛИ 47.12 сигнал Ci(2), ИЛИ 47.13 - сигнал Ci(3), ИЛ И 47.16-сигнал С2(1).

С выходом Ау соединены входы элементов ИЛИ 47.9, ИЛИ 47.18, ИЛИ 47;20, выход или 47.9 образует сигнал Gi(5), выход ИЛИ 47.18 - сигнал С2(10). выход ИЛ И 47.20-сигнал С2(2).

С выходом AS соединены входы элементов ИЛИ 47.3, ИЛИ 47.14, ИЛИ 47.29: выход ИЛИ 47.3 образует сигнал Go), выход ИЛИ 47.14 - сигнал Ci(34), выход 47.29 - сигнал G3(12).

G выходом Ад соединены входы элементов ИЛИ 47.9, ИЛИ 47.29, выход ИЛИ 47.9 образует сигнал Gi(5),выход ИЛИ 47.29 сигнал G3(12).

G выходом АЮ соединены входы элементов ИЛИ 47.5, ИЛИ 47.9, ИЛИ 47.21, выход или 47.5 образует сигнал Go(12), выход ИЛИ 47.9 - сигнал Gi(5), выход 47.21 сигнал G2(3).

G выходом All соединены входы элементов ИЛИ 47.8. ИЛИ 47.11. ИЛИ 47.18,

ИЛИ 47.27, ИЛИ 47.32, выход ИЛИ 47.8 образует сигнал Go(104), ИЛИ 47.11 - сигнал Gi(12). ИЛИ 47.27 - сигнал G3(5), ИЛИ 47.32 сигнал G7(6), GY(30), ИЛИ 47.18 - сигнал G2(10).

0 G выходом Ai2 соединены входы элементов ИЛИ 47.16, ИЛИ 47.19, ИЛИ 47.22. ИЛИ 47.23, ИЛИ 47.24, выход ИЛИ 47.16 образует сигнал G2(1), ИЛИ 47.19 -сигнал G2(12), ИЛИ-47.22 - сигнал G2(36), ИЛИ 47.23 - сиг5 нал G2(39), ИЛИ 47.24- сигнал G2(105).

G выходом Ai3 соединены входы элементов ИЛИ 47.4, ИЛИ 47.12, ИЛИ 47.13, ИЛИ 47.16, выход ИЛИ 47.4 образует сигнал Go(10), выход ИЛИ 47.12 - сигнал Gi(2), выход 47.13 - сигнал Gi(3), выход ИЛ И 47.16 сигна л G2(1).

G выходом Ai4 соединены входы элементов ИЛИ 47.10, ИЛИ 47.21, выход ИЛИ 47.10 образует сигнал Gi(10), выход ИЛИ

5 47.21-сигнал G2(3).

G выходом Ai5 соединены входы элементов ИЛИ 47.11, ИЛИ 47.17. ИЛИ 47.18, ИЛИ 47.30, ИЛИ 47.32, выход ИЛИ 47.11 образует сигнал Gi(12), выход ИЛИ 47.17 0 сигнал G2(5), выход ИЛИ 47.18 - сигнал G2(10), выход ИЛИ 47.30 - сигнал G5(40), выход ИЛИ 47.32 - сигнал G7(6), G7(30).

G выходом Ai6 соединены входы элементов ИЛИ 47.11, ИЛИ 47.27, ИЛИ 47.28,

5 ИЛИ 47.30, ИЛИ 47.32, выход ИЛИ 47.11 образует сигнал Gi(12); выход ИЛИ 47.127 сигнал G3{5), ИЛИ 47.28-сигнал G3(10). ИЛИ 47.30 - сигнал G5(40), ИЛИ 47.32 - сигнал G7{6), G7(30).

0 G выходом Ai7 соединены входы элементов ИЛИ 47.5, ИЛИ 47.6, ИЛИ 47.7, ИЛИ 47.8, выход ИЛИ 47.5 образует сигнал Go(12), ВЫХОД 47.6 - сигнал Go(35). выход ИЛИ 47.7 - сигнал Go(38), выход ИЛИ 47.8 5 сигнал Go(104).

G выходом Ai8 соединены входы элементов ИЛИ 47.25. ИЛИ 47.26, выход ИЛИ

47.25образует сигнал G41), выход ИЛИ

47.26- сигнал G4(15).

0 G выходом Aig соединены входы элементов ИЛИ 47.9, ИЛИ 47.31, выход ИЛИ 47.9 образует сигнал Gi(5), выход И Л И 47.31 - сигнал G6(4).

G выходом А20 соединены входы элементов ИЛИ 47.15, ИЛИ 47.29. выход ИЛИ 47.15 образует сигнал Gi(37). выход ИЛИ 47.29-сигнал рз(12).

Узел проверки контрольного кода 46 (фиг.8) реализует булевы функции табл. 1 блока управления БУ23 и состоит из двух

элементов И 64, И 65, первые входы которых соединены с выходом дешифратора 45, помеченным символом гав, второй вход И 64 соединен с выходом «2, а второй вход И 65 с выходом иг, выход И 64 образует сигнал Аб и соединен одновременно с первым входом элемента ИЛИ 66, второй вход которого соединен с rais, а выход образует сигнал 17(Аб) и соединен с входом последовательности элементов ИЛИ 67, НЕ 68, пр1И этом выход ИЛИ 67 формирует сигнал РП, а выход НЕ 68 сигнал Сц, выход Tai3 соединен с первыми входами элементов И.69, И 70, И 71, И 72, причем выход элемента И 72 соединен с первым входом элемента ИЛИ 73, к трем другим входам которого подсоединены выходы И 65, Tai4i И 70; вторые входы И 69, И 71 соединены с Ой, а третьи с %, четвертый вход И 69 соединен с аз, а И 71 саз, таю соединен с первым входом И 74; оъ с вторым входом И 74,а (% с вторым входом И 77, первые входы элементов И 76, И 77, И 79соединены с таю, вторые входы И 76 и И 79 соединены с Оо, а третьи входы И 76, И 77 с at, a«i с третьими входами И 74, И 79, с четвертым входом И 74 соединен оз, а од с четвертым входом И 79, выходы И 76, И 77 образуют сигналы A9i Ai5, а через схему ИЛИ-НЕ 78 образуют сигнал fii, и выход ИЛИ-НЕ 78 подсоединен к четвертому входу ИЛИ 67, второй и третий вход И 70 соединены с входами (% и (%, а второй вход И 72 с «о. выходы И 65, И 70. И 72 и гам объединяются через элемент ИЛИ 73, выход которого соединяется с вторым входом ИЛИ 67, одновременно выход ИЛИ 73 образует сигнал f6(Al2).

Выход И 71 образует сигнал Аг и совместно с выходом И 74 через элемент ИЛИ 75 образует сигнал fi4(Ai7), который подсоединен одновременно к третьему входу ИЛИ 67, выходы И 69, И 79 через элемент ИЛИ 80 образует сигналы fi5(A18), и выход ИЛИ 80 подсоединен к пятому входу ИЛИ 67, к шестому входу которой подсоединен fo таб. Кроме того, узел 46 проверки контрольного кода содержит элементы И 81, И 82,,.., И 90, при этом первые входы И 81, И 83, И 85. И 87, И 90 соединены с Со, а ггервые входы И 82, И 84, И 86, И 8В, И 92 с с, вторые входы И 81, И 82 соединены с rag, вторые входы И 83, И 84 соединены с ran, второй вход И 85 с га 12, вторые входы И 86, И 87 с Га7, вторые входы И 88, И 90 с гае, при этом выходы И 81-И 86 образуют соответственно сигналы Аз, Ai4, АЮ. Ai6, All, Ai3, а выходы И 87, И 88 объединяются элементом ИЛИ 89 и обрауют сигнал AT, выход И 90 и гао объединяются элементомИЛИ 91 и образуют сигнал I, второй вход И 92 соединен с rai2, а выход И 92 образует сигнал Аао.

Блок 23 управления содержит узел 48

контроля правильности переходов (фиг.6) из одного состояния в другое. На основании алгоритма работы блока управления БУ23 фиг.4) получен граф переходов (фиг.5). АнаИЗ фиг.5 показывает, что переходы из одного состояния в другое, отличные от счетного режима, осуществляются в состоянии 0,6,7,14,15 (табл.2).

Как видно из табл.2, кроме переходов 6-

О, , , у всех других переходов обязательно в двух состояниях ai(t) и ai+i(t+1) должны быть тождественны по крайней мере три бита из четырех в регистре памяти 42 и счетчике 44 блока управления 23.

На этом свойстве и построен узел 48 контроля правильности переходов (фиг.6), который содержит схемы 93-96 эквивалентнЪсти, входы которых соединены с прямыми выходами дриггеров регистра 42 и

счетчика 44 и образуют первую и вторую группы информационных входов узла, выходы схем 93-96 эквивалентности различными комбинациями три из четырех выходов связаны с вторыми входами первого элемента И 97, второго элемента И 98 и третьего элемента И 99, выходы схем 93,94,96 эквивалентности соединены с вторым входом элемента И 97, выходы схем 93,95,96 эквивалентности соединены

с вторым входом элемента И 98, выходы схем 94,95,96 эквивалентности соединены с вторым входом элемента И 99, выходы первого-третьего элементов И 97-И 99 подключены к входам элемента ИЛИ-ИЕ

100, выход которого соединёй с вторым входом четвертого элемента И 101, выход которого связан с единичным входом первого триггера Т102, нулевой вход которого подключен к третьему входу синхронизации узла, а прямой выход к первому входу пятого элемента И 103, второй вход которого соединен с вторым входом синхронизации узла, а выход с выходом ошибки-узла и с единичным входом второго триггера

Т 104, инверсный выход которого связан с первым входом шестого элемента И 105, второй вход которого подключен ко входу управления выдачей результата узла, а нулевой вход связан с выходом первого элемента ИЛИ 106, два входа которого служат первым и вторым управляющими входами узла, прямой выход второго триггера Т 104 и выход шестого элемента И 105 являются двумя индикационными выходами 25,26 и

информационным выходом 27 узла, группа входов второго элемента ИЛИ 107 и третьего элемента ИЛИ 108 соединены с третьей и четвертой группами информационных входов узла, выходы второго элемента ИЛИ 107 и третьего элемента ИЛИ 108 соединены с первым и вторым входами элемента И-НЕ 109, третий вход которого и первые входы первого элемента И 97, второго элемента И 98 и третьего элемента И 98 соединены с первым входом синхронизации узла, выход элемента И-НЕ 109 соединен с первым входом четвертого элемента И 101.

Шифратор 41 блока 23 управления {фиг,9) включает в себя шесть элементов ИЛИ 110.1,110.2,...110.6 с числом входов равным двум (ИЛИ 110.1,110.2,110.6), равным трем (ИЛИ 110.5) и четырем (ИЛИ 110.3,110.4), соединенных по матричной схеме с выходами узла 46 проверки контрольного кода, помеченным символами

fo,fRf7,f14f15.

На фиг.9 показана структура регистра 42, состоящая из триггеров Т 42.1, Т 42.2, Т 42.3, Т 42.4 и цепи установки регистра Рг42 блока 23 управления в нулевое состояние через элемент ИЛИ 112, один вход которого соединяется с выходом 46 проверки контрольного кода, на другой подается сигнал Со(42), и элементы ИЛИ 110.1,..., ИЛИ 110.6 шифратора 41 сигналом Со(42). .Там же показана структура узла элементов И 43, синхронизируемая выходом Г2 элемента И 54 блока 23 управления, и цепи установки в нулевое (исходное) состояние триггеров счетчика 44 блока 23 управления

через элементы ИЛИ 111.1 ИЛИ 111.4

узла элементов И 43 сигналом Сс(44).

Счетчик 44 представляет собой четырехразрядный двоичный счетчик; на счетный вход которого поступают сигналы та элемента И 51 блока 23 управления, а на единичные входы триггеров Т 44.1,..., Т 44.4 сигналы с выходов узла элементов И 43. Выходы счетчика 44 соединены с входами дешифратора 45 (фиг.6).

На фиг.9 показаны связи счётчика 44 с узлом элементов И 43. Счетчик 44 может быть реализован на интегральной микросхеме типа К155ИЕ7 или типа КМ155ИЁ7.

Генератор 53 импульсов состоит (фиг.10) из генератора 113 тактов (ГТ), счетчика 114 и дешифратора 115, первые выходы которого обеспечивают выдачу периодически повторяющихся разнесенных во времени импульсов ir, TI, Г2. Эта схема наиболее проста и требует типового двухразрядного счетчика 114 и дешифратора 115 на два входа и четыре выхода.

Однако недостатком такой реализации ГИ53 (хотя и приемлемой) является пропуск такта, в также одинаковая длительность тактов г, п, Т2, хотя каждый из них обеспечивает тактирование разных по логической глубине схем. Так. сигналом пг и П тактируются элементы И 51, И 52, осуществляющие прибавление 1 в запись параллельного кода в счетчик 44, также и установку в исходное состояние Т 102 и синхронизацию И 103 узла 48 контроля правильности переходов (фиг.6), тогда как сигнал т осуществляет тактирование узла 46 проверки контрольного кода и узла 48

5 контроля правильности переходов по цепям ИЛИ 107, И-НЕ 109, И 97, И 98, И 99, ИЛИНЕ 100 с записью результата на Т 102. Суммарная логическая глубина узлов КСх46 и БКП 48 для сигнала г равна десяти, а для сигналов TI и Т2 двум, т.е. с точки зрения быстродействия допустимо в качестве схемы ГИ53 использовать такой вариант реализации ГИ 53, в которой генерируется первый импульс т длительностью lOt, а два других (п, Та) длительностью 2t, где t - условная единица времени, равная задержке одного элементарного логического элемента типа И, ИЛИ, НЕ (фиг. 12). Так.ой вариант реализа,ции ГИ53 приведен на фиг.11. Из периодического сигнала х ГТ 113 за счет задержки на 4t элементами НЕ 116-119 и на It элементом НЕ 120 элементом И 121 формируется сигнал TI, равный длительности Зг{так как TI xj, z x+3t), a сигнал- T2 формируется элементами HE 122,..., HE 125 за счет задержки TI на 4t. И тот и другой вариант реализации ГИ53 реализуется интегральными схемами. В частности, логическая схема фиг.И может реализоваться на 2 корпусах

0 типовой логики К155, так как в одном корпусе размещается до 8 схем НЕ. N На фиг.13,14 представлены блоки 1 6130.

За исключением блоков индикации и

5 постоянных запоминающих устройств 2,3 все устройство поиска неисправных блоков и элементов может быть выполнено как на элементах типовой логики, так и в виде заказнрй или полузаказной большой интегральной схемы.

Функционирование устройства поиска 1;1еисправных блоков и элементов осуществляется в последовательности, определяемой алгоритмом фиг.4, после подачи

5 сигнала Пуск i24 (желательно, чтобы контакт Пуск 24 был бездребезговый, схемы таких контактов известны). Однако и при наличии дребезга все устройство в целом будет работать правильно, с той лишь разницей, что первые К импульсов при дребезге вызовут работу устройства, которая прекратится следующим импульсом U работа начнется заново, т.е. фактически из К импульсов только последний окончательно запустит устройство в работу). Устанавливается в исходное состояние БУ23 (фиг.6)(Т 50, Т 62. Т 104, Сч 44, Рг 42, Т 31) и само устройство поиска (фиг.2) оператором АО (табл.3) за счет установки исходного (нулевого) состояния Сч 1, Сч 21, регистров 5,10,12, триггеров 35,38 в блоке 15 контроля результата (фиг.З) и триггера Т 104 в узле 48 контроля правильности переходов: Через задержку 2t сигналом оператора Al9 БУ23 (фиг.6,2, табл.3) осуществляется запись 1 (сигнал Се(4), С1(5)) на Рг05, код которого после А19 становится равным 011...1. Согласно алгоритму работы предлагаемого устройства поиска неисправныхблоков и элементов, если код параметров в РгПО 10 равен 000...О, а коды столбцов и строк таблицы неисправностей одинаковы и равны 011...1, то результатом работы всего устройства поиска должен быть код111...1 на регистре результата РгР12 и БИ13. Эта тестовая проверка и проводится в результате выполнения операторов А1-AS (фиг.4), при этом сначала считывается код(А1) регистров 5,10 через блок оценки Б07 и через элементы И 11 (фиг.2), производится запись промежуточного результата в РгР12, при этом для прохождения элементов И 11 подается импульс Со(40) от элемента ИЛИ 40 БК15 (фиг.2,3). Далее (А считывается обратный код РгР12 и производится перепись его на Рг05 и проверка БК15 (сигнал Cl(34)): имеется ли на РгР12 хотя бы одна единица. Результат хранится на Т 35 в виде единичного (была единица) или нулевого состояния. Оператор A3устанавливаеУ в нулевое состояние РгР12, подготавливая его к приему следующего кода. Оператором А4 производится считывание прямого кода РгРЮ, Рг05 и обратного кода Рг05 через .элементы И 6 (сигнал С7(6)), при отключении ИЛИ-НЕ30.1-И30.2 Б07 (сигнал )) с записью результата на РгР12 (сигнал C1(12)), при этом прохождение элементов И 11 обеспечивает сигнал единичного плеча Т 35 (фиг.З), если на предыдущем шаге работы БУ23 в промежуточном результате имелась хотя бы одна единица (Э1).

. Оператор А5 осуществляет запись считывания oбpaтнo o кода РгР12 (сигнал С3(12)) и прием на Т 38 результата свертки fToro кода элементом ИЛИ 33 БК15. На Т 38 |удет зафиксирована 1 тогда, когда код РгР12 состоит из одних 1, т.е. 111...1.

Одновременно (параллельно) сигналом С1(10) оператора Аб осуществляется прием кода параметров объекта на РгПОЮ. Затем производится проверка состояния Т38: действительно ли он не перешел в состояние 1 («1 - 1„ если ). Если это произошло ((% 0), то устройство поиска само является неисправным, выполняется оператор А12 фиг,4, Табл.2) и работа прекращается. Оператор А12 считывает во внешнюю микрог роцессррную систему содержимое счетчика 1, регистра 12 результата, триггеров 6К15 Т 36 и Т 39, триггера фиксации ошибки Т104 и подготавливает автоматическое отключение генератора импульсов ГИ53 сигналом Снач.

Если же тестовая проверка .дала вильный результат , то осуществляет-ся переход к оператору Аб. Заметим, что при тестовой проверке, за исключением 1ПЗУ2 и 2ПЗУЗ, осуществляется проверка работы всех блоков и всех связей предлагаемого устройства поиска.

Оператор Аб устанавливает исходное состояние Рг05, РгР12 и БК15 (35,38) и про-. изводит запись содержимого Сч1 на адресные регистры ПЗУ2,3 (который входит в состав ПЗУ2,3 и на схемах фиг.2,3 не показан). Затем производится проверка логического условия Оо ((XG 1), если производится работа предлагаемого устройства в основном режиме - поиск неисправных блоков и элементов). Если % 1, то производится считывание содержимого 1ПЗУ2 и РгПОЮ и запись на Рг05 (оператор т), заТем по-; вторяется операция А-1 (табл.2) - получение промежуточного результата на РгР12 и БК15 (Т 35), после которого оператор-Ав формирует проверку промежуточного результата (аналогично оператору А2 в части сигналов Сз(12), Ci(34)) на БК15 (Т 53) и сигналом Со(5) устанавливает в исходное состояние Рг05, подготавливая его тем самым к приему кода из РгР12. Логический оператор «i проверяет, имеется ли хотя бы одна 1 (хотя, бы одна неисправность), если имеется, то осуществляется переход (операторы А9-А13) к вычислению номеров неисправных блоков. При этом оператором А9производится перепись обратного кода РгР12 на Рг05, оператором АЮсодержимое 2ПЗУЗ (прямой код) также записывается на Рг05, при этом за счет последовательной записи содержимого РгР12 и ПЗУЗ на один и тот же регистр Рг05 побиТно осуществляется операция ИЛ И, так как Рг05 предварительно устанавливается в О, Оператором А11, полностью аналогичном оператору А4 кроме добавленного сигнала Co(1Q4) - отсутствие ошибки в работе предлагеГемого устройства, осуществляется вычисление окончательного результата и выдача (Al результата во внешнюю цепь с остановкой работы БУ23 за счет отключения генератора 53 импульсов (фиг.4,6). Если же после оператора As проверкой d будет установлено, что on 0, то осуществляется проверка OQ - не последняя ли это была строка (столбец) таблицы неисправностей (i Jmax). ЕСЛИ 05 1, ТО все проверки закончились, оператором Ai7 производится установка нулевого состояния триггера фиксации осиибки Т 104, регистра результата РгР12, БК15 и осуществляется переход к оператору Ai2.

Если 03 О, то к содержимому См 1 и Сч21 приб1авляется 1(А18)и программа повторяется с оператора А6

То, что в основном режиме действительно будет найден номер неисправного блока или элемента в коде параметров объекта, убедимся на примере: пусть для тестируемого устройства таблица функций неисправностей дана в виде табл.4.

Образуем код параметров рбъекта в виде логического умножения столбца 4 и 12, что,очевидно соответствует одновременно двум неисправностям и убедимся, что предлагаемое устройство выделит неисправные блоки в соответствии с описанным .алгоритмом функционирования структурной схемы.

Тогда код параметров объекта примет вид:

х°1 х х х°4х%хОбх°7х%х°9х°Юх°11 х°12х°13 1 11000001 11 00

Пусть код параметров объекта записан уже в РгПО 10, 1ПЗУ2, 2ПЗУЗ содержит ТФН объекта, а на Сч21 установлено jmsxмаксимальное число столбцов (строк) ТФН оператором через вход, а тестовая проверка дает результат Й2 1. Тогда происходит переход к оператору Аб(фиг,4), который устанавливает в исходное состояние триггеры 35, 38 БК15, регистров Рг05, РгР12 и производит запись первого адреса столбца и строки таблицы функций неисправностей (ТФН) в адресные регистры 1ПЗУ2, 2ПЗУЗ из содержимого Сч1. Пусть выполняется логическое условие оь 1,соответствующее работе устройства в режиме поиска неисправных блоков. Тогда выполняется оператор А, считывающий кбд параметров объекта из РгПОЮ и код первого столбца ТФН из 1ПЗУ2 и записывающий его на Рг05, затем выполняется оператор AI считывание кода первого столбца из РгО5,

кода параметров объекта W3 и их запись в РгР12,

В результате выполнения оператора А1 получается промежуточный результат на

РгР12. Оператор АО устанавливает в исходное состояние Рг05, считывает обратный коде РгР12, производит его запись на БК15 (Т 35), формирует логический оператор «i, проверяющий наличие хотя бы одной еди- .

ницы в обратном коде. В рассматриваемом случае ai О (табл.5). Тогда БК15 (Т 31) осуществляет проверку условия OQ - не последняя ли это была строка (столбец) ТФНГti jmax). в нашем случае оа О, так как

столбец Не последний, тогда к содержимому счетчиков Сч1. Сч21 прибавляется 1(опера тор АШ).

Цикл, включак щий операторы и условия l--Ay- l-.

повторяется до ввода четвертого столбца ТФН, т.е. для первого, второго и третьего столбца ТФН (табл.5-7). После ввода четвертого столбца ТФН оператор А формирует «i 1 , т.е. фиксируется наличие хотя бы

одной неисправности (табл.8). Тогда осуществляется переход (операторы А9-А12) к вычислению номеров неисправных блоков.

Оператор А9 произведет перепись об; ратного кода РгР12 на Рг05, оператор А10

запишет код четвертой строки ТФН на Рг05, при этом побитно осуществляется операция ИЛИ кода четвертой строки ТФН и обратного кода РгР12, записанного на Рг05 оператором А9, производится устЗновка в нулевое состояние РгР 12 (табл.9). Произойдет считывание обратного кода из Рг05

на вторые входы 2БЛСхИ6, на первые входы

которых поступает сигнал синхронизации

СХ6) из БУ23. Выходные сигналы 2БЛСхИ6

поступают на входы синхронизации элементов ИЛИ-НЕ 30.3 507, на первые входы которых считывается код параметров объекта из РгПОЮ. При этом сигналом СХЗО) на вторые-входы элементов ИЛИ-НЕ 30.3 Ьчитываются нулевые сигналы из цепочек элементов ИЛИ-НЕ 30.1-И30.2 БО7. ;

Элементы И 11 1БЛСхИ синхронизируются сигналом CS(40)SK15, полученным при реализации оператора А8, Результаты вычисления номеров неисправных блоков с выходом элементов И 11 1 БЛСхИ записываются на РгР 12 (табл.10).

Оператором А12 производится выдача результата на блок индикации БИ 13, на

контроле появляется визуальная сигнализация о неисправности четвертого и двенадц того блоков.

При Оо О осуществляется работа предлагаемого устройства в режиме расширения

области применения путем одновременного контроля разнородных типовых блоков вычислительйой техники.Режим работы (ао f О или «о -1) устанавливается опера: о . тором по входам 20-1 и 20-2. ,Для рассмотрим режим контроля параметров запоминающих устройств.

Контроль ЗУ производится с применением эталонного ЗУ. Записывается код в проверяемое и эталонное ЗУ и контрольным считыванием определяется Брак-годен.

В предлагаемой конструкции устройства поиска неисправных блоков и элементов на место первого и второго ПЗУ2 и ПЗУЗ следует установить эталонное и проверяемое ПЗУ с заранее записанной информацией на одном и том же программаторе. За счет возможных неисправностей в проверяемом ПЗУ (или оперативном ЗУ), начиная с какого-то адреса, коды эталонного и проверяемого ЗУ окажутся различными в случае неисправности.,

Согласно алгоритму (фиг.4) при «0 0 оператором АТЗустанавливается в исходное состояние РгПОЮ, так как код параметров объекта не потребуется в этом режиме и производится запись кода адреса на Рг адреса первого и второго ЗУ. Оператором А производится считывание на Рг05 кода эталонного ПЗУ, а на регистр РгПОЮ - кода проверяемого ПЗУ (оператор А1.4 для одного и того же адреса. Оператором А15через элементь И 6 производится запись кода Рг05 и кода РгПОЮ на РгР12. Для прохождения элементов И 11 подается сигнал С5(40). Оператором А16производится то же действие, но только для обратных кодов Рг05 и РгПОЮ. Таким рбарзом, на РгР12 образуется функция эквивалентности vj ai bi-b ai bi,,2,...,п}, где ai и Ы - значение i-ro бита Рг05 и РгПОЮ. При выполнении операторов А15/ А16на одни,входы элементов I/ 6 подается синхросигнал С7(6), а на одни- входы элементов ИЛИ-НЕ 30.1 сигнал С7(30), при котором на выходах элементов Й30.2 фиксируются нулевыесигналы.

Следовательно, если коды эталонного и проверяемого ПЗУ совпадают, то на РгР12 будет зафиксирован код из одних 1, т.е. 111...1. Оператором А20(СЗ(12), С 1(37)) осуществляется считывание обратного кода РгР12 и запись результата на Т 38. Т 38 окажется в состоянии 1, если на РгР12 все 1 .За оператором А20после проверки «2 (VI) осуществляется либо фиксация ошибки (А12), либо проверки j jmax.

Заметим, что вместо ЗУ (оперативного или постоянного) на место проверяемого ПЗУ может быть включена комбинационная схема или программируемая логическая

матрица (ПЛМ). При этом в эталонном ЗУ осуществляется предварительная запись правильной комбинации выходных кодов на каждую входную комбинацию, а при установке КСх или ПЛМ к ним не подсоединяется сигнал управления БУ23, так как их функционирование определяется появлением внешних (по отношению к КСх или ПЛ М) сигналов на их входах от Сч1.

Точно так же могут проверяться и счетчики, при этом произойдет перепись содержимого Сч,1 напроверяемый счетчик тем же сигналом (С 1(1)), а в эталонном ЗУ в этом случае должна быть записана последовательность кодов счетчика.

При реализации алгоритма (фиг.4) БУ23 работает в такой последовательности. Перед подачей сигнала (вход 24) по входам 20-114ли 20-2 устанавливается режим работы (а о 1 или «о 0), а также в Сч21 по установочному входу 22 заносится дополнительный код м.аксймального количества Отах) столбцов В таблице неисправностей (для основного режима) или количество проверяемых комбинаций (для дополнительного режима).

После команды Пуск 24 через элемент

ИЛИ 57 производится установка БУ23 в исходное состояние (Т 50, Т б2, РГ4.2, Сч44,

Т 104, Т 31) и через задержку 4t сигналом

единичного плеча Т 62 подключается ГИ53. Первым же импульсом г от элемента И 56 производится опрос КСх46 через ДШ45. Поскольку БУ23 находился до этого в нулевом

состоянии, то согласно фиг.5 (граф переходов БУ23 фиг.5 получен в строгом соответствии с алгоритмом фиг.4) КСх4б выдает сигнал А1 и поставит Т 50 через схему ИЛИ 49 в нулевое состояние. Эта последовательность работы сохранится и для любого i-ro состояния (фиг.5). Одновременно этим же сигналом ТВ Рг42 осуществляется запись нового состояния БУ23 по выходам КСх46, которые помечены символом F1, если (сргласно фиг.5) эта смена состояний не достигается простым счетом. В этом же случае в БКП 48 триггер Т 102 зафиксирует по сигналу г, будет ли переход в новое состояние правильным, а перед сменой этого состоя-:

ния сигналом РП Т 150 будет установлен в единичное состояние. Следующим придет импульс TI, который проверит состояние триггера Т 102 и, если ошибки в переходе нет, то темп работы БУ23 не нарушается.

Если же обнаружена ошибка, то сигналом. Сош работа БУ23 приостанавливается. .

ошибки не было, то изменение в работе БУ23 происходит только по сигналу Т2. При этом по сигналу Г2 происходит изме-

нение состояния Сч44, либо за счет прибавления 1 через И 51, либо за счет занесения параллельного кода Рг42 через ВлСхИ42 по сигналу И 52. После завершения серии импульсов г, п, Г2 на Сч44 оказывается Новое состояние и работа БУ23 повторяется с приходом новой серии импульсов г, ri, Т2 согласно фиг.4,5.

Внешние информационные выходы предлагаемого устройства позволяют вынести результаты контроля во внешние системы для автоматического принятия решений.

Формула изобретения 1.Устройство поиска неисправных блоков и элементов, содержащее два блока памяти таблицы неисправностей, регистр

оценки, блок оценки кода исправности, регистр параметров-объекта, первый блок элементов И, регистр результата, блок управления и блок индикации, вход которого соединён с выходом прямого кода регистра результата, информационный вход которого связан с выходом первого блока элементов И, группы входов которого подключены к группе блока оценки кода исправности, отличающееся тем, что, с целью расширения области применения .устройства путем одновременного контроля разнородных типовых блоков, вычислительной техники, в устройство введены два счетчика, два блока элементов ИЛИ, второй блок элементов И и блок контроля результата, установочные входы, информационные и индикационные выходы которого являются соответствующими входами и выходами устройства, управляющий выход соединен с входом первого блока элементов И, группа контрольных выходов - с rpynnoi информационных входов блока управления, тактовый вход подключен к выходу переполнения второго счетчика, а группа входов результата, первая группа входов первого блока элементов ИЛИ и группа выходов результата проверки устройства соединены с выходом обратного кода регистра результата, управляющий считыванием информации вход которого, управляющие считыванием информации входы регистра параметров объекта, регистра оценки, первого и второго блоков памяти таблицы неисправностей, блока оценки кода исправности, счетные входы счё тчиков, вторая группа входов первого блока, элементов ИЛИ, первая группа входов второго блрка элементов И и .группа входов синхронизации блока контроля результата связаны с группой выходов синхронизации блока управления, информационный выход.

индикационные выходы и вход запуска ко торого являются соответствуюЩими выхо- . дами и входом устройства, адресные входы первого и второго блоков памяти таблицы

неисправностей соединены с выходом пе|эвого счетчика, установочные входы счетчиков служат соответствующими входами устройства, группы выходов блоков памяти таблицы неисправностей связаны с третьей

0 и четвертой груг1пами входов первого блока элементов ИЛИ, выход которого подключен к информационному входу регистра оценки и к первому входу торого блока элементов ИЛИ, бторой вход которого явля-.

5 ется информационным входом устройства, а выход соединен с информационным входом регистра параметров объекта, группа выходов которого связана с пятой группой входов первого блока элементов

0 ИЛИ и с первой группой информационных входов блока оценки кода исправности, вход синхронизации которого Г1одключен к выходу второго блока элементов И, а вторая группа информационных входов и вторая группа входов второго блока элементов И соединены с группой выходов регистра оценки.

2.Устройство по п. 1,0 т л и ч а ю щ е е с я тем, что блок контроля результата содержит два элемента ИЛИ, четыре элемента И и нетыре триггера, нулевой и единичный входы второго триггера соединены соответственно с первым и вторым установочными входами блока, прямые и инверсные выходы всех триггеров составляют группу контрольных выходов блока группа входов синхронизации которого связана с первыми входами всех элементов И, с первым входои второго элемента ИЛИ и с нулевыми

0 входами первого, третьего и четвертого триггеров, единичный вход первого триггера подключен к тактовому входу блока, группа входов результата соединена с входами первого элемента ИЛИ, выход которого связан с вторыми входами первого и третьего элементов И. выходы которых подключены соответственно к единичным входам третьего и четвертого триггеров, прямые выходы которых соответственно соединены с первыми входами второго и чет-, вертого элементов И, с вторым и третьим входами второго элемента ИЛИ и с индикационными выходами блока, выходы второго и четвертого элементов И связаны с

5 информационным выходамиблока, выход второго элемента ИЛИ подключен к управ- ляющему выходу блока.

З.Устройство по П.1, о т л и ч а ю щ е ес я тем, что блок управления содержит шифратор, регистр, узел элементов И, счётчик.

дешифратор, узел проверки контрольного кода, коммутатор, узел контроля правильности переходов, два элемента ИЛW, три триггер1а, пять элементов И, генератор импульсов и два последовательно соединенных .элемента задержки, выход второго элемента задержки связан с единичным входом третьего триггера, нулевой вход которого служит входом запуска блока, прямой выход подключен к единичному входу второго триггера, а инвер1сный выход- к первым входам первого и второго элементов ИЛИ, к входу первого элемента задержки, к одному из выходов группы выходов синхронизации блока, к управляющему входу шифратора, к входу узла элементов И, к п е р в ы м у п ра в л яю щим входам коммутато ра и узла контроля правильности переходо.в, выход первого элемента задержки .соединен с вторым управляющим входом коммутатора, выходы которого образуют группу выходов синхронизации блока и связаны с вторым управляющим входом и с входом управления выдачей результата узла контроля правильности переходов, информационный и индикационные выходы которого я в ля ются с ооТветствУ ю щ ими в Ыхода ми блока, первая и вторая информационных входов подкляэчены к выходам счетчика и регистра, три входа синхрр.низации соединены с выходами пятого, четвертого и третьего элементов И, третья и четвертая группы информационных входов - с первой группой выходов узла проверки контрольного кода и с выходами соответствующих разрядов дешифратора, выход ошибки - с вторым входом второгоэлемента ИЛИ; третий вход KOTpJDOrO связан с выходом QOOTветствую,щего разряда дешифратора, а выход-с нулевым входом второго триггера, прямой выход которого подключен к первым входам трётьего-пятого элементов И, вторые входы которых соединены с выходами -генератора импульсов, выход первого элемента ИЛИ связан с нулевым входом первого триггера, инверсный и прямой выходы которого подключены к первым входам первого и второго элементов И, а единичный вход, второй вход первого эле-мента ИЛИ и вход шифратора соединены с соответствующими выходами узла проверки контрольного кода, группа выходов которого связана с группой информационных входов коммутатора, а первая и вторая группы входов У с группой информационных входов блока и с выходами дешифратора.

информационные и управляющий входы которого соединены соответственно с выходами счетчика и пятого элемента И, счетный вход счетчика соединен с выходом первого.

элемента И, а вход обнуления - с выходом узла элементов И, вход которого связан с выходом второго элемента И, а группа входов; - с выходами регистра, информационный вход которого подключен к выходу

шифратора, вторые входы первого и второго элементов И соединены с выходом третьего элемента И.

4.Усгройство по п.З, отл и ча ю щеес я тем, что у;зел контроля правильности переходов содержит четыре схемы эквивалентности, шесть элементов И, элемент , два Триггера, три элемента ИЛИ и элемент И-НЕ, выход которого соединен с

первЬ1М входом четвертого элемента И, первый и второй входы - с выходами второго и третьего элементов ИЛИ, а третий вход и первые входы первого-третьего элементов И- с первым входом синхронизации

узла, вторые входы первого-третьего эле: ментов Й,связаны соответственно с выходамИ первой, второй и четвертой схем

эквивалентности, первой, третьи и четвертой схем эквивалентности и второй, третьи

и четвертой схем эквивалентности, входы которыхобразуют первую и вторую группы информационных входов узла, выходы первого-третьего элементов И подключены к входам элемента ИЛ И-НЕ, выход которогр соединен с вторым входом четвертогр элемента И, выход которого связан с единичным входом первого триггера, нулевой вход которого подключен к третьему входу синхронизации узла, а прямой выход - к

первому входу пятого элемента И, второй

вход которого соединен с вторым входом

синхронизации узла, а выход - с выходом

ощибки узла и с единичным входом второго

триггера, нулевой вход которого связан с

выходом первого элемента ИЛИ, а инверсный выход - с первым входом шестого элемента И, второй вход которого подключен к входу управления выдачей результата-узла, а выход и прямой выход второго триггера

являются информационным и двумя индикационными выходами узла,-группы входов второго и третьего элементов ИЛИ соединены с третьей и четвертой группами информационных входов узла, два входа первого

элемента ИЛИ служат первым и вторым уп равляющими .входами узла., .fo p A fg Qr f, -00 f ai , 08 f 5 «-ЙС t,) f4 Ь . А,Ч. A,s X. fg . + Uo&a,,, + .,o+5:, - + Aj, 3 Аб ( Ag ,9 , A, ,A о(:;гацА 2 f л -ц 0 Z f-о 3 л-о 7 A 4 ,5 0 (У, to ,0 fn Ai8 «Xg aj+ta g f,&a - i.M C(o ;o2a,5 A fg a , 2o° o

Таблица 2 2 2, ,5+о(в52(Уз 0,0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Графический дисплей с контролем | 1984 |

|

SU1249526A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Тренажер оператора радиоэлектронной аппаратуры | 1988 |

|

SU1524084A1 |

Изобретение относится к вычислительной технике и может быть использовано вТспециализированных вычислительных системах и информационно-измерительных комплексах. Цель изобретения состоит в расширении области применения устройства путем одновременного контроля разнородных типовых блоков вычислительной техники. Устройство содержит два блока памяти 2 и 3 таблицы неисправностей, регистр оценки 5. регистр 10 параметров объекта, блок оценки 1 кода исправности, первый блок элементов 11 И, регистр результата 12, блок индикации 13. В устройство дополнительно введены два счетчика 1 и 21, два блока 4 и 8 элементов ИЛИ. втор'ой блок 6 элементов И и блок 15 контроля результата с соответствующими /связями. 3 з.п.ф-лы, 14ил., Ютабл.(Dut.J-ЧОю00 CJI

Набор микроопераций

N2№

Со(1.21,5.10.12,35,38,104)

С2(5.10) Ci(12)C5(40)

Сз(12) Gi(34) Ci(5)

Со{12) С7(6.30) С2(10) С2(5)Сз(5) CiCl2)

Сз(12) Ci(37) Ci(10) Со(5,12.35.38) С2(1). Ci(2.3)

C2(2)C2(10)Ci(5) ез(12) Ci(34) Со(5)

Сз(12)С1(5) С2(3) Ci(5) Со(12)

СтСб.ЗО) С2С10) Сз(5) Ci(12) Со(104) 02(1,12,36,39,105) CQ(10)C2(1)Gi(2.3)

C2{3)Ci(10)

Таблица 3

Содержание

Установка исходного состояния

Получение промежуточного, результата

Проверка промежуточного результата

Обнуление регистра рез-та

Получение рез-та проверки

Проверка рез-та и прием кода объекта

Запись первого адреса ТФН в 1ПЗУ2 и

ПЗУЗ иуст. исх. сост. Рг05. РгР12. БК15

Считывание 1ПЗУ2

Формирование ai

Перепись РгР12-Рг05

Считывание 2ПЗУЗ и запись Рг05

. Получение результата

Выдача результата Установка исх. сост. РгПОЮ и запись

кода счетчика на РгПЗУ Считывание 2ПЗУЗ и запись РгПОЮ

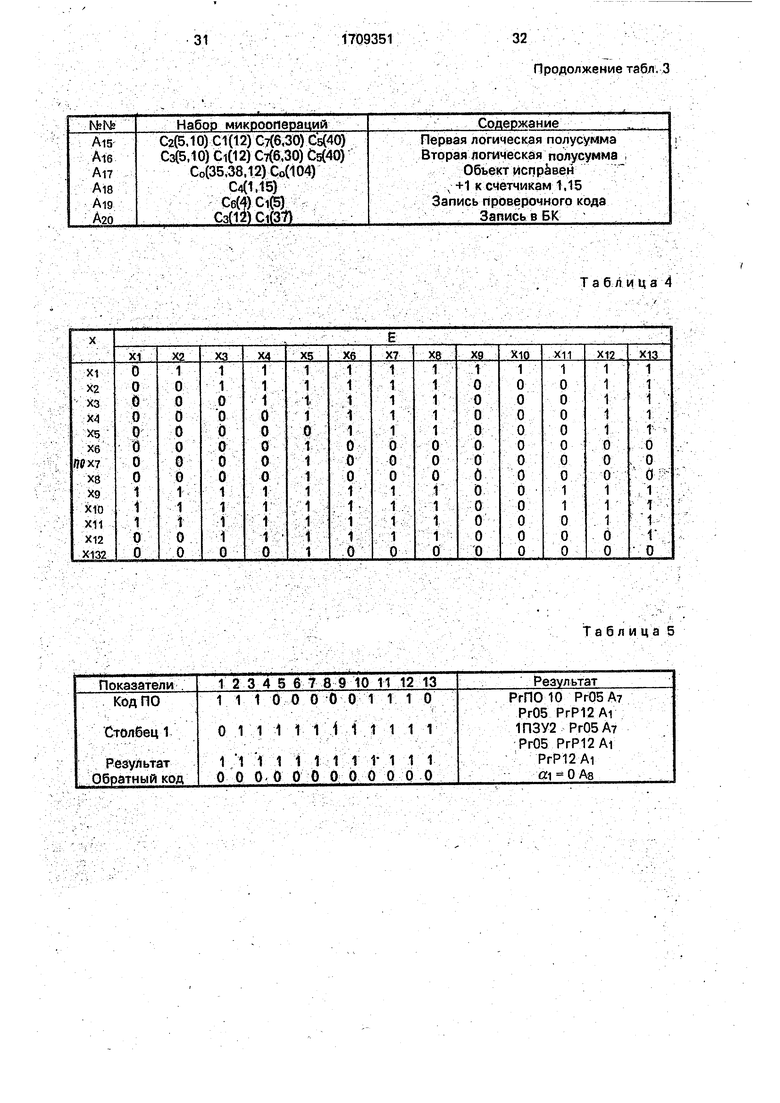

Продолжение табл, 3

Та бЛи ца 4

Таблица 5

Таблица б

Таблица 7

Таблица 8

Т а б лица 9

Табл и ц а 10

Фиг.2

(Конеи

фигЛ

(

ГЛУ) J

ct otfCfj

AIB

фиг.5

65 счетный режип (Cif)

Фиг.В

Фиг. 9

113

т

115

9u.lO

X

ШФШ

-/I

ti .Го

125

M

Фиг. 11

Фцг. 1Z

СоСгОу

Фuг.

| УНИВЕРСАЛЬНОЕ УСТРОЙСТВО ДЛЯ ПОИСКА НЕИСПРАВНЫХ | 0 |

|

SU220636A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для контроля движения | 1921 |

|

SU1968A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-01-30—Публикация

1989-12-25—Подача