Изобретение относится к вычислительной технике и автоматике, предназначено преимущественно для определения скользящего среднего в устройствах обработки цифровой информации, в цифровых измерительных приборах и других устройствах и является усовершенствованием известного устройства, описанного в авт. св. № 1012272.

Цель изобретения - расширение функциональных возможностей устройства за счет вычисления скользящего среднего дискретных двумерных полей при высокой точности и быстродействии,

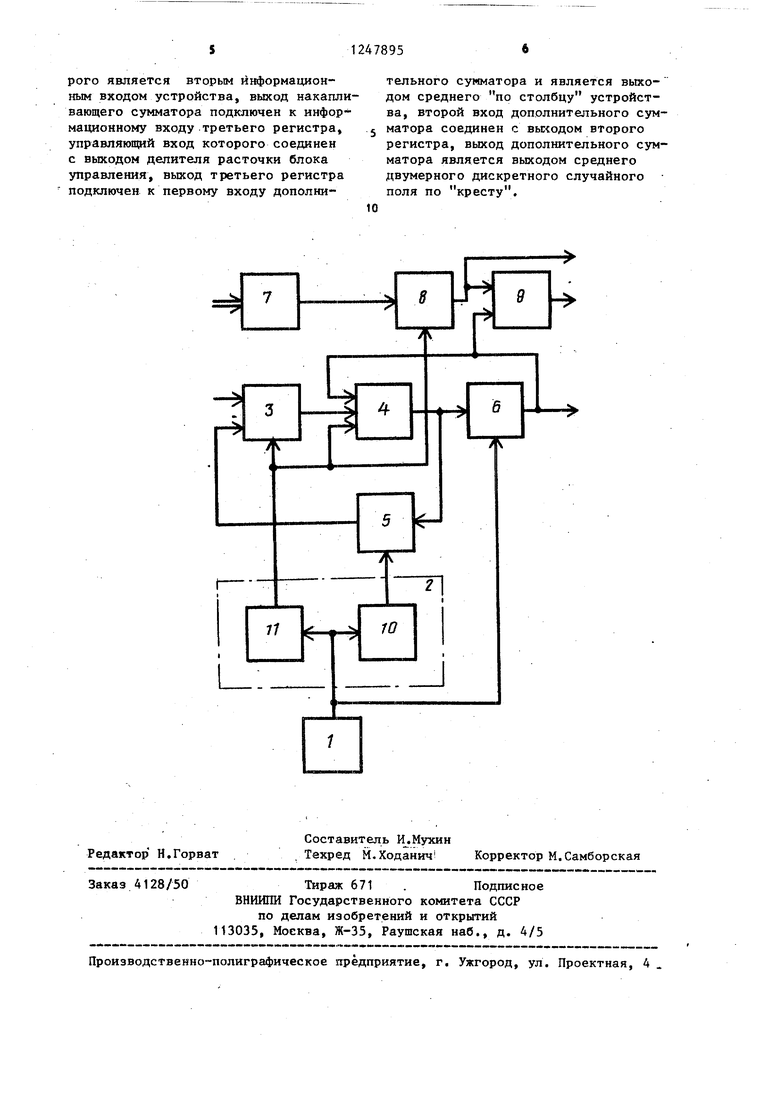

На чертеже представлена функциональная схема предложенного устройства для вычисления скользящего среднего,

Устройство содержит генератор текстовых импульсов ГТИ 1, блок 2 управления, коммутатор 3, сумматор 4, регистр 5, регистр 6, накапливающий сумматор 7, регистр 8, дополни- тельньй сумматор 9, причем блок 2 управления содержит делитель частоты 10 и триггер 11.

Пусть выборка типа крест состоит из пересекающихся строки и столбца. Нумерация отсчетов в кресте в соответствии с прямоугрльной матриN. .

выбрана строка oL к столбец р Тогда элемент пересечения есть а(с(,р), а общее количество отсчетов в выборке равно N + N . причем элемент а(с(,) считается дважды. Обозначим через К и К двоичный логарифм соответст- венно числа N, и N,, а через п-раз рядность отсчетов выборки. Деление на N 2 реализуется за счёт отбрасывания К младших разрядов кода. Для определенности примем, что скольжение креста происходит по строке.

Устройство работает следующим об- ра -ом.

ГТИ 1 вырабатывает тактовые им- . пульсы, поступающие на вход блока 2 управления. По сигналам с первого выхода блока.2 управления коммутатор 3, имеющий разрядность (п + 2К , + 1), подключает ко второму информационному входу первого сумматора 4 поочередно либо входной п-разрядный двоичный код очередного отсчета строки, либо (п + 2К„ + 1)-разрядный инверсцей размерами (N, N,), из которой он выбран. В качестве креста

Выход первого сумматора 4 подключается поразрядно к соответствующим разрядньм входным цепям (п + 2К + + 1)-разрядного второго регистра 6,

5 выход которого подключается поразряд но к первому входу сумматора 4 для обеспечения работы в режиме накапливающего сумматора. Вместе с этим (п + К + 1) старших разрядов суммаto тора 4 подключены к (п + К + 1)

входным цепям регистра 5, соответствующие инверсные выходы которого используются в качестве (п + К + 1) младших разрядов инверсного кода.

15 Таким образом при записи значений кода из сумматора 4 в регистр 5 осуществляется смещение в сторону младших разрядов на К разрядов, т.е. реализуется операция деления на N

20 2 2 и инвертирование полученных

значений младших (п + к + 1) разрядов кода. При этом значения п старших разрядов полной разрядной сетки кода со стороны входа регистра 5 не

25 заполнены., т.е. равны нулю. Поэтому соотв.етствующие им значения К старших разрядов инверсного кода на выходе регистра 5 формируются как постоянные одинаковые сигналы логичес30 кой 1, для передачи которых через 3 при технической реаликоммутаторзации достаточно однопроводной линии связи, с которой на выходе ком35

старших второго входа сумматора 4.

мутатора 3 соединены К

разрядов

Для выполнения- операции вычитания

образуется дополнительный код на

основе сформированного инверсного

кода регистра 5 путем подачи на

. вход переноса сумматора сигнала логической 1 с первого выхода блока 2 управления. Этот сигнал поступает в те «промежутки времени, когда через коммутатор 3 на второй вход

, сумматора 4 передается с регистра 5 инверсный код. К выходу ГТИ 1 подключен управляющий вход регистра 6. Зыход регистра 6 является выходом .устройства, с которого снимается текущее значение обрабатываемой выборки по строке oi. в форме п-разряд- ного параллельного кода. На N (п + + К, + 1)-разрядных входа второго (п + К.( + 1)-разрядного сумматора 7 поступают N отсчетов столбца |5 . (п + 1) старших разрядов кода суммы значений отсчетов столбца выбранного креста с выхода сумматора

5С

ный код с выхода первого регистра 5. 7 по сигналу первого выхода блока 2

Выход первого сумматора 4 подключается поразрядно к соответствующим разрядньм входным цепям (п + 2К + + 1)-разрядного второго регистра 6,

выход которого подключается поразрядно к первому входу сумматора 4 для обеспечения работы в режиме накапливающего сумматора. Вместе с этим (п + К + 1) старших разрядов сумматора 4 подключены к (п + К + 1)

входным цепям регистра 5, соответствующие инверсные выходы которого используются в качестве (п + К + 1) младших разрядов инверсного кода.

Таким образом при записи значений кода из сумматора 4 в регистр 5 осуществляется смещение в сторону младших разрядов на К разрядов, т.е. реализуется операция деления на N

2 2 и инвертирование полученных

значений младших (п + к + 1) разрядов кода. При этом значения п старших разрядов полной разрядной сетки кода со стороны входа регистра 5 не

заполнены., т.е. равны нулю. Поэтому соотв.етствующие им значения К старших разрядов инверсного кода на выходе регистра 5 формируются как постоянные одинаковые сигналы логической 1, для передачи которых через 3 при технической реаликоммутаторзации достаточно однопроводной линии связи, с которой на выходе ком

старших второго входа сумматора 4.

мутатора 3 соединены К

разрядов

Для выполнения- операции вычитания

образуется дополнительный код на

основе сформированного инверсного

кода регистра 5 путем подачи на

вход переноса сумматора сигнала логической 1 с первого выхода блока 2 управления. Этот сигнал поступает в те «промежутки времени, когда через коммутатор 3 на второй вход

, сумматора 4 передается с регистра 5 инверсный код. К выходу ГТИ 1 подключен управляющий вход регистра 6. Зыход регистра 6 является выходом .устройства, с которого снимается текущее значение обрабатываемой выборки по строке oi. в форме п-разряд- ного параллельного кода. На N (п + + К, + 1)-разрядных входа второго (п + К.( + 1)-разрядного сумматора 7 поступают N отсчетов столбца |5 . (п + 1) старших разрядов кода суммы значений отсчетов столбца выбранного креста с выхода сумматора

С

управления записываются в (п + 1)- разрядньв1 третий регистр 8, выход Которого является дополнительным выходом устройства, с которого снимается параллельно код скользящего среднего по столбцу креста. Кроме этого (п + 1)-разрядный, код с выхода регистра 8 поступает на первый вход третьего) (п + 1)-разрядного сумматора 9, на второй вход которого поступают (п + 1) старших разрядов кода со второго регистра 6, Таким образом п старших разрядов кода на выходе сумматора 9 представляют собой значение скользящего среднего по кресту. Алгоритм работы устройства описывается следующим уравнением:

Z(iT) у, (iT) + у, (iT)/2,

где Z(iT) - значение хода скользящего среднего по кресту в момент времени 1Т

у (1Т) - значение кода скользящего среднего по строке oi в момент времени iTJ

у (iT) - значение кода скользящего среднего по столбцу в момент времени iT;

у (iT) yД(i - OTj (i . - 1)ТЗ + x (iT), ,

где у (i - 1)Т - значение кода

скользящего среднего по строке сИ в момент iTi X (iT) - значение входного хода для вычисления скользящего среднего по строке 6L в момент времени iT

y(iT) L x(iT) /N,,

где X (iT) - значения отсчетов столбца в момент времени iT.

Устройство работает по тактам, каждый из которых состоит из двух полутактов, определяемых двумя соседними импульсами (нечетным и четным) ГГИ 1. В первом полутакте значения кодов отсчета столбца р поступают на входы сумматора 7, для суммирования в котором из-за многовходовости отводится практически такт работы устройства, а входной код очередного

2478954

отсчета строки d поступает через коммутатор 3 на второй вход сумматора 4 и суммируется с кодом y(i - 1)т регистра 6. Полученное на выходе сум- матора 4, значение кода суммы у, (i - -1)т + ) записывается в регистр 6 по заднему фронту нечетного импульса ГГИ 1, который воздействует также на триггер 10 и изменяет состояние его JO выхода с логического О на логическую 1, Во втором полутакте под действием сигнала логической 1 с выхода блока 2 управления (триггер 11) в- коммутаторе 3 открывается цепь JJ для прохождения на второй вход суммато- : ра 4 инверсного кода с выхода регистра 5. В результате суммирования прямого кода регистра 6 и дополнительного кода заполненного в предьщущем такте 2Q значения кода регистра 5 в сумматоре . 4 реализуется операция вычитания

{y;(i - 1)Т + х (iT)} - y,(i г 1)т. Полученное на выходе сумматора 4 текущее среднее значение кода записывается в регистр 6 по заднему фронту четного импульса ПИ 1, при этом триггер 11 блока 2 управления возвращается в исходное состояние. Запись кода в регистр 5 с выхода сум30 матора 4 производится в каждом такте по заднему фронту импульса, посту- паюцего со второго выхода блока 2 управления. Этот импульс фор 1ируется в делителе 7 частоты (коэффициент

35 деления равен 2 N) синхронно с соот- ветствующйм четным импульсом ГТИ 1.

25

Первые N тактов регистр 5 сохраняет запись нулевого значения кода. Запись кода в регистр В с выхода

сумматора 7 производится по заднему фронту импульса, поступающего с первого выхода блока 2 управления (с выхода триггера 11). Коды с выходов регистров 6 и 8 поступают на соот-

ветствующие входы сумматора 9, с выхода которого снимается текущее значение кода среднего по кресту.

Ф.ормула изобретения

Устройство для вычисления скользящего среднего по авт. св.№ 1012272, отличающееся тем, что, с целью расширения функциональных возможностей за счет вычисления скользящего среднего дискретных двумерных полей, в него введены третий регистр, дополнительный сумматор и накапливаю1ций сумматор, выход которого является вторым информационным входом устройства, выход накапливающего сумматора подключен к информационному входу третьего регистра управляюпщй вход которого соединен с выходом делителя расточки блока управления, выход третьего регистра подключен к первому входу дополниРедактор Н.Горват

Составитель И.Мухин , Техред М.Ходанич

А128/50

Тираж 671 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/3

Производственно полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

тельного сумматора и является выходом среднего по столбцу устройства, второй вход дополнительного сумматора соединен с вькодом второго регистра, выход дополнительного сумматора является выходом среднего двумерного дискретного случайного поля по кресту.

8

h Г

Корректор М.Самборская

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Цифровое сглаживающее устройство | 1983 |

|

SU1092520A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СКОЛЬЗЯЩЕГО СРЕДНЕГО ЗНАЧЕНИЯ | 1990 |

|

RU2015552C1 |

| Устройство для вычисления скользящего среднего | 1984 |

|

SU1241260A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| Устройство для вычисления скользящего среднего | 1986 |

|

SU1410058A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для вычисления произведения векторов (его варианты) | 1984 |

|

SU1280389A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

Изобретение относится к вычислительной технике и автоматике, предназначено преимущественно для использования в устройствах обработки 1Ц1ФРОВОЙ информации в цифровых измерительных приборах и является усовершенствованием устройства по авт. св. № 1012272. Цель изобретения - расширение функциональных возможностей устройства за счет вычисления скользящего среднего дискретных двумерных полей при высокой точности и быстродействии. Для этого в устройство для вычисления скользящего среднего дополнительно введены третий регистр, дополнительный и накапливающий сумматоры с соответствующими связями. Устройство позволяет реализовать возможность вычисления скользящего среднего по кресту, а следовательно, и возможность использования изобретения в цифровых устройствах измерения и обработки не.только процессов, но и двумерных полей , в частности двумерных изображений. 1 ил. (Л 00

| Устройство для вычисления скользящего среднего | 1981 |

|

SU1012272A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1986-07-30—Публикация

1985-01-04—Подача