Изобретение относится к вычислительной технике и может быть .использовано для вычисления скользящего среднего.в устройствах обработки цифровой информации и в цифровых измерительных приборах.

Цель изобретения - расширение функциональных возможностей устройства за счет усреднения знакопеременной цифровой информации.

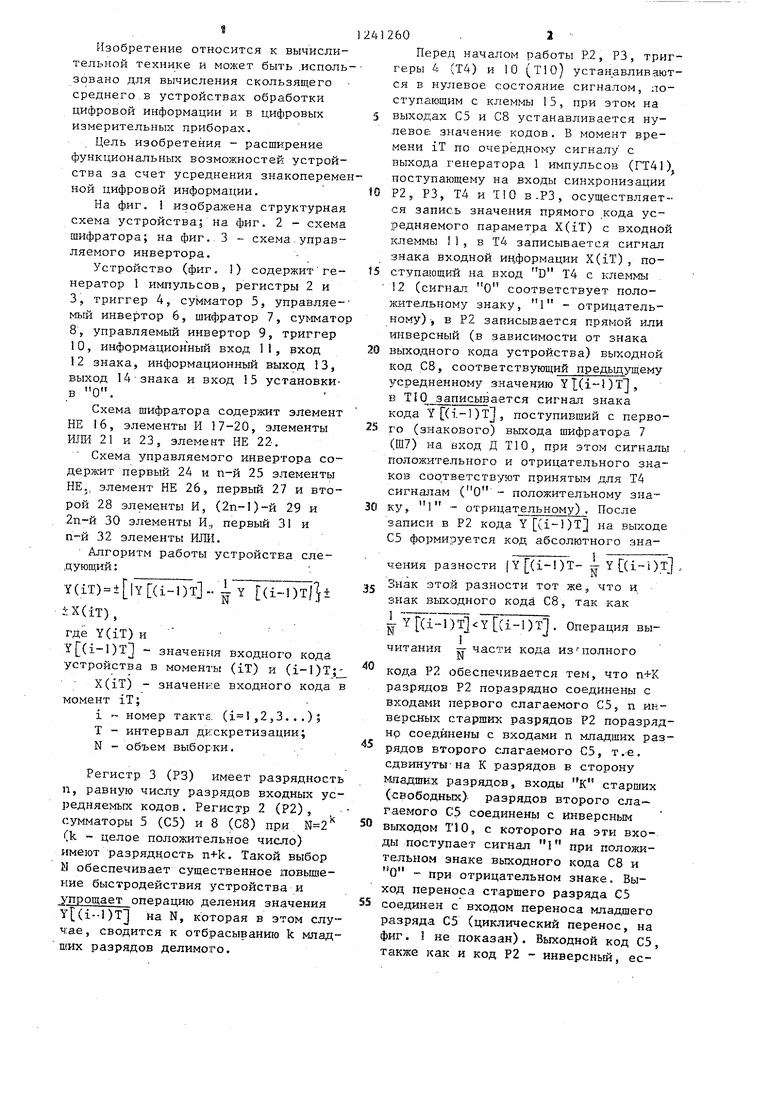

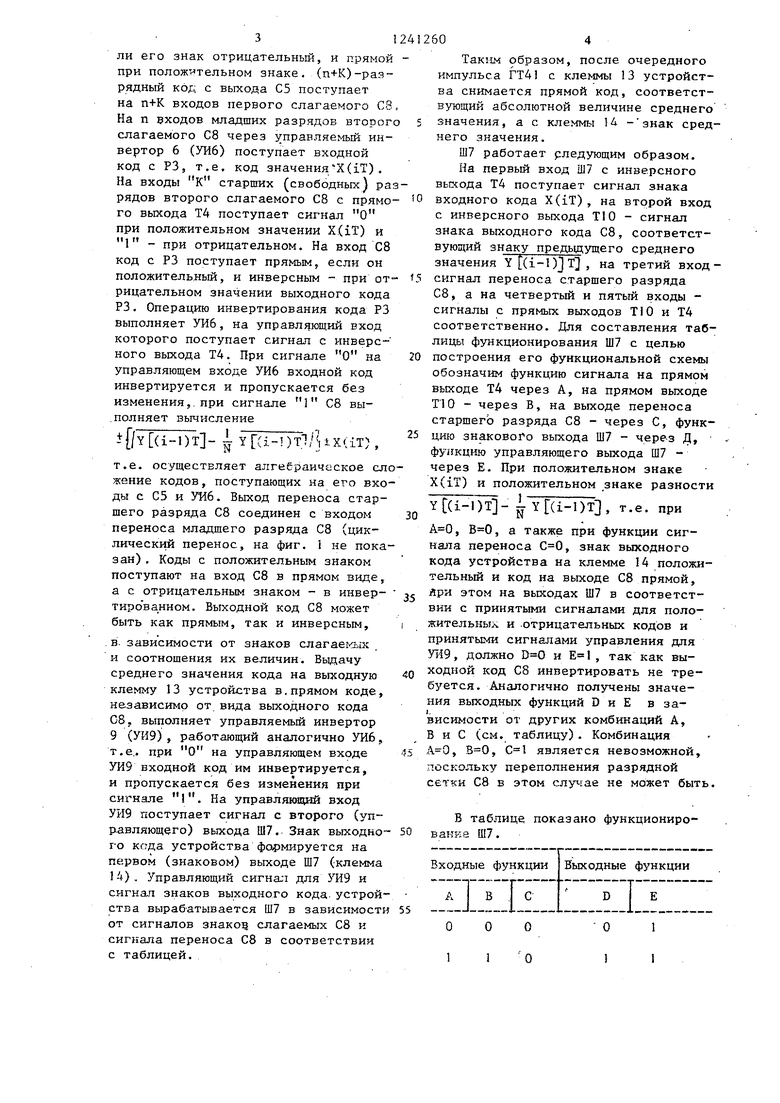

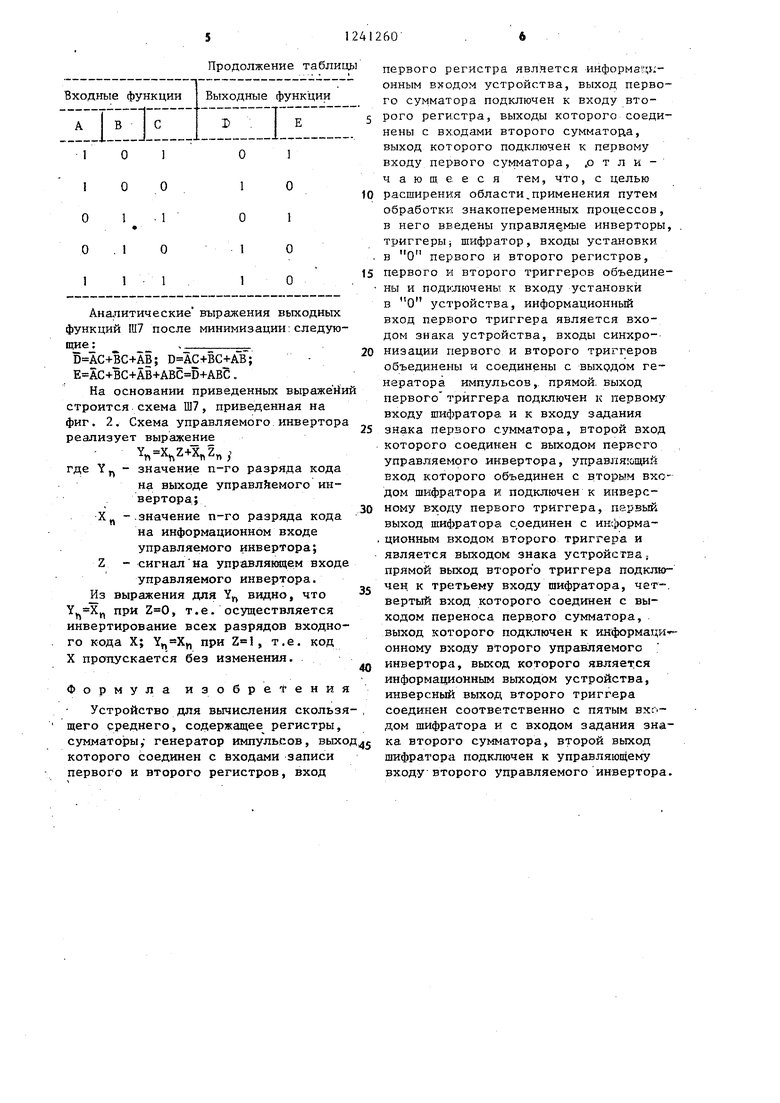

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - схема шифратора; на фиг.. 3 - схема.управляемого инвертора.

Устройство (фиг. ) содержит генератор 1 импульсов, регистры 2 и 3, триггер 4, сумматор 5, управляемый инвертор 6, шифратор 7, сумматор 8, управляемый инвертор 9, триггер 1 О, информационный вход 11, вход 12 знака, информационный выход 13, выход 14-знака и вход 15 установки- в О.

Схема шифратора содержит элемент НЕ 16, элементы И 17-20, элементы ИЛИ 21 и 23, элемент НЕ 22-.

Схема управляемого инвертора содержит первый 24 и п-й 25 элементы НЕ,., элемент НЕ 26, первый 27 и второй 28 элементы И, (2п-1)-й 29 и 2п-й 30 элементы И., первый 31 и п-й 32 элементы ИЛИ.

Алгоритм работы устройства следующий :

Y(iT) .(i-l)T .. IY (i-.l) iX(iT), где Y(iT) и

y(i-l)Tj - значенРЕя входного кода устройства в моменты (IT) и (.i-l)T;j

X(iT) - значение входного кода в момент IT;

i - номер такт. (,2,3...);

Т - интервал дискретизации;

N - объем выбор-ки.

Регистр 3 (РЗ) имеет разрядность п, равную числу разрядов входных усредняемых кодов. Регистр 2 (Р2), сумматоры 5 (С5) и 8 (С8) при (k целое п.оложительное ЧИС,ГЕО) имеют разрядцость n+k. Такой выбор М обеспечивает существенное повышение быстродействия устройства и упрощает операцию деления значения Y(i--)T На N, которая в этом случае, сводится к отбрасыванию k младших разрядов делимого.

4)260 . 2

Перед началом работы Р.2, РЗ, триггеры 4 (Т4) и 10 (ТГО) устанавливаются в нулевое состояние сигналом, поступающим с клеммы 15, при этом на

5 выходах С5 и С8 устанавливается нулевое значение кодов. В момент времени IT по очередному сигналу с выхода генератора 1 импульсов (ГТ41) поступающему на входы синхронизации

to Р2, РЗ, Т4 и Т10 в-РЗ, осуществляется запись значения прямого кода усредняемого параметра X(iT) с входной клеммы П 5 в Т4 записывается сигнал знака входной информации X(iT), по15 ступаЕощий на вход D Т4 с клеммы . 12 (сигнал О соответствует положительному знаку, 1 - отрицательному) , в Р2 записывается прямой или инверсный (в зависимости от знака

20 выходного кода устройства) выходной код С8, соответствующий предыд тцему усредненному значению Yt() Т i 0 записывается сигнал знака кода Y(i-l)Tj, поступивший с перво25 го (знакового) выхода шифратора 7 (Ш7) на вход Д Т10, при этом сигналы положительного и отрицательного знаков соответствуют принятым для Т4 сигналам (О - положительному зна30 ку, 1 - отрицательному). После

записи в Р2 кода Y(i-i)T3 на выходе €5 формируется код абсолютного значения

разности (Y(i-)T- YC(i-i)T

Знак этой разности тот же, что и.

знак выходного кода С8, так как

N

читания

Y(:L-l)(i-l)T. Операция выг части кода из полного

кода Р2 обеспечивается тем, что п+К разрядов F2 поразрядно соединены с входами первого слагаемого С5, п инверсных старших разрядов Р2 поразрядно соединены с входами п младших разрядов второго слагаемого С5, т .-е, сдвинуты-на К разрядов в сторону №1адпш:х разрядов, входы К старших (свободных)- разрядов второго сла гаемого С5 соединены с инверсным выходом Т10, с которого на эти входы поступает сигнал I при положительном знаке выходного кода С8 и О

при отрицательном знаке, Выход переноса старшего разряда С5 соединен с входом переноса младшего разряда С5 (циклический перенос, на фиг. I не показан). Выходной код С5, также как и код Р2 - инверсный, ее31241260

его знак отрицательный, и прямой имв ву зн не

при положительном знаке, (п+К)-разрядный код с выхода С5 поступает на п+К входов первого слагаемого С8 На п 5ХОДОВ младших разрядов второго слагаемого С8 через управляемый инвертор 6 (УИ6) поступает входной код с РЗ, т.е. код значения ХСIT). На входы к старших (свободных) разрядов второго слагаемого С8 с прямо- го выхода Т4 поступает сигнал О при положительном значении X(iT) и 1 - при отрицательном. На вход С8 код с РЗ поступает прямым, если он положительный, и инверсным - при от- рицательном значении выходного кода РЗ. Операцию инвертирования кода РЗ выполняет УИ6, на управл5 ющий вход которого поступает сигнал с инверсного выхода Т4. При сигнале О на управляющем входе УИ6 входной код инвертируется и пропускается без изменения,-при сигнале 1 С8 вы- .полняет вычисление

/у(1-1) i Yfd-DTl/{iX(IT; ,

т.е. осуществляет алгебраическое сложение кодов, поступающих на его входы с С5 и таб. Выход переноса старшего разряда С8 соединен с входом переноса младшего разряда С8 (циклический перенос, на фиг. 1 не показан) . Коды с положительным знаком поступают на вход С8 в прямом виде, а с отрицательным знаком - в инвер- тиро ванном. Выходной код С8 может быть как прямым, так и инверсным.

в. зависимости от знаков слагаемьж и соотношения их величин. Выдачу среднего значения кода на выходную клемму 13 устройства в.прямом коде, независимо от вида выходного кода С8, выполняет управляемьй инвертор 9 (УИ9), работающий аналогично УИб, т.е.. при О на управляющем входе УИ9 входной код им инвертируется, и пропускается без изменения при сигнале |. На управляннцнй вход УИ9 поступает сигнал с второго (управляющего) вьжода Ш7. Знак выходно- го кода устройства формируется на первом (знаковом) выходе Ш7 (клемма 14). Управляющий сигнал для УИ9 и сигнал знаков выходного кода устрой- ства вырабатывается Ш7 в зависимости от сигналов знако слагаемых С8 и сигнала переноса С8 в соответствии с таблицей.

5 О ,5 0

0

5

5

0 5 0 5

образом, после очередного импульса ГТ41 с клеь1мы 13 устройства снимается прямой код, соответствующий абсолютной величине среднего значения, а с клеммы 14 - знак среднего значения.

Ш7 работает рледующим образом.

На первый вход Ш7 с инверсного выхода Т4 поступает сигнал знака входного кода X(iT), на второй вход с инверсного выхода Т10 - сигнал знака вьгходного кода С8, соответствующий знаку предыдущего среднего значения Y (i-l)j Т} , на третий вход - сигнал переноса старшего разряда С8, а на четвертый и пятый входы - сигналы с прямых выходов Т10 и Т4 соответственно. Для составления таб- лиць функционирования Ш7 с целью построения его функциональной схемы обозначим функцию сигнала на прямом выходе Т4 через А, на прямом выходе ПО - через В, на выходе переноса старшего разряда СБ - через С, функцию знакового выхода Ш7 - через Д, функцию управляющего выхода Ш7 - через Е. При положительном знаке X(iT) и положительном знаке разности

Y(i-l) i Y(i-l)T, т.е. при

, , а также при функции сигнала переноса , знак выходного кода устройства на клемме 14 положительный и код на выходе С8 прямой, йри этом на выходах Ш7 в соответствии с принятыми сигналами для положительных и .отрицательных кодов и принятыми сигналами управления для Уй9, должно и , так как выходной код С8 Инвертировать не требуется. Аналогично получены значения выходных функций D и Е в зависимости от других комбинаций А, В и С (см. таблицу). Комбинация , , является невозможной, поскольку переполнения разрядной сетки СВ в этом случае не может быть.

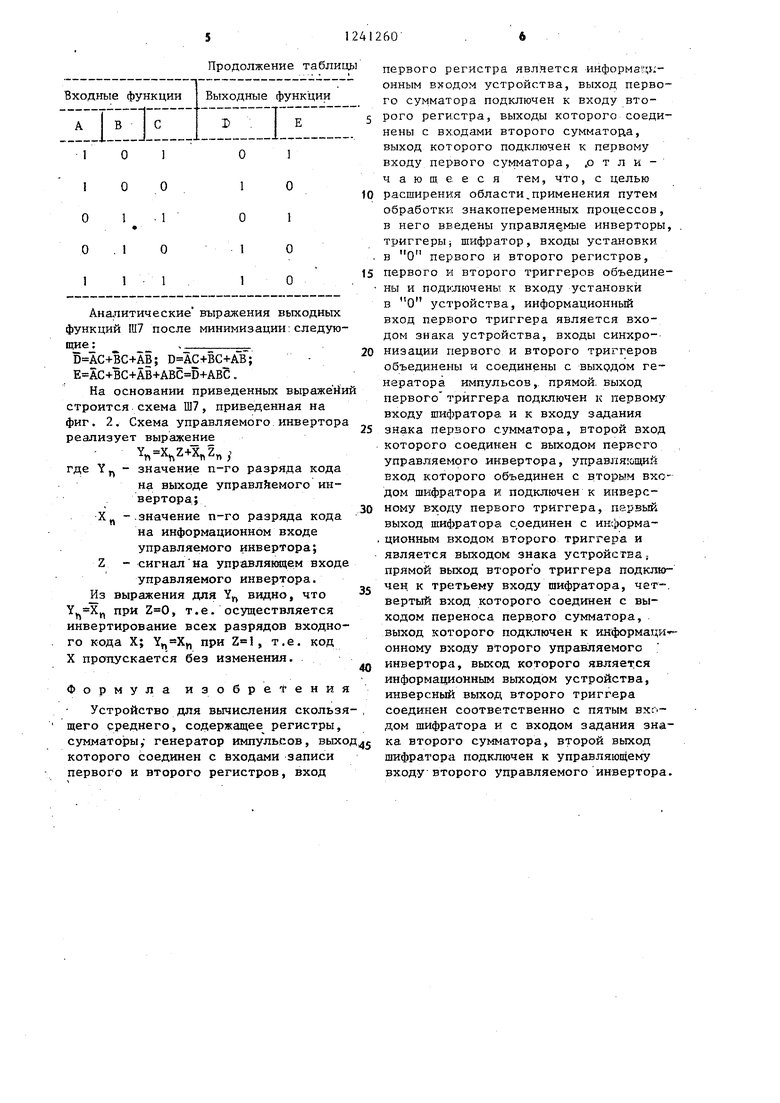

В таблице показано функционировакка Ш7.

Продолжение таблицы

О

О

1

. 1

1

о

. 1 о 1

о 1

о 1 1

1

о 1

о о

Аналитические выражения выходных функций Ш7 после минимизации:следующие :

Б АС+ВС+АВ; D AC+BC+A B; E AC+BC+AB+ABC D+ABC.

На основании приведенных выражени строится схема Ш7, приведенная на фиг, 2. Схема управляемого инвертора реализует выражение

j

где Y - значение п-го разряда кода на выходе управлйемого инвертора;

Х -.значение п-го разряда кода на информационном входе управляемого инвертора; Z - сигнал на управляющем входе

управляемого инвертора, выражения для Y видно, что при , т.е. осуществляется инвертирование всех разрядов входного кода X; при , т.е. код X пропускается без изменения.

Из

Формула изобретения

Устройство для вычисления скользя- , щего среднего, содержащее регистры, сумматоры,- генератор импульсов, выход которого соединен с входами записи первого и второго регистров, вход

0

5

0

5

0

5

0

первого регистра является информационным входом устройства, выход первого сумматора подключен к входу второго регистра, выходы которого соединены с входами второго сумматода, выход которого подключен к первому входу первого сумматора, ,о т л и - чающееся тем, что, с целью расширения области,применения путем обработки знакопеременных процессов, в него введены управляемые инверторы, триггерыj шифратор, входы установки в О первого и второго регистров, первого и второго триггеров объединены и под1 лючены к входу установки в О устройства, информационный вход первого триггера является входом знака устройства, входы синхро-- низации первого и второго триггеров объединены и соединены с выходом генератора импульсов,, прямой, выход первого триггера подключен к первому входу шифратора и к входу задания знака первого сумматора, второй вход которого соединен с выходом первого управляемого инвертора, yпpaвJIя йщий вход которого объединен с вторым входом шифратора и подключен к инверсному входу первого триггера, первый выход шифратора соединен с информа- ционньгм входом второго триггера и является выходом знака устройства; прямой выход второго триггера подключен к тр€ тьему входу шифр-атора, чет-, верты вход которого соединен с выходом переноса перв.ого сумматора, выход которого подключен к информации- онному входу второго управляемого инвертора, выход которого является информационным выходом устройства, инверсный выход второго триггера соединен соответственно с пятым входом шифратора и с входом задания знака второго сумматора, второй выход шифратора подключен к управляющему входу второго управляемого инвертора.

13

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1990 |

|

SU1746378A1 |

| Устройство для деления | 1990 |

|

SU1728860A1 |

| Преобразователь двоичного кода в двоично-десятичный и двоично-десятичного в двоичный | 1979 |

|

SU860051A1 |

| Устройство для вычитания | 1987 |

|

SU1418703A1 |

| Дельта-модулятор | 1988 |

|

SU1510090A2 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Устройство для управления трехфазным инвертором | 1984 |

|

SU1246295A1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| Устройство для сравнения двоичных чисел | 1990 |

|

SU1805463A1 |

| Моментный вентильный электродвигатель | 1988 |

|

SU1751836A1 |

Изобретение относится к вычислительной технике и может быть использовано для вычисления скользящего среднего в устройствах обработки цифровой информации и в цифровых измерительных прибор ах . Цель изобретения - расширение функциональных возможностей устройства за счет .усреднения знакопеременной цифровой информации. Цель изобретения достигается зд счет введения в устройство управляемых инверторов, триггеров и шифратора с соответствующими функциональньми связями между ними и известными блоками устройства. Устройство позволяет получать на его выходе как прямой код, соответствующий абсолютной величине среднего значения, так и знак среднего значения. 3 ил. 1 табл. |i (BBJk. tsS

tt

е

Составитель И. Мухин . Редактор Е,. Копча Тех1)ед В.Кадар Корректор О. Луговая

Заказ 3601/45 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб. д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Зт

| Авторское свидетельство СССР № 762009, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления скользящего среднего | 1981 |

|

SU1012272A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1986-06-30—Публикация

1984-10-03—Подача