Изобретение относится к информационно-измерительной технике и может применяться для обработки данных полученных, в частности, с выхода адаптивных информационно-измерительных систем (АНИС).

Цель изобретения - расширение класса анализируемых сигналов за счет обработки сигналов, аппроксимированных полиномами первой степени.

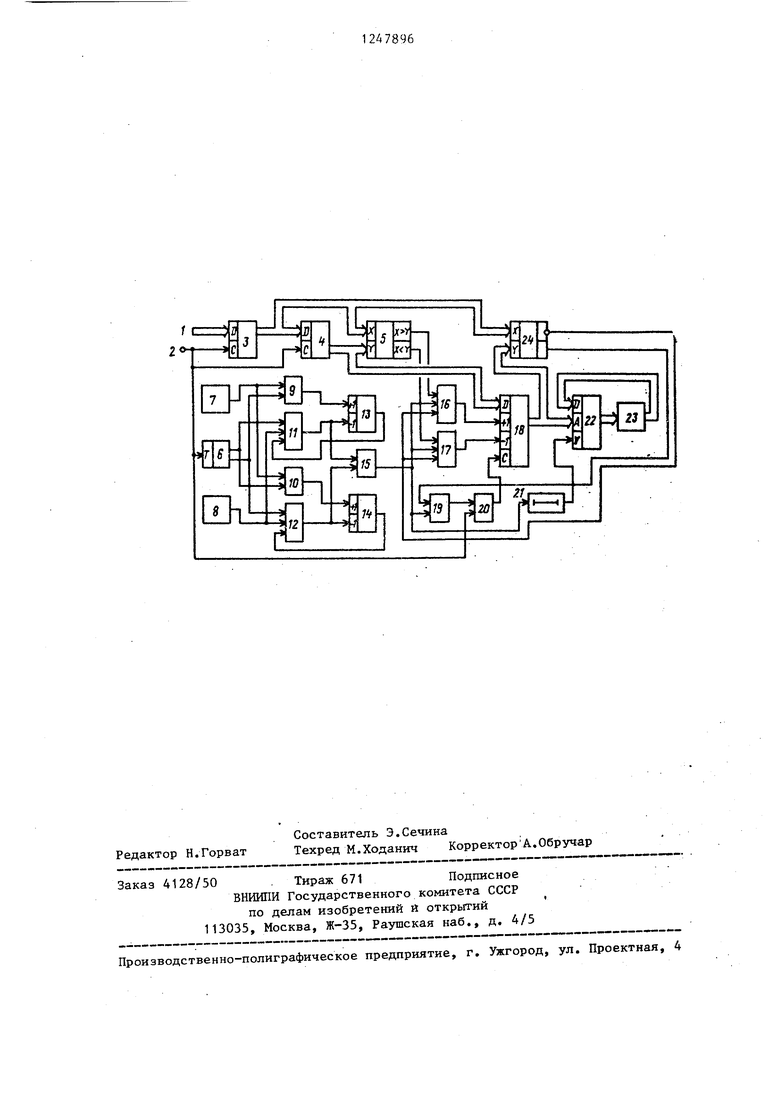

На чертеже, представлена блок-схема устройства для анализа распределений случайных процессов.

Устройство содсфжит информационный вход 1J вход,2 синхронизации, первый 3 и второй 4 регистры,. (двоичный компаратор 5, Т-триггер 6, генераторы 7 и 8 соответственно калибровочных и счетчных импульсовJ элементы И 9-12, счетчики 13 и 14, элемент ИЛИ 15, элементы И 16, 7, счетчик 18, элемент И 19, элемент ИЛИ 20, элемент 21 задержки, блок 22 памяти, комбинационный сумматор 23, схему 24 сравнения кодов.

Устройство работает . следукищим обpJ.v OM.

Дг:к определения плотности распределения случайных процессов измеряется время пребынакия сигнала в дифференциальных коридорах между значениями соседних отсчетов. Время пре- бьшания измеряется в каждом интервале дискретизации за два последовательных цикла - измерения длительности интервала дискретизации и его обработка. Поступивпшй в момент времен t| отсчет X. прерывает цикл измерения длительности интервала dtj - tj и запускает циклы обработки интервала &t и измерения длительности интервала Atj, до ожидаемого ртс-чета Xj .

В цикле измерения определяется общая длительность интервала дискретизации методом подсчета числа калибровочных импульсов Tj

. 1/F, - модуль-макси

А/М,„„КС (

мум 1-и производной исследуемого сигнала, ширина дифференциапь- ного коридора) соответствует , - минимально возможному времени пребывания сигнала в ьХд.

В цикле обработки в ненатуральном ускоренном, масштабе времени восста- навливаются промежуточные значения сигнала и длительность всего интервала дискретнаа15-1И распределяется по

ТОВ X.

зации At.

всём дифференциальным коридорам, расположенньм между значениями отсче и X, интервала дискрети- Дпя i-rp цикла обработки формируется пачка счетных импульсов,, число которых равно числу калибровочных в i-M интервале дискретизации. Импульс АВД, сопровождающий х. , через второй вход устройства поступает, в частности, на Т-вход Т-триггера 6 и перебрасывает его в противоположное состояние, например в 1. Прямой выход последнего открывает элементы И 10, 11. При этом счетчик 14 переводится в режим цикла измерения, так как на его суммируюпщй вход че- рез открывшийся элемент И 11 начина- ют проходить импульсы от генератора 7 калибровочных импульсов. Счётчик 13 переводится в режим цикла обработки: суммирздощий вход блокируется закрытием элемента И 9 О на инверсном выходе Т-триггера 6, счетчик 13 фиксирует число N dtjF и на его вычитающий вход и одновременно на первый вход первого элемента ИЛИ 15 через элемент И 11 начинают

проходить импульсы частоты F с выхода генератора 8 счетных импульсов. N-й счетный импульс обнулит счетчик 13 и появившийся на его инверсном выходе переноса закроет элемент И 11, прекращая прохождение на вычитающий вход, а также на первый вход элемента ИЛИ 15 счетных,импульсов . Пачка счетных импульсов для 1-го цикла обработки сформирована. Для завершения цикла обработки до прихода Xj,, необходимо выполне

ние условия F (it )--F, - наименьший возможньш

тех/

где

интервал диcкpeтизaции at наибольший возможный интервал дискретизации. Следующий (i + 1)-й импульс АВД перебрасывает Т-триггер 6 в состояние О и счетчики 13 и 14 меняются ролями: калибровочные импульсы подсчитьшаются счетчиком 13, а счетные импульсы уменьшают содержимое счетчика 14.

Код отсчета Xj поступает на первый вход 1 устройства и записывается в первый регистр 3 импульсом АВД, который одновременно переписывает из первого 3 во второй 4 регистр код отсчета Xi

и заносит его

в счетчик 18, пройдя через элемент ИЛИ 20 на вход начальной установки

3 - 1

счетчика 18. Коды отсчетов Х; и Xj J проверяются в двоичном компара торе 5 и схеме 24 сравнения кодов на выполнение условий.соответствени X , X.

В

г-1 - - 1-1

зависимости от их выполнения зависи режим цикла счета,

Xj Х|, (Сигнал за времй dt. находился в К-м дифференциальном коридоре, К Х|(дхд) 1 с прямого выхода схемы 24 сравнения кодов открывает элемент И 19 для прохождения счетньпс импульсов на вход начальной установки третьего счетчика 18. О с инверсного выхода схемы 24 сравнения кодов за:крывает элементы И 16,

17,блокируя тем самьи суммирующий

и вычитающий входы счетчика 18. Каждый иэ N счетных импульсов заносит в него код отсчета х . Этот код с .выхода счетчика 18, подаваясь на адресный вход блока 22 памяти, опрашивает его К-ю ячейку. Содержимое этой ячейки увеличивается на 1 в комбинационном сумматоре 23 и с его выхода подается на информационный вход блока 22 памяти и записывается в ту же ячейку счетным импульсом, задержанным элементом 21 задержки на величину, равную сумме времен установки кода отсчета х. в счетчик

18,срабатьшания комбинационного суи матора 23 и считывания из блока 23 памкти. Тс.ким образом, содержимое К-й ячейки блока 22 памяти увеличивается на число N, пропорциональное времени пребывания (в данном случае At|) сигнала в К-м дифференциальном коридоре.

X: Xj.,

(Сигнал за время ut; находился в К-м (К - 1)-м, ..., (К - - f)-м дифференциальных коридорах, t .дх./йХд). На первом выходе двоичного компаратора 5 появляется 1,. которая вместе с 1, поступающей с инверсного вы,:ода схемы 24 сравнения кодов, открьшает элемент И 17. для прохождения счетных импульсов на вычитающий вход счетчика 18. Логические О со второго выхода двоичного компаратора 5 и с прямого выхода схемы 24 сравнения кодов .блокируют остальные входы счетчика 18. Первый в цикле обработки счетный импульс, пройдя на вычитающий вход счетчика 18, умень шит на 1 записанный в нем код отсчета х., . На выходе блока 22 памяти появится содержимое (К - 1)-й

2478964

ячейки, которое увеличится на 1 в комбинационном сумматоре 23 и запишется в ту же ячейку первым счетным импульсом, задержанным элементом 21 5 задержки. Следующие счетные импульсы последовательно уменьшают установленный в счетчике 18 код х;., , производя таким образом опрос ячеек блока 22 памяти и увеличивая на 1 их со10 держимое, t-й счетный импульс сравняет выходной код счетчика 18 с кодом X.. 1 с прямого выхода схемы 24 сравнения кодов откроет элемент И 19, а. О { инверсного выхода закроет

15 элементы И 16, 17. (t + 1)-й счетный импульс пройдет на вход начальной установки счетчика 18, установит в

него код отсчета х.

и увеличит на

1 содержимое К-й ячейки блока 22 20 памяти. Такой подцикл опроса соответствует изменению сигнала с М,,

и

нахождению его в каждом из f ди4)фе- . ренциальных коридоров наименьшее время. При + 1 подциклы опроса повторяются D раз и содержимое ячеек от К до К - t увеличится на D. Таким образом

D N/1 + 1 Fc&t i/лх- , А

I: - в(«...кХг).

В - A /4Хд.

, ...и ,

Так как М, AXi /ut; и М.,„„

ux;/ut ,. то D B-itj /At .

Поскольку в и , заранее известны j то число, записанное в каждую ячейку из t ячеек блока 22 памяти за i-й цикл обработки, пропорционально

времени пребывания сигнгша в каждом из t дифференциальных коридоров, х х- . . Режим работы устройства аналогичен предыдущему, отличаясь тем, что счетчик 18, формирующий код адреса блока 22 памяти в подциклах опроса, суммирует счетные импульсы к установленному в нем коду х. . В подцикле опроса вычитающий вход счетчика 18 блокирован,

так как элемент И 17 закрыт О с первого выхода двоичного компаратора 5. 1 со второго выхода последнего вместе с 1 с инверсного выхода схемы 24 сравнения кодов открывает

элемент И 1б для прохождения в под- цикле опроса счетных импульсов на суммирующий вход счетчика 18. Таким образом учитывается знак производ-

ой исследуемого сигнала на инвер- але л tj .

При обработке отсчетов, переданных при аппроксимации сигнала поли- номами нулевой степени, дХ| будет постоянным для интервалов дискрети- здции любой длительности. При обработке данных с выхода неадаптивньк ИИС будет постоянным ut;i. И, следовательно, число N.

Коды отсчетов и сопровождающие их импульсы могут поступать как с выхода блока воспроизведения на магнитной ленте, так и непосредственно с выхода информационно-измерительной системы (адаптивной или обычной).

Формула изобретения

-Устройство для анализа распределений случайных процессов, содержащее блок памяти, группа выходов которого соединена соответственно с группой входов комбинационного сумматора, группа выходов которого подключена к группе информационных входов блока памяти, отличающееся тем, что, с целью расширения класса анализируемых путем обработки сигналов, аппроксимированных полиномам. -г первой степени,, оно содержит компаратор, Т-триггер, генератор калибровочных импульсов, с первого по седьмой элементы И, первый и второй элементы ИЛИ, элемент задержки, генератор счетных импульсов, первый, второй и третий счетчи- .ки, схему сравнения кодов, первый и второй регистры, причем выход первого регистра подключен к информационному входу второго регистра, а также к первым входам компаратора и схемы сравнения кодов, выход второго регистра подключен к второму входу компаратора и к входу начальной установки первого счетчика, выход которого подключен к адресному входу памяти и второму входу схемьз сравнения кодов, выход генератора калибровочных импульсов подключен к

первым входам первого и второго элементов- И, выходы которых соединены с суммирующими входами соответственно второго и третьего счетчиков, выход генератора счетных импульсов соединен с первыми входами третьего и четвертого элементов И, выходы кото- рьгк соединены с вычитающими входами

соответственно второго и третьего счетчиков и соответственно - с первым и вторым входами первого элемента ИЛИ, инверсные выходы переноса второго и третьего счетчиков подключены к вторым входам соответственно третьего и четвертого элементов И, третий вход четвертого элемента И и второй вход первого элемента И объединены и подключены к инверсному

выходу Т-триггера, прямой выход которого соединен с третьим входом третьего и вторым входом второго элементов И, выход первого элемента ИЛИ .подключен к первым входам пятого,

шестого и седьмого элементов И непосредственно, а через элемент задержки - к входу управления записью блог. ка памяти, вторые входы пятого и шестого элементов И соединены соответственно с выходами Больше и Меньше двоичного компаратора, а выходы пятого и шестого элементов И соединены соответственно с суммирующим и вычитающим входами первого

. вход начальной установки которого подключен к выходу второго элемента ИЛИ, первый вход которого соединен с выходом седьмого элемента ИЛИ, второй вход которого подключен к прямому выходу схемы сравнения кодов, инверсный выход которой соединен с третьими входами пятого и шестого элементов И, при этом информационный вход первого регистра является информационным входом устройства, а вход синхронизации первого регистра объединен с одноименным входом второго регистра, вторым входом второго элемента ИЛИ, входом Т-триг- гера и подключен к шине синхронизации устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Усреднитель-анализатор спектра Фурье | 1980 |

|

SU955086A1 |

| Цифровой перестраиваемый полосовой фильтр | 1982 |

|

SU1166274A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ АКТИВНОЙ МОЩНОСТИ | 1993 |

|

RU2074397C1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Многофункциональный цифровой коррелометр | 1986 |

|

SU1363246A1 |

| Аналого-цифровой нелинейный процессор | 1988 |

|

SU1575194A1 |

| Функциональный преобразователь | 1984 |

|

SU1241257A1 |

| АНАЛИЗАТОР СЛУЧАЙНЫХ ПРОЦЕССОВ | 1991 |

|

RU2012052C1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Адаптивный кодирующий преобразователь стационарных случайных процессов | 1980 |

|

SU960846A1 |

Изобретение относится к информационно-измерительной технике и может применяться для ю бработки данных, полученных, в частности, с выхода адаптивных информационно-измерительных систем (АИИС). Цель изобретения - распшрение класса анализируемых сигналов за счет допол1СТ €0 0 Н « 13 ;;::: ,13 Б1КЛНОТЕКЛ нительной обработки сигналов, ап- 11роксимированных полиномами первой степени. С этой целью в устройство для анализа распределений случайных процессов, содержащее блок памяти, комбинационный сумматор, соединенный выходом с информационным входом блока памяти, а входом - с выходом последнего, введены первый и второй регистры, двоичный компаратор, Т- триггер, генератор калибровочнйх и генератор счетным импульсов, первый, второй. Третий, четвертуй, пятый, шестой и седьмой элементы И, первый и второй, элементы ИЛИ, первый и второй элементы НЕ, элемент задержки, первый, второй и третий счетчики, схема совпадения кодов. Преимущества устройства состоят в том, что- создается возможность в обработке данных с выхода АИИС, аппроксимирующих сигналов полиномами как нулевой, так и первой степени, 1 ил. т

Составитель Э.Сечина Редактор Н.Горват ехред М.ХоданичКорректор А.)бр У;1ар.

з1к1з1128/50 Тираж 671 °ТсССР

ВНИИПИ Государственного комитета buof

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие.

г. Ужгород, ул. Проектная, 4

| Устройство для формирования гистограммы случайных чисел | 1981 |

|

SU995097A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для анализа распреде-лЕНий СлучАйНыХ пРОцЕССОВ | 1979 |

|

SU830399A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1986-07-30—Публикация

1985-02-22—Подача