Изобретение относится к вычислительной технике, в частности к устройствам хранения ин ормации, и предназначено, например, для электрон- ных цифровых вычислительных систем, выполненных на узлах с большой степенью интеграции.

Цель изобретейия - расширение области применения устройства за счет обеспечения ассоциативного маскированного поиска в элементах постоянной памяти, а также параллельной записи информации в элементы оперативной памяти в процессе ассоциативного поиска.

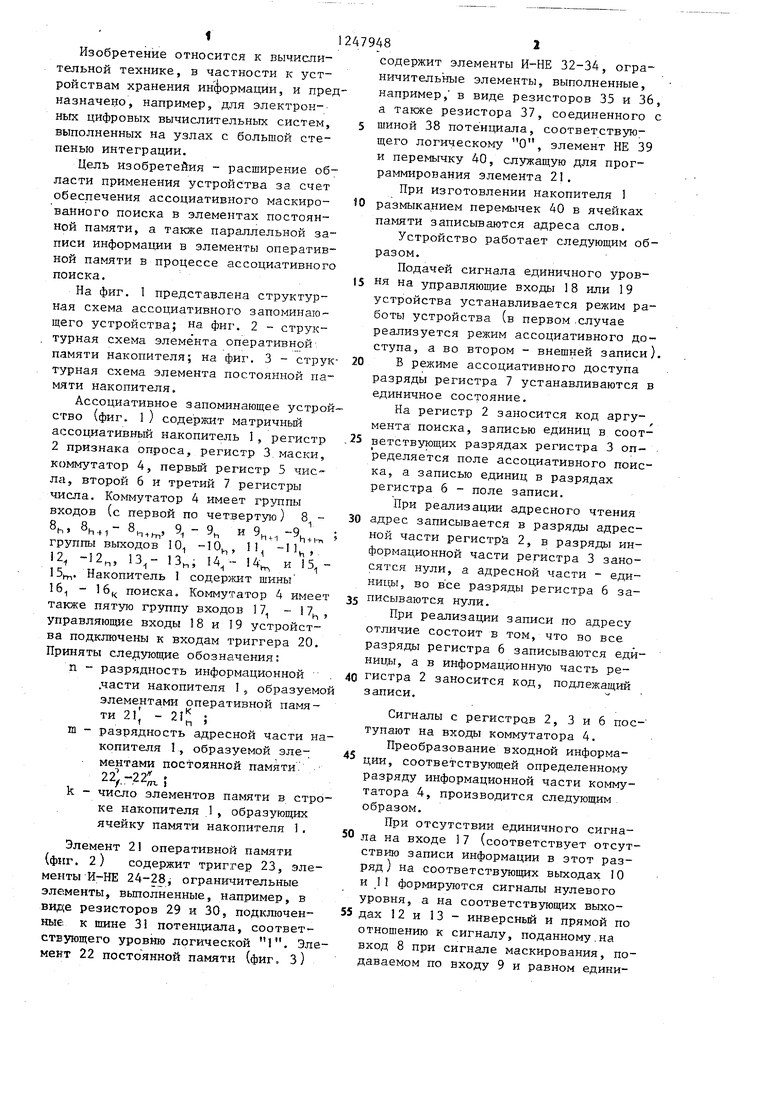

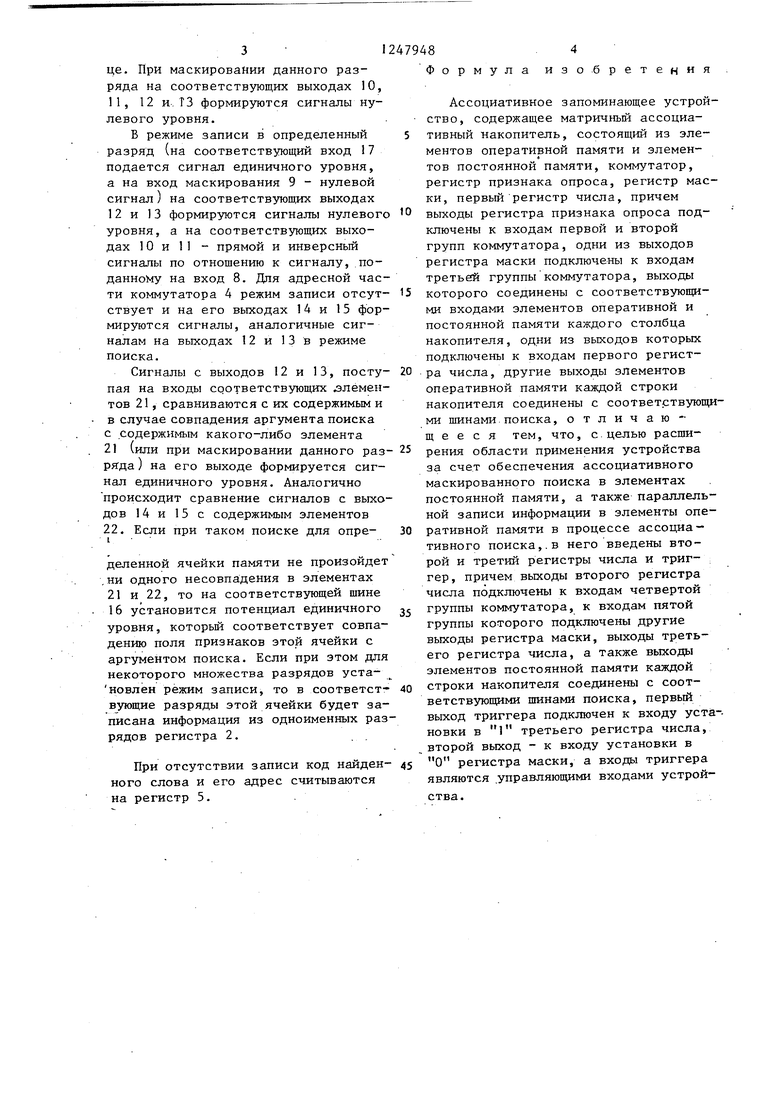

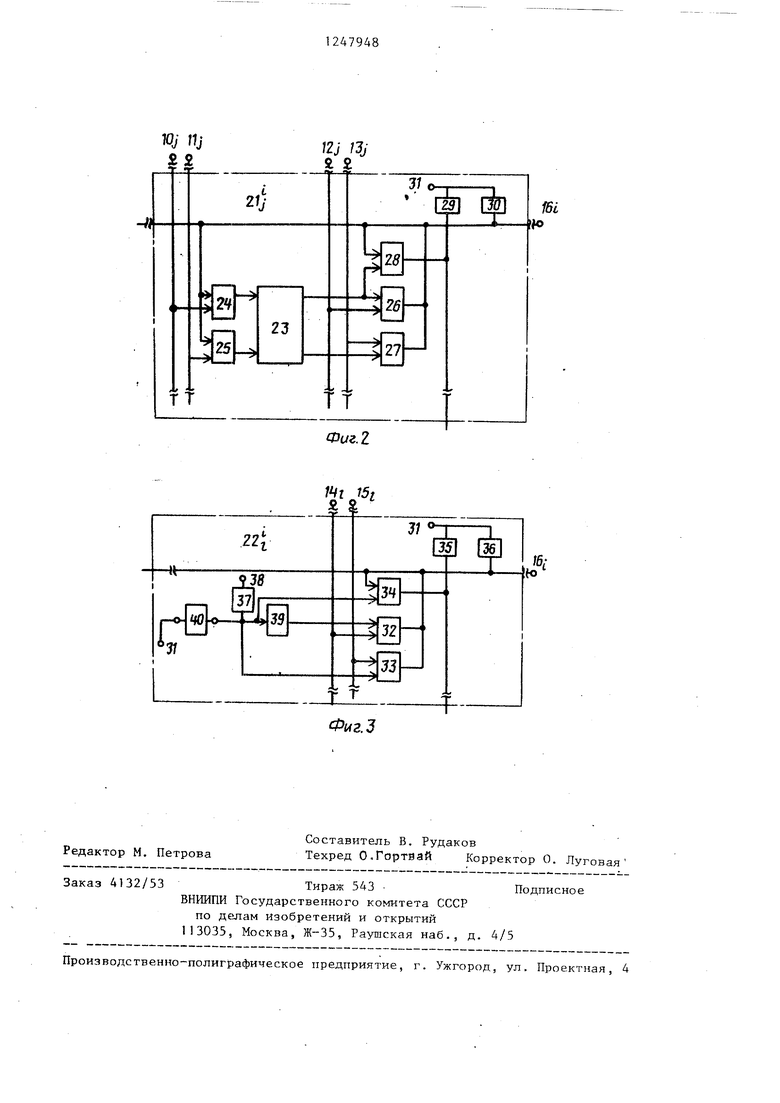

На фиг. 1 представлена структурная схема ассоциативного запоминающего устройства; на фиг. 2 - структурная схема элеме нта оперативн ой памяти накопителя; на фиг. 3 - структурная схема элемента постоянной памяти накопителя.

Ассоциативное запоминающее устроство (фиг. 1 ) содержит матричньш ассоциативный накопитель I, регистр 2 признака опроса, регистр 3. маски, коммутатор 4, первьй регистр 5 чис ла, второй б и третий 7 регистры числа. Коммутатор 4 имеет группы входов (с первой по четвертую) 8 - 8, 8.,,- 8.. . 9. - 9. и

Q -О

h+i h + hr,

Ы h-tl h + iT, l

группы ВЫХОДОВ 10, l h

2, -12,

13,13.

lA,- 4

. Накопитель 1 содержит шины

15,16, 16,

4 имеет 17.

j поиска. Коммутатор также пятую группу входов 17, п управляющие входы 18 и 19 устройства подключены к входам триггера 20. Приняты следующие обозначения: п - разрядность информационной

.части накопителя I , образуемо

элементами оперативной памя- ти 21 211 ;

m - разрядность адресной части наk ментами постоянной памяти.

22 -22 f. f- -m. )

число элементов памяти в стро- 1

Сигналы с регистров 2, 3 и 6 пос- тупают на входы коммутатора 4.

Преобразование входной информа- копителя 1, образуемой эле- 45 ,

. 4J ции, соответствующей определенному

разряду информационной части коммутатора 4, производится следующим . образом.

При отсутствии единичного сигна50 ла на входе 17 (соответствует отсутствию записи информации в этот разряд) на соответствующих выходах 10 и 1I формируются сигналы нулевого уровня, а на соответствующих выхо55 дах 12 и 13 - инверсньй и прямой по отношению к сигналу, поданному.на вход В при сигнале маскирования, подаваемом по входу 9 и равном единике накопителя 1, образующих ячейку памяти накопителя 1,

Элемент 2 оперативной памяти (фнг. 2) содержит триггер 23, элементы И-НЕ 24-28, ограничительные элементы, выполненные, например, в виде резисторов 29 и 30, подключенные к шине 31 потешшала, соответствующего уровню логической 1. Элемент 22 постоянной памяти (фиг. Э)

содержит элементы И-НЕ 32-34, ограничительные элементы, выполненные, например, в виде резисторов 35 и 36, а также резистора 37, соединенного с

шиной 38 потенциала, соответствующего логическому О, элемент НЕ 39 и перемычку 40, служащую для программирования элемента 21.

При изготовлении накопителя 1

0 размыканием перемычек 40 в ячейках памяти записываются адреса слов.

Устройство работает следующим образом.

Подачей сигнала единичного уров5 ня на управляющие входы 18 или 19 устройства устанавливается режим работы устройства (в первом .случае реализуется режим ассоциативного доступа, а во втором - внешней записи).

0 В режиме ассоциативного доступа разряды регистра 7 устанавливаются в единичное состояние.

На регистр 2 заносится код аргумента поиска, записью единиц в соот- 5 ветствующих разрядах регистра 3 оп- . ределяется поле ассоциативного поиска, а записью единиц в разрядах регистра 6 - поле записи.

При реализации адресного чтения

0 адрес записывается в разряды адресной части регистра 2, в разряды информационной части регистра 3 заносятся нули, а адресной части - единицы, во все разряды регистра 6 за5 писываются нули.

При реализации записи по адресу отличие состоит в том, что во все разряды регистра 6 записываются единицы, а в информационную часть ре40 гистра 2 заносится код, подлежащий записи.

це. При маскировании данного разряда на соответствующих выходах 10, 11, 12 и.ТЗ формируются сигналы нулевого уровня.

В режиме записи в определенный разряд (на соответствующий вход 17 подается сигнал единичного уровня, а на вход маскирования 9 - нулевой сигнал) на соответствующих выходах 12 и 13 формируются сигналы нулевого уровня, а на соответствующих выходах 10 и 11 - прямой и инверсный сигналы по отношению к сигналу, поданному на вход 8. Для адресной части коммутатора 4 режим записи отсут- ствует и на его выходах 14 и 15 формируются сигналы, аналогичные сигналам на выходах 12 и 13 в режиме поиска.

Сигналы с выходов 12 и 13, посту- пая на входы соответствующих .элементов 21, сравниваются с их содержимым и в случае совпадения аргумента поиска с содержимым какого-либо элемента 21 (или при маскировании данного раз ряда) на его выходе формируется сигнал единичного уровня. Аналогично происходит сравнение сигналов с выходов 14 и 15 с содержимым элементов 22. Если при таком поиске для опре-

деленной ячейки памяти не произойдет , ни одного несовпа дения в элементах 21 и 22, то на соответствующей шине 16 установится потенциал единичного уровня, которьй соответствует совпадению поля признаков этой ячейки с аргументом поиска. Если при этом для некоторого множества разрядов уста- новлен режим записи, то в соответст- вующие разряды этой ячейки будет записана информация из одноименных разрядов регистра 2.

При отсутствии записи код найден- ного слова и его адрес считываются на регистр 5.

Формула изобретения

Ассоциативное запоминающее устройство, содержащее матричньм ассоциативный накопитель, состоящий из элементов оперативной памяти и элементов постоянной памяти, коммутатор, регистр признака опроса, регистр маски, первый регистр числа, причем выходы регистра признака опроса подключены к входам первой и второй групп коммутатора, одни из выходов регистра маски подключены к входам третьей группы коммутатора, выходы которого соединены с соответствующими входами элементов оперативной и постоянной памяти каждого столбца накопителя, одни из выходов которых подключены к входам первого регистра числа, другие выходы элементов оперативной памяти каждой строки накопителя соединены с соответствующми шинами,поиска,отличаю- щ е е с я тем, что, с.целью расширения области применения устройства за счет обеспечения ассоциативного маскированного поиска в элементах постоянной памяти, а также параллельной записи информации в элементы оперативной памяти в процессе ассоциативного поиска,.в него введены второй и третий регистры числа и триггер, причем выходы второго регистра числа подключены к входам четвертой группы коммутатора, к входам пятой группы которого подключены другие выходы регистра маски, выходы третьего регистра числа, а также выходы элементов постоянной памяти каждой строки накопителя соединены с соответствующими шинами поиска, первый вьпсод триггера подключен к входу уста новки в 1 третьего регистра числа, второй выход - к входу установки в О регистра маски, а входы триггера являются .управляющими входами устройства.

Фиг.1

Фиг.З

Редактор М. Петрова

Составитель В. Рудаков

Техред О.Гортяай Корректор О. Луговая

Заказ 4132/53Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР

по Изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство | 1982 |

|

SU1043750A1 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Ассоциативное оперативное запоминающее устройство | 1986 |

|

SU1363307A1 |

| Ассоциативное оперативное запоминающее устройство | 1987 |

|

SU1462420A1 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1309041A1 |

| Устройство для поиска информации в ассоциативной памяти | 1988 |

|

SU1617460A1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1388949A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2045787C1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1401518A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2025796C1 |

| Ассоциативное запоминающее устройство | 1977 |

|

SU720510A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Патент США № 3602899, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

Авторы

Даты

1986-07-30—Публикация

1985-02-11—Подача