Изобретение относится, к вьгч сли- тельной техн:ике н предназначено для генерирования последовательности натуральных чисел в р-коде Фибоначчи

Цель изобретения - повышение бьуст родействрш о

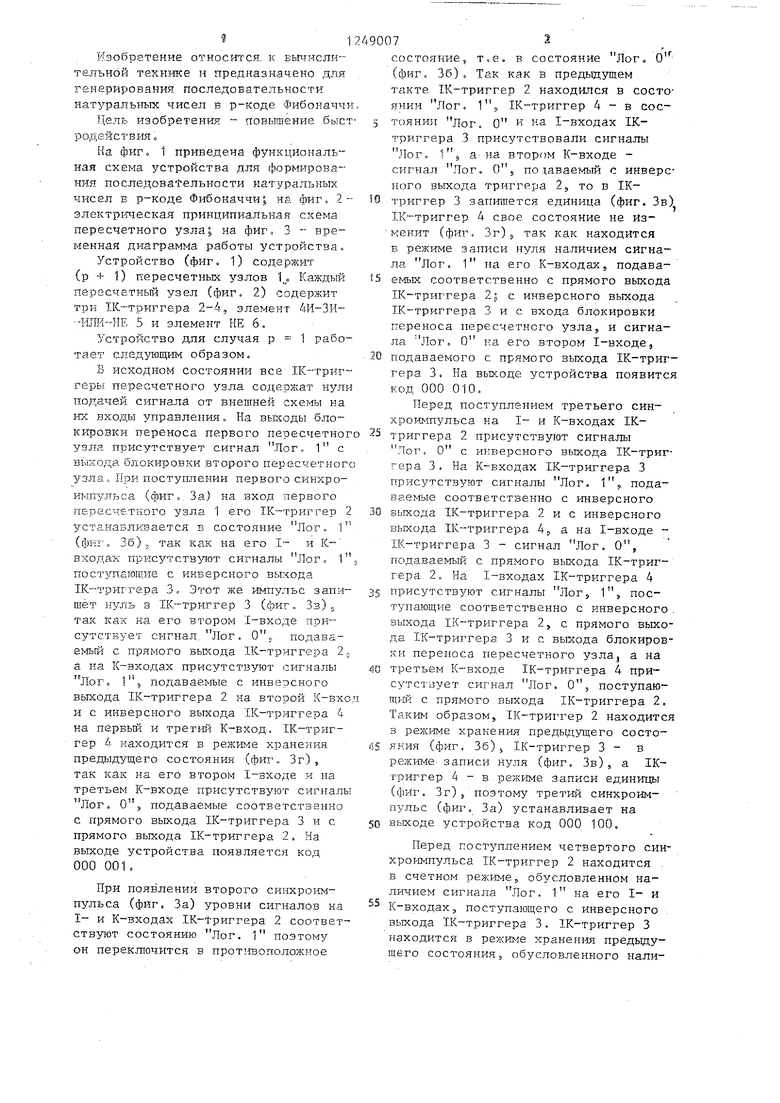

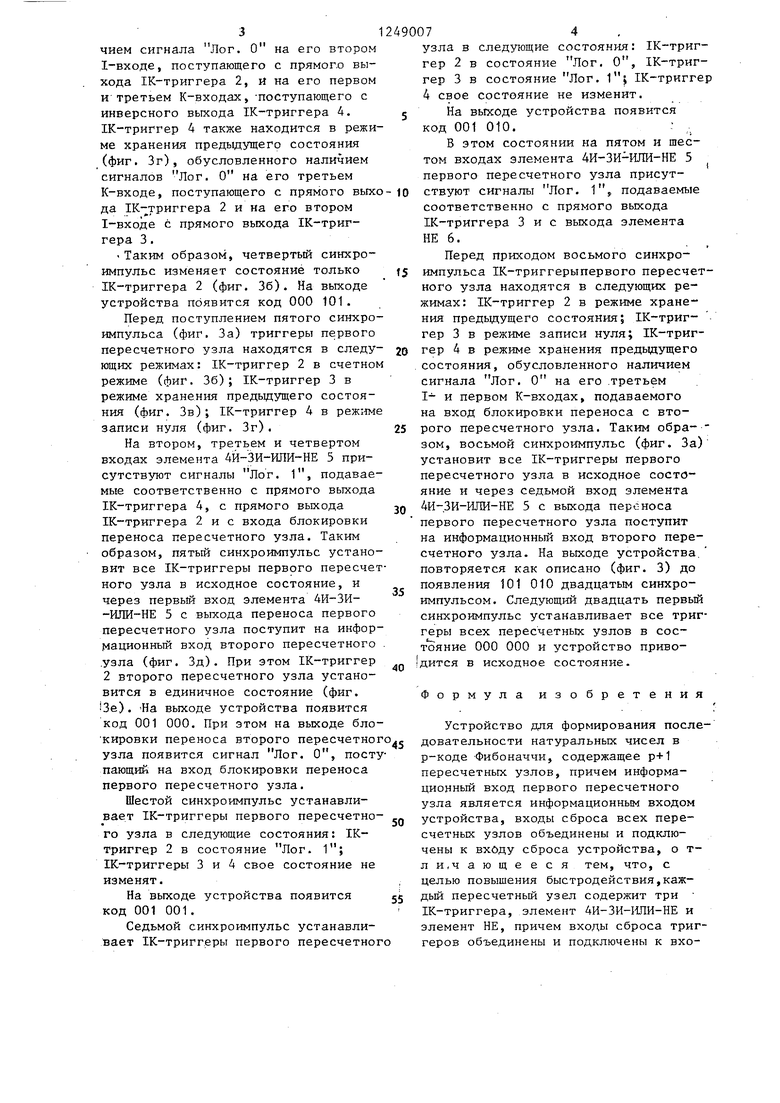

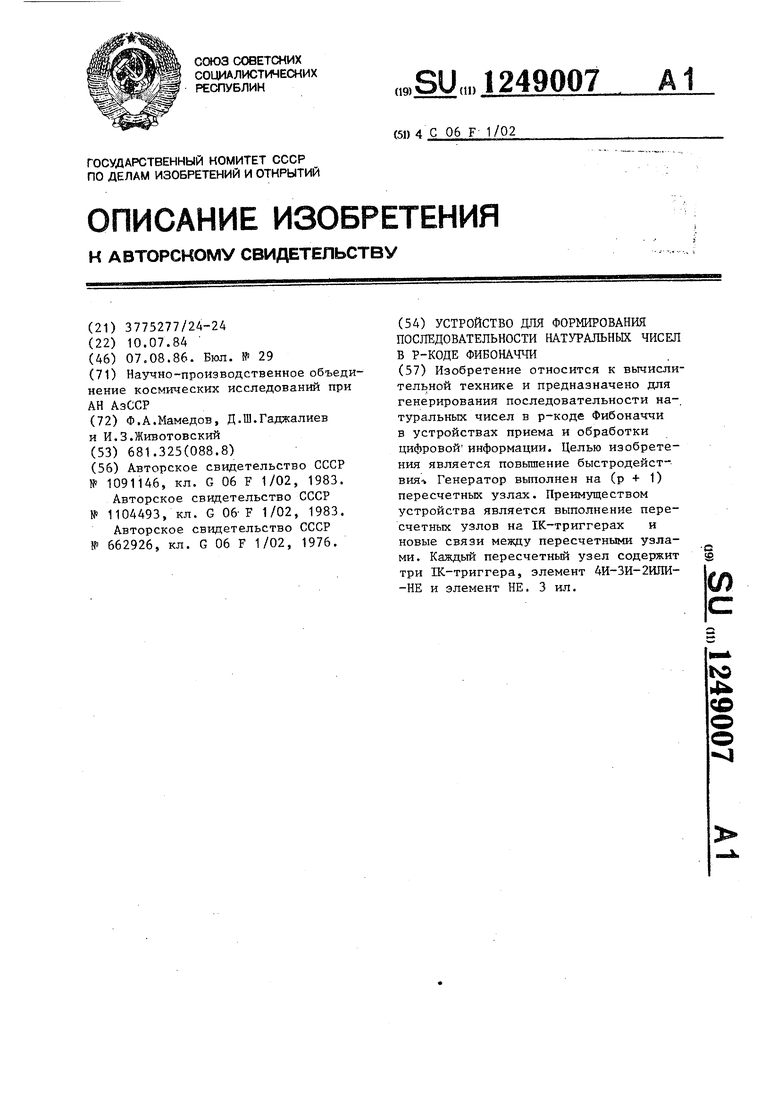

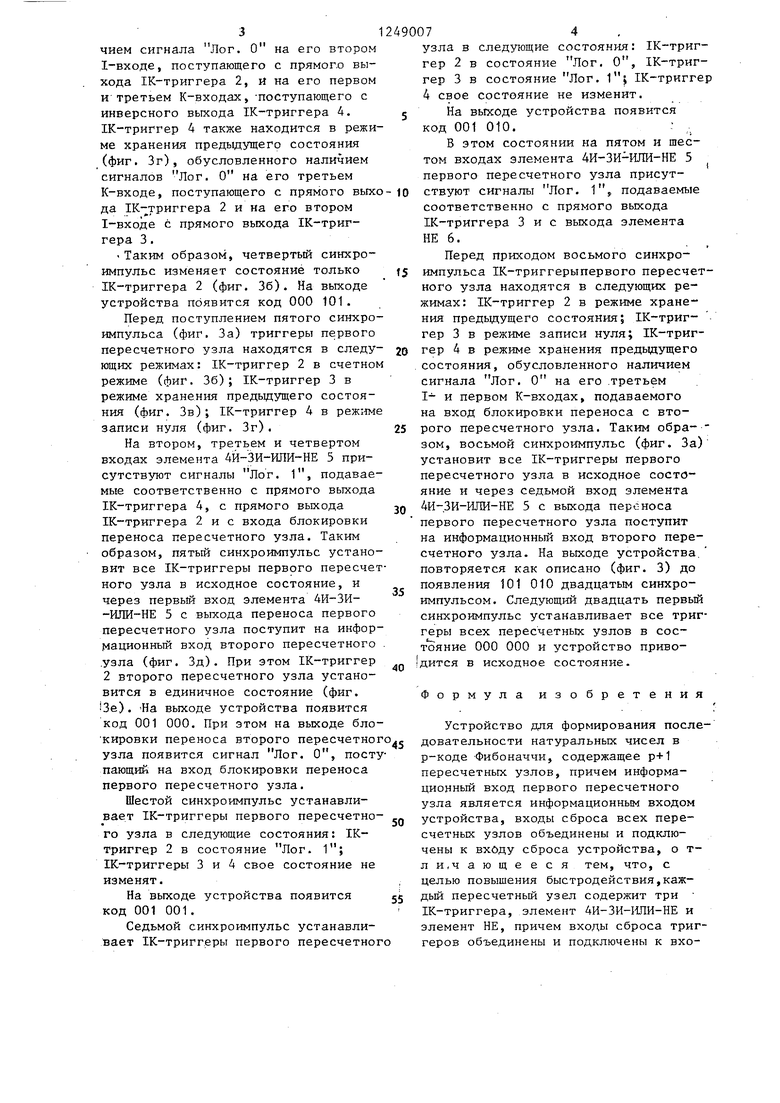

Ка фиг, 1 приведена функциональная схема устройства для формирования последовательности натуральных чисел Е р-коде Фибоначчи; на фиг. 2- электрическая принципиальная схема

пересчетного узла; на фиг.

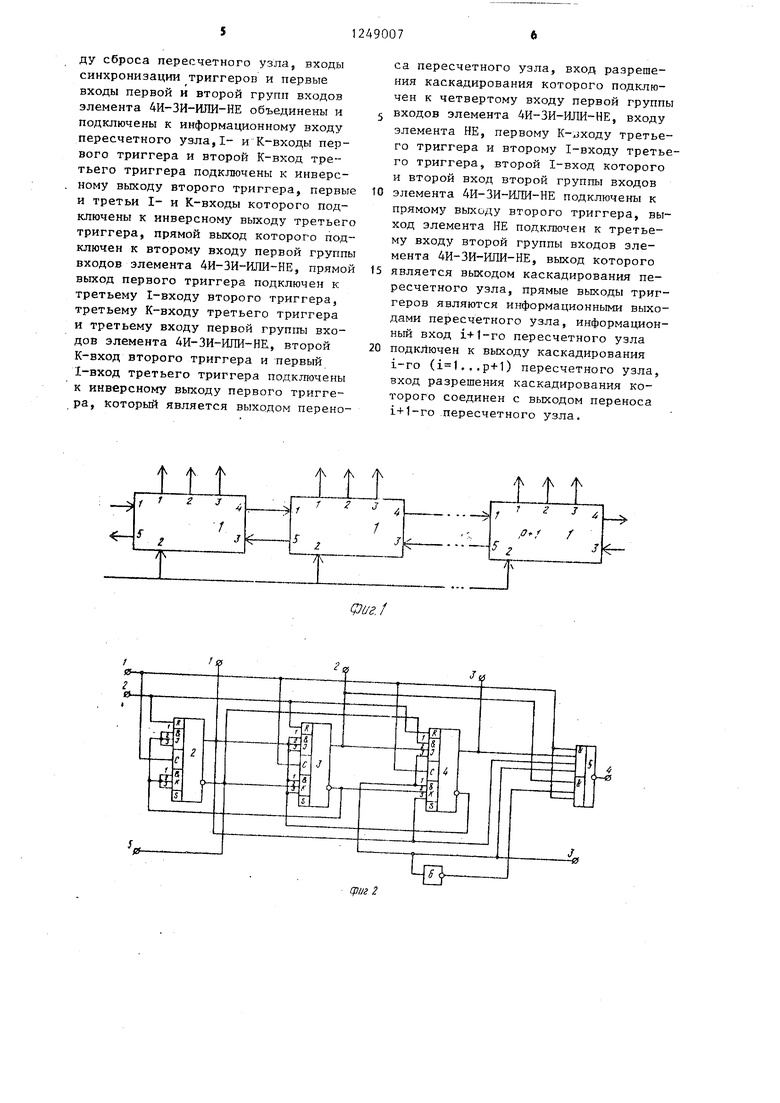

временная диаграмма работы устройства.

Устройство (фиго 1) содержит (р 4- 1) пересчетных узлов 1,, Каждый пересчетньм узел (фиг« 2) содержит три НС-триггера 2-4, элемент 4И-ЗИ 1 Ш1 НЕ 5 и элемент НЕ 6.

Устройство для случая р 1 работает след тощи1ч образом с

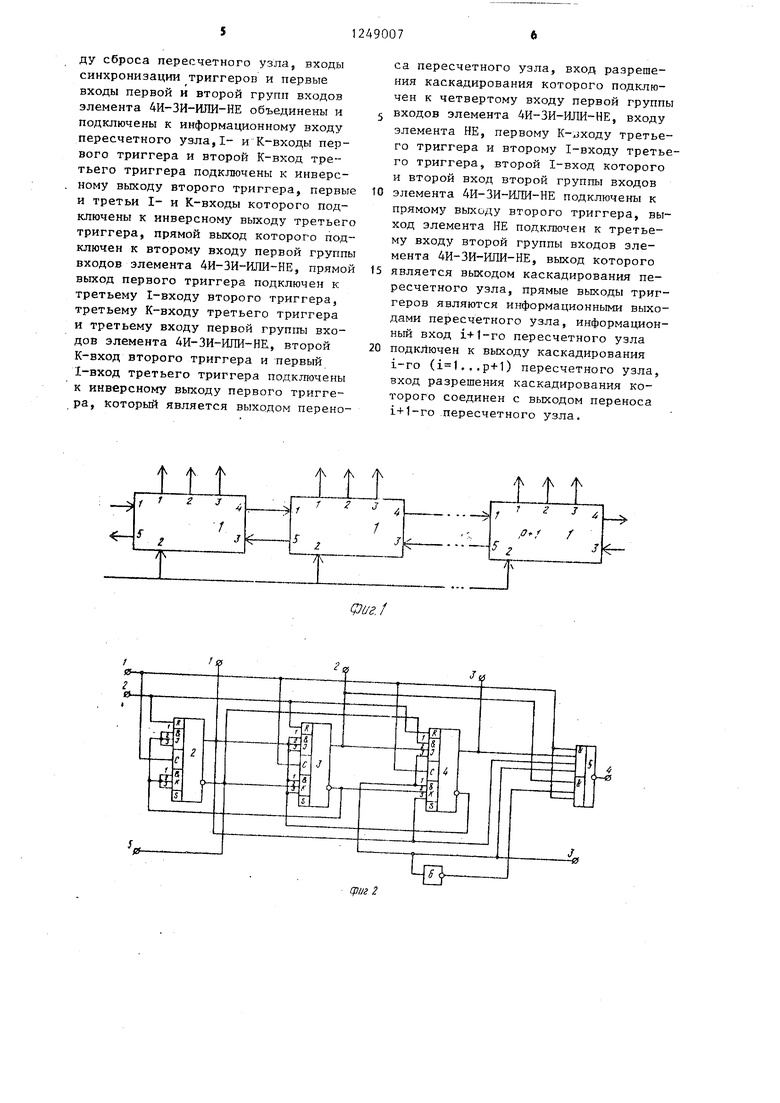

В исходном состоянии все Ж-триг- геры пересчетного узла содерхсат нули подачей сигнала от внешней схемы на WX входы управления о На выходы блокировки переноса первого нересчетног узла присутствует сигнал Лог, 1 с выхода блокировки второго пересчетного узла о При поступлении первого синхроимпульса (фиг. За.) на вход первого Перес-четкого узла 1 его IK-триггер 2 устанавливается в состояние Лого 1 (фиг о Зб),. так как на его I- и входах прксутств от сигналы Лог, 1 % поступающие с инверсного выхода Т.К-триг гера 3. Этот же иг- пульс запи- нуль в 1К-триггер 3 (фиг. Зз) , так как на его втором 1-входе присутствует сигнал. Лог . О,, подаваемый с прямого выхода 1К-триггера 2о. а на К-входах присутствуют сигналы Лог 1 % подавае. с инверсного выхода 1К-триггера 2 на второй К-вхо и с инверсного выхода IK-триггера 4 на первый и третий К-вход. 1К триг - гер 4 находится в режиме хранения предыдущего состояния (фиг, Зг), так как на его втором 1-входе и на третьем К входе присутствуют сигна.пь Лог 0 % подаваемые соответственно с прямого выхода 1К-триггера 3 и с прямого выхода 1К-триггера 2. На выходе устройства появляется код 000 001.

При появлении второго синхро1-1м- пульса (фиг. За) уровни сигналов на I- и К-входах 1К-триггера 2 соответствуют состоянию Лог. 1 поэтому он переключится в противоположное

72

состояниеS т.е. в состояние Лого О (фиг 36) Так как в предыдущем такте 1К-триггер 2 находился в состоянии Лог. 1,, 1К-триггер 4 - в состоянии Лог О и 1-входах IK- триггера 3 присутствовали сигналы Лог. Г ,, а на втором К-входе - сигна.п Лог. подаваемый с инверсного выхода триггера 2 то в IK- триггер 3 запишется единица (фиг. Зв) 1К--триггер 4 свое состояние не Изменит (фиг. Зг)J так как находится в режиме записи нуля наличием сигнала Лог. 1 на его К-входах, подаваемых: соответственно с прямого выхода 1К-триггера 2; с инверсного выхода Т.К-триггера 3 и с входа блокировки переноса пересчетного узла, и сигна- .па Лог, О ка его втором Х-входед подаваемого с прямого выхода 1К-триг- гера 3 На выходе устройства появится код 000 010.

Перед поступлением третьего син- хро тульса на I- и К-входах IK- триггера 2 присутствуют сигналы Лог О с инверсного выхода IK-триггера 3. На К-входах 1К-триггера 3 присутствуют сигналы Лог. Г , подаваемые соответственно с инверсного

выхода 1К-триггера 2 и с инверсного выхода 1К Триггера 4,, а на 1-входе - Ж-триггера 3 - сигнал Лог. О, подаваемый с прямого выхода IK-триггера 2. На 1-входах 1К-триггера 4 присутствует сигналы Лог, 1, пос- Т5 паю1цие соответственно с инверсного . выхода 1К--триггера 2, с прямого выхода ГК-триггера 3 и с выхода блокировки переноса пересчетного узла, а на третьем К-входе 1К-триггера 4 присутствует сигнал Лог. О, поступаю- Ш.1-1Й с прямого выхода 1К-триггера 2. Такшч образом, 1К-триггер 2 находится в режиме хранения предыдущего состояния (фиг. Зб)5 1К-триггер 3 - в режиме- записи Нуля (фиг. Зв), а IK- триггер 4 - в режиме записи единицы (фиг. Зг)S поэтому третий синхроимпульс (фиг. За) устанавливает на

выходе устройства код 000 100с

Перед поступлением четвертого синхроимпульса 1К-триггер 2 находится . в счетном режиме, обусловленном наличием сигнала Лог.. 1 на его I- и К-входахэ поступающего с инверсного выхода 1К триггера 3, 1К-триггер 3 находится в режю.е хранения предыдущего состоянияS обусловленного нали

чием сигнала Лог. О на его втором 1-входе, поступающего с прямого выхода 1К-триггера 2, И на его первом И третьем К-входах, -поступающего с инверсного выхода 1К-триггера 4. 1К-триггер 4 также находится в режиме хранения предьщущего состояния (фиг. Зг), обусловленного наличием сигналов Лог. О на его третьем К-входе, поступающего с прямого выхо да 1К-триггера 2 и на его втором 1-входе с прямого выхода 1К-триг- гера 3.

Таким образом, четвертый синхроимпульс изменяет состояние только 1К-триггера 2 (фиг. 36). На выходе устройства Появится код 000 101.

Перед поступлением пятого синхроимпульса (фиг. За) триггеры первого пересчетного узла находятся в следу- ющих режимах: 1К-триггер 2 в счетном режиме (фиг. 36); 1К-триггер 3 в режиме хранения предыдущего состояния (фиг. Зв); 1К-триггер 4 в режиме записи нуля (фиг. Зг).

На втором, третьем и четвертом входах элемента 4И-ЗИ-ИЛИ-НЕ 5 присутствуют сигналы Лог. 1, подаваемые соответственно с прямого выхода 1К-триггера 4, с прямого выхода Ж-триггера 2 и с входа блокировки переноса пересчетного узла. Таким образом, пятый синхроимпульс установит все 1К-триггеры первого пересчетного узла в исходное состояние, и через первьй вход элемента 4И-ЗИ- -ИЛИ-НЕ 5 с выхода переноса первого пересчетного узла поступит на информационный вход второго пересчетного .узла (фиг. Зд). При этом 1К-триггер 2 второго пересчетного узла установится в единичное состояние (фиг. Зе). На выходе устройства появится код 001 000. При этом на выходе бло- кировки переноса второго пересчетног узла появится сигнал Лог. О, поступающий на вход блокировки переноса первого пересчетного узла.

Шестой синхроимпульс устанавливает 1К-триггеры первого пересчетного узла в следующие состояния: IK- триггер 2 в состояние Лог. 1К-триггеры 3 и 4 свое состояние не изменят.

На выходе устройства появится код 001 001.

Седьмой синхроимпульс устанавливает 1К-триггеры первого пересчетног

g ю

15

20 25

JQ с

0

5

узла в следующие состояния: 1К-триг- гер 2 в состояние Лог. О, 1К-триг- гер 3 в состояние Лог. 1К-триггер 4 свое состояние не изменит.

На выходе устройства появится код 001 010.

В этом состоянии на пятом и шестом входах элемента 4И-ЗИ-Ш1И-НЕ 5 первого пересчетного узла присутствуют сигналы Лог. 1, подаваемые соответственно с прямого выхода 1К-триггера 3 и с выхода элемента НЕ 6.

Перед приходом восьмого синхроимпульса 1К-триггерыпервого пересчетного узла находятся в следующих режимах: 1К-триггер 2 в режиме хранения предыдущего состояния; 1К-триг- - гер 3 в режиме записи нуля; 1К-триг- гер 4 в режиме хранения предьщущего состояния, обусловленного наличием сигнала Лог. О на его .третьем I- и первом К-входах, подаваемого на вход блокировки переноса с второго пересчетного узла. Таким обра- зом, восьмой синхроимпульс (фиг. За) установит все 1К-триггеры первого пересчетного узла в исходное состояние и через седьмой вход элемента 4И-ЗИ-ИЛИ-НЕ 5 с выхода переноса первого пересчетного узла поступит на информационньга вход второго пересчетного узла. На выходе устройства. повторяется как описано (фиг. 3) до появления 101 010 двадцатым синхроимпульсом. Следующий двадцать первьй синхроимпульс устанавливает все триггеры всех пересчетных узлов в состояние 000 000 и устройство приводится в исходное состояние.

Формула изобретения

Устройство для формирования последовательности натуральных чисел в р-коде -Фибоначчи, содержащее пересчетных узлов, причем информационный вход первого пересчетного узла является информационным входом устройства, входы сброса всех пересчетных узлов объединены и подключены к входу сброса устройства, о т- л и,ч а ю щ е е с я тем, что, с целью повышения быстродействия,каждый пересчетный узел содержит три 1К-триггера, элемент АИ-ЗИ-ИПИ-НЕ и элемент НЕ, причем входы сброса триггеров объединены и подключены к входу сброса пересчетного узла, входы синхронизации триггеров и первые входы первой и второй групп входов элемента 4И-ЗИ-ИЛИ-НЕ объединены и подключены к информационному входу пересчетного узла,1- и К-входы первого триггера и второй К-вход третьего триггера подключены к инверсному выходу второго триггера, первые и третьи I- и К-входы которого подключены к инверсному выходу третьего триггера, прямой выход которого подключен к второму входу первой группы входов элемента 4И-ЗИ--ИЛИ-НЕ, прямой выход первого триггера подключен к третьему 1-входу второго триггера, третьему К-входу третьего триггера и третьему входу первой группы входов элемента 4И-ЗИ-ИЛИ-НЕ, второй К-вход второго триггера и первый 1-вход третьего триггера подключены к инверсному выходу первого триггера, который является выходом переноIt t

tit

са пересчетного узла, вход разрешения каскадирования которого подключен к четвертому входу первой группы

входов элемента 4И-ЗИ-ИЛИ-НЕ, входу элемента НЕ, первому третьего триггера и второму 1-входу третьего триггера, второй 1-вход которого и второй вход второй группы входов

элемента 4И-ЗИ-ИЛИ-НЕ подключены к прямому выходу второго триггера, выход элемента НЕ подключен к третьему входу второй группы входов элемента 4И-ЗИ-ИЛИ-НЕ, выход которого

является выходом каскадирования пересчетного узла, прямые выходы триггеров являются информационными выходами пересчетного узла, информационный вход i+1-го пересчетного узла

подключен к выходу каскадирования i-ro (..,p+1) пересчетного узла, вход разрешения каскадирования которого соединен с выходом переноса i+l-ro -пересчетного узла.

t t t

T г j

5

, / /

I I И I I I I I I И I I I И I I М

e

x

3

ор С. Патрушева 4196/24

Составитель С. Курош Техред Г.Ге.рбер.

Корректор А

Тираж 343

Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор А. Тяско

| название | год | авторы | номер документа |

|---|---|---|---|

| Пересчетная схема в коде Фибоначчи | 1985 |

|

SU1322467A1 |

| Пересчетное устройство в @ -кодах Фибоначчи | 1987 |

|

SU1497743A1 |

| Модуль пересчетной схемы в минимальном Р-коде Фибоначчи | 1988 |

|

SU1511862A1 |

| Устройство для управления преобразователем постоянного напряжения в квазисинусоидальное с ШИМ | 1983 |

|

SU1358055A1 |

| Многоканальное устройство для управления вентильным преобразователем | 1990 |

|

SU1777216A1 |

| Многофункциональное счетное устройство | 1985 |

|

SU1298911A2 |

| Счетчик импульсов | 1985 |

|

SU1298904A1 |

| Функциональный счетчик | 1988 |

|

SU1531214A1 |

| Пересчетная схема в коде Фибоначчи | 1990 |

|

SU1757098A1 |

| Устройство для измерения временных интервалов /его варианты/ | 1984 |

|

SU1255985A1 |

Изобретение относится к вычислительной технике и предназначено для генерирования последовательности на-. туральных чисел в р-коде Фибоначчи в устройствах приема и обработки цифровой информации. Целью изобретения является повышение быстродейст- вия- Генератор выполнен на (р + 1) пересчетных узлах. Преимуществом устройства является выполнение пересчетных узлов на Ж-триггерах и новые связи между пересчетными узлами. Каждый пересчетный узел содержит три Ж-триггера, элемент 4И-ЗИ-2ИЛИ- -НЕ и элемент НЕ. 3 ил. | сл с ts9 4 «

| Генератор последовательности @ -чисел Фибоначчи | 1983 |

|

SU1091146A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор последовательностей ( @ , @ )-чисел с произвольными начальными условиями | 1983 |

|

SU1104493A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор последовательности обобщенных чисел фибоначчи с произвольными начальными условиями | 1976 |

|

SU662926A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-07—Публикация

1984-07-10—Подача